## 32-Bit RISC Microcontroller

CMOS

## FR Family MB91110 Series

# MB91110/MB91V110

#### DESCRIPTION

The MB91110 series is a standard single-chip micro controller featuring various I/O resources and bus control mechanisms to incorporate the control with required for high performance high-speed CPU processes, having a 32-bit RISC CPU (FR30 series) in its core. Although external bus access is the basis for supporting a large address space accessible by a 32-bit CPU, a 1-KB instruction cache memory has been built-in to increase the instruction/ execution speed of the CPU.

This unit features the optimal specifications for incorporating applications that require high performance CPU processing power such as navigation systems, high performance facsimile systems, printer control, etc.

#### ■ FEATURES

#### FR30CPU

- 32-bit RISC, load / store architecture, 5-level pipeline

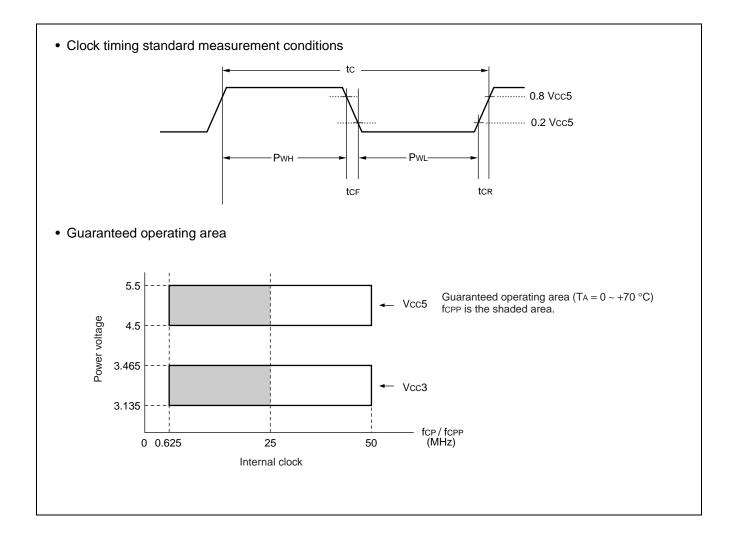

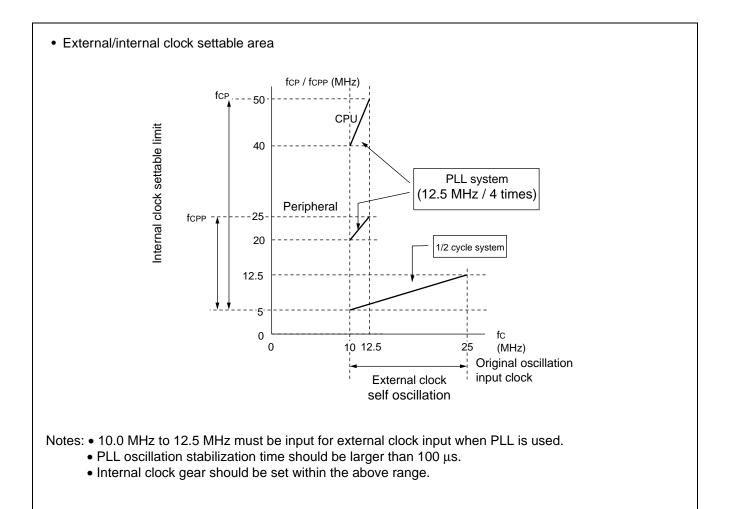

- Operating frequency : external 25 MHz, internal 50 MHz

- Multi-purpose register : 32 bits  $\times$  16

- 16-bit fixed length instructions (basic instruction), 1 instruction per cycle

- · Instructions for barrel shift, bit processing and inter memory transfers : Instructions suited to loading purposes

- Function entry / exit instruction, multi load / store instruction of register details : Instruction capable of handling High level language instruction.

- Register Interlock function : Simplification of assembler description

#### PACKAGE

#### (Continued)

- Branch instruction with delay slot : Reduction in overheads in case of branching

- Multiplier is built-in / Supported at instruction level Signed 32-bit multiplication : 5 cycles

- Signed 16-bit multiplication : 3 cycles

- Interruption (saving PC and PS) : 6 cycles, 16 priority levels

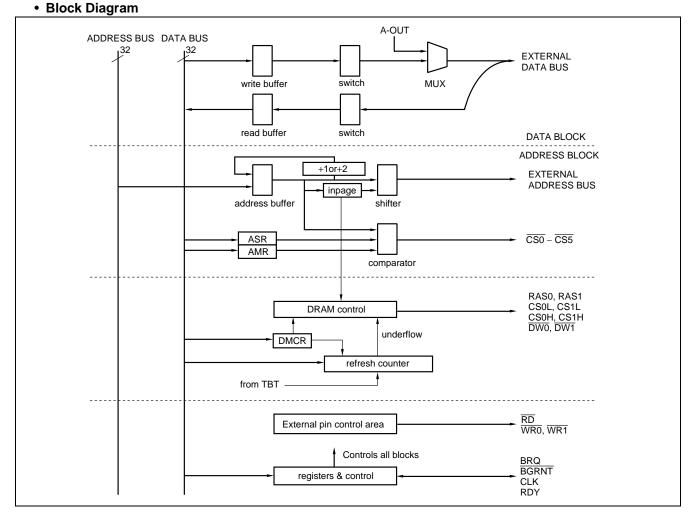

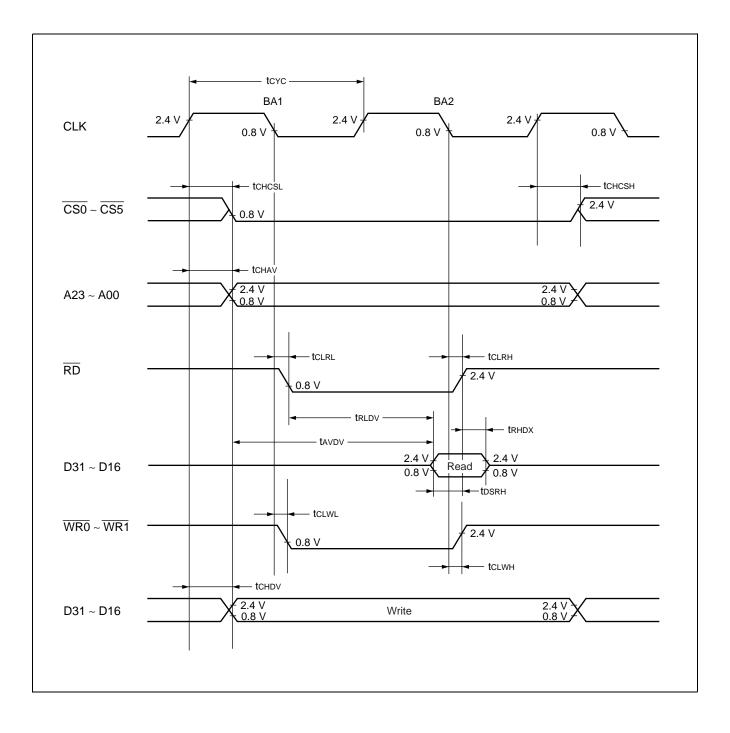

#### **Bus Interface**

- 24-bit address bus (16 MB space)

- Operating frequency : 25 MHz

- 16- / 8-bit data bus

- Basic external bus cycle : 2 clock cycles

- · Chip select output that can be set to a minimum 64-Kbyte units

- Interface support for various memories DRAM interface (areas 4, 5)

- Automatic waiting cycle : Can be randomly set from 0 to 7 cycles per area

- Unused data and address pins can be used as input/output ports.

- Supports "little endian" mode (One area is selected from areas 1 to 5)

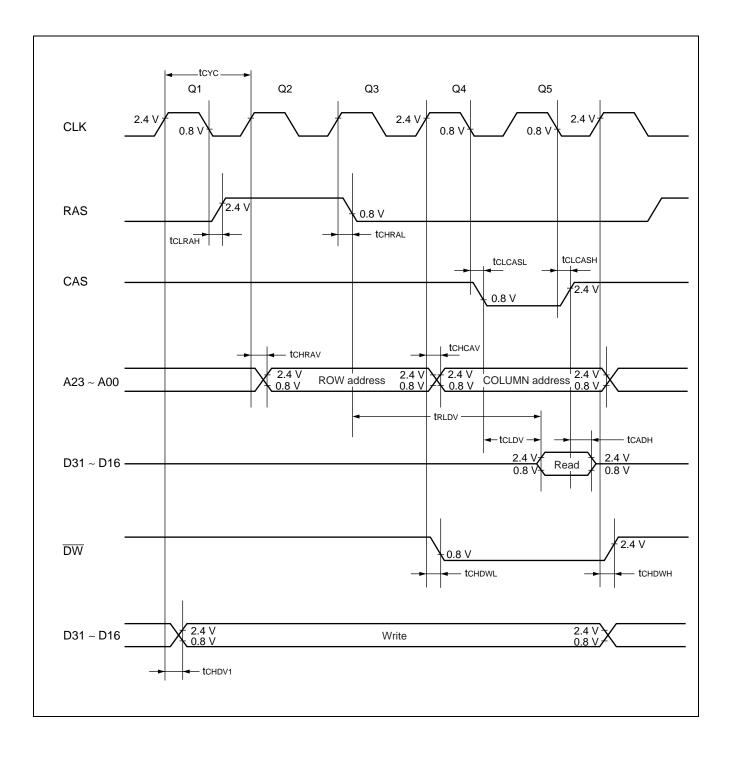

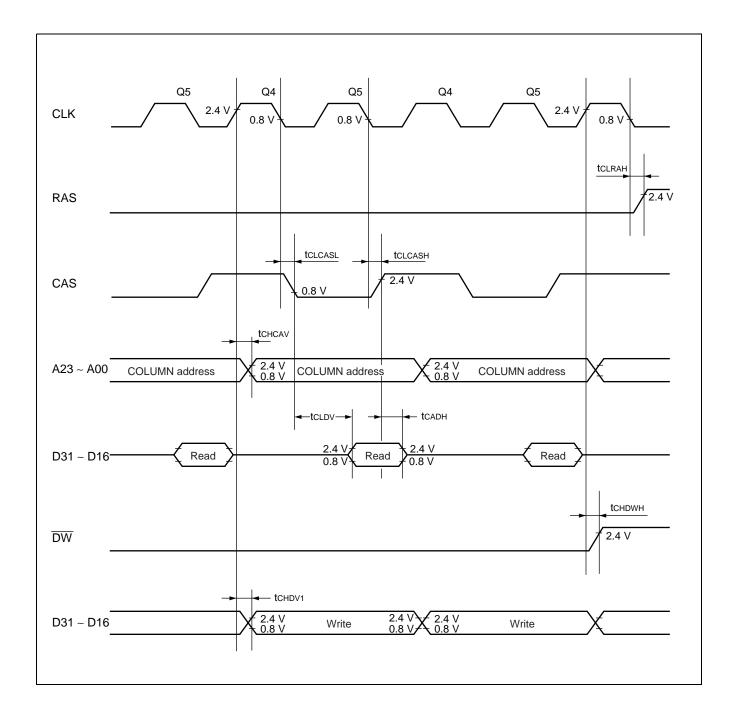

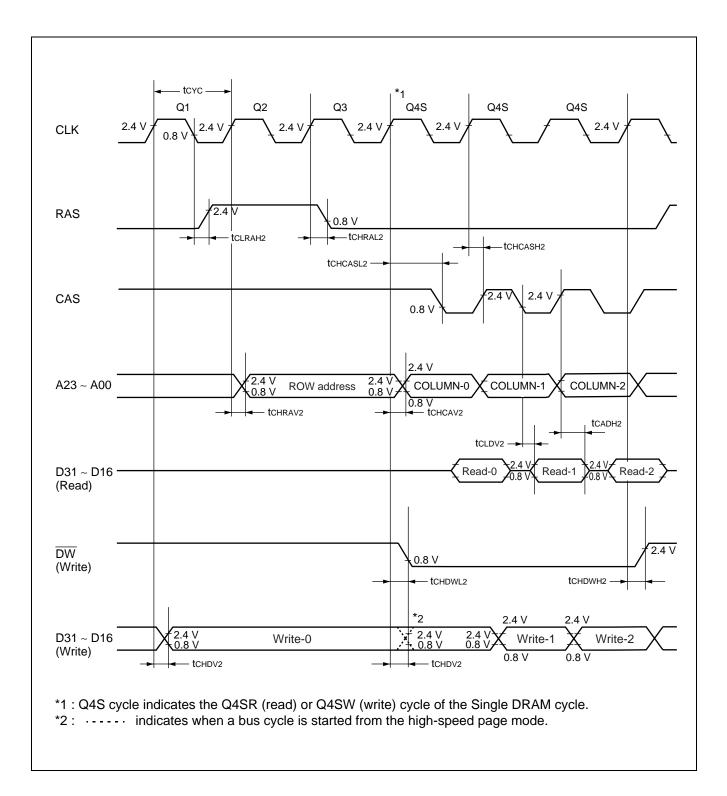

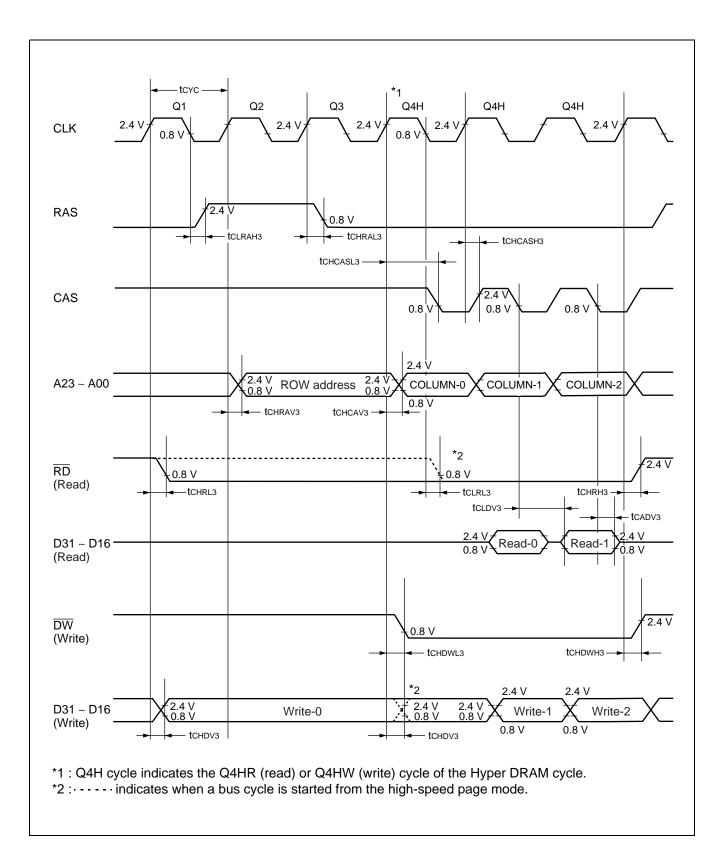

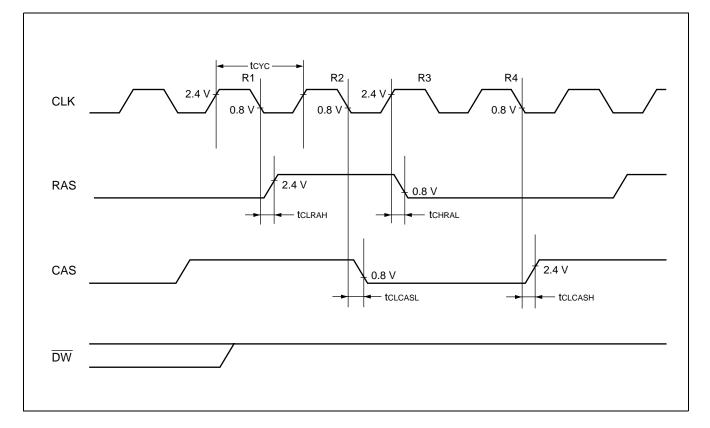

#### **DRAM Interface**

- 2-bank individual control (area 4, 5)

- Normal mode / high speed page mode

- Basic bus cycles : normally 5 cycles, 1 cycle access is possible in high-speed page mode.

- Programmable waveform : 1 cycle waiting can be inserted automatically in RAS and CAS.

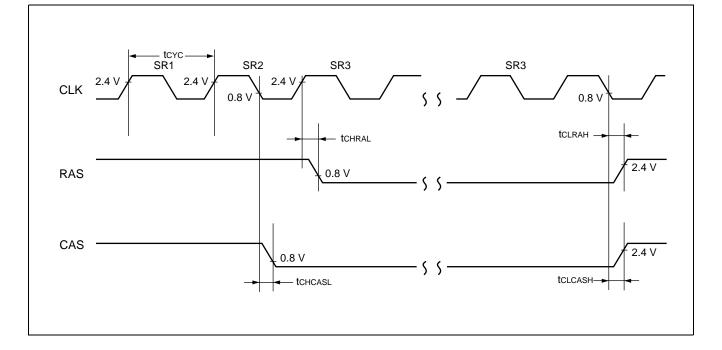

- DRAM refresh CBR refresh (Interval is randomly set using the 6-bit timer.) Self refresh mode

- Supports addresses for 8, 9, 10 and 12 columns

- 2CAS/1WE or 2WE/1CAS can be selected.

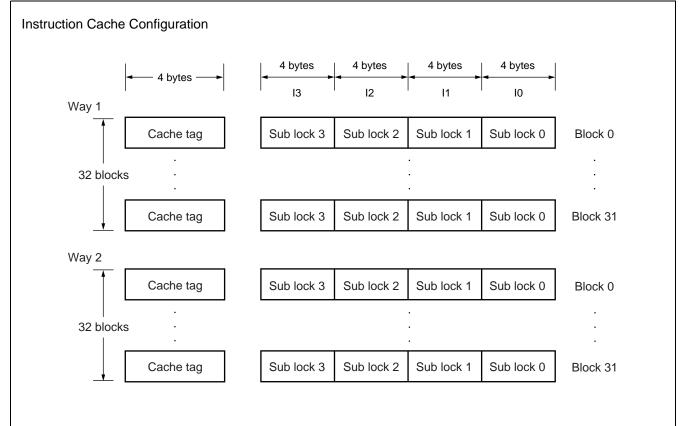

#### **Cache Memory**

- 1 KB instruction cache

- 2 way set associative

- 32 blocks / way, 4 entries (4 words) / block

- Lock function : Residing in the specified program codes at cache

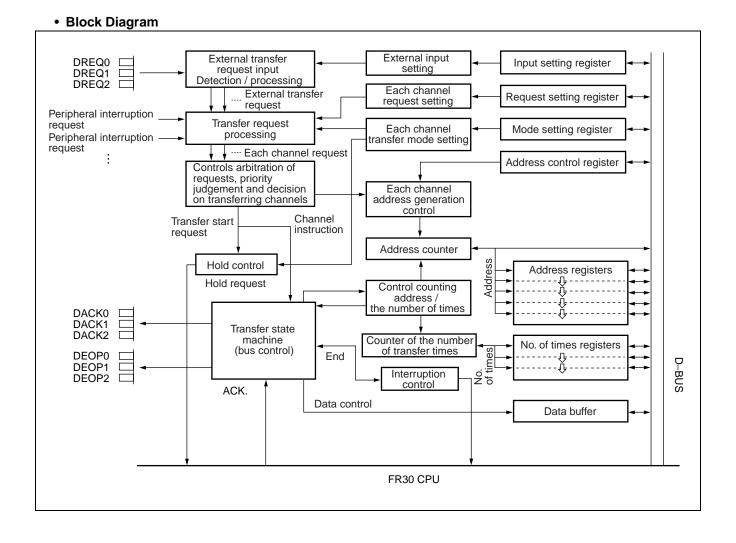

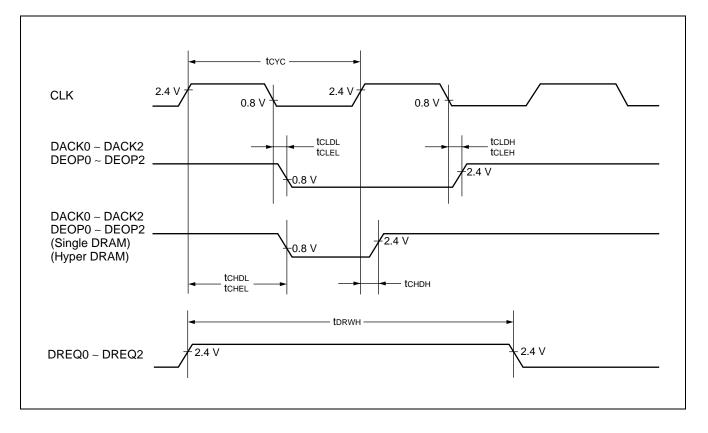

#### DMA Controller (DMAC)

- 5 channels

- External  $\rightarrow$  external 2.5 access cycles / transfer (if 2 clock cycles are defined as 1 access cycle)

- Internal  $\rightarrow$  external 1.5 access cycles / transfer (if 2 clock cycles are defined as 1 access cycle)

- Address register (inc, dec, or reload are possible) : 32 bits  $\times$  5 channels

- Transfer count register (reload possible) : 16 bits  $\times$  5 channels

- Transfer factors : external pin / built-in resources interruption request / software

- Transfer sequence

Step transfer / block transfer

Burst / consecutive transfer

- Transfer data length : 8-bit, 16-bit or 32-bit can be selected

- Suspension is possible using NMI / interruption request

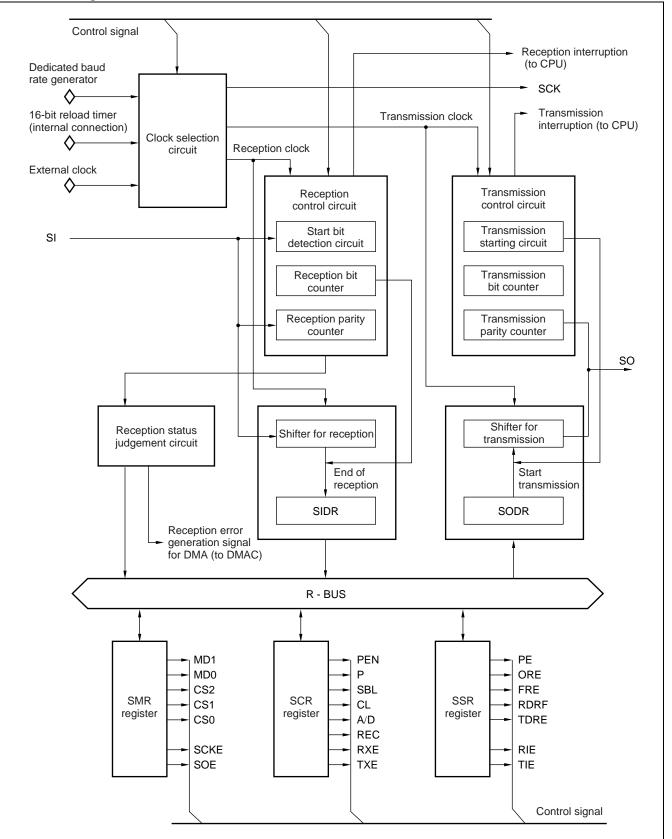

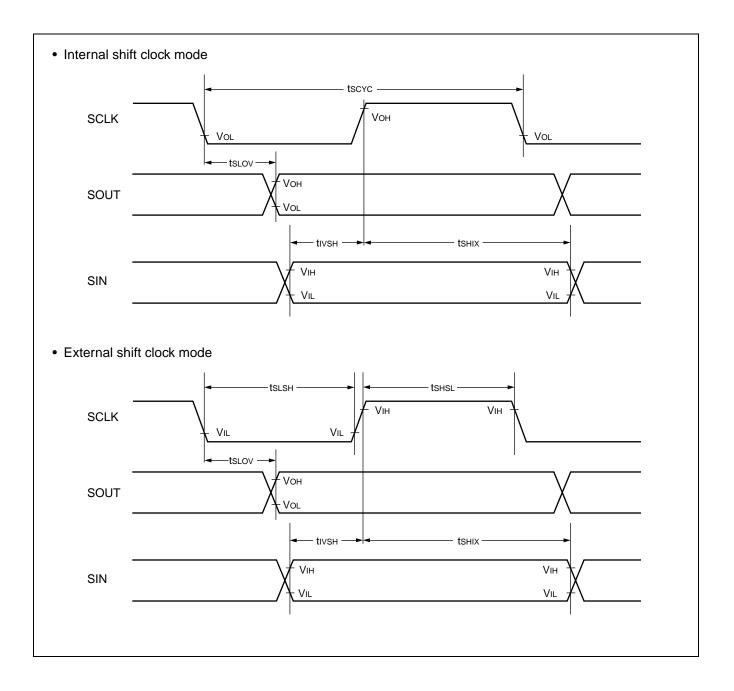

#### UART

- Fully duplicated double buffer

- Data length : 7 to 9 bits (without parity) , 6 to 8 bits (with parity)

- Asynchronous (start-stop synchronization) or CLK synchronized communication can be selected.

- Multiprocessor mode

- Dedicated baud rate generator is built-in.

- External clock can be used as the transfer clock

- · Baud rate clock can be output

- Error detection : parity, frame, overrun

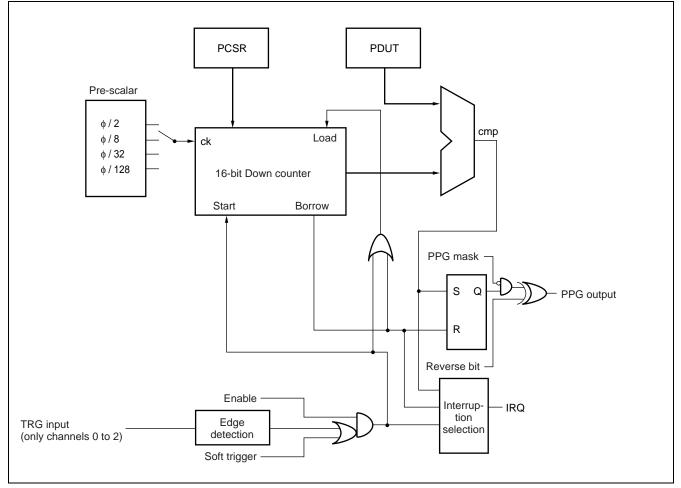

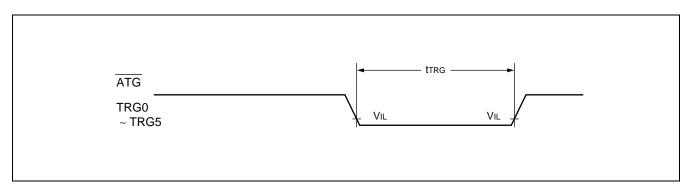

#### **PPG Timer**

- 16 bits, 6 channels (frequency setting register / duty setting register)

- PWM function or one-shot function can be selected

- · Initiation : Software or external trigger can be selected

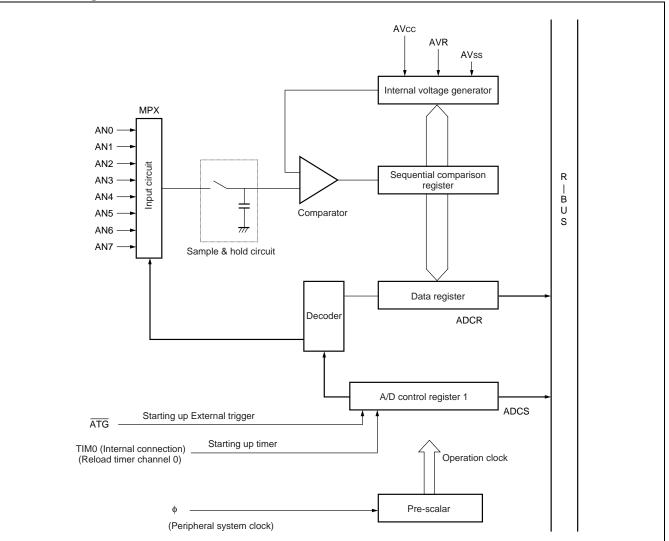

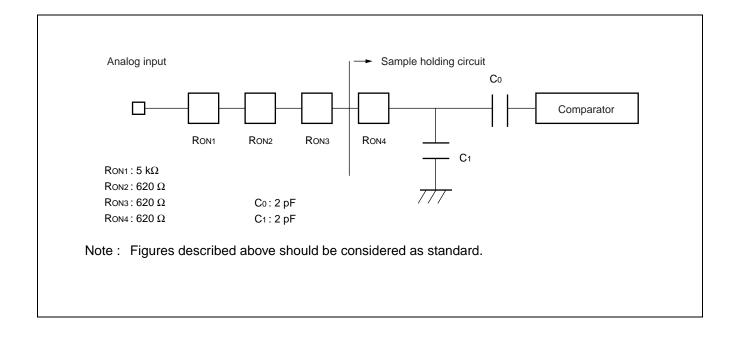

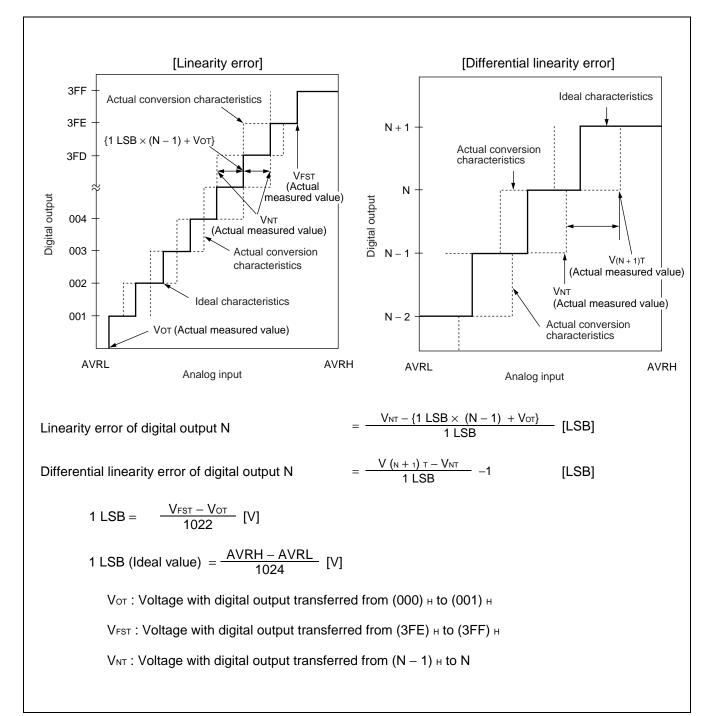

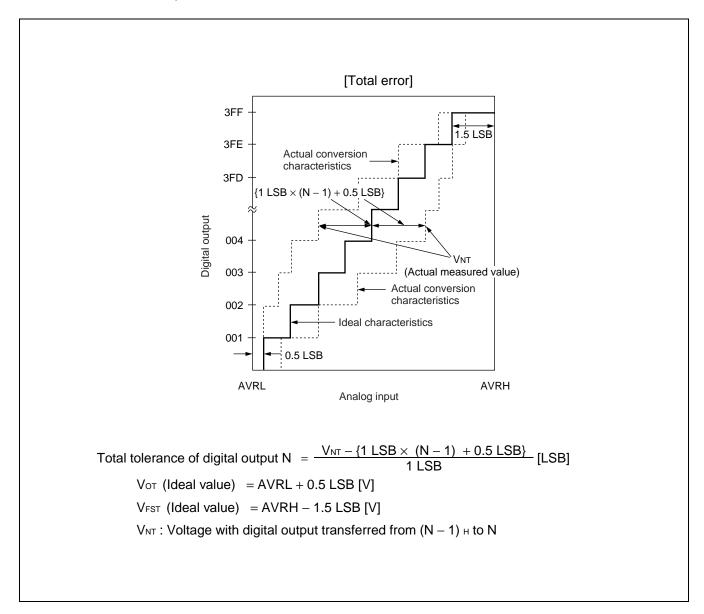

#### A/D Converter (sequential conversion type)

- 10-bit resolution, 8 channels

- Sequential comparison conversion : 5.6  $\mu$ s in the case of 25 MHz

- Sample & hold circuit is built-in.

- Conversion mode : Single, scan or repeat conversion can be selected.

- Initiation : Software, external trigger or built-in timer can be selected.

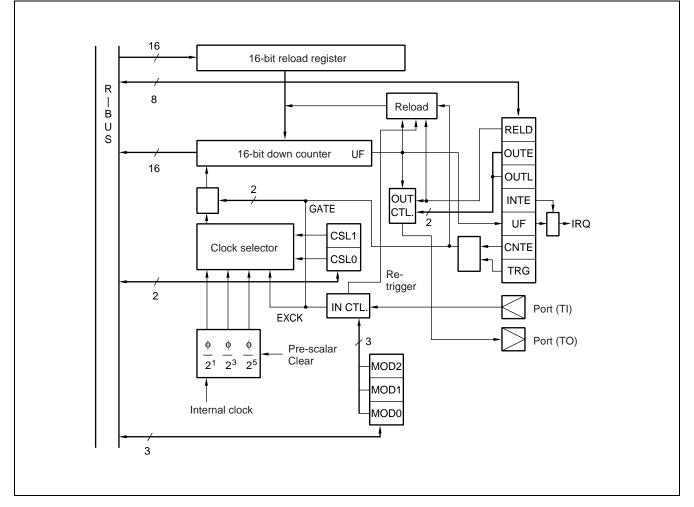

#### **Reloading Timer**

- 16-bit timer : 2 channels

- Internal clock : 2 clock cycle resolutions, 2, 8 or 32 cycles can be selected.

- · Pin input : event counter input / gate function

- Rectangular wave output

#### **Other Interval Timer**

• Watchdog timer : 1 channel

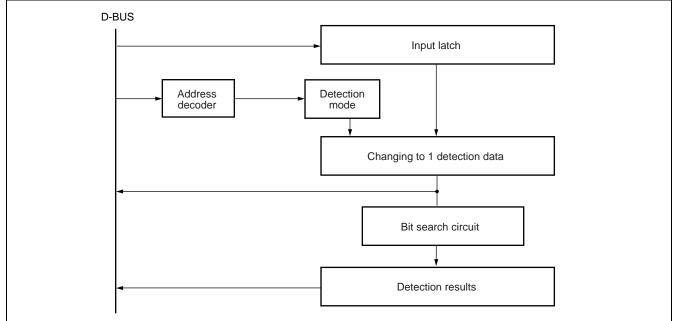

#### **Bit Search Module**

• Searches the first "1" / "0" change bit positions within 1 cycle from MSB in 1 word.

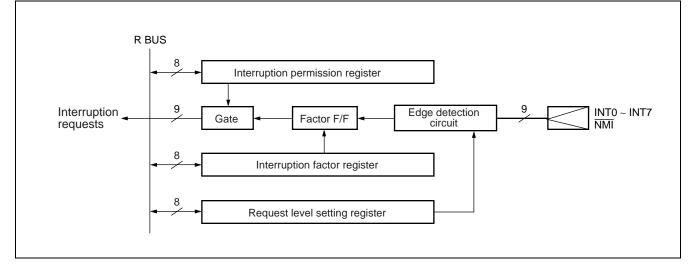

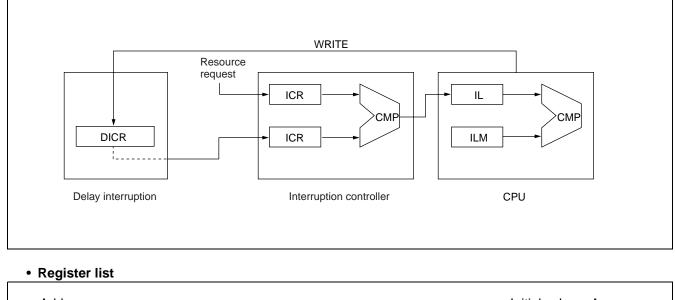

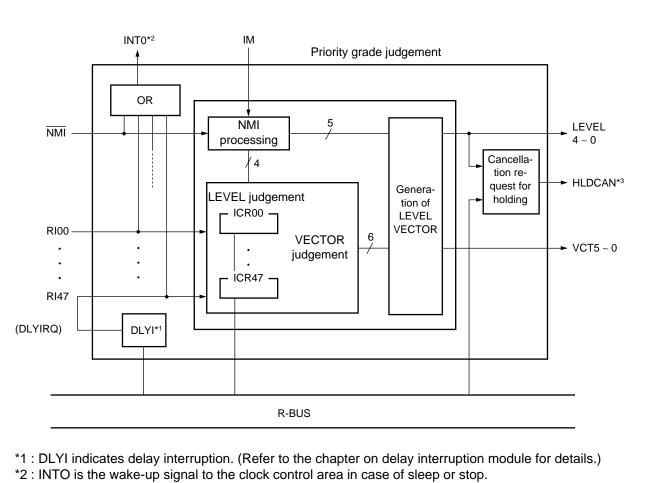

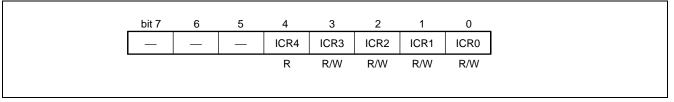

#### **Interruption Controller**

- External interruption input : Mask impossible interruption (NMI) , normal interruption × 8 (INT0 to INT7)

- Internal interruption factors : UART, DMAC, A/D, reloading timer, PPG timer, delay interruption

- Priority levels are programmable except for mask impossible interruption (16 levels)

#### **Reset Factors**

· Power-on reset / hardware standby / watchdog timer / software reset / external reset

#### Low Power Consumption Mode

Sleep / stop mode

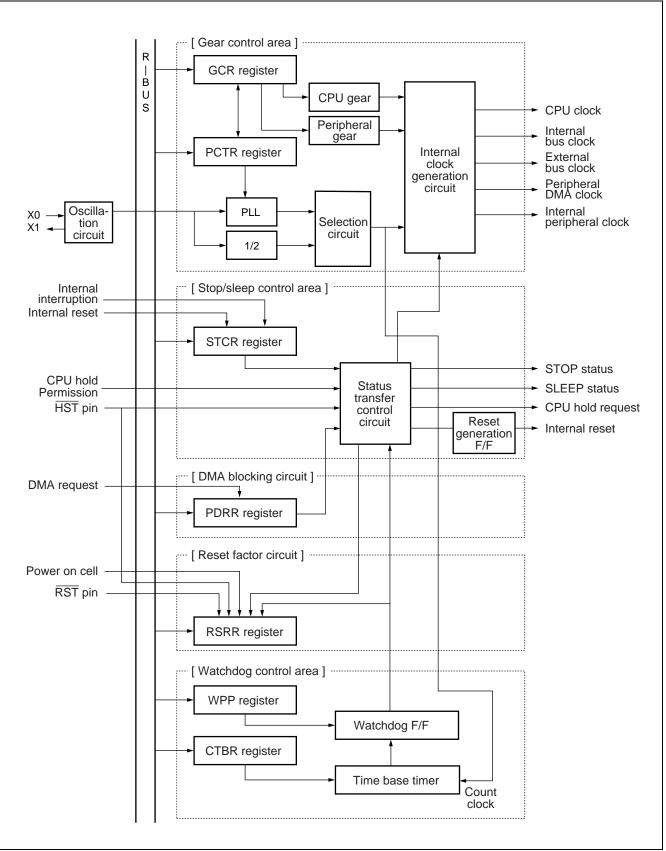

#### **Clock Control**

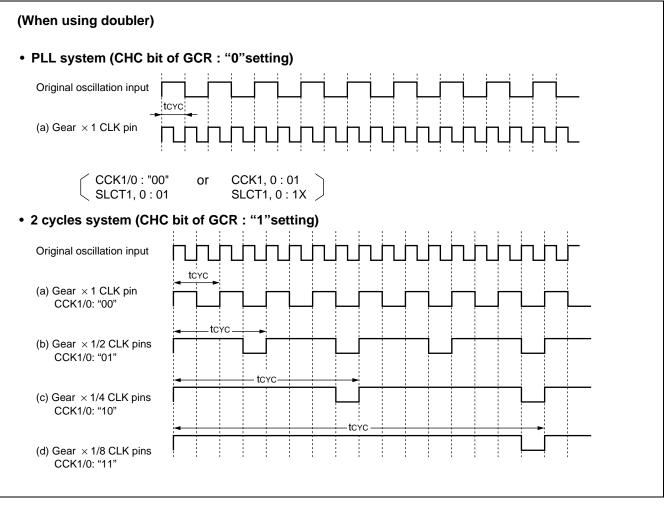

• Gear functions : Operating clock frequencies peripheral to the CPU can be set randomly and independently. Gear locks can be selected from 1/1, 1/2, 1/4 or 1/8 (or 1/2, 1/4, 1/8, or 1/16).

#### Others

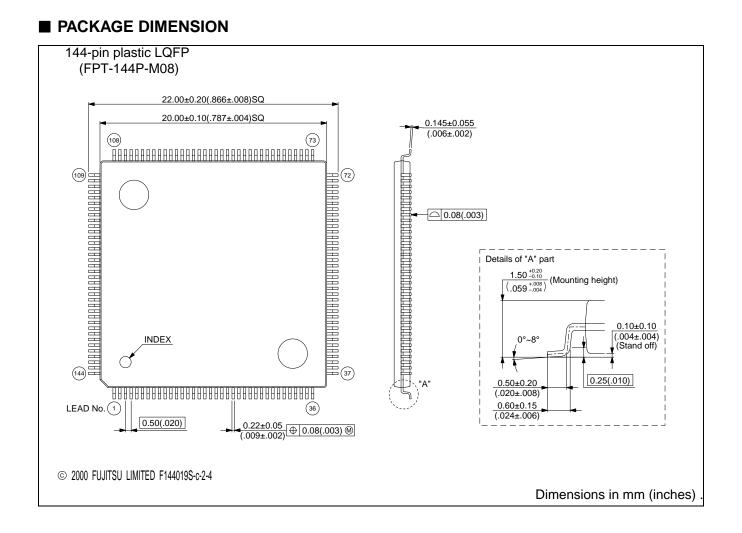

- Package : LQFP-144

- CMOS technology : 0.35 μm

- Power : 5.0 V  $\pm$  10%, 3.3 V  $\pm$  5%

### ■ PRODUCT LINEUP

|                             | MB91V110<br>(For evaluation) | MB91110<br>(I-RAM mounted version) |

|-----------------------------|------------------------------|------------------------------------|

| I-RAM                       | 16 Kbyte                     | 16 Kbyte                           |

| RAM                         | 5 Kbyte                      | 5 Kbyte                            |

| ROM                         |                              |                                    |

| I-\$                        | 1 Kbyte                      | 1 Kbyte                            |

| DSU3<br>evaluation function | Mounted                      |                                    |

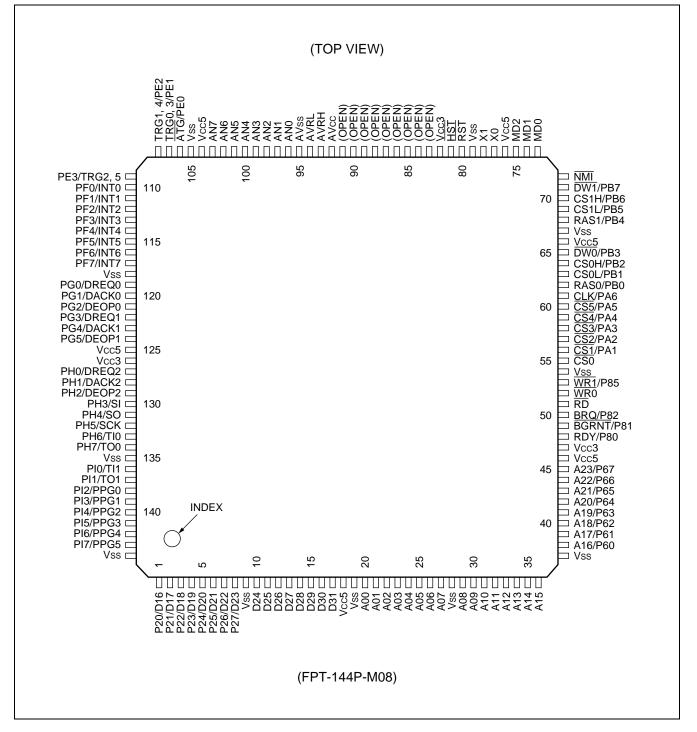

#### ■ PIN ASSIGNMENT

#### ■ PIN DESCRIPTIONS

| Pin no.                                      | Pin name                                                                             | I/O* | Circuit type | Function                                                                                                                                                |

|----------------------------------------------|--------------------------------------------------------------------------------------|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8         | D16/P20<br>D17/P21<br>D18/P22<br>D19/P23<br>D20/P24<br>D21/P25<br>D22/P26<br>D23/P27 | I/O  | С            | These pins use bits 16 to 23 of the external data bus.<br>They can be used as a port (P20 to P27) if the external bus<br>width is 8 bits.               |

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | D24<br>D25<br>D26<br>D27<br>D28<br>D29<br>D30<br>D31                                 | I/O  | С            | These pins use bits 24 to 31 of the external data bus.                                                                                                  |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | A00<br>A01<br>A02<br>A03<br>A04<br>A05<br>A06<br>A07                                 | I/O  | С            | These pins use bits 00 to 07 of the external address bus.                                                                                               |

| 29<br>30<br>31<br>32<br>33<br>34<br>35<br>36 | A08<br>A09<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15                                 | I/O  | С            | These pins use bits 08 to 15 of the external address bus.                                                                                               |

| 38<br>39<br>40<br>41<br>42<br>43<br>44<br>45 | A16/P60<br>A17/P61<br>A18/P62<br>A19/P63<br>A20/P64<br>A21/P65<br>A22/P66<br>A23/P67 | I/O  | С            | These pins use bits 16 to 23 of the external address bus.                                                                                               |

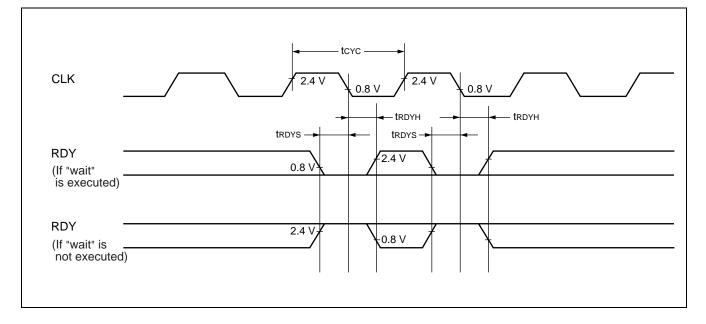

| 48                                           | RDY/P80                                                                              | I/O  | С            | This is for external ready input. "0" is input if the bus cycle be-<br>ing executed is incomplete. It can be used as a port when not<br>otherwise used. |

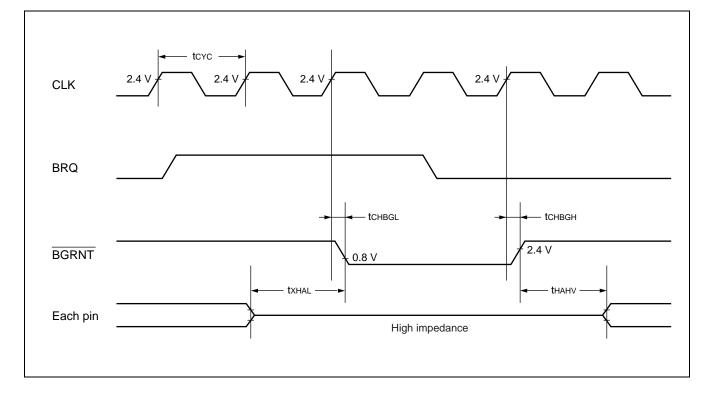

| 49                                           | BGRNT/P81                                                                            | I/O  | Н            | This is the external bus open reception output. "L" is output if<br>the external bus is opened. It can be used as a port when not<br>otherwise used.    |

| Pin no.                                      | Pin name                                                                                   | I/O*  | Circuit type | Function                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |                    |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| 50                                           | BRQ/P82                                                                                    | I/O   | С            | external bus is                                                                                                                                                                                                                                                                                                                   | This is the external bus open request input. "1" is input if the external bus is to be opened. It can be used as a port when not otherwise used. |                    |  |

| 51                                           | RD                                                                                         | 0     | G            | This is the ext                                                                                                                                                                                                                                                                                                                   | ernal bus read strok                                                                                                                             | pe.                |  |

| 52                                           | WR0                                                                                        | 0     | G            | This is the ext                                                                                                                                                                                                                                                                                                                   | ernal bus write strol                                                                                                                            | be.                |  |

|                                              |                                                                                            |       |              |                                                                                                                                                                                                                                                                                                                                   | 16-bit bus width                                                                                                                                 | 8-bit bus width    |  |

| 53                                           | WR1/P85                                                                                    | I/O   | н            | D31-24                                                                                                                                                                                                                                                                                                                            | WR0                                                                                                                                              | WR0                |  |

|                                              |                                                                                            |       |              | D23-16                                                                                                                                                                                                                                                                                                                            | WR1                                                                                                                                              | (Port is possible) |  |

| 55                                           | CS0                                                                                        | 0     | G            | Chip select 0                                                                                                                                                                                                                                                                                                                     | output (Low active)                                                                                                                              |                    |  |

| 56<br>57<br>58<br>59<br>60                   | CS1/PA1<br>CS2/PA2<br>CS3/PA3<br>CS4/PA4<br>CS5/PA5                                        | I/O   | н            | Chip select 1 output (Low active)<br>Chip select 2 output (Low active)<br>Chip select 3 output (Low active)<br>Chip select 4 output (Low active)<br>Chip select 5 output (Low active)<br>They can be used as ports when not otherwise used.                                                                                       |                                                                                                                                                  |                    |  |

| 61                                           | CLK/PA6                                                                                    | I/O   | н            | This is the system clock output. The same clock as the stan-<br>dard clock is output. This can be used as a port when not oth-<br>erwise used.                                                                                                                                                                                    |                                                                                                                                                  |                    |  |

| 62<br>63<br>64<br>65<br>68<br>69<br>70<br>71 | RAS0/PB0<br>CS0L/PB1<br>CS0H/PB2<br>DW0/PB3<br>RAS1/PB4<br>CS1L/PB5<br>CS1H/PB6<br>DW1/PB7 | I/O   | Н            | RAS output with DRAM bank 0.<br>CASL output with DRAM bank 0.<br>CASH output with DRAM bank 0.<br>WE output with DRAM bank 0. (Low active)<br>RAS output with DRAM bank 1.<br>CASL output with DRAM bank 1.<br>CASH output with DRAM bank 1.<br>WE output with DRAM bank 1.<br>They can be used as ports when not otherwise used. |                                                                                                                                                  |                    |  |

| 72                                           | NMI                                                                                        |       | E            | Non Maskable                                                                                                                                                                                                                                                                                                                      | e Interrupt (NMI) inp                                                                                                                            | ut. (Low active)   |  |

| 73<br>74<br>75                               | MD0<br>MD1<br>MD2                                                                          | I     | I            | Non Maskable Interrupt (NMI) input. (Low active)<br>These are mode pins from 0 to 2.<br>Basic MCU operation modes are set using these pins.<br>They should be connected directly to Vcc or Vss for use.                                                                                                                           |                                                                                                                                                  |                    |  |

| 77<br>78                                     | X0<br>X1                                                                                   | <br>0 | A            | Clock (oscillation) input.<br>Clock (oscillation) output.                                                                                                                                                                                                                                                                         |                                                                                                                                                  |                    |  |

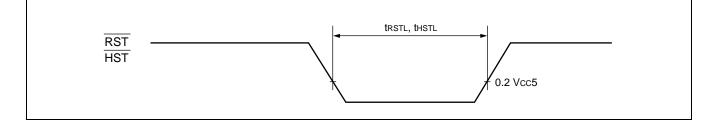

| 80                                           | RST                                                                                        | I     | В            | This is the ext                                                                                                                                                                                                                                                                                                                   | ernal reset input. (L                                                                                                                            | .ow active)        |  |

| 81                                           | HST                                                                                        | I     | E            | This is the ha                                                                                                                                                                                                                                                                                                                    | dware standby inpu                                                                                                                               | ıt. (Low active)   |  |

| 83                                           | (OPEN)                                                                                     |       | —            | Set this to OPEN.                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                  |                    |  |

| 84<br>85<br>86                               | (OPEN)<br>(OPEN)<br>(OPEN)                                                                 |       | _            | Set this to OPEN.                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                  |                    |  |

| Pin no.                                          | Pin name                                                             | I/O* | Circuit type                                                                                                                                                                                                                   | Function                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------|----------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 87<br>88<br>89<br>90                             | (OPEN)<br>(OPEN)<br>(OPEN)<br>(OPEN)                                 | _    | _                                                                                                                                                                                                                              | Set this to OPEN.                                                                                                                                                                                                                                                                                               |

| 91                                               | (OPEN)                                                               |      | — Set this to OPEN.                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 92                                               | AVcc                                                                 |      |                                                                                                                                                                                                                                | Vcc power supply for the A/D converter.                                                                                                                                                                                                                                                                         |

| 93                                               | AVRH                                                                 | _    |                                                                                                                                                                                                                                | A/D converter reference voltage (high potential side). Be sure to turn on/off this pin with potential higher than AVRH applied to $V_{\rm CC}$ .                                                                                                                                                                |

| 94                                               | AVRL                                                                 |      |                                                                                                                                                                                                                                | A/D converter reference voltage (low potential side).                                                                                                                                                                                                                                                           |

| 95                                               | AVss                                                                 |      |                                                                                                                                                                                                                                | Vss power supply for the A/D converter.                                                                                                                                                                                                                                                                         |

| 96<br>97<br>98<br>99<br>100<br>101<br>102<br>103 | AN0<br>AN1<br>AN2<br>AN3<br>AN4<br>AN5<br>AN6<br>AN7                 | I    | D                                                                                                                                                                                                                              | [AN0 to 7] A/D converter analog input.                                                                                                                                                                                                                                                                          |

| 106                                              | ATG/PE0                                                              | I/O  | н                                                                                                                                                                                                                              | [ATG] This is the external trigger input for the A/D converter.<br>This function is always used if selected as the initiation factor<br>for A/D, so output by other functions should be stopped ex-<br>cept when it is carried out intentionally.                                                               |

|                                                  |                                                                      |      |                                                                                                                                                                                                                                | [PE0] This is a general-purpose input/output port.                                                                                                                                                                                                                                                              |

| 107                                              | TRG0, 3/PE1                                                          |      |                                                                                                                                                                                                                                | [TRG0 to 5] These are external trigger input pins of the PPG.                                                                                                                                                                                                                                                   |

| 108<br>109                                       | TRG1, 4/PE2<br>TRG2, 5/PE3                                           | I/O  | H                                                                                                                                                                                                                              | [PE1 to 3] These are general-purpose input/output ports.                                                                                                                                                                                                                                                        |

| 110<br>111<br>112<br>113<br>114<br>115<br>116    | INT0/PF0<br>INT1/PF1<br>INT2/PF2<br>INT3/PF3<br>INT4/PF4<br>INT5/PF5 | I/O  | F                                                                                                                                                                                                                              | [INT0 to 7] These are external interruption request inputs.<br>This input is always used while the corresponding external<br>interruption is permitted, so output using other functions<br>should be stopped except when carried out intentionally.<br>[PF0 to 7] These are general-purpose input/output ports. |

| 116<br>117                                       | INT6/PF6<br>INT7/PF7                                                 |      |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

| 119                                              | DREQ0/PG0                                                            | I/O  | H<br>[DREQ0] This is the DMA external transfer reque<br>0) . This input is always used if selected as the transfer reque<br>for DMAC, so outputs from other functions should<br>stopped except when carried out intentionally. |                                                                                                                                                                                                                                                                                                                 |

|                                                  |                                                                      |      |                                                                                                                                                                                                                                | [PG0] This is a multi-purpose input/output port.                                                                                                                                                                                                                                                                |

| Pin no. | Pin name          | I/O* | Circuit type | Function                                                                                                                                                                                                                                 |

|---------|-------------------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120     | DACK0/PG1         | I/O  | С            | [DACK0] This is the DMAC external transfer request recep-<br>tion output (ch 0) . This function is effective if the transfer re-<br>quest reception output specification of DMAC is permitted.                                           |

| 120     | DAGROFGT          | 1/0  |              | [PG1] This is a multi-purpose input/output port. This function<br>is effective if the transfer request reception output specifica-<br>tion of DMAC is prohibited.                                                                        |

| 121     | DEOP0/PG2         | I/O  | С            | [DEOP0] This is the DMA transfer end signal output (ch 0) .<br>This function is effective if the transfer end signal output<br>specification of DMAC is permitted.                                                                       |

| 121     | DEOF0/PG2         | 1/0  |              | [PG2] This is a multi-purpose input/output port. This function<br>is effective if the transfer end signal output specification of<br>DMAC is prohibited.                                                                                 |

| 122     | DREQ1/PG3         | I/O  | н            | [DREQ1] This is the DMA external transfer request input (ch<br>1). This input is always used if selected as the transfer factor<br>of DMAC, so output using other functions should be stopped<br>except when carried out intentionally.  |

|         |                   |      |              | [PG3] This is a multi-purpose input/output port.                                                                                                                                                                                         |

| 123     | DACK1/PG4         | I/O  | С            | [DACK1] This is the DMAC external transfer request recep-<br>tion output (ch 1) . This function is effective if the transfer re-<br>quest reception output specification of DMAC is permitted.                                           |

| 123     |                   | 1/0  | C            | [PG4] This is a multi-purpose input/output port. This function<br>is effective if the transfer request reception output specifica-<br>tion of DMAC is prohibited.                                                                        |

| 124     | DEOP1/PG5         | I/O  | С            | [DEOP1] This is the DMA transfer end signal output (ch 1) .<br>This function is effective if the transfer end signal output<br>specification of DMAC is permitted.                                                                       |

| 124     | DEOFI/PG5         | 1/0  |              | [PG5] This is a multi-purpose input/output port. This function<br>is effective if the transfer end signal output specification of<br>DMAC is prohibited.                                                                                 |

| 127     | DREQ2/PH0         | I/O  | н            | [DREQ2] This is the DMA external transfer request input (ch<br>2) . This input is always used if selected as the transfer factor<br>of DMAC, so output using other functions should be stopped<br>except when carried out intentionally. |

|         |                   |      |              | [PH0] This is a multi-purpose input/output port.                                                                                                                                                                                         |

| 128     | 128 DACK2/PH1 I/O |      | С            | [DACK2] This is the DMAC external transfer request recep-<br>tion output (ch 2) . This function is effective if the transfer re-<br>quest reception output specification of DMAC is permitted.                                           |

| 120     |                   |      |              | [PH1] This is a multi-purpose input/output port. This function<br>is effective if the transfer request reception output specifica-<br>tion of DMAC is prohibited.                                                                        |

| Pin no. | Pin name      | I/O* | Circuit type | Function                                                                                                                                                                                     |

|---------|---------------|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 129     | DEOP2/PH2 I/O |      | с            | [DEOP2] This is the DMA transfer end signal output (ch 2) .<br>This function is effective if the transfer end signal output<br>specification of DMAC is permitted.                           |

| 129     | DEOF2/F112    | 1/0  |              | [PH2] This is a multi-purpose input/output port. This function<br>is effective if the transfer end signal output specification of<br>DMAC is prohibited.                                     |

| 130     | SI/PH3        | I/O  | н            | [SI] This is UART data input. This input is always used while UART inputs, so outputs from other functions should be stopped except when carried out intentionally.                          |

|         |               |      |              | [PH3] This is a general-purpose input/output port.                                                                                                                                           |

|         |               |      |              | [SO] This is UART data output. This function is effective when UART data output specification is permitted.                                                                                  |

| 131     | SO/PH4        | I/O  | С            | [PH4] This is a general-purpose input/output port. This func-<br>tion is effective when UART data output specification is pro-<br>hibited.                                                   |

|         |               |      |              | [SCK] This is UART clock input/output. Clock output is effec-<br>tive when UART clock output specification is permitted.                                                                     |

| 132     | SCK/PH5       | I/O  | Н            | [PH5] This is a general-purpose input/output port. This func-<br>tion is effective when UART clock output specification is pro-<br>hibited.                                                  |

| 133     | TI0/PH6       | I/O  | н            | [TI0] This is reload timer 0 input. It is always used when re-<br>load timer input is permitted, so outputs from other functions<br>should be stopped except when carried out intentionally. |

|         |               |      |              | [PH6] This is a general-purpose input/output port.                                                                                                                                           |

| 134     | TO0/PH7       | I/O  | С            | [TO0] This is reload timer 0 Output. This function is effective when reload timer specification is permitted.                                                                                |

| 134     | 100/11/       | 1/0  |              | [PH7] This is a general-purpose input/output port. This func-<br>tion is effective when reload timer specification is prohibited.                                                            |

| 136     | TI1/PI0       | I/O  | н            | [TI1] This is reload timer 1 input. It is always used when re-<br>load timer input is permitted, so outputs from other functions<br>should be stopped except when carried out intentionally. |

|         |               |      |              | [PI0] This is a general-purpose input/output port.                                                                                                                                           |

|         |               |      |              | [T01] This is the reload timer 1 output. This function is effec-<br>tive if the output specification of the reload timer is permitted.                                                       |

| 137     | TO1/PI1       | I/O  | С            | [PI1] This is a multi-purpose input/output port. This function<br>is effective if the output specification of the reload timer is<br>prohibited.                                             |

| Pin no.                                                           | Pin name                         | I/O* | Circuit type | Function                                                                                                                                             |

|-------------------------------------------------------------------|----------------------------------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 138<br>139<br>140                                                 | PPG0/PI2<br>PPG1/PI3<br>PPG2/PI4 | I/O  | С            | [PPG0 to 5] This is the PPG timer 1 output. This function is effective if the output specification of the PPG timer is permitted.                    |

| 141<br>142<br>143                                                 | PPG3/PI5<br>PPG4/PI6<br>PPG5/PI7 | 1/0  | U U          | [PI2 to 7] This is a multi-purpose input/output port. This func-<br>tion is effective if the output specification of the PPG timer is<br>prohibited. |

| 18<br>46<br>66<br>76<br>104<br>125                                | Vcc5                             |      |              | This provides power for the 5 V digital circuit system.                                                                                              |

| 47<br>82<br>126                                                   | Vcc3                             |      |              | This provides power for the 3 V digital circuit system.                                                                                              |

| 9<br>19<br>28<br>37<br>54<br>67<br>79<br>105<br>118<br>135<br>144 | Vss                              |      |              | This is the earth level for digital circuits.                                                                                                        |

\*: I/O shown above indicates input/output classification.

(Continued)

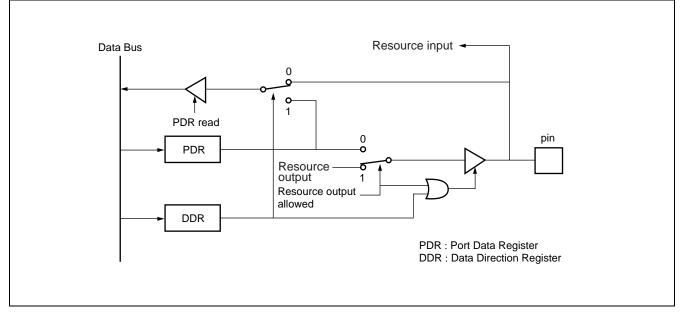

Note : The I/O port and resource input/outputs for most of the above pins are multiplexed, i.e. Pxx/xxxx. In the event of both the port and resource outputs were to use the same pins, the resource is given priority.

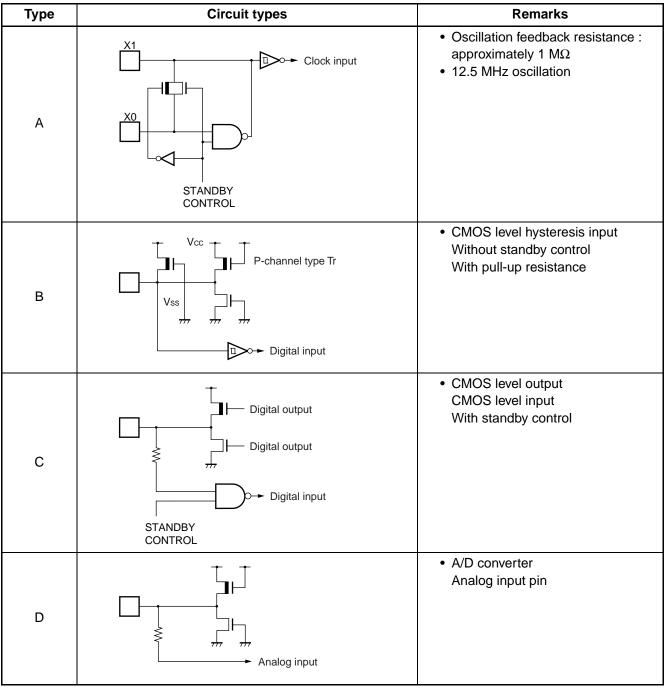

#### ■ I/O CIRCUIT TYPE

| Type | Circuit types                                                                             | Remarks                                                                                                |

|------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| E    | Digital input                                                                             | CMOS level hysteresis input<br>Without standby control                                                 |

| F    | Digital output                                                                            | <ul> <li>CMOS level output</li> <li>CMOS level hysteresis input<br/>Without standby control</li> </ul> |

| G    | Digital output                                                                            | CMOS level output                                                                                      |

| н    | Digital output<br>Digital output<br>Digital output<br>Digital input<br>STANDBY<br>CONTROL | <ul> <li>CMOS level output</li> <li>CMOS level hysteresis input<br/>With standby control</li> </ul>    |

| I    | Digital input                                                                             | CMOS level input     Without standby control                                                           |

#### ■ HANDLING DEVICES

#### • Preventing Latch-up

The "Latch-up" phenomenon may be generated if a voltage in excess of  $V_{CC}$  or lower than  $V_{SS}$  is applied to the input/output pins, or if the voltage exceeds the rating between  $V_{CC}$  and  $V_{SS}$ . If latch-up is generated, the electrical current increases significantly and may destroy certain components due to the excessive heat, so great care must be taken to ensure that the maximum rating is not exceeded during use.

#### • Handling Unused Input Pins

Input pins that are not used should be pulled up or down as they may cause erroneous operations if they are left open.

#### • External Reset Input

"L" level should be input to the  $\overline{RST}$  pin, which is required for at least five machine cycles to ensure the internal status is reset.

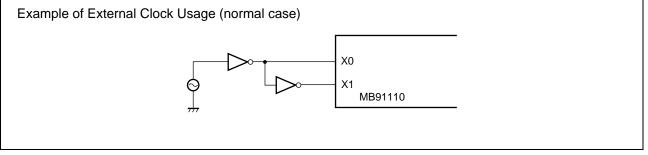

#### • Using External Clocks

If external clock is used, X0 pin should be provided, and X1 pin should be provided with reverse phase to X0 pin input. If the STOP mode (oscillation stop mode) is used simultaneously, the X1 pin is stopped with the "H" output. So, when STOP mode is specified, approximately 1 k $\Omega$  of resistance should be added externally. An example of the external clock usage methods is shown in the following circuit.

Note : Resistance must be added to the X1 pin if the STOP mode (oscillation stop mode) is used.

#### • Power Supply Pins

In products with multiple Vcc or Vss pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However you must connect the pins to an external power and a ground line to lower the electro-magnetic emission level to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total current rating.

Make sure to connect Vcc and Vss pins via the lowest impedance to power lines.

It is recommended to provide a bypass capacitor of around 0.1 F between Vcc and Vss pins near the device.

#### • Crystal Oscillator Circuits

Noise around the X0 or X1 pins may cause erroneous operation. Make sure to provide bypass capacitors via shortest distances from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure that lines of oscillation circuits not cross the lines of other circuit.

A printed circuit board artwork surrounding the X0 and X1 pins with ground area for stabilizing the operation is highly recommended .

#### • N.C. Pins

N.C. pins must be opened for use.

#### • Mode Pins (MD0 to MD2)

Those pins must be directly connected to Vcc or Vss for use.

Pattern length between V<sub>cc</sub> or V<sub>ss</sub> and each mode pin on the printed-circuit board should be arranged to be as short as possible to prevent the test mode being erroneously turned on due to noise, they should also be connected with low impedance.

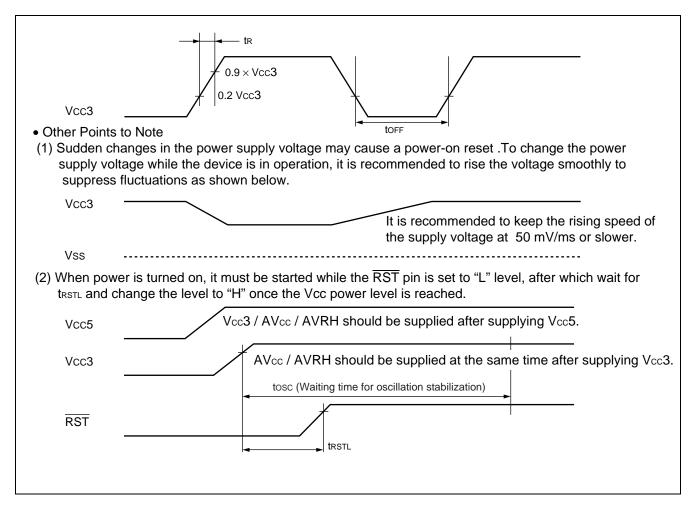

#### • In the Event that Power Is Turned on

The  $\overline{RST}$  pin must be started from "L" level when the power is turned on, and when the power is adjusted to the V<sub>CC</sub> level it should be changed to the "H" level after being left for at least five cycles of the internal operation clock.

#### • Original Oscillation Input in the Event that Power Is Turned on

The clock must be input until the waiting status for oscillation stability is reset in the event that power is turned on.

#### • Hardware Standby in the Event that Power Is Turned on

Standby is not set in the event that power is turned on while the HST pin is set at "L" level. The HST pin becomes effective after being reset, but it must first be returned to "H" level.

#### Power on Reset

When power is turned on, "Power on reset" must be executed. If the power voltage falls below the guaranteed operating voltage, "Power on reset" must be executed by turning on power supply again.

#### • Restrictions for Standby

Programs to be set for stop and sleep must be placed on the ROM in the C-bus or address area of the external memory. If placed in the ROM address area on the I-bus, operation can not be guaranteed after returning.

#### • Execution of Programs in I-ROM/RAM Areas

In the event that programs in the I-ROM/RAM areas are executed, enter the I-ROM/RAM areas in accordance with the JMP system instruction. Conversely, when accessing from programs in the I-ROM/RAM area to those in other areas, exit in accordance with the JMP system instructions.

#### BLOCK DIAGRAM

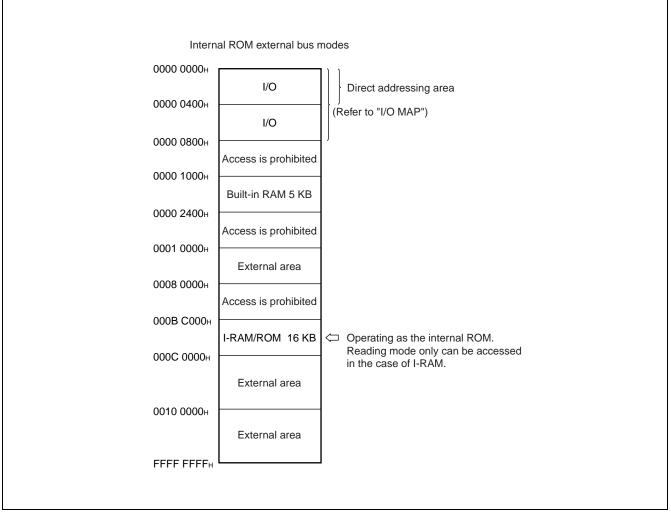

#### MEMORY SPACE

The FR30 series has 4 Gbytes (2<sup>32</sup> addresses) of logic address space which the CPU accesses linearly.

#### 1. Memory Map

Note : MB91110 series only supports internal ROM external bus mode.

#### • Direct addressing area

The following areas of the address space are used for I/O. This area is called the "direct addressing area" and the address of the operand can be specified directly during instruction. The direct area differs depending on data size to be accessed.

- Byte data access : 0-0FFH

- Half-word data access : 0-1FFH

- Word data access : 0-3FF<sub>H</sub>

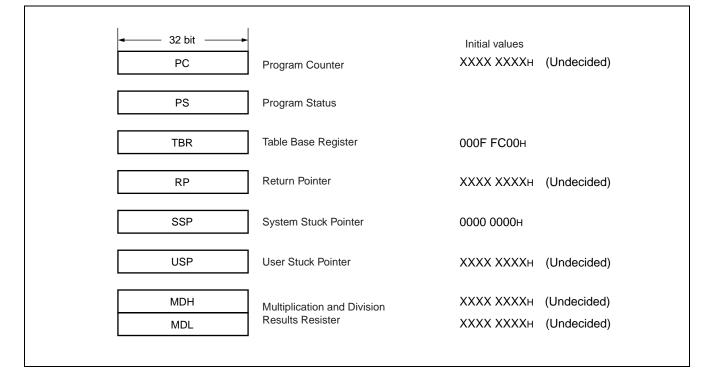

#### 2. Registers

There are two types of multi-purpose registers in the FR family. One is a dedicated purpose register that exists within the CPU and the other is a multi-purpose register that exists in the memory.

| <ul> <li>Dedicated Registers</li> </ul>                   |                                                                                                                  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Program Counter (PC)                                      | : 32-bit length; indicates instruction storage position.                                                         |

| Program Status (PS)                                       | : 32-bit length; stores register pointers and condition codes.                                                   |

| Table Base Register (TBR)                                 | : Holds the starting address of the vector table to be used for Exception, In-<br>terruption and Trapping (EIT). |

| Return Pointer (RP)                                       | : Holds the address to which you will return to from the sub-routine.                                            |

| System Stuck Pointer (SSP)                                | : Indicates the systems stuck position.                                                                          |

| User Stuck Pointer (USP)                                  | : Indicates the user's stuck position.                                                                           |

| Multiplication and Division<br>Results Resister (MDH/MDL) | : 32-bit length; These are the registers for multiplication and division.                                        |

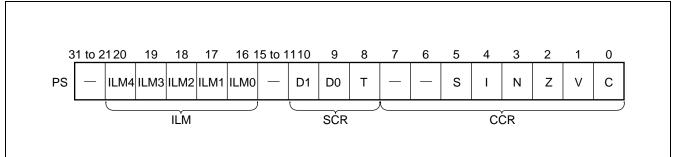

#### • Program Status (PS)

PS is the register that holds the program status and is classified into three categories, namely, Condition Code Register (CCR), System Condition Code Register (SCR) and Interruption Level Master Register (ILM).

#### • Condition Code Register (CCR)

S flag : Specifies the stuck pointer to be used as R15.

- I flag : Controls permission and prohibition of user interruption requests.

- N flag : Indicates codes when the computation results are defined as integers that are expressed in complements of 2.

- Z flag : Indicates if arithmetic results were "0."

- V flag : Indicates when operands are used for computation and defined as integers expressed in complements of 2, and indicates whether or not an overflow is generated as a result of the computation.

- C flag : Indicates whether carrying or borrowing is generated from the highest bit as a result of the computation.

#### • System Condition Code Register (SCR)

T flag : Specifies whether or not the step- trace- trap will be valid.

#### • Interruption Level Mask Register (ILM)

ILM4 to ILM0 : Holds the interruption level mask values, and those values that are held by the ILM are used for the level mask. Interruption requests can only be accepted when the interruption levels handled within the interruption requests to be input into the CPU are stronger than the levels shown by the ILM.

| ILM4 | ILM3 | ILM2 | ILM1 | ILM0 | Interruption level | Strength |

|------|------|------|------|------|--------------------|----------|

| 0    | 0    | 0    | 0    | 0    | 0                  | Strong   |

|      |      |      |      |      |                    | Ť        |

| 0    | 1    | 0    | 0    | 0    | 15                 |          |

|      |      | 1    |      |      | <b>↓</b>           |          |

| 1    | 1    | 1    | 1    | 1    | 31                 | Weak     |

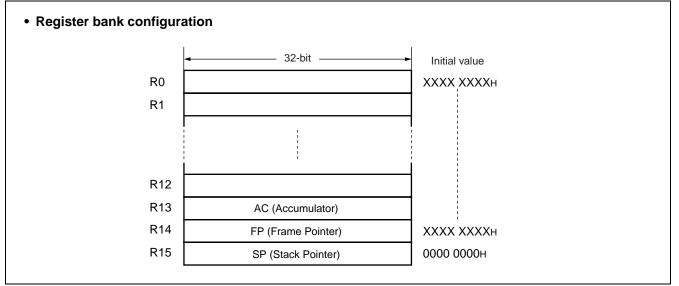

#### MULTI-PURPOSE REGISTERS

The multi-purpose registers are CPU registers (R0 to R15) which are used as accumulators for various computations and memory access pointers (field that indicates the address) .

Special purposes are assumed for the following three registers out of the 16 registers. Thus, some instructions are emphasized.

R13 : Virtual accumulator (AC)

R14 : Frame Pointer (FP)

R15 : Stack Pointer (SP)

Initial values for R0 to R14 on resetting are unspecified. The initial value of R15 will be 0000 0000H (SSP value).

#### ■ MODE SETTING

#### 1. Pins

Mode pins and set mode

| M   | lode pins |     | Mode name                 | Reset vector    | External data bus | Bus modes             |  |

|-----|-----------|-----|---------------------------|-----------------|-------------------|-----------------------|--|

| MD2 | MD1       | MD0 | Mode name                 | access areas    | width             | Bus modes             |  |

| 0   | 0         | 0   | External vector<br>mode 0 | External        | 8-bit             | External ROM external |  |

| 0   | 0         | 1   | External vector<br>mode 1 | External 16-bit |                   | bus mode              |  |

| 0   | 1         | 0   |                           |                 |                   | Setting is prohibited |  |

| 0   | 1         | 1   | Internal vector<br>mode   | Internal        |                   | Single chip mode*     |  |

| 1   |           |     |                           |                 | —                 | Usage is prohibited   |  |

\*: MB91110 series is not supported single chip mode.

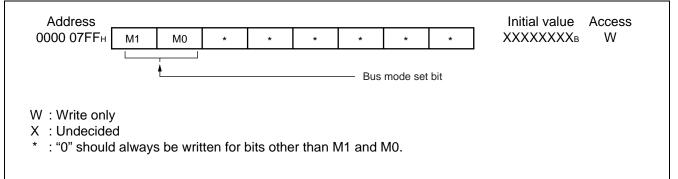

#### 2. Register

#### • Mode register (MODR) and set mode

#### • Bus mode set bit and its functions

| M1 | MO | Functions                      | Remarks               |

|----|----|--------------------------------|-----------------------|

| 0  | 0  | Single chip mode               | Not supported         |

| 0  | 1  | Internal ROM external bus mode |                       |

| 1  | 0  | External ROM external bus mode |                       |

| 1  | 1  | _                              | Setting is prohibited |

#### ■ I/O MAP

| Address             |                                                                   |                             | Internal recourse           |                        |                                                  |

|---------------------|-------------------------------------------------------------------|-----------------------------|-----------------------------|------------------------|--------------------------------------------------|

| Address             | +0                                                                | +1                          | +2                          | +3                     | Internal resource                                |

| 000000н             | _                                                                 | PDR2 (R/W)<br>XXXXXXXX      |                             | _                      |                                                  |

| 000004н             | _                                                                 | PDR6 (R/W)<br>XXXXXXXX      |                             |                        |                                                  |

| 000008н             | PDRB (R/W)<br>XXXXXXXX                                            | PDRA (R/W)<br>- XXXXXX -    |                             | PDR8 (R/W)<br>XXXX     | Port data register                               |

| 00000Сн             |                                                                   | _                           | _                           |                        |                                                  |

| 000010н             | _                                                                 | _                           | PDRE (R/W)<br>XXXX          | PDRF (R/W)<br>XXXXXXXX |                                                  |

| 000014н             | PDRG (R/W)<br>XXXXXX                                              | PDRH (R/W)<br>XXXXXXXX      | PDRI (R/W)<br>XXXXXXXX      |                        |                                                  |

| 000018 <sub>H</sub> |                                                                   | -                           | _                           |                        | Reserved                                         |

| 00001Cн             |                                                                   | _                           | _                           |                        | Reserved                                         |

| 000020н             | SSR (R/W)<br>00001-00                                             | SIDR/SODR (R/W)<br>XXXXXXXX | SCR (R/W)<br>00000100       | SMR (R/W)<br>00000-00  | UART                                             |

| 000024н             | _                                                                 | CDCR (R/W)<br>011111        | _                           | _                      |                                                  |

| 000028н             | TMRLR<br>XXXXXXXX                                                 | (W)<br>XXXXXXXX             | TMR<br>XXXXXXXX             | (R)<br>XXXXXXXX        | Reload timer 0                                   |

| 00002Cн             | -                                                                 | _                           | TMCSR<br>0000               | (R/W)<br>00000000      |                                                  |

| 000030н             | 00030H TMRLR (W) TMR (R)<br>XXXXXXX XXXXXXXX XXXXXXX XXXXXXXXXXXX |                             |                             |                        |                                                  |

| 000034н             |                                                                   | _                           | TMCSR (R/W)<br>0000 0000000 |                        | Reload timer 1                                   |

| 000038н             | ADCR                                                              | (R)<br>XXXXXXXX             | ADCS<br>00000000            | (R/W)<br>00000000      | A/D converter<br>(Sequential<br>comparison type) |

| 00003Сн             |                                                                   | _                           | _                           |                        | Reserved                                         |

| Address         | Register         |                 |                        |                        |                   |  |  |

|-----------------|------------------|-----------------|------------------------|------------------------|-------------------|--|--|

| Address         | +0               | +1              | +2                     | +3                     | Internal resource |  |  |

| 000040н         |                  |                 | _                      |                        | Reserved          |  |  |

| 000044н         | Access is        | prohibited      | PCSR<br>XXXXXXXX       | (W)<br>XXXXXXXX        | PPG0              |  |  |

| 000048н         | PDUT<br>XXXXXXXX | (W)<br>XXXXXXX  | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 | FFGU              |  |  |

| 00004Cн         | Access is        | prohibited      | PCSR<br>XXXXXXXX       | (W)<br>XXXXXXXX        | PPG1              |  |  |

| 000050н         | PDUT<br>XXXXXXXX | (W)<br>XXXXXXX  | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 |                   |  |  |

| 000054н         | Access is        | prohibited      | PCSR<br>XXXXXXXX       | (W)<br>XXXXXXXX        | PPG2              |  |  |

| <b>000058</b> н | PDUT<br>XXXXXXXX | (W)<br>XXXXXXXX | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 | 1102              |  |  |

| 00005Cн         | Access is        | prohibited      | PPG3                   |                        |                   |  |  |

| 000060н         | PDUT<br>XXXXXXXX | (W)<br>XXXXXXXX | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 |                   |  |  |

| 000064н         | Access is        | prohibited      | PCSR<br>XXXXXXXX       | (W)<br>XXXXXXXX        |                   |  |  |

| 000068н         | PDUT<br>XXXXXXXX | (W)<br>XXXXXXXX | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 | PPG4              |  |  |

| 00006Сн         | Access is        | prohibited      | PCSR<br>XXXXXXXX       | (W)<br>XXXXXXXX        | PPG5              |  |  |

| 000070н         | PDUT<br>XXXXXXXX | (W)<br>XXXXXXX  | PCNH (R/W)<br>0000000- | PCNL (R/W)<br>00000000 |                   |  |  |

| 000074н         |                  |                 | _                      |                        |                   |  |  |

| <b>000078</b> н | 000078н —        |                 |                        |                        |                   |  |  |

| 00007Сн         |                  | Reserved        |                        |                        |                   |  |  |

| 000080н         |                  |                 | _                      |                        |                   |  |  |

| Address         |                        |                        |    |    |                        |

|-----------------|------------------------|------------------------|----|----|------------------------|

| Address         | +0                     | +1                     | +2 | +3 | Internal resource      |

| 000084H         |                        |                        | -  |    |                        |

| 000088H         |                        |                        | _  |    | Reserved               |

| 00008Cн         |                        |                        | _  |    |                        |

| 000090н         |                        |                        | _  |    |                        |

| <b>000094</b> н | EIRR (R/W)<br>00000000 | ENIR (R/W)<br>00000000 | _  | _  | External interruption/ |

| 000098H         | ELVR<br>00000000       | (R/W)<br>00000000      | -  | _  | NMI                    |

| 00009Сн         |                        | -                      | _  |    |                        |

| 0000А0н         |                        | _                      | _  |    |                        |

| 0000А4н         |                        |                        |    |    |                        |

| 0000А8н         |                        | _                      | _  |    |                        |

| 0000ACн         |                        |                        | _  |    |                        |

| 0000В0н         |                        |                        | _  |    | Reserved               |

| 0000B4н         |                        |                        |    |    |                        |

| 0000В8н         |                        |                        |    |    |                        |

| 0000BCH         |                        |                        |    |    |                        |

| 0000С0н         |                        |                        |    |    |                        |

| 0000C4н         |                        |                        |    |    |                        |

|                          |                    | Internal recourse                                                                                                 |                      |                      |                                       |  |  |  |

|--------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------------------------|--|--|--|

| Address                  | +0                 | +1                                                                                                                | +2                   | +3                   | <ul> <li>Internal resource</li> </ul> |  |  |  |

| 0000C8н                  |                    |                                                                                                                   |                      | •                    | Reserved                              |  |  |  |

| 0000ССн                  |                    |                                                                                                                   |                      |                      | Reserved                              |  |  |  |

| 0000D0н                  | _                  | _                                                                                                                 | DDRE (W)             | DDRF (W)<br>00000000 | Data direction                        |  |  |  |

| 0000D4н                  | DDRG (W)<br>000000 | DDRH (W)<br>00000000                                                                                              | DDRI (W)<br>00000000 |                      | register                              |  |  |  |

| 0000D8н<br>to<br>0000FCн |                    |                                                                                                                   |                      |                      | Reserved                              |  |  |  |

| 000100н<br>to<br>0001FCн |                    |                                                                                                                   |                      |                      | Reserved                              |  |  |  |

| 000200н                  | DMACS0<br>0-00-    |                                                                                                                   | ) XX-00000           | (R/W)<br>XX-X        |                                       |  |  |  |

| <b>000204</b> н          | DMACC0<br>XX       |                                                                                                                   | xxxxxxxx xx          | (R/W)<br>XXXXXX      | DMA controller                        |  |  |  |

| 000208н                  | DMASA0<br>XXXXXX   |                                                                                                                   | xxxxxxx xx           | (R/W)<br>XXXXXX      | channel 0                             |  |  |  |

| 00020Сн                  | DMADAC<br>XXXXXX   |                                                                                                                   | xxxxxxxx xx          | (R/W)<br>XXXXXX      |                                       |  |  |  |

| 000210н                  | DMACS1<br>0-00-0   |                                                                                                                   | ) XX-00000           | (R/W)<br>XX - X      |                                       |  |  |  |

| 000214н                  | DMACC1             | DMA controller                                                                                                    |                      |                      |                                       |  |  |  |

| <b>000218</b> н          | DMASA1<br>XXXXXX   | channel 1                                                                                                         |                      |                      |                                       |  |  |  |

| 00021Сн                  |                    | XXXXXXXX       XXXXXXXX       XXXXXXXX         DMADA1       (R/W)         XXXXXXXX       XXXXXXXX       XXXXXXXXX |                      |                      |                                       |  |  |  |

| Address         |        | Reg          | jister       |        |                   |

|-----------------|--------|--------------|--------------|--------|-------------------|

| Address –       | +0     | +1           | +2           | +3     | Internal resource |

| 000220н         | DMACS2 |              |              | (R/W)  |                   |

| 000220H         | 0-00-0 | 000 000000   | XX-00000     | XX - X |                   |

| 000224н         | DMACC2 |              |              | (R/W)  |                   |

| 000224H         | XX     | XX XXXX-XXX  | XXXXXXXX XXX | XXXXXX | DMA controller    |

| 000228н         | DMASA2 | 1            |              | (R/W)  | channel 2         |

| 000220H         | XXXXXX | xx xxxxxxxx  | XXXXXXXX XX  | XXXXXX |                   |

| 00022Cн         | DMADA2 |              |              | (R/W)  |                   |

| 0002204         | XXXXXX | xx xxxxxxxx  | XXXXXXXXX XX | XXXXXX |                   |

| 000230н         | DMACS3 |              |              | (R/W)  |                   |

| 000230H         | 0-00-0 | 000 000000   | XX-00000     | XX - X |                   |

| 000234н         | DMACC3 |              |              | (R/W)  |                   |

| 000234H         | XX     | XX XXXX-XXX  | XXXXXXXX XXX | XXXXXX | DMA controller    |

| 000238н         | DMASA3 |              |              | (R/W)  | channel 3         |

| 0002308         | XXXXXX | XXX XXXXXXXX | XXXXXXXX XX  | XXXXXX |                   |

| 00023Сн         | DMADA3 |              |              | (R/W)  |                   |

| 0002304         | XXXXXX | XXX XXXXXXXX | XXXXXXXX XX  | XXXXXX |                   |

| 000240н         | DMACS4 |              |              | (R/W)  |                   |

| 0002408         | 0-00-0 | 000 000000   | XX-00000     | XX - X |                   |

| <b>000244</b> н | DMACC4 |              |              | (R/W)  |                   |

| 0002-1-11       | XX     | XX XXXX-XXX  | XXXXXXXX XXX | XXXXXX | DMA controller    |

| <b>000248</b> H | DMASA4 |              |              | (R/W)  | channel 4         |

| 0002-1011       | XXXXXX | XXX XXXXXXXX | XXXXXXXX XX  | XXXXXX |                   |

| 00024Cн         | DMADA4 |              |              | (R/W)  |                   |

| 0002408         | XXXXXX | XXX XXXXXXXX | XXXXXXXX XX  | XXXXXX |                   |

| 000250н         | DMACR  |              |              | (R/W)  | Overall DMA       |

| 00020011        |        |              | 00           | 0      | controller        |

| <b>000254</b> н |        | -            |              |        |                   |

|                 |        |              |              |        |                   |

| 000258н         |        | -            |              |        |                   |

|                 |        |              |              |        | Reserved          |

| 00025Cн         |        |              |              |        |                   |

| 000260н         |        |              |              |        |                   |

| · ·             |        |              |              |        |                   |

| Address         +0         +1         +2         +3         Internal resource           000264H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Address             |             | Internal resource |            |                                       |                           |  |