FUJITSU SEMICONDUCTOR MICROCONTROLLER

# **MB90M405** F<sup>2</sup>MC-16LX FAMILY 16-BIT MICROCONTROLLERS HARDWARE MANUAL ABSTRACTS

MB90M405 F<sup>2</sup>MC-16LX FAMILY 16-BIT MICROCONTROLLERS HARDWARE MANUAL ABSTRACTS ©1999 FUJITSU LIMITED Printed in Japan

- 1. Circuit diagrams utilizing Fujitsu products are included as a mean of illustrating typical semiconductor applications. Complete information sufficient for construction proposes is not necessarily given.

- 2. The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

- 3. The information contained in this document does not convey any license under the copy right, patent right to trademarks claimed and owned by Fujitsu.

- 4. Fujitsu reserved the right to change products or specifications without notice.

- 5. No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.

- 6. The products described in this document are not intended for use in equipment requiring high reliability, such as marine relays and medical life-support systems. For such applications, contact your Fujitsu sales representative.

- 7. If the products and technologies described in this document are controlled by the Foreign Exchange and Foreign Trade Control Act established in Japan, their export is subject to prior approval based on the said act.

#### Preface

#### ■ Objective of Manual and Target Audience

The MB90M405 Series is a general-purpose semiconductor device in the F<sup>2</sup>MC-16LX family. It is a 16-bit single-chip microcontroller ASIC (Application Specific IC). This manual explains the functions and operations of the MB90M405 Series for engineers who design products using this device.

#### How to Read This Manual

#### ■ Page Organization

A summary is given below the title of each section. A title of the main section is noted in the sub-section to recognize a current-reading section.

#### ■ Index Organization

(1) Register map index

The register map index format is similar to the I/O map and it allows search for the page explaining the bits of each register from the address, register abbreviation, register name, and resource macro name. Use the register map index at searching for the register function when designing a resource macro.

(2) Pin function index

The pin function index is similar to the explanation of the pin function and it allows serch for the block diagram of each resource macro, the explanation of the pin function, and notes from the package pin number, pin name, circuit type, and resource macro name. Use the pin function index when creating the system board, etc. (The pin function index will be provided in the next revision of this manual).

#### Organization of Notes and Checks

- **Notes** : Reference information is given here. Use this as a hint or note when using the MB90M405. This also gives a section(s) to refer.

- **Check** : Precautions when using the MB90M405 are given here. Specification restrictions, etc., are included.

# 1. GENERAL

| 1.1  | Features1-3                    |

|------|--------------------------------|

| 1.2  | Resources1-4                   |

| 1.3  | Product Lineup                 |

| 1.4  | Block Diagram1-6               |

| 1.5  | Pin Assignment1-7              |

| 1.6  | Pin Description1-8             |

| 1.7  | I/O Circuit Type 1-11          |

| 1.8  | Notes on Handling Devices 1-13 |

| 1.9  | Clock Supply Map 1-15          |

| 1.10 | Low Power Consumption Mode1-16 |

This chapter explains the features and basic specifications of the Monolith (MB90M405).

The MB90M405 Series is a general-purpose 16-bit microcontroller developed for applications requiring fluorescent lamp panel control and contains 60 high-voltage withstand output pins required for a fluorescent lamp.

As with the original F<sup>2</sup>MC-8L and F<sup>2</sup>MC-16L families, the instruction system inherits the AT architecture, and has extended high-level language interface instructions and the extended addressing modes, enhanced multiplication/division instructions (signed), and enhanced bit processing. In addition, a 32-bit accumulator enables handle long word processing.

#### 1.1 Features

- Clock:

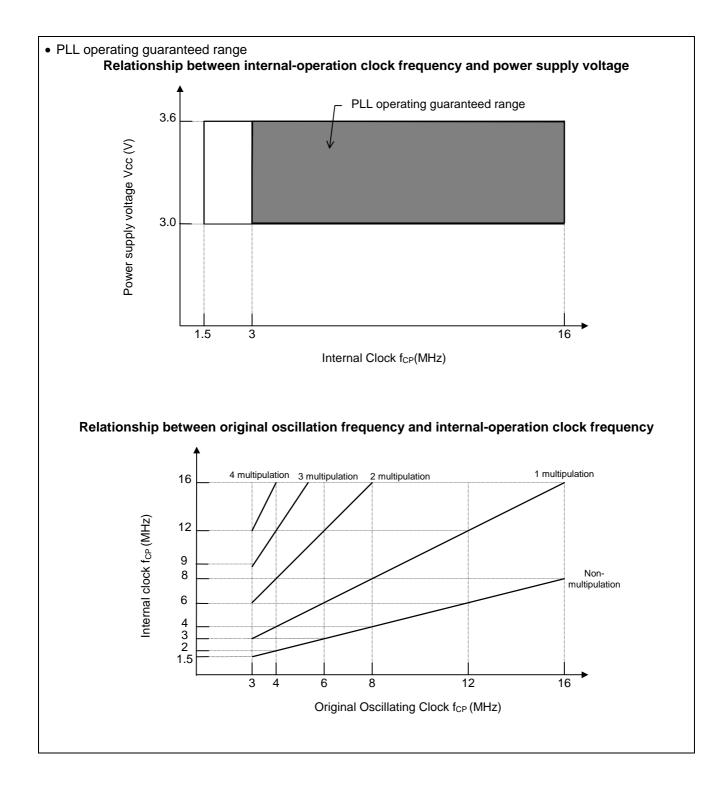

- PLL Clock multiplication circuit built-in

- Operating clock (PLL clock) generated by dividing original oscillation by 2 or by multiplying original oscillation by 1 to 4 (2.1 MHz to 16.8 MHz at original oscillation of 4.2 MHz). Can be selected.

- Minimum instruction execution time is 59.5 ns (when the original oscillation is 4.2 MHz, the PLL clock is generated by multiplying the original oscillation by 4, and Vcc = 3 V).

- It is possible to generate an external output as a clock output by dividing the original oscillation by 16, 32, 64, or 128.

- Maximum memory space: 16 Mbytes

- 24-bit addressing in memory space

- Instruction system suited for controller

- Applicable data types (bit, byte, word, long-word)

- Various addressing modes: 23 types

- High code efficiency

- High-precision operation with 32-bit accumulator

- Signed multiplication and division instructions and enhanced RETI instruction

- Powerful instruction system applicable to high-level language (C) or multitasking

- System stack pointer

- Symmetric instruction set and barrel shift instruction

- Program patch function (2-address pointer)

- Shortened execution time: 4-byte instruction queue

- Powerful interrupt function (eight programmable priority levels)

- Powerful interrupt function for 32 interrupt factors

- Data transfer function (extended intelligent I/O service function: 16 channels maximum)

- Low-power consumption (standby mode)

- Sleep mode (stops CPU operating clock)

- Pseudo-timer mode (stops everything except original oscillation and time-base timer)

- Stop mode (stops original oscillation)

- CPU Intermittent operation mode

- Package

- QFP-100 (FPT-100P-M06: 0.65 mm pin pitch)

- Process

- CMOS technology

#### 1.2 Resources

- I/O port: 26 pins maximum (All 26 pins can also serve as resource pins).

- 18-bit time-base timer: 1 channel

- Watchdog timer: 1 channel

- 16-bit reload timer: 3 channels

- 16-bit free-run timer: 1 channel

- 16-bit output compare: 1 channel

- 16-bit input capture: 2 channels

- When the count value of the 16-bit free-run timer matches the setting value of the output compare, the timer is cleared and an interrupt request is issued.

- Serial I/O: 2 channels

- UART: 2 channels

- Clock-synchronous serial transfer (I/O extended serial) can be used.

- The direction of the shift clock level can be selected arbitrarily (MSB or LSB).

- DTP/external interrupt (4 channels)

- Start extended intelligent I/O services by an external input, and generate an external interrupt.

- Delayed interrupt generation module

- A task-switching interrupt request is generated.

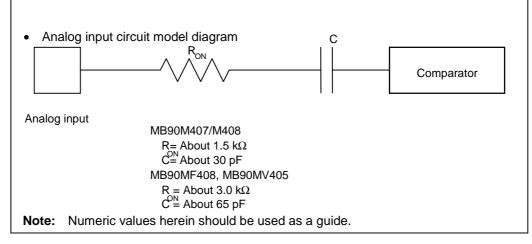

- 8-/10-bit A/D converter (16 channel)

- 8- or 10-bit resolution can be selected.

- FL controller

- Enables FL driver control. (The auto display control is performed for 32 digits max. and 59 segments max.)

- 1 to 32 digits can be set (can be set on a digit-by-digit basis).

- The dimmer can be set.

- Enables LED driver control (Auto display control is performed for 16 segments maximum).

- The auto display control can be performed for 16 segments max. at 1/2 duty.

- Timer clock divider

- The original oscillation can be divided by 32, 64, 128, or 256.

# 1.3 Product Lineup

*Table 1-1* lists the Monolith (MB90M405) series product lineup. Functions other than the ROM/RAM capacity are shared.

| Product name               | MB90MV405                                                                                                                                                                                                                                                                                            | MB90MF408                                        | MB90M408                                        | MB90M407     |  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------|--|--|--|--|

| Classification             | Evaluate                                                                                                                                                                                                                                                                                             | Flash Type ROM                                   | oduct (mask ROM)                                |              |  |  |  |  |

| ROM capacity               | Not provided                                                                                                                                                                                                                                                                                         | 128 Kbytes 96 Kbytes                             |                                                 |              |  |  |  |  |

| RAM capacity               | 4 Kbytes                                                                                                                                                                                                                                                                                             | 4 Kt                                             | oytes                                           | 4 Kbytes     |  |  |  |  |

| CPU Function               | Count of basic instructions: 351<br>Minimum instruction execution time: 59.5 ns (at original oscillation of 4.2 MHz, with<br>PLL clock generated by multiplying origina<br>oscillation by 4)<br>Addressing types: 23<br>Program patch function: 2-address pointer<br>Maximum memory space: 16 Mbytes |                                                  |                                                 |              |  |  |  |  |

| Port                       | I/O port (CMOS)                                                                                                                                                                                                                                                                                      | 26 pins (all of 26                               | ) pins also serve as res                        | source pins) |  |  |  |  |

| FL Controller              | <ul> <li>60 FL output pins can be used (Under LED control, 43 FL output pins and 17 LED control pins are required).</li> <li>Enables FL driver control and LED driver control can be performed.</li> <li>Under FL driver control, the dimmer can be set for both digits and segments.</li> </ul>     |                                                  |                                                 |              |  |  |  |  |

| Serial I/O (UART)          | Can also be used as the clock-synchronous method extended I/O serial.<br>A dedicated baud rate generator is built-in.<br>Four channels are built-in (two channels also serve as UART channels).                                                                                                      |                                                  |                                                 |              |  |  |  |  |

| 16-bit reload timer        |                                                                                                                                                                                                                                                                                                      |                                                  | or one-shot output ca<br>hree channels are buil | · ·          |  |  |  |  |

| 16-bit free-run timer      | 16-bit output compare x 1 channel (for clearing free-run timer)<br>16-bit input capture x 2 channels                                                                                                                                                                                                 |                                                  |                                                 |              |  |  |  |  |

| 8-/10-bit A/D<br>converter |                                                                                                                                                                                                                                                                                                      | 16 channels (input mu<br>time: 6.2 µs (at intern | ltiplex)<br>al operation of 16 MHz              | z)           |  |  |  |  |

| Timer clock divider        | The external input clock can be divided and output to the outside.<br>Clock division rates: 16, 32, 64, or 128 (programmable)                                                                                                                                                                        |                                                  |                                                 |              |  |  |  |  |

| External interrupt         | Four independent channels (also serve for A/D input)<br>Interrupt factor: $L \rightarrow H$ edge, $H \rightarrow L$ edge, L level, or H level                                                                                                                                                        |                                                  |                                                 |              |  |  |  |  |

| Low power consumption mode | Sleep mode, stop mode, CPU intermittent mode, or pseudo-timer mode                                                                                                                                                                                                                                   |                                                  |                                                 |              |  |  |  |  |

| Process                    | CMOS                                                                                                                                                                                                                                                                                                 |                                                  |                                                 |              |  |  |  |  |

| Package                    | PGA256                                                                                                                                                                                                                                                                                               | Q                                                | FP-100 (0.65 mm pitcl                           | h)           |  |  |  |  |

| Operating voltage          | 3.3                                                                                                                                                                                                                                                                                                  | 3 V ±0.3 V(16.8 MHz:                             | 4.2 MHz multiplied by                           | 4)           |  |  |  |  |

| Table 1-1 | MB90M405 | Series | Product | Lineup |

|-----------|----------|--------|---------|--------|

|-----------|----------|--------|---------|--------|

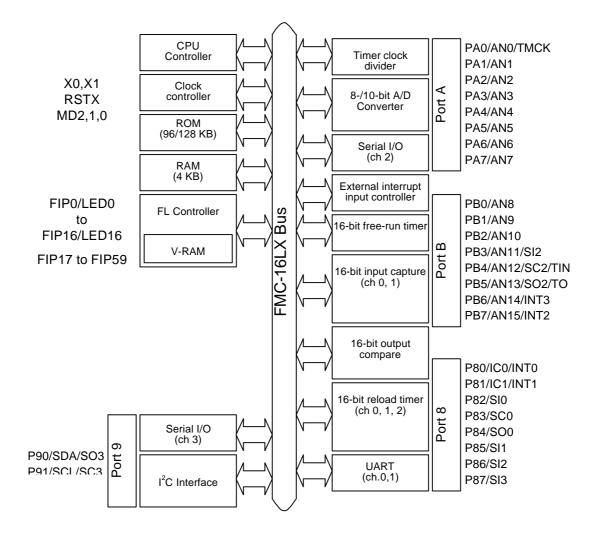

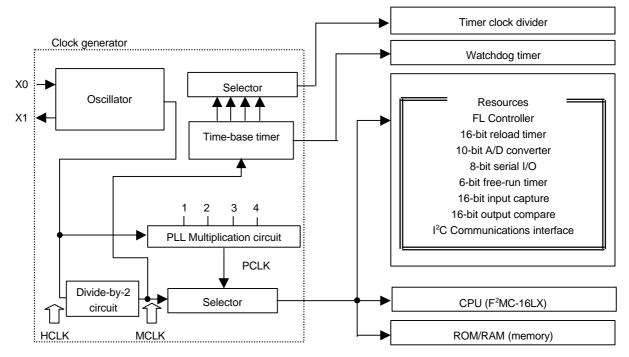

# 1.4 Block Diagram

Fig. 1.1 Block Diagram (MB90M405)

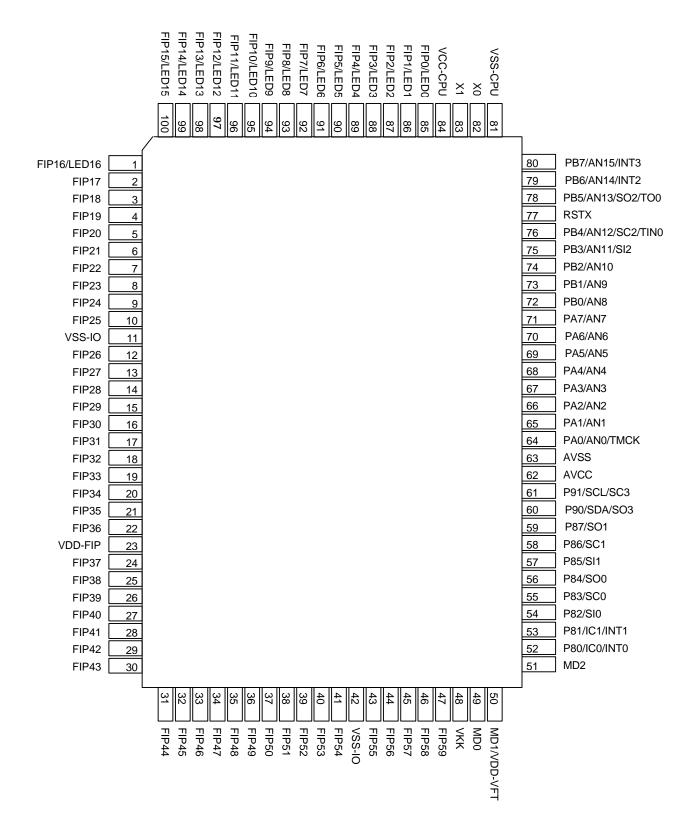

# 1.5 Pin Assignment

#### FPT-100P-M06 Pin Assignment

# 1.6 Pin Description

Tables 1-2, 1-3 and 1-4 list the pin name, function, circuit type, and reset-time state/function.

| Pin No.<br>QFP-100M06            | Pin Name       | Circuit<br>Type | State/function at reset                   | Function                                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|----------------------------------|----------------|-----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-------------------------------------------------------------------------------------------------------------------------------|

| 82, 83                           | X0, X1         | А               | Oscillation state Oscillation input pins. |                                                                                                                                                                                                             |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 77                               | RSTX           | В               | Reset input                               | External reset input pin                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | FIP0 to FIP15  |                 |                                           | This function is selected when the FL driver is enabled.                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 85 to 100                        | LED0 to LED15  |                 |                                           | This function is selected when the LED driver is enabled.                                                                                                                                                   |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 1                                | FIP16          |                 |                                           | This function is selected when the FL driver is enabled.                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| I                                | LED16          | Ŭ               | VKK Pull-down                             | This function is selected when the LED driver is enabled.                                                                                                                                                   |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 2 to 10<br>12 to 19              | FIP17 to FIP33 |                 | output                                    |                                                                                                                                                                                                             |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 20 to 22<br>24 to 41<br>43 to 47 | FIP34 to FIP59 | D               |                                           | Dedicated pins for the FL driver output.                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P80            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 52                               | IC0            |                 |                                           | External trigger input pin for input capture 0                                                                                                                                                              |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | INT0           |                 |                                           | External factor input pin for external interrupt input 0<br>This pin is only accepted when it is enabled by the EN0 bit.                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P81            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 53                               | IC1            | -               |                                           | External trigger input pin for input capture 1                                                                                                                                                              |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | INT1           |                 |                                           | External factor input pin for external interrupt input 1<br>This pin is only accepted when it is enabled by the EN1 bit.                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P82            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 54                               | SIO            |                 |                                           | Serial data input pin for serial I/O channel 0<br>This pin is always effective when channel 0 is under input operation.                                                                                     |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P83            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 55                               | SC0            |                 |                                           | Serial clock I/O pin for serial I/O channel 0<br>This pin is effective when the channel-0 clock output is enabled.                                                                                          |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P84            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 56                               | SO0            |                 |                                           |                                                                                                                                                                                                             |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | Serial data output pin for serial I/O channel 0<br>This pin is effective when the channel-0 serial data output is<br>enabled. |

|                                  | P85            |                 | Hi-Z                                      | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 57                               | SI1            | 1               |                                           |                                                                                                                                                                                                             | Serial data input pin for serial I/O channel 1<br>This pin is always effective when channel 0 is under input operation. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P86            |                 |                                           | General-purpose I/O port                                                                                                                                                                                    |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 58                               | 58 SC1         |                 |                                           | Serial clock I/O pin for serial I/O channel 1<br>This pin is effective when the channel-0 clock output is enabled.                                                                                          |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P87            |                 |                                           | This pin is a general-purpose I/O port.                                                                                                                                                                     |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 59                               | SO1            |                 |                                           | Serial data output pin for serial I/O channel 1<br>This pin is effective when the channel-0 serial data output is<br>enabled.                                                                               |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | P90            |                 | 1                                         | General-purpose I/O port (However, the N ch is open drain.)                                                                                                                                                 |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

| 60                               | SDA            | G               |                                           | Data I/O pin for the $l^2$ C interface. This function is effective when operation of the $l^2$ C interface is enabled.<br>Also, set the port output to the Hi-Z state when operating the $l^2$ C interface. |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

|                                  | SO3            |                 |                                           | Serial data output pin for serial I/O channel 3<br>This pin is effective when the channel-3 serial data output is<br>enabled.                                                                               |                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                                                                                               |

#### Table 1-2 Pin Description

# Table 1-3 Pin Description

| Pin No.<br>QFP-100M06 | Pin Name      | Circuit<br>Type | State/function at reset | Function                                                                                                                                                                                                                                        |                                                                                                                                                   |

|-----------------------|---------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | P91           |                 |                         | General-purpose I/O port (However, the N ch is open drain.)                                                                                                                                                                                     |                                                                                                                                                   |

| 61                    | SCL           | G               | Hi-Z                    | Clock I/O pin for the I <sup>2</sup> C interface<br>This function is effective when operation of the I <sup>2</sup> C interface is<br>enabled.<br>Also, set the port output to the Hi-Z state when operating the I <sup>2</sup> C<br>interface. |                                                                                                                                                   |

|                       | SC3           |                 |                         | Serial clock I/O pin for serial I/O channel 3<br>This pin is effective when the channel-3 clock output is enabled.                                                                                                                              |                                                                                                                                                   |

|                       | PA0           |                 |                         | General-purpose I/O port                                                                                                                                                                                                                        |                                                                                                                                                   |

| 64                    | AN0           |                 |                         | Analog input pin 0 for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).                                                                                                          |                                                                                                                                                   |

|                       | ТМСК          |                 |                         | Timer clock output pin<br>This pin is only effective when output is enabled. This pin is null<br>when analog input is enabled using ADER.                                                                                                       |                                                                                                                                                   |

|                       | PA1 to PB2    |                 |                         | General-purpose I/O port                                                                                                                                                                                                                        |                                                                                                                                                   |

| 65 to 74              | AN1 to AN10   |                 |                         | Analog input pins (1 to 10) for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).                                                                                                 |                                                                                                                                                   |

|                       | PB3           |                 |                         | General-purpose I/O port                                                                                                                                                                                                                        |                                                                                                                                                   |

| 75                    | AN11          |                 | Analog input            |                                                                                                                                                                                                                                                 | Analog input pin (11) for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).         |

|                       | SI2           |                 |                         | Serial data input pin for serial I/O channel 2<br>This pin is always effective when channel 2 is under input<br>operation.                                                                                                                      |                                                                                                                                                   |

|                       | PB4           |                 |                         |                                                                                                                                                                                                                                                 | General-purpose I/O port                                                                                                                          |

|                       | AN12          | F               |                         |                                                                                                                                                                                                                                                 | Analog input pin (12) for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).         |

| 76                    | SC2           |                 |                         | Serial clock I/O pin for serial I/O channel 2<br>This pin is effective when the channel-2 clock output is enabled.                                                                                                                              |                                                                                                                                                   |

|                       | TINO          |                 |                         |                                                                                                                                                                                                                                                 | External clock input pin for reload timer channel 0<br>This pin is enabled when the external clock input is effective<br>(ADER takes precedence). |

|                       | PB5           |                 |                         | General-purpose I/O port                                                                                                                                                                                                                        |                                                                                                                                                   |

|                       | AN13          |                 |                         |                                                                                                                                                                                                                                                 | Analog input pin (13) for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).         |

| 78                    | SO2           |                 |                         | Serial data output pin for serial I/O channel 2<br>This pin is effective when the channel-2 serial data output is<br>enabled.                                                                                                                   |                                                                                                                                                   |

|                       | TO0           |                 |                         | External event output pin for reload timer channel 0<br>This pin is effective when the external event output is enabled<br>(ADER takes precedence).                                                                                             |                                                                                                                                                   |

|                       | PB6 and PB7   | 1               |                         | General-purpose I/O port                                                                                                                                                                                                                        |                                                                                                                                                   |

| 79, 80                | AN14 and AN15 |                 |                         | Analog input pins (14, 15) for the A/D converter<br>This function is effective when the analog input specification is<br>enabled (using ADER).                                                                                                  |                                                                                                                                                   |

|                       | INT2 and INT3 |                 |                         | External factor input pins for external interrupt inputs 2 and 3<br>These pins are accepted only when they are enabled using the<br>EN2 bit and the EN3 bit.                                                                                    |                                                                                                                                                   |

| 62                    | AVCC          | н               |                         | Vcc power input pin for the analog macro                                                                                                                                                                                                        |                                                                                                                                                   |

| 63                    | AVSS          |                 | Power input             | Vss power input pin for the analog macro                                                                                                                                                                                                        |                                                                                                                                                   |

| 48                    | VKK           |                 |                         | Power pin on the pull-down side at high-voltage withstand output.                                                                                                                                                                               |                                                                                                                                                   |

| Table 1-4 | Pin Descript | ion |

|-----------|--------------|-----|

|-----------|--------------|-----|

| Pin No.    | Din Norre           | Circuit | State/function at | Function                                                                                                                                            |                                                                                                                  |  |  |

|------------|---------------------|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| QFP-100M06 | QFP-100M06 Pin Name |         | reset             | Function                                                                                                                                            |                                                                                                                  |  |  |

| 49         | MD0                 |         |                   | Input pin for specifying the operating mode<br>Connect this pin to Vcc. Also, always switch this pin to Vss at boot<br>programming to flash memory. |                                                                                                                  |  |  |

| 50         | MD1/VDD-VFT         | В       | Mode pin          | Mode pin                                                                                                                                            | Input pin for specifying the operating mode<br>Connect this pin to Vcc. This pin also serves as the VDD-VFT pin. |  |  |

| 51         | MD2                 |         |                   |                                                                                                                                                     |                                                                                                                  |  |  |

| 11, 42     | VSS-IO              |         |                   | Power (0 V: GND) input pins for I/O                                                                                                                 |                                                                                                                  |  |  |

| 23         | VDD-FIP             |         | Power input       | Power (3 V: Vcc) input pin for the FIP                                                                                                              |                                                                                                                  |  |  |

| 81         | VSS-CPU             | _       |                   | Power (0 V: GND) input pin for the controller                                                                                                       |                                                                                                                  |  |  |

| 84         | VCC-CPU             |         |                   | Power (3 V: Vcc) input pin for the controller                                                                                                       |                                                                                                                  |  |  |

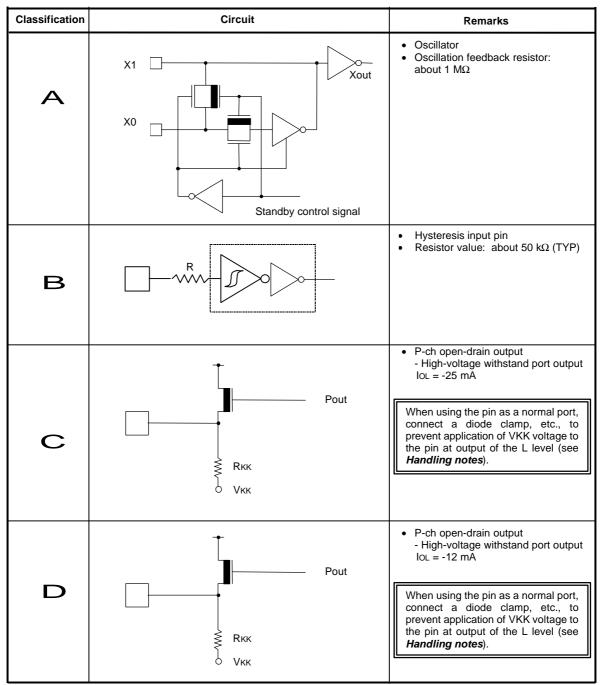

# 1.7 I/O Circuit Type

Tables **1-5** and **1-6** show the circuit type for each pin.

| Classification | Circuit                                                                     | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E              | Pout<br>Pout<br>Nout<br>R<br>Hysteresis input<br>Standby control            | <ul> <li>CMOS hysteresis I/O pin</li> <li>CMOS-level output</li> <li>CMOS Hysteresis input<br/>(The input cutoff function is<br/>provided in the standby mode.)<br/>IOL = 4 mA</li> </ul>                                                                                                                                                                                                                                  |

| Ľ              | Pout<br>Pout<br>Nout<br>Hysteresis input<br>Standby control<br>Analog input | <ul> <li>Analog/CMOS hysteresis I/O pin</li> <li>CMOS-level output</li> <li>CMOS hysteresis input<br/>(The input cutoff function is provided<br/>in the standby mode.)</li> <li>Analog input<br/>(Analog input is effective when the<br/>corresponding bit of ADER is 1.)<br/>IOL = 4 mA</li> </ul>                                                                                                                        |

| Ű              | R<br>R<br>Hysteresis input<br>Standby control                               | <ul> <li>N-ch open drain output</li> <li>CMOS Level hysteresis input<br/>(The input cutoff function is<br/>provided in the standby mode.)</li> <li>Unlike the CMOS I/O pin, there is no<br/>P-ch transistor at this pin.<br/>Consequently, even when an<br/>external voltage is applied to this pin<br/>with the power to the device set to<br/>OFF, no current flows to the device<br/>power (Vcc-IO/Vcc-CPU).</li> </ul> |

| н              |                                                                             | Analog power input protector                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 1-6 I/O Circuits

# 1.8 Notes on Handling Devices

(1) Be careful not to exceed the maximum rated voltage (Prevention of latch up).

For a CMOS IC, latch-up may occur if a voltage higher than Vcc or a voltage lower than Vss is applied to the I/O pin other than medium-/high-voltage withstand I/O pins, or when a voltage that exceeds the rated voltage is applied between Vcc and Vss.

Latch up rapidly increases the power current, and the device may be destroyed by heat.

When using the device, take care not to exceed the maximum rating. Also, take care that the analog power (AVcc) and the analog input do not exceed the digital power (Vcc) when turning the AC/DC power on or off. (2) Design the device so the supply voltage is as stable as possible.

A sudden change in the power voltage may cause a malfunction even within the operating assurance range of the VCC power supply voltage. For safety, the VCC ripple (p-p) of the commercial frequency (50/60 MHz) must be 10% or less of the standard VCC value, and the transient fluctuation at instantaneous power switching must be 0.1 V/ms or less. Also, take countermeasures to power noise, etc.

(3) Notes at power-on

The voltage rise time at power-on must be 50  $\mu$ s or more (0.2 to 2.7 V).

(4) Setting unused input pins

Leaving unused input pins open may cause a malfunction. Therefore, these pins must be set to the pullup or pull-down state.

(5) Handling of power pins for A/D converter

Even when the A/D converter is not used, connect the pins so that the following relationships are established: AVcc = Vcc, AVss = Vss.

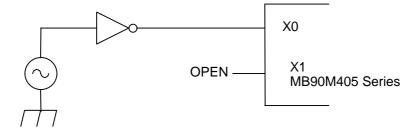

(6) Notes on using external clock

Even when an external clock is used, the oscillation stabilization wait time is required at the power-on reset or the cancellation of the stop mode. In this case, drive the X0 pin only and leave the X1 pin open.

#### Example of using external clock

(7) Power pins

When two or more Vcc pins and Vss pins are provided, pins are designed to be at the same electric potential are internally connected to the device to prevent malfunctions such as latch-up. However, always connect all same electric potential pins to power and ground outside the device to prevent decrease of extraneous and radiation the malfunction of the strobe signal due to a ground level rise, and follow the standards on total output current, etc. Also, consider to connecting the pins to Vcc and Vss of this device at the lowest possible impedance from the current supply source (It is recommended to connect a bypass capacitor of about 0.1  $\mu$ F of the device between Vcc and Vss).

#### (8) Application sequence for power analog inputs for A/D converter

Apply the digital power (Vcc) first, and then apply the power (AVcc) and analog inputs (AN0 to AN15) for the A/D converter. Disconnect the power and analog inputs for the A/D converter first, and then disconnect the digital power (Vcc).

Also, do not allow the input voltage to exceed AVcc even when using a pin shared with an analog input as an input port (Simultaneous application and disconnection of analog power and digital power is allowed).

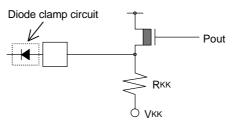

(9) Output of high-voltage withstand output pin (circuit type C or D) When the high-voltage withstand output pin (circuit type is C or D) is used as an ordinary output port, the port outputs the VKK pin voltage pull-down value at the L level output. In this case, the VKK pin level voltage is applied to the external circuit, so it is recommended to add a diode clamp circuit as shown in the figure below.

# 1.9 Clock Supply Map

The clock supply map for this device (Monolith: MB90M405) is shown below.

HCLK: Oscillation clock

MCLK: Main clock (operating clock: clock generated by dividing oscillation clock by 2)

PCLK: PLL clock

# 1.10

This section provides an overview of the low power consumption mode.

The onolith (MB90M405) has the following modes that stop various functions and clocks

#### Chapter 4.

#### • Relationships between operating modes and power

| Operating mode | Main clock | PLL Clock | CPU      | Resources | Timer clock |

|----------------|------------|-----------|----------|-----------|-------------|

| PLL Run        | Operates   | Operates  | Operates | Operates  | Operates    |

| Main Run       | Operates   | Stops     | Operates | Operates  | Operates    |

| PLL Sleep      | Operates   | Operates  | Stops    | Operates* | Operates    |

| Main sleep     | Operates   | Stops     | Stops    | Operates* | Operates    |

| Pseudo-time    | Operates   | Stops     | Stops    | Stops     | Operates    |

| Stop           | Stops      | Stops     | Stops    | Stops     | Stops       |

In the above table, the power consumption decreases as the operating mode goes down from the top of the table.

In the PLL Run mode, operation is performed on the PCLK generated by multiplying the original oscillation by 1 to 4. In the Main Run mode, operation is performed on the MCLK generated by dividing the original oscillation by 2.

\*: In the sleep mode, the CPU stops, so resources cannot be accessed from the CPU.

Preliminary Version 1

# Data sheet**MB90M405 Series**Electric Specification Table

#### Electrical Characteristics

#### 1. Absolute Maximum Rating

| Devenueter                               | Cumhal                | Rated                | Value                 | 11   | Domoska                                                                  |

|------------------------------------------|-----------------------|----------------------|-----------------------|------|--------------------------------------------------------------------------|

| Parameter                                | Symbol                | Min.                 | Max.                  | Unit | Remarks                                                                  |

|                                          | V <sub>CC-CPU</sub>   | V <sub>SS</sub> -0.3 | V <sub>SS</sub> + 4.0 | V    | Power supply pin for control circuit                                     |

|                                          | V <sub>DD-FIP</sub>   | $V_{SS} - 0.3$       | V <sub>SS</sub> + 4.0 | V    | Power supply pin for FIP                                                 |

| Power supply voltage                     | AV <sub>CC</sub>      | $V_{SS} - 0.3$       | V <sub>SS</sub> + 4.0 | V    | $Vcc \ge AVcc^{*1}$                                                      |

|                                          | Vĸĸ                   | V <sub>CC</sub> – 45 | V <sub>CC</sub> + 0.3 | V    | Pull-down side power supply pin for high voltage resistance output.      |

|                                          | Vi                    | Vss – 0.3            | Vss + 4.0             | V    | *2                                                                       |

| Input voltage                            | • 12                  | Vss – 0.3            | Vss + 5.5             | V    | *3                                                                       |

| Output valtage                           | Vo                    | Vss – 0.3            | Vss + 4.0             | V    | *2                                                                       |

| Output voltage                           | V <sub>O2</sub>       | Vss – 0.3            | Vss + 5.5             | V    | * (Open drain output)                                                    |

| "L" level max. output current            | I <sub>OL</sub>       | —                    | 15                    | mA   | *4, *5                                                                   |

| "L" level avg. output current            | Iolav                 | _                    | 4                     | mA   | Average value (Operating current $\times$ Operating rate) $^{\star 5}$   |

| "L" level max. overall output current    | Σl <sub>OL</sub>      | _                    | 100                   | mA   | *5                                                                       |

| "L" level avg. overall output<br>current | ΣΙ <sub>ΟLAV</sub>    | _                    | 50                    | mA   | Average value (Operating current $\times$ Operating rate) * <sup>5</sup> |

|                                          | I <sub>OH</sub>       | _                    | -15                   | mA   | * <sup>4</sup> * <sup>5</sup>                                            |

| "H" level max. output current            | I <sub>OHFIP1</sub>   | _                    | -27                   | mA   | FIP00 to FIP33 pins                                                      |

|                                          | I <sub>OHFIP2</sub>   | —                    | -14                   | mA   | FIP34 to FIP59 plns                                                      |

| "H" level avg. output current            | I <sub>OHAV</sub>     | _                    | -4                    | mA   | Average value (Operating current $\times$ Operating rate) $^{\star5}$    |

| "H" level max. overall output current    | Σl <sub>OH</sub>      | _                    | -100                  | mA   | *5                                                                       |

| "H" level avg. overall output            | ΣΙ <sub>ΟΗΑV</sub>    | _                    | -50                   | mA   | Average value (Operating current $\times$ Operating rate) $*^5$          |

| current                                  | ΣΙ <sub>ΟΗΓΙΡΑΥ</sub> | _                    | -180                  | mA   | Average value (Operating current $\times$ Operating rate) $^{\ast6}$     |

|                                          | P <sub>D_CPU</sub>    | _                    | 300                   | mW   | For CPU_Chip individual operation                                        |

| Power consumption                        | P <sub>D_FL</sub>     |                      | 1176                  | mW   | For FL_Chip individual output operation                                  |

| Operating temperature                    | T <sub>A</sub>        | -40                  | +85                   | °C   |                                                                          |

| Storage temperature                      | T <sub>STG</sub>      | -55                  | +150                  | °C   |                                                                          |

$(V_{SS-CPU} = V_{SS-IO} = AVss = 0.0 V)$

- \*1:  $AV_{CC}$  should not exceed  $V_{CC}$  when turning on the power supply.

- \*2: V<sub>I</sub> and V<sub>O</sub> should not exceed V<sub>CC</sub> + 0.3 V.

- \*3: The 5 V withstandable voltage pin for I<sup>2</sup>C. Applies to P90/SDA, P91/SCL only.

- \*4: The maximum output current is standard at the peak value of the corresponding 1 pin.

- \*5: Excludes currents on the FIP00 to FIP59 pins.

- \*6: FIP00 to FIP59 pins are targeted.

- **Cautions:** 1. The V<sub>CC</sub> specification in the table means:  $V_{DD-FIP} = V_{DD-VFT} = V_{CC-CPU}$ . Use with the same power supply level as the three pins described above. Also,  $V_{SS}$  means:  $V_{SS-IO} = V_{SS-CPU}$ . Connect this pin to the GND.

- 2. This device contains circuity to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltage to this high impedance circuit.

# 2. Recommended Conditions

| $(V_{SS-IO} = V_{SS-CPU} = AVss = 0.0 V)$ |

|-------------------------------------------|

|-------------------------------------------|

| Desemptor                  | Symbol              | Rated value |           | Unit | Demarka                                                                                  |

|----------------------------|---------------------|-------------|-----------|------|------------------------------------------------------------------------------------------|

| Parameter                  | Symbol              | Min.        | Max.      | Unit | Remarks                                                                                  |

|                            | V <sub>CC-CPU</sub> | 3.0         | 3.6       | V    | Under normal operation                                                                   |

| Power supply<br>voltage    | V <sub>DD-FIP</sub> | 3.0         | 3.6       | V    | Under normal operation                                                                   |

| Ũ                          | Vcc                 | 2.5         | 3.6       | V    | Maintains status of stop operation                                                       |

|                            | VIHS                | 0.8 Vcc     | Vcc + 0.3 | V    | CMOS Hysterisis input pins other than I <sup>2</sup> C                                   |

| "H" level input voltage    | V <sub>IHS2</sub>   | 0.8 Vcc     | 5.8       | V    | CMOS Hysterisis input pins of I <sup>2</sup> C (5 V withstandable voltage)* <sup>1</sup> |

|                            | V <sub>IHM</sub>    | Vcc – 0.3   | Vcc + 0.3 | V    | MD pin input                                                                             |

|                            | V <sub>ILS</sub>    | Vss – 0.3   | 0.2 Vcc   | V    | CMOS Hysterisis input pins other than I <sup>2</sup> C                                   |

| "L" level input<br>voltage | V <sub>ILS2</sub>   | Vss – 0.3   | 0.2 Vcc   | V    | CMOS Hysterisis input pins of I <sup>2</sup> C (5 V withstandable voltage)* <sup>1</sup> |

|                            | VILM                | Vss – 0.3   | Vss + 0.3 | V    | MD pin input                                                                             |

| Operation<br>temperature   | T <sub>A</sub>      | -40         | +85       | °C   |                                                                                          |

\*1: On the 1st ES product of MB90MF408, the withstandable voltage is 3 V (can be used up to 4.5 V at the test lab level).

**Caution:** The V<sub>CC</sub> specification in the table means:  $V_{DD-FIP} = V_{DD-VFT} = V_{CC-CPU}$ . Use with the same power supply level as the three pins described above. Also,  $V_{SS}$  means:  $V_{SS-IO} = V_{SS - CPU}$ . Connect this pin to the GND.

# 3. DC Specifications

| Parameter                  |                  |                                               | $\frac{1}{DD-FIP} = V_{DD-VFT} = V_{CC-CPU}$                                          | Rated value   |             |     |      |                                                                            |

|----------------------------|------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|---------------|-------------|-----|------|----------------------------------------------------------------------------|

|                            | Symbol           | Pin                                           | Test Condition                                                                        | Min.          | Typ. Max.   |     | Unit | Remarks                                                                    |

| Output H<br>voltage        | V <sub>OH5</sub> | FIP00 to                                      | V <sub>CC</sub> = 3.3 V<br>I <sub>OH5</sub> = -23 mA                                  | Vcc –<br>2.5  | _           | _   | V    |                                                                            |

|                            | V <sub>OH4</sub> | FIP33                                         | V <sub>CC</sub> = 3.3 V<br>I <sub>OH4</sub> = -12 mA                                  | Vcc –<br>1.3  | _           | _   | V    |                                                                            |

|                            | V <sub>OH3</sub> | FIP34 to                                      | V <sub>CC</sub> = 3.3 V<br>I <sub>OH3</sub> = -12 mA                                  | Vccv –<br>2.0 | _           | _   | V    |                                                                            |

|                            | V <sub>OH2</sub> | FIP59                                         | V <sub>CC</sub> = 3.3 V<br>I <sub>OH2</sub> = -5 mA                                   | Vcc –<br>1.0  | _           | _   | V    |                                                                            |

|                            | V <sub>OH1</sub> | SDA/SCL                                       | $I_{OH1} = -4 \text{ mA}$                                                             | _             |             | 5.5 | V    | Open drain pin *                                                           |

|                            | Vоно             | All output<br>pins other<br>than the<br>above | I <sub>OH</sub> = -2.0 mA                                                             | Vcc –<br>0.5  | Vcc-<br>0.3 | _   | v    |                                                                            |

|                            | V <sub>OL1</sub> | SDA/SCL                                       | I <sub>OL</sub> = 15 mA                                                               | _             | 0.5         | 0.8 | V    |                                                                            |

| Output L<br>voltage        |                  |                                               | I <sub>OL</sub> = 2.0 mA                                                              |               | 0.2         | 0.4 | v    |                                                                            |

| Input leak<br>current      | I⊫               | Input pins<br>other than<br>FIP00-59          | $V_{CC} = 3.0 V$<br>( $V_{S.} < V_{I} < V_{CC}$ )                                     | -5            | -1          | 5   | μA   |                                                                            |

| Output leak<br>current     | I <sub>LO3</sub> | FIP00 to<br>FIP33                             | $V_{CC} = 3.3 V$<br>( $V_{CC} - 43 < V_{I} < V_{CC}$ )                                | _             | _           | 20  | μA   |                                                                            |

|                            | I <sub>LO2</sub> | FIP34 to<br>FIP59                             | V <sub>CC</sub> = 3.3 V<br>(V <sub>CC</sub> - 43 <v<sub>I&lt; V<sub>CC</sub>)</v<sub> | —             | _           | 10  | μA   |                                                                            |

| Power<br>supply<br>current | Icc              | Vcc                                           | Vcc = 3.3 V, and<br>internal operation at<br>16 MHz, and normal<br>operation          | _             | 32          | 40  | mA   | MB90M407/8<br>(argeted<br>standard<br>values)* <sup>1</sup>                |

|                            |                  |                                               | Vcc = 3.3 V, and<br>internal operation at<br>16 MHz, and A/D<br>operation             | _             | 37          | 45  | mA   | MB90M407/8<br>(targeted<br>standard<br>values)* <sup>1</sup>               |

|                            |                  |                                               | Vcc = 3.3 V, and<br>internal operation at<br>16 MHz, and normal<br>operation          | _             | 40          | 50  | mA   | MB90MF408<br>MB90MV405 (F<br>targeted<br>standard<br>values)*1             |

|                            |                  |                                               | Vcc = 3.3 V, and<br>internal operation at<br>16 MHz, and A/D<br>operation             | _             | 45          | 55  | mA   | MB90MF408<br>MB90MV405<br>(F targeted<br>standard<br>values)* <sup>1</sup> |

|                            |                  |                                               | Flash<br>programming/erasing                                                          | —             | 40          | 50  | mA   | MB90MF408                                                                  |

|                            | I <sub>CCS</sub> |                                               | Vcc = 3.3 V, and<br>internal operation at<br>16 MHz, and sleep<br>operation           | _             | 15          | 20  | mA   | *1                                                                         |

(Continue)

(Continued)

| Parameter             | Symbol           | Pin            | Test Condition                               | Rated value |      |      | Unit | Remarks                          |

|-----------------------|------------------|----------------|----------------------------------------------|-------------|------|------|------|----------------------------------|

| Farameter             | Symbol           | FIII           | Test Condition                               | Min.        | Тур. | Max. | Unit | Reindiks                         |

| Power supply current  | Іссн             |                | $T_A = +25^{\circ}C$ , and operation stopped | _           | 15   | 20   | μΑ   | (Targeted<br>standard<br>values) |

| Pull-up<br>resistor   | R <sub>UP</sub>  | RSTX           | _                                            | 20          | 65   | 200  | kΩ   |                                  |

| Pull-down<br>resistor | R <sub>DW1</sub> | MD2            | —                                            | 20          | 65   | 200  | kΩ   |                                  |

|                       | R <sub>DW1</sub> | FIP00 to FIP59 | When there are settings                      | 80          | 120  | 160  | kΩ   |                                  |

- \*1: Current values that are specified do not include the consumption current on the high withstandable voltage pins. They indicate the consumption current internally on the circuit.

- \*2: On the 1st ES product of MB90MF408, the Max. standard value is 3.6 V (can be used up to 4.5 V at the test lab level).

- **Notes:** 1. The V<sub>CC</sub> specification in the table means:  $V_{DD-FIP} = V_{DD-VFT} = V_{CC-CPU}$ . Use with the same power supply level as the three pins described above. Also,  $V_{SS}$  means:  $V_{SS-IO} = V_{SS CPU}$ . Connect this pin to the GND.