# FUJITSU

# MB86614A

# IEEE 1394 SERIAL BUS CONTROLLER (400Mbps)

# **SPECIFICA TION**

Provisional Edition 3.1

#### 1.1. Overview

This section will explain the outline of the MB86614A.

Fujitsu MB86614 is a high performance 1394 serial bus controller device conforming to IEEE 1394 standard (IEEE std 1394-1995), and a part of P1394a draft. It has two 1394 interface ports with differential transceiver and comparator for the network under 1394 cable circumstance. The 1394 data rate achieves maximum 400Mbps.

The MB86614 device integrates both physical - layer block and link - layer block into a single - chip to realize the down - sizing and low power consumption for 1394 serial bus applications.

The device has a 16-bit Asynchronous data port, can automatically separates the header section from the data section and packetizes it for the continuity of data transfer.

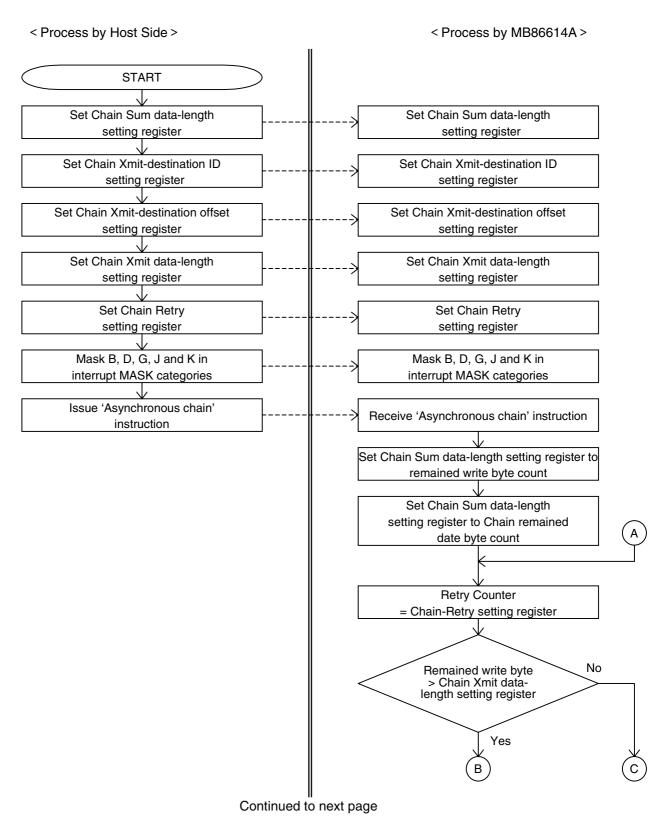

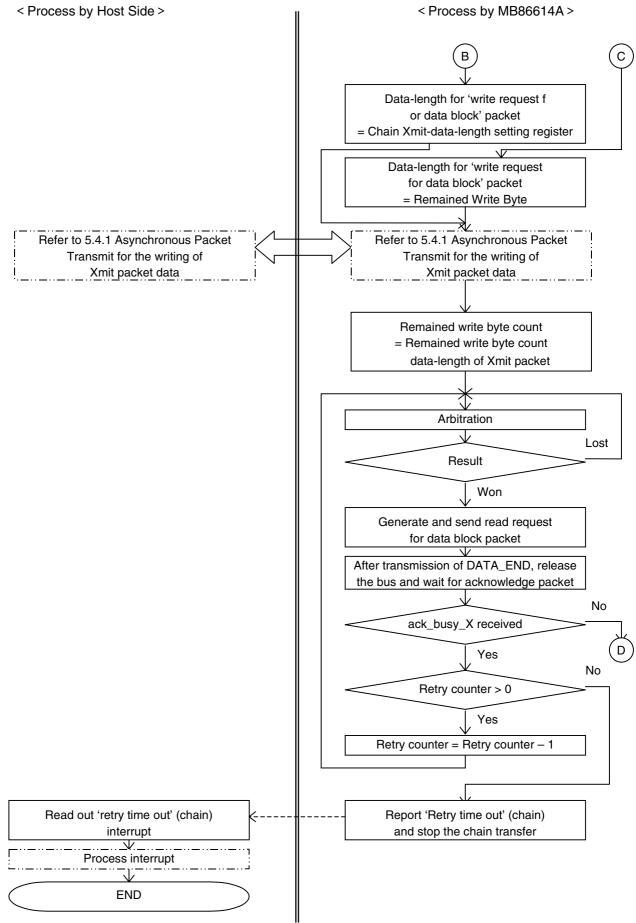

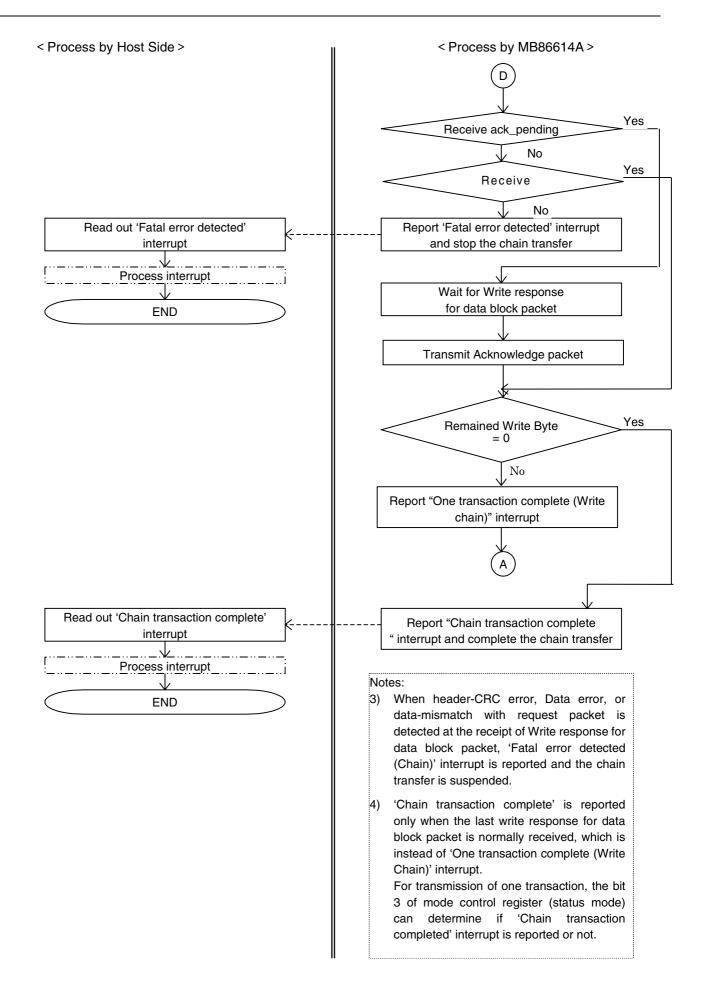

The device also has the Write request/Read request Chain functions to improve the performance of the system.

The MB86614A has a Cycle timer resister in it to realize the Cycle master function.

The device can run as a repeater node with cable power supply when the system power is turned off.

#### 1.2. Features

This section will explain the features of the MB86614A.

• Complies with IEEE 1394 high-performance serial bus standard (IEEE std 1394-1995) and a part of P1394a draft

Automatic generation and correspondence of Short Bus reset Automatic response at Ping packet transmission/receive

- Integrates Physical layer and Link layer into a single-chip

- 2 cable ports

- 100/200/400Mbps data transfer speed

- +3.3V Single Power Supply (5V I/F for digital input)

- Internal clock generation by on-chip PLL

- Low power consumption and forced sleep state with instruction from MPU

- Automatic separation of received header from data and their packetization for transmission

- Cycle master function

- 32-bit CRC generation & check

- General-purpose system interface ports (16-bit MPU/DMA common bus interface)

- Write request/Readrequest Chain transfer functions

- Supports 6-pin cable

- Package: 80 Pin Plastic LQFP, 112 pin plastic Fine pitch BGA (FBGA)

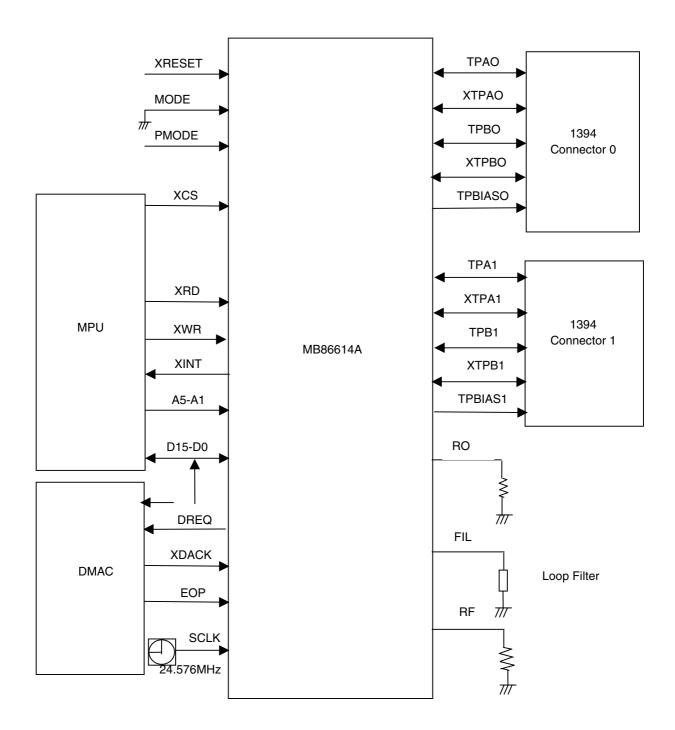

# 1.3. Block Diagram

This section will show the block diagram of the MB86614A.

Fig. 1.1 Block Diagram

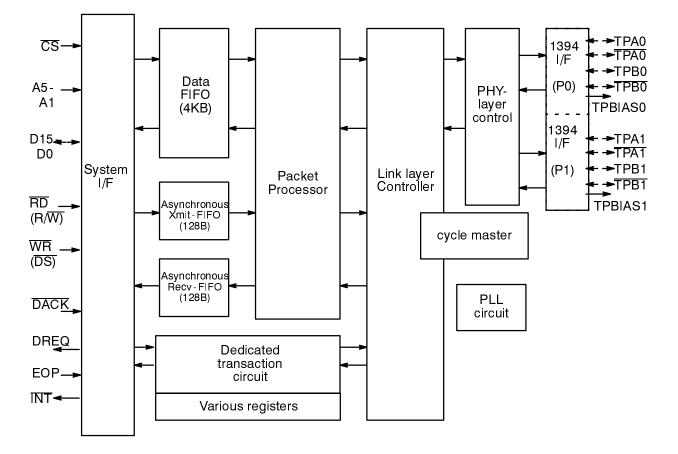

# 1.4. Outline of Each Block Function

<Physical layer>

- Supports asynchronous transfer under IEEE 1394 cable circumstance

- Maximum data transfer speed is 393.216Mbps.

- Two ports for analog transceiver/receiver, with bus status monitor, initialization, speed signaling, arbitration and encode/decode functions for data transmission/reception.

#### <Link layer>

- Controls generation and transfer of standard packet in compliance with IEEE 1394

- Generates and checks 32-bits CRC for data and header

- Incorporates 32-bits cycle timer register and cycle master function

<Transmission/Reception FIFO>

- Incorporates a 4KB Transmit/Receive FIFO (for asynchronous transmit, bank switching 1, 2, or 4 available) for asynchronous data.

- Incorporates two 128B FIFOs for independent asynchronous transmit and receive.

<Packet Process>

- For transmission, it packetizes the header, data, and CRC sections. CRC is automatically generated and added.

- For reception, it isolates the bus packet into the header and data sections, and discards the CRC section.

<Various Registers>

• This section is composed of the LSI control registers, 1394 parameter setting registers, and so on.

<PLL circuit>

• Generates internal operation clock of 49.152MHz and transfer clock of 393.216MHz. The reference clock applied is 24.576MHz.

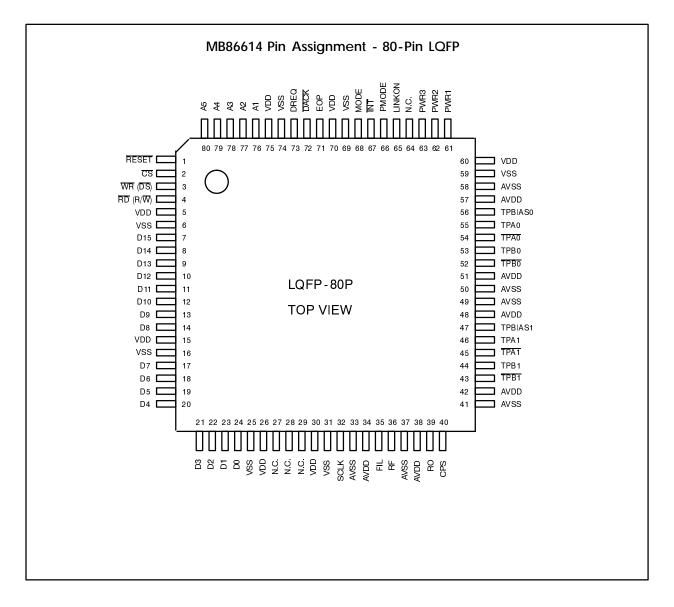

#### 1.5. Pin Assignment

The figure below shows the pin assignment of MB86614A for 112-Pin FBGA-112.

| 0       |

|---------|

| FUJITSU |

| А                                          | В               | С               | D               | Е                | F                | G                | н               | J                | к                | L                |

|--------------------------------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|

| N.C.                                       | N.C.            | N.C.            | N.C.            | TPA0             | TPB0             | AV <sub>DD</sub> | TPB1            | N.C.             | N.C.             | N.C.             |

| N.C.                                       | PWR1            | V <sub>DD</sub> | V <sub>SS</sub> | TPBIASC          | TPB0             | AV <sub>SS</sub> | TPA1            | AV <sub>DD</sub> | AV <sub>SS</sub> | N.C.             |

| N.C.                                       | PWR2            | PWR3            | N.C.            | AV <sub>SS</sub> | TPA0             | AV <sub>SS</sub> | TPA1            | TPB1             | CPS              | N.C.             |

| N.C.                                       | LINKON          | N.C.            | PMODE           | N.C.             | AV <sub>DD</sub> | AV <sub>DD</sub> | TPBIAS1         | N.C.             | AV <sub>DD</sub> | AV <sub>SS</sub> |

| INT                                        | MODE            | V <sub>SS</sub> | V <sub>DD</sub> | F                | BGA-12           |                  | R0              | RF               | AV <sub>DD</sub> | AV <sub>SS</sub> |

| EOP                                        | DACK            | DREQ            | A1              |                  |                  |                  | FIL             | N.C.             | SCLK             | V <sub>SS</sub>  |

| V <sub>SS</sub>                            | V <sub>DD</sub> | A2              | A4              |                  |                  | vv               | V <sub>DD</sub> | N.C.             | N.C.             | N.C.             |

| N.C.                                       | A3              | N.C.            | V <sub>SS</sub> | D12              | V <sub>SS</sub>  | D5               | V <sub>DD</sub> | V <sub>SS</sub>  | D0               | N.C.             |

| N.C.                                       | A5              | WR              | V <sub>DD</sub> | D13              | D9               | D7               | N.C.            | D1               | D2               | N.C.             |

| N.C.                                       | RESET           | cs              | RD              | D14              | D10              | V <sub>DD</sub>  | D6              | D4               | D3               | N.C.             |

| N.C.                                       | N.C.            | N.C.            | N.C.            | D15              | D11              | D8               | N.C.            | N.C.             | N.C.             | N.C.             |

| N.C. N.C. N.C. D15 D11 D8 N.C. N.C. N.C. 1 |                 |                 |                 |                  |                  |                  |                 |                  |                  |                  |

FUĴITSU

#### 1.6. Pin List

This section will show the pin assignment of MB86614A.

#### 1.6.1. 80-Pin LQFP

The pin list for 80-Pin LQFP will be shown below.

| Pin | I/O  | 80-MPU I/F Mode | 68-MPU I/F Mode | Pin | I/O  | 80-MPU I/F Mode  | 68-MPU I/F Mode  |

|-----|------|-----------------|-----------------|-----|------|------------------|------------------|

| No. |      | Pin Name        | Pin Name        | No. |      | Pin Name         | Pin Name         |

| 1   | ID   | RESET           | RESET           | 24  | ID/O | D0               | D0               |

| 2   | ID   | CS              | cs              | 25  | -    | V <sub>SS</sub>  | V <sub>SS</sub>  |

| 3   | ID   | WR              | DS              | 26  | -    | V <sub>DD</sub>  | V <sub>DD</sub>  |

| 4   | ID   | RD              | R∕W             | 27  | -    | N.C.             | N.C.             |

| 5   | -    | V <sub>DD</sub> | V <sub>DD</sub> | 28  | -    | N.C.             | N.C.             |

| 6   | -    | $V_{SS}$        | V <sub>SS</sub> | 29  | -    | N.C.             | N.C.             |

| 7   | ID/O | D15             | D15             | 30  | -    | V <sub>DD</sub>  | V <sub>DD</sub>  |

| 8   | ID/O | D14             | D14             | 31  | -    | V <sub>SS</sub>  | V <sub>SS</sub>  |

| 9   | ID/O | D13             | D13             | 32  | ID   | SCLK             | SCLK             |

| 10  | ID/O | D12             | D12             | 33  | -    | AV <sub>SS</sub> | AV <sub>SS</sub> |

| 11  | ID/O | D11             | D11             | 34  | -    | AV <sub>DD</sub> | AV <sub>DD</sub> |

| 12  | ID/O | D10             | D10             | 35  | 0    | FIL              | FIL              |

| 13  | ID/O | D9              | D9              | 36  | 0    | RF               | RF               |

| 14  | ID/O | D8              | D8              | 37  | -    | AV <sub>SS</sub> | AV <sub>SS</sub> |

| 15  | -    | V <sub>DD</sub> | V <sub>DD</sub> | 38  | -    | AV <sub>DD</sub> | AV <sub>DD</sub> |

| 16  | -    | V <sub>SS</sub> | V <sub>SS</sub> | 39  | 0    | R0               | R0               |

| 17  | ID/O | D7              | D7              | 40  | I    | CPS              | CPS              |

| 18  | ID/O | D6              | D6              | 41  | -    | AV <sub>SS</sub> | AV <sub>SS</sub> |

| 19  | ID/O | D5              | D5              | 42  | -    | AV <sub>DD</sub> | AV <sub>DD</sub> |

| 20  | ID/O | D4              | D4              | 43  | I/O  | TPB1             | TPB1             |

| 21  | ID/O | D3              | D3              | 44  | I/O  | TPB1             | TPB1             |

| 22  | ID/O | D2              | D2              | 45  | I/O  | TPA1             | TPA1             |

| 23  | ID/O | D1              | D1              | 46  | I/O  | TPA1             | TPA1             |

|     |      |                 |                 |     |      |                  | (Continued)      |

(Continued)

| Pin | I/O | 80-MPU I/F Mode  | 68-MPU I/F Mode  | Pin | I/O   | 80-MPU I/F Mode             | 68-MPU I/F Mode     |

|-----|-----|------------------|------------------|-----|-------|-----------------------------|---------------------|

| No. |     | Pin Name         | Pin Name         | No. |       | Pin Name                    | Pin Name            |

| 47  | 0   | TPBIAS1          | TPBIAS1          | 70  | -     | V <sub>DD</sub>             | V <sub>DD</sub>     |

| 48  | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 71  | ID    | EOP                         | EOP                 |

| 49  | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 72  | ID    | DACK                        | DACK                |

| 50  | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 73  | ID    | DREQ                        | DREQ                |

| 51  | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 74  | -     | V <sub>SS</sub>             | V <sub>SS</sub>     |

| 52  | I/O | TPB0             | TPB0             | 75  | -     | V <sub>DD</sub>             | V <sub>DD</sub>     |

| 53  | I/O | TPB0             | TPB0             | 76  | ID    | A1                          | A1                  |

| 54  | I/O | TPA0             | TPA0             | 77  | ID    | A2                          | A2                  |

| 55  | I/O | TPA0             | TPA0             | 78  | ID    | A3                          | A3                  |

| 56  | 0   | TPB AS0          | TPBIAS0          | 79  | ID    | A4                          | A4                  |

| 57  | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 80  | ID    | A5                          | A5                  |

| 58  | -   | AV <sub>SS</sub> | AV <sub>SS</sub> |     |       |                             |                     |

| 59  | -   | V <sub>SS</sub>  | V <sub>SS</sub>  |     |       |                             |                     |

| 60  | -   | VDD              | VDD              |     |       |                             |                     |

| 61  | ID  | PWR1             | PWR1             |     |       |                             |                     |

| 62  | ID  | PWR2             | PWR2             |     |       |                             |                     |

| 63  | ID  | PWR3             | PWR3             |     |       |                             |                     |

| 64  | -   | N.C.             | N.C.             |     |       |                             |                     |

| 65  | 0   | LINKON           | LINKON           |     |       |                             |                     |

| 66  | ID  | PMODE            | PMODE            | l r | Note  |                             |                     |

| 67  | 0   | ĪNT              | INT              |     | :     | Input<br>Input pull down w  | ith resistance      |

| 68  | ID  | MODE             | MODE             | (   | C :   | Output<br>Input/Output (two |                     |

| 69  |     | V <sub>SS</sub>  | V <sub>SS</sub>  | İ   | D/O : | Input pull down w           | ith resistance /Out |

#### 1.6.2. 112-Pin FBGA

The pin list for 112-Pin FBGA will be shown.

| Pin | Ball | I/O  | 80-MPU I/F Mode | 68-MPU I/F Mode | Pin | Ball | I/O  | 80-MPU I/F Mode  | 68-MPU I/F Mode  |

|-----|------|------|-----------------|-----------------|-----|------|------|------------------|------------------|

| No. | No.  |      | Pin Name        | Pin Name        | No. | No.  |      | Pin Name         | Pin Name         |

| 1   | A1   | -    | N.C.            | N.C.            | 24  | G4   | ID/O | D5               | D5               |

| 2   | B1   | -    | N.C.            | N.C.            | 25  | J1   | -    | N.C.             | N.C.             |

| 3   | B2   | ID   | RESET           | RESET           | 26  | J2   | ID/O | D4               | D4               |

| 4   | C1   | -    | N.C.            | N.C.            | 27  | HЗ   | -    | N.C.             | N.C.             |

| 5   | C2   | ID   | <u>cs</u>       | <u>cs</u>       | 28  | K1   | -    | N.C.             | N.C.             |

| 6   | C3   | ID   | WR              | DS              | 29  | L1   | -    | N.C.             | N.C.             |

| 7   | D1   | -    | N.C.            | N.C.            | 30  | ٢2   | -    | N.C.             | N.C.             |

| 8   | D2   | ID   | RD              | R/W             | 31  | K2   | ID/O | D3               | D3               |

| 9   | D3   | -    | V <sub>DD</sub> | V <sub>DD</sub> | 32  | L3   | -    | N.C.             | N.C.             |

| 10  | D4   | -    | $V_{SS}$        | $V_{SS}$        | 33  | К3   | ID/O | D2               | D2               |

| 11  | E1   | ID/O | D15             | D15             | 34  | JЗ   | ID/O | D1               | D1               |

| 12  | E2   | ID/O | D14             | D14             | 35  | L4   | -    | N.C.             | N.C.             |

| 13  | E3   | ID/O | D13             | D13             | 36  | K4   | ID/O | D0               | D0               |

| 14  | E4   | ID/O | D12             | D12             | 37  | J4   | -    | V <sub>SS</sub>  | V <sub>SS</sub>  |

| 15  | F1   | ID/O | D11             | D11             | 38  | H4   | -    | V <sub>DD</sub>  | V <sub>DD</sub>  |

| 16  | F2   | ID/O | D10             | D10             | 39  | L5   | -    | N.C.             | N.C.             |

| 17  | F3   | ID/O | D9              | D9              | 40  | K5   | -    | N.C.             | N.C.             |

| 18  | G1   | ID/O | D8              | D8              | 41  | J5   | -    | N.C.             | N.C.             |

| 19  | G2   | -    | V <sub>DD</sub> | V <sub>DD</sub> | 42  | H5   | -    | V <sub>DD</sub>  | V <sub>DD</sub>  |

| 20  | F4   | -    | V <sub>SS</sub> | V <sub>SS</sub> | 43  | L6   | -    | V <sub>SS</sub>  | V <sub>SS</sub>  |

| 21  | G3   | ID/O | D7              | D7              | 44  | K6   | ID   | SCLK             | SCLK             |

| 22  | H1   | -    | N.C.            | N.C.            | 45  | J6   | -    | N.C.             | N.C.             |

| 23  | H2   | ID/O | D6              | D6              | 46  | L7   | -    | AV <sub>SS</sub> | AV <sub>SS</sub> |

(Continued)

| 0       |

|---------|

| FUJITSU |

| Pin | Ball | I/O | 80-MPU I/F Mode  | 68-MPU I/F Mode  | Pin | Ball | I/O | 80-MPU I/F Mode  | 68-MPU I/F Mode  |

|-----|------|-----|------------------|------------------|-----|------|-----|------------------|------------------|

| No. | No.  |     | Pin Name         | Pin Name         | No. | No.  |     | Pin Name         | Pin Name         |

| 47  | K7   | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 70  | G8   | -   | AV <sub>DD</sub> | AV <sub>DD</sub> |

| 48  | H6   | 0   | FIL              | FIL              | 71  | F11  | I/O | TPB0             | TPB0             |

| 49  | J7   | 0   | RF               | RF               | 72  | F10  | I/O | TPB0             | TPB0             |

| 50  | L8   | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 73  | F9   | I/O | TPA0             | TPA0             |

| 51  | K8   | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 74  | E11  | I/O | TPA0             | TPA0             |

| 52  | H7   | 0   | R0               | R0               | 75  | E10  | 0   | TPBIAS0          | TPB AS0          |

| 53  | L9   | -   | N.C.             | N.C.             | 76  | F8   | -   | AV <sub>DD</sub> | AV <sub>DD</sub> |

| 54  | K9   | I   | CPS              | CPS              | 77  | E9   | -   | AV <sub>SS</sub> | AV <sub>SS</sub> |

| 55  | J8   | -   | N.C.             | N.C.             | 78  | D11  | -   | N.C.             | N.C.             |

| 56  | L10  | -   | N.C.             | N.C.             | 79  | D10  | -   | V <sub>SS</sub>  | V <sub>SS</sub>  |

| 57  | L11  | -   | N.C.             | N.C.             | 80  | E8   | -   | N.C.             | N.C.             |

| 58  | K11  | -   | N.C.             | N.C.             | 81  | C11  | -   | N.C.             | N.C.             |

| 59  | K10  | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 82  | C10  | -   | V <sub>DD</sub>  | V <sub>DD</sub>  |

| 60  | J11  | -   | N.C.             | N.C.             | 83  | D9   | -   | N.C.             | N.C.             |

| 61  | J10  | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 84  | B11  | -   | N.C.             | N.C.             |

| 62  | 19   | I/O | TPB1             | TPB1             | 85  | A11  | -   | N.C.             | N.C.             |

| 63  | H11  | I/O | TPB1             | TPB1             | 86  | A10  | -   | N.C.             | N.C.             |

| 64  | H10  | I/O | TPA1             | TPA1             | 87  | B10  | ١D  | PWR1             | PWR1             |

| 65  | Н9   | I/O | TPA1             | TPA1             | 88  | A9   | -   | N.C.             | N.C.             |

| 66  | H8   | 0   | TPB AS1          | TPBIAS1          | 89  | В9   | ١D  | PWR2             | PWR2             |

| 67  | G11  | -   | AV <sub>DD</sub> | AV <sub>DD</sub> | 90  | C9   | ١D  | PWR3             | PWR3             |

| 68  | G10  | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 91  | A8   | -   | N.C.             | N.C.             |

| 69  | G9   | -   | AV <sub>SS</sub> | AV <sub>SS</sub> | 92  | B8   | 0   | LINKON           | LINKON           |

(Continued)

| Pin | Ball | I/O 80-MPU I/F Mode |          | 68-MPU I/F Mode |

|-----|------|---------------------|----------|-----------------|

| No. | No.  |                     | Pin Name | Pin Name        |

| 93  | C8   |                     | N.C.     | N.C.            |

| 94  | D8   | ID                  | PMODE    | PMODE           |

| 95  | A7   | 0                   | INT      | INT             |

| 96  | B7   | ID                  | MODE     | MODE            |

| 97  | C7   | -                   | VSS      | VSS             |

| 98  | D7   | -                   | VDD      | VDD             |

| 99  | A6   | ID                  | EOP      | EOP             |

| 100 | B6   | ID                  | DACK     | DACK            |

| 101 | C6   | 0                   | DREQ     | DREQ            |

| 102 | A5   | -                   | VSS      | VSS             |

| 103 | B5   | -                   | VDD      | VDD             |

| 104 | D6   | ID                  | A1       | A1              |

| 105 | C5   | ID                  | A2       | A2              |

| 106 | A4   | -                   | N.C.     | N.C.            |

| 107 | B4   | ID                  | A3       | A3              |

| 108 | D5   | ID                  | A4       | A4              |

| 109 | A3   | -                   | N.C.     | N.C.            |

| 110 | B3   | ID                  | A5       | A5              |

| 111 | C4   | -                   | N.C.     | N.C.            |

| 112 | A2   | -                   | N.C.     | N.C.            |

Note

T

: Input : Input pull down with resistance ID

0 Output

I/O : Input/Output (two-way) ID/O : Input pull down with resistance /Output pull down in two-way

PRELIMINAR Y

# 1.7. Pin Functions

This section will explain the function of pins on the MB86614A.

### 1.7.1. 1394 interface

The 1394 interface of the MB86614A will be explained.

| Nameof pin | I/O | Function                                                                          |

|------------|-----|-----------------------------------------------------------------------------------|

| TPA0       | I/O | TPA positive signal of cable port 0                                               |

| TPA0       | I/O | TPA negative signal of cable port 0                                               |

| TPB0       | I/O | TPB positive signal of cable port 0                                               |

| TPB0       | I/O | TPB negative signal of cable port 0                                               |

| TPA1       | I/O | TPA positive signal of cable port 1                                               |

| TPA1       | I/O | TPA negative signal of cable port 1                                               |

| TPB1       | I/O | TPB positive signal of cable port 1                                               |

| TPB1       | I/O | TPB negative signal of cable port 1                                               |

| TPB AS0    | 0   | Reference voltage output pin for common voltage for cable port 0 common voltage   |

| TPB AS1    | 0   | Reference voltage output pin for common voltage for cable port 1 common voltage   |

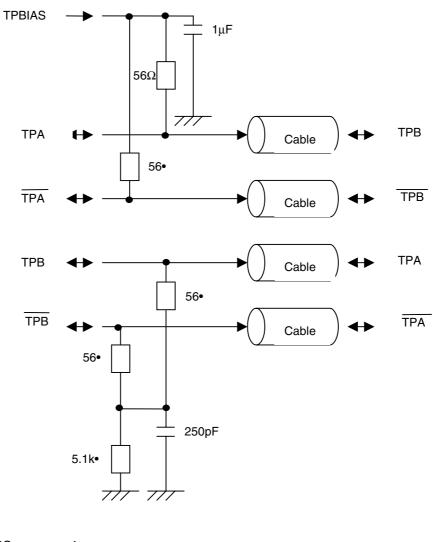

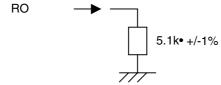

| R0         | 0   | Load resistance connection pin $\ $ (Ground the pin via a 5.1k $\Omega$ resistor) |

# 1.7.2. System interface

The system interface of the MB86614A will be explained.

| Nameof pin | I/O | Function                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| टड         | I   | Chip Select signal Input pin for MPU to select this device as an I/O device                                                                                                                                                                                                                                                              |  |  |  |  |

| A5 to A1   | I   | Address input pins for selecting internal registers.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D15 to D0  | I/O | 16-bit data input/output pins. (MSB:D15, LSB:D0)                                                                                                                                                                                                                                                                                         |  |  |  |  |

| RD (R/W)   | -   | In 80-system mode: Input pin of read strobe signal for output data to data bus from this device<br>In 68-system mode: Input pin of control signal R/W for output and input data from/to this<br>device                                                                                                                                   |  |  |  |  |

| WR (DS)    | -   | In 80-system mode: Input pin for Write strobe signal for input data on data bus to this device In 68-system mode: Input pin of $\overline{\text{DS}}$ signal output when the data bus is enabled                                                                                                                                         |  |  |  |  |

| DREQ       | 0   | DMA Request signal output pin. This signal requests for DMA transfer between the MB86614A device and a host memory.                                                                                                                                                                                                                      |  |  |  |  |

| DACK       | -   | DMA acknowledge signal input pin. This input signal allows the DMA access with a DMAC device.                                                                                                                                                                                                                                            |  |  |  |  |

| EOP        | -   | End of Process signal input pin from a DMAC device.Signal to stop the Chain transfer (continu-<br>ous packet transfer).<br>This is not a pin for stopping the DMA transfer I/F.<br>The value is maintained once this pin is in active state.<br>Do not make this pin active except when the device is in the continuous transfer period. |  |  |  |  |

| INT        | 0   | Interrupt output pin.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

# 1.7.3. Others

The system interface of the MB86614A will be explained.

| Nameof pin     | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK           | l   | System Clock input pin for internal PLL component. (24.576MHz)                                                                                                                                                                                                                                                                                                                           |

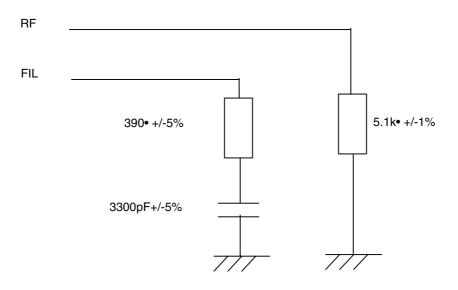

| RF             | 0   | Ground this pin with a 5.1 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                          |

| FIL            | 0   | Filter circuit connection pin.                                                                                                                                                                                                                                                                                                                                                           |

| RESET          |     | System Reset signal input pin. When no system power is present on the device, input "0" to this pin.                                                                                                                                                                                                                                                                                     |

| MODE           | l   | MPU Mode select pin. When "0" : 80-system mode, and when "1" : 68-system mode                                                                                                                                                                                                                                                                                                            |

| PWR1 -<br>PWR3 | I   | Power_Class field setting pins for self_ID packet transmission at the cable power operation.<br>While the device is operating with the system power, not with the cable power, Power_Class<br>field setting is not influenced with these pin settings but the internal register settings as de-<br>scribed in Section 2 Physical Register #4 in this document.                           |

| LINKON         | 0   | Link - on Packet detection pin. At the reception of link - on packet, this pin outputs "H" signal.<br>Then, this pin outputs "L" when PMODE="H". When this signal is not used, please leave this<br>pin open.                                                                                                                                                                            |

| PMODE          | I   | Operation mode input pin to determine the operating environment (system power supply or cable power supply [halt condition of MPU I/F]).<br>Input "0" to this pin when the system power is OFF.<br>Input "1" when the cable power is OFF or system power is ON.                                                                                                                          |

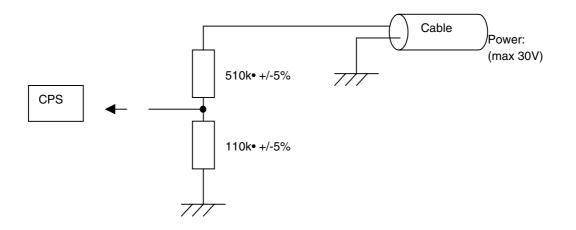

| CPS            | I   | Input pin to detect the availability of cable power supply.<br>Cable power supply: 8 to 30V message to decrease the voltage with an external resistance.<br>The pin determines the availability of cable power supply (1.2 V or more must be applied to the<br>CPS pin) for operation.<br>This pin is not used when cable power supply is not used. In this case, connect it to the GND. |

| AVDD           | -   | Analog power supply pin                                                                                                                                                                                                                                                                                                                                                                  |

| AVSS           | -   | Analog GND pin                                                                                                                                                                                                                                                                                                                                                                           |

| VDD            | -   | Digital power supply pin                                                                                                                                                                                                                                                                                                                                                                 |

| VSS            | -   | Digital GND pin                                                                                                                                                                                                                                                                                                                                                                          |

| N.C.           | -   | No connection pins. Do not connect anything to these pins.                                                                                                                                                                                                                                                                                                                               |

FUJITSU

# 2. Internal Registers

The following lists the MB86614A internal registers. These registers are accessible only in 16-bit.

| ۸dr  | Address<br>Adr |    |    | When Write | When Dood |                                               |                                             |

|------|----------------|----|----|------------|-----------|-----------------------------------------------|---------------------------------------------|

| (hex | ) A5           | A4 | A3 | A2         | A1        | when white                                    | When Read                                   |

| 00   | 0              | 0  | 0  | 0          | 0         | mode - control register                       | ←                                           |

| 02   | 0              | 0  | 0  | 0          | 1         | (Reserved)                                    | flag & status register                      |

| 04   | 0              | 0  | 0  | 1          | 0         | instruction-fetch register                    | ←                                           |

| 06   | 0              | 0  | 0  | 1          | 1         | interrupt-mask register                       | interrupt-code register                     |

| 08   | 0              | 0  | 1  | 0          | 0         | (Reserved)                                    | Receive acknowledge display register        |

| 0A   | 0              | 0  | 1  | 0          | 1         | A-Buffer Data Port (Transmit)                 | A-Buffer Data Port (Receive)                |

| 0C   | 0              | 0  | 1  | 1          | 0         | D-Buffer Data Port (Transmit)                 | D-Buffer Data Port (Receive)                |

| 0E   | 0              | 0  | 1  | 1          | 1         | (reserved)                                    | (reserved)                                  |

| 10   | 0              | 1  | 0  | 0          | 0         | (reserved)                                    | (reserved)                                  |

| 12   | 0              | 1  | 0  | 0          | 1         | Xmit-Async-des-ID setting register            | (reserved)                                  |

| 14   | 0              | 1  | 0  | 1          | 0         | Xmit - Async - PKT - param setting register   | Rcv-Async-PKT-param display register        |

| 16   | 0              | 1  | 0  | 1          | 1         | Xmit-Async data-length setting register       | Rcv-Async data-length display register      |

| 18   | 0              | 1  | 1  | 0          | 0         | Xmit-Async ex-tcode setting register          | Rcv-Async ex-tcode display register         |

| 1A   | 0              | 1  | 1  | 0          | 1         | Xmit-Async source-bus-ID setting register     | Rcv-Async source-bus-ID display register    |

| 1C   | 0              | 1  | 1  | 1          | 0         | Xmit - Async rcode setting register           | Rcv - Async rcode display register          |

| 1E   | 0              | 1  | 1  | 1          | 1         | Xmit-Async des-offset setting register (upper | ) Rcv-Async des-offset display reg. (upper) |

| 20   | 1              | 0  | 0  | 0          | 0         | Xmit-Async des-offset setting register (mid.) | Rcv-Async des-offset display reg. (mid.)    |

| 22   | 1              | 0  | 0  | 0          | 1         | Xmit-Async des-offset setting register (lower | ) Rcv-Async des-offset display reg. (lower) |

| 24   | 1              | 0  | 0  | 1          | 0         | Chain sum-data-length setting reg. (upper)    | Chain remained data byte counter (upper)    |

| 26   | 1              | 0  | 0  | 1          | 1         | Chain sum-data-length setting reg. (lower)    | Chain remained data byte counter (lower)    |

| 28   | 1              | 0  | 1  | 0          | 0         | Chain Xmit-des-ID setting register            | Ping Time Monitor register                  |

| 2A   | 1              | 0  | 1  | 0          | 1         | Chain Xmit-des-offset setting reg. (upper)    | (reserved)                                  |

| 2C   | 1              | 0  | 1  | 1          | 0         | Chain Xmit-des-offset setting reg. (mid.)     | (reserved)                                  |

| 2E   | 1              | 0  | 1  | 1          | 1         | Chain Xmit-des-offset setting reg. (lower)    | (reserved)                                  |

| A dr        |    | А  | ddres | S  |    | When Write                                 | When Read                                  |

|-------------|----|----|-------|----|----|--------------------------------------------|--------------------------------------------|

| Adr<br>(hex | A5 | A4 | A3    | A2 | A1 | when whe                                   | when Read                                  |

| 30          | 1  | 1  | 0     | 0  | 0  | Chain Xmit-data-length setting register    | Rcv-packet transfer speed display register |

| 32          | 1  | 1  | 0     | 0  | 1  | Chain - Retry setting register             | Cycle-timer-monitor display reg. (upper)   |

| 34          | 1  | 1  | 0     | 1  | 0  | (reserved)                                 | Cycle-timer-monitor display reg. (lower)   |

| 36          | 1  | 1  | 0     | 1  | 1  | (reserved)                                 | (reserved)                                 |

| 38          | 1  | 1  | 1     | 0  | 0  | PHY/LINK register address setting register | ←                                          |

| ЗA          | 1  | 1  | 1     | 0  | 1  | PHY/LINK register access port (Write)      | PHY/LINK register access port (Read)       |

| 3C          | 1  | 1  | 1     | 1  | 0  | (reserved): access prohibited              | (reserved): access prohibited              |

| ЗE          | 1  | 1  | 1     | 1  | 1  | (reserved) : access prohibited             | (reserved) : access prohibited             |

Notes:

- 1) Address 3Ch and 3Eh are assigned for the deivce internal test purpose. Do not access these addresses.

- 2) MPU Access Recovery Time:

- For consecutive write opration to regular registers: There must be 25ns (45ns in sleep mode) or longer interval between a rising edge of first WR signal and a falling edge of next WR signal.

- For consecutive read operation to regular registers: There must be 25ns (45ns in sleep mode) or longer interval between a rising edge of first RD signal and a falling edge of next RD signal.

- For read-after-write operation to regular registers: There must be 80ns (160ns in sleep mode) or longer interval between a rising edge of WR signal and a falling edge of RD signal.

- For write operation to PHY/LINK register access port after writing to PHY/LINK register address setting register:

There must be 100ns or longer interval between rising edges of WR signals. (This operation never happens in sleep mode because the internal PLL stops in sleep mode.)

- - For read operation from PHY/LINK register access port after writing to PHY/LINK register address setting register:

There must be 100ns (200ns in sleep mode) or longer interval between a rising edge of WR signal and a falling edge of RD signal.

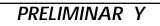

# 2.1 mode-control register (read/write): Address 00h

This register sets the operating mode and automatic operation of the MB86614A.

|                   | bit 15 | 14   | 13    | 12  | 11             | 10           | 9    | 8   | 7   | 6             | 5   | 4   | 3              | 2   | 1            | 0             |

|-------------------|--------|------|-------|-----|----------------|--------------|------|-----|-----|---------------|-----|-----|----------------|-----|--------------|---------------|

| Function :<br>R/W | -      | Bank | c-Div | -   | Chain<br>- dir | Chain<br>-en | B-In | -   | pad | S∣eep<br>Mode | -   | -   | Status<br>Mode | СМ  | tcode<br>add | s-∣D<br>store |

| Default           | '0'    | '0'  | '0'   | '0' | '0'            | ' 0'         | "0"  | '0' | '0' | '0'           | '0' | '0' | '0'            | '0' | '1'          | 'O'           |

[UNUSED] : R/W

Bits 15, 12, 8, 5 and 4 are unused bits. "0" is read out from these bits. For write operation of this register, always set "0" to these bits.

[Bank-Div]: R/W

This field specifies the bank organization of data buffer:

"00" : 1 - bank "01" : 2 - bank "1X" : 4 - bank

[Chain-dir]: R/W

"0" at this bit uses Read chain for the chain transfer.

"1" at this bit uses Write chain for the chain transfer.

[Chain\_en]: R/W

This bit enables the chain transfer.

"0" at this bit does not use the data buffer for the chain transfer.

"1" at this bit uses the data buffer for the chain transfer. This bit retains "1" even if the chain transfer is suspended due to an error detected, EOP signal asserted, or "chain suspend" instruction issued.

[B\_In]: R/W

"0" at this bit stores a write request for data block packet in the asynchronous receive-FIFO, as well as the case of other asynchronous packet.

But "1" at this bit does not store a write request for data block packet in the asynchronous receive - FIFO. Instead, it is stored in 4KB transmit/receive - FIFO when the FIFO is used for asynchronous packet transfer.

Note: When using the chain transfer, please set "0" to this bit. Only Write request for data payload is stored because the chain is set when receiving Read response for data block.

[pad] : R/W

Padding enable bit.

"0" at this bit pads '0' data to received data that does not reach the specified data-length in header. "1" at this bit pads '1' data to received data that does not reach the specified data-length in header.

Note: This bit implies the chip, either way, always contains a packet with correct data - length.

PRELIMINAR Y

#### [Sleep mode]: R/W

When "0" is set: The 1394 port goes to the sleep state after issuing Sleep instruction. The value at the register, which indicates the state of connection to the 1394, is invalid. When "1" is set: The 1394 port does not go to the sleep state after issuing Sleep instruction. The value at the register, which indicates the state of connection to the 1394, is valid.

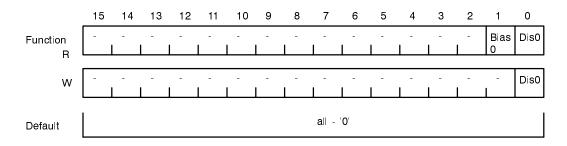

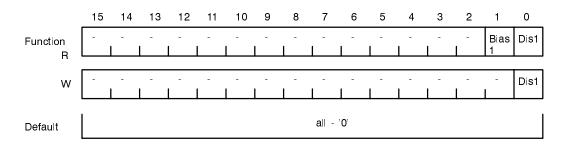

Note: Register: Bias bit on Physical register #8 and #9.

#### [Status mode]: R/W

When "0" is set: Bit 12 of Flag & status register displays ISO cycle. When "1" is set: Bit 12 of Flag & status register displays D-buffer not all empty.

#### [CM] : R/W

When "0" is set, the device does not function as a "cycle master". When "1" is set, the device can function as a "cycle master".

Note: Refer to Section 2.2 in this document for the function of Bit 12 on the flag & status register. Also the interrupt report of Chain operation depends on this bit as described in Section 3.2 in this document.

Note: The condition to be the cycle master is when this bit being contains "1" after bus reset to set RHB bit and the device became a root node. So, even if this bit is set to "1", the device does not become a cycle master when it failed to become a root node. 'cmstr' bit in flag & register indicates whether or not the device is being the cycle master.

#### [tcode add] : R/W

When "0" is set: For Send - operation, it incorporates the values in tcode section for the corresponding registers (Xmit-ISO-PKT - header setting register and Xmit-ASYNC-PKT - param setting register) into the packet header.

When "1" is set: For Send-operation, it automatically incorporates the tcode corresponding to the instruction issued into the packet header. For details, please see Section 4.7 in this document.

#### [s-IDstore] : R/W

When "0" is set: It functions as "No self-ID packet receipt". When the chip receives a self-ID packet during the bus reset process it discards the received packet.

When "1" is set: The chip stores the self-ID packet in the asynchronous receive-FIFO. Section 5.3 in this document further describes the operational flows for self-ID receive.

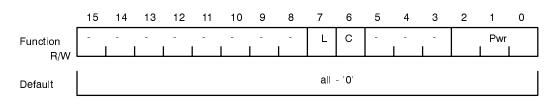

# 2.2 flag & status register (read): Address 02h

This resister indicates the status and data access request of the device.

|            |   | bit 15      | 14            | 13   | 12   | 11            | 10                      | 9    | 8                     | 7                     | 6                     | 5             | 4       | 3           | 2            | 1     | 0            |

|------------|---|-------------|---------------|------|------|---------------|-------------------------|------|-----------------------|-----------------------|-----------------------|---------------|---------|-------------|--------------|-------|--------------|

| Function : | R | ∣PC<br>busy | tran<br>ready | tran | buff | buff<br>empty | A - Rx<br>buff<br>empty | buff | A-Tx<br>buff<br>avail | A-Rx<br>buff<br>avail | : D-<br>buff<br>avail | Int-<br>inser | i sleep | data<br>req | recv<br>busy | cmstr | INT          |

| Default    |   | '0'         | '0'           | '0'  | '0'  | '1'           | '1'                     | "1"  | '1'                   | '1'                   | '1'                   | '0'           | '0      | ' '0'       | '0'          | '0'   | ' <b>0</b> ' |

[IPC busy]: R

"0" at this bit indicates that the chip is ready for receiving an instruction.

"1" at this bit indicates that the chip is busy and not ready for receiving an instruction.

[tran ready] : R

"0" at this bit indicates that the bus reset is in-progress or in forced-sleep state so no packet transfer possible. "1" at this bit indicates that the bus reset has been completed and now ready to transfer packets.

[tran busy] : R

"0" at this bit indicates that the chip is not transmitting or receiving a packet.

"1" at this bit indicates that the chip is transmitting or receiving a packet.

[D-buff all empty] : R (ISO cycle)

Status mode 0: "0" at this bit indicates that the chip is not in the isochronous cycle.

Status mode 1: "0" at this bits indicates that no data is in the bank of all D-Buff. (no data is in all banks of D-Buffer.)

Status mode 0: "1" at this bit indicates that the chip is in the isochronous cycle.

Status mode 1: "1" at this bits indicates that data is in the bank of D-Buff.

[A - Tx buff - empty] : R

"0" at this bit indicates that the asynchronous transmit-FIFO is not empty.

"1" at this bit indicates that the asynchronous transmit-FIFO is empty.

[A-Rx buff-empty] : R

"0" at this bit indicates that the asynchronous receive - FIFO is not empty.

"1" at this bit indicates that the asynchronous receive - FIFO is empty.

[D-buff-empty] : R

"0" at this bit indicates that the transmit/receive-FIFO has no bank with empty.

"1" at this bit indicates that the transmit/receive-FIFO has the bank with empty.

[A-Tx buff-avail] : R

"0" at this bit indicates that the asynchronous transmit - FIFO has 1 packet data already and so no more packet can be stored.

"1" at this bit indicates that the asynchronous transmit-FIFO has a space available to store packet.

#### [A-Rx buff-avail] : R

"0" at this bit indicates that the asynchronous receive - FIFO has 1 packet data already and so no more packet can be stored.

"1" at this bit indicates that the asynchronous receive - FIFO has a space available to store packet.

#### [D-buff-avail] : R

"0" at this bit indicates that all the banks of transmit/receive - FIFO have 1 packet data each and no more packet can be stored.

"1" at this bit indicates that at least 1 bank still has a space available to store packet.

#### [int-reset]

At 1, it indicates that the device is releasing from the internal reset state. At 0, it indicates that the device is in internal reset state.

Note: After the powered - on, the chip retains the internal reset state until the on - chip PLL is locked. The PHY and Link layers do not start operating in this state.

#### [sleep]

At 1, it indicates that the device is in forced-sleep state. At 0, it indicates that the device is not in forced-sleep state.

#### [data-req]

"0" at this bit indicates that the asynchronous receive - FIFO does not contain any data.

"1" at this bit indicates that the asynchronous receive - FIFO contains any data.

This bit is used for reading out self-ID packet contained in the asynchronous receive - FIFO.

#### [recv-busy]

At 0, it indicates that the device is not in busy mode. At 1, it indicates the device is in busy mode because of an asynchronous/self-ID packet received or 'start busy mode' instruction (03h) issued.

Note: When an asynchronous packet is received while this bit indicates "1", the chip transmits 'ack\_busy\_X'. But, one exception is that the chip is receiving a read response for data block packet during the chain transfer. In this case there is no relationship between the packet receipt and the busy mode indicated by this bit.

[cmstr]

"0" at this bit means the device is not a cycle master. "1" at this bit means the device is a cycle master.

#### [INT]

Interrupt flag bit.

"0" at this bit means the device does not hold interrupt(s).

"1" at this bit means the device holds interrupt(s).

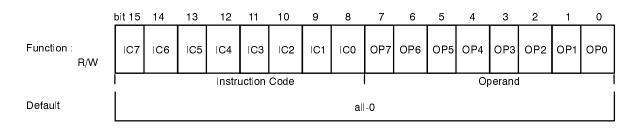

# 2.3 Instruction-fetch register (read/write): Address 04h

This register is composed of "instruction code" and "Operand", used for writing the instruction to the device. See Chapter 3 for details of instruction codes and operands.

Note: Before writing an instruction code, please check the IPC busy bit of flag&status register and make sure it indicates "0".

[instruction-code] :Bits 15 to 8 Specify an instruction code as listed in Chapter 3.

[operand] : Bits 7 to 0

Specify operand for the instruction. If no operand instruction, write "0" at this field.

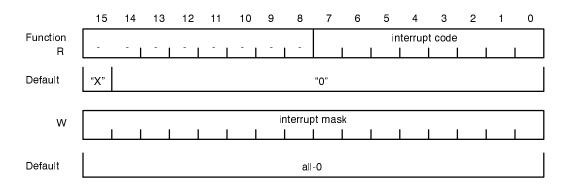

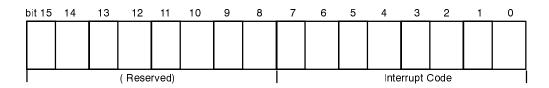

### 2.4 Interrupt coderegister(read) /Interrupt mask register(write) : Address 06h

Interrupt code register indicates the interrupt reported by the device.

Refer to Section 4 for the details of interrupt code.

Interrupt mask register controls the mask of each interrupt factor generated by the device.

It is controlled with flags by bit. Refer to Section 4 for the details of interrupt factors to be masked.

#### [UNUSED] : Bits 15 to 8

Undefined value is read out from these bits at the read operation. "0" data is read out from this field. However, "X" data is read out from bit 15 in interrupt code register.

[interrupt code (read)]

Stores 8-bit code for each interrupt factor (This is a FIFO type (8-byte) register, and saves up to 8 interrupts generated by the chip.)

[interrupt mask (write)]

Specifies mask of each interrupt factor. The interrupt code masked by setting with this register is not stored in the interrupt-code register and INT signal is not asserted.

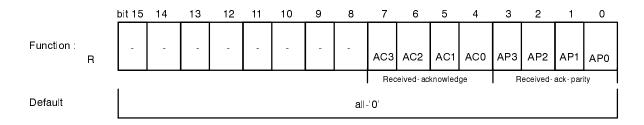

# 2.5 Receive-acknowledgedisplay register (read): Address 08h

This register indicates the acknowledge packet received to the chip itself. This register must be read out after reporting "Asynchronous packet sent" interrupt (61h).

Interrupt code register indicates the interrupt reported by the device.

Refer to Section 4 for the details of interrupt code.

Interrupt mask register controls the mask of each interrupt factor generated by the device.

It is controlled with flags by bit. Refer to Section 4 for the details of interrupt factors to be masked.

[UNUSED] : Bits 15 to 8

"0" is read out from this field.

[received-acknowledge]: Bits 7 to 4

This field indicates the code section of the received acknowledge packet. (MSB:AC3, LSB: AC0) (MSB:bit7, LSB: bit4)

[received-ack-parity]

This field indicates the parity section of the received acknowledge packet (MSB:AP3, LSB:AP) (MSB:bit3, LSB: bit0)

When an acknowledge code could not be received within a specified time, the indication of this register retuns to the initial value "0000h", and the chip reports "acknowledge missing" interrupt (91h).

FUJITSU

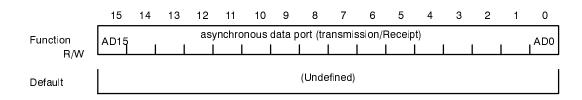

# 2.6 A-Buffer DataPort (Receive)(read)/(Transmit) (write): Address 0Ah

This is a data-port register for accessing the asynchronous receive- or transmit-FIFO.

The read data can be read out in the order of the receipt of 1394 bus - packet (MSB: 1st read). MSB: AD15, LSB: AD0

The write data is sent out as 1394 bus-packet in the order of written (MSB: 1st write). MSB: AD15, LSB: AD0

[asynchronous data - port ] : Bits 15 to 0

For Read operation, these are the receive - FIFO read out ports for Asynchronous transfer. (MSB: bit15, LSB: bit0)

For Write operation, these are the transmit-FIFO write ports for Asynchronous transfer. (MSB:bit15, LSB: bit0)

# 2.7 D-Buffer DataPort (Receive)(read)/(Transmit) (write): Address 0Ch

This is a data-port register for accessing the transmit/receive-FIFO.

It accesses to the Xmit/recv-data port without the DMA transfer and can write/read out the transmitting/received data.

The data written in this port is sent out as 1394 bus-packet in order of written (MSB: 1st write). MSB: DD15, LSB: DD0

The read data is deda out I order the receipt with 1394 bus-packet (MSB: 1st read). MSB: DD15, LSB: DD0

|          | 15   | 14 | 13 | 12 | 11 | 10 | 9      | 8     | 7       | 6 | 5 | 4 | 3 | 2 | 0     |

|----------|------|----|----|----|----|----|--------|-------|---------|---|---|---|---|---|-------|

| Function | DD15 |    |    |    |    | Xn | nit/Re | cv-da | ta port | t |   |   |   |   | . DD0 |

| R/W      |      |    |    |    |    |    |        |       |         |   |   |   |   |   | 1     |

| ,        |      |    |    |    |    |    |        |       |         |   |   |   |   |   |       |

| Default  |      |    |    |    |    |    |        | (Unde | fined)  |   |   |   |   |   |       |

| Deruun   |      |    |    |    |    |    |        |       |         |   |   |   |   |   |       |

[Xmit/Recv-data port]: Bits 15 to 0

For Read operation, these are the Xmit/recv-FIFO read out ports. (MSB:bit15, LSB: bit0) For Write operation, these are the Xmit/recv-FIFO write ports. (MSB:bit15, LSB: bit0)

# 2.8 Xmit-ASYNC-Destination-ID setting register (write): Addr:12h

This register sets the destination ID field of header at Asynchronous packet transmission.

|                    | 15 | 14 | 13 | 12  | 11       | 10     | 9    | 8 | 7 | 6 | 5    | 4   | 3        | 2     | 1    | 0 |

|--------------------|----|----|----|-----|----------|--------|------|---|---|---|------|-----|----------|-------|------|---|

| Function           |    |    |    | Des | stinatio | on-bus | 8-ID |   |   |   |      | Des | stinatio | on-PH | Y-ID |   |

| W                  |    |    |    |     |          |        |      |   |   |   |      |     |          |       |      |   |

| Default "3FFh" "00 |    |    |    |     |          |        |      |   |   |   | 00h" |     |          |       |      |   |

#### [Destination-bus-ID]

Set the destination bus-ID for transmit-asynchronous packet header (MSB:bit15, LSB:bit6) Set the destination-bus-ID.

#### [Destination-PHY-ID]

Set the destination physical-ID for transmit-asynchronous packet header (MSB:bit5, LSB:bit0) Set the destination-physical-ID.

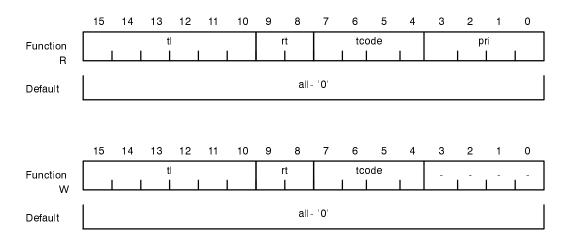

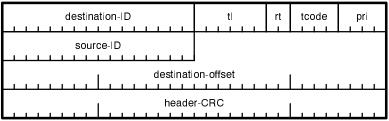

### 2.9 Xmit-/Recv-Asynchronous-packet-parameteregister (write/read):Addr:14h

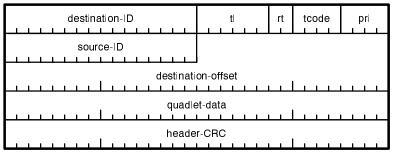

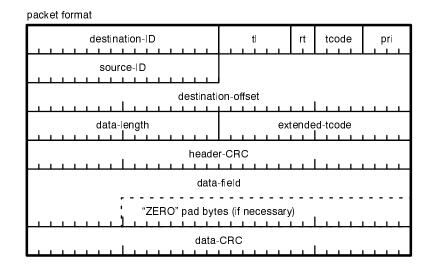

Xmit-Asynchronous-packet-parameter register sets the tl, rt, tcode and pri fields of header at Asynchronous packet transmission.

Recv-Asynchronous-packet-parameter register indicates the tl, rt, tcode and pri fields of header at received Asynchronous packet.

[tl]

For read-operation, it indicates the tl for receive-asynchronous packet header (MSB:bit15, LSB:bit10) For write-operation, set the tl for transmit-asynchronous packet header (MSB:bit15, LSB:bit10)

[rt]

For read-operation, it indicates the rt(retry code) for receive-asynchronous packet header (MSB:bit9, LSB:bit8).

For write-operation, set the rt(retry code) for transmit-asynchronous packet header (MSB:bit9, LSB:bit8)

[tcode]

For read-operation, it indicates the tcode(transaction code) for receive-asynchronous packet header (MSB:bit7, LSB:bit4).

For write-operation, set the tcode (transaction code) for transmit-asynchronous packet header (MSB:bit7, LSB:bit4). These bits setting is invalid when "1" is set in the tcode-add bit (bit 1 of the mode-control register:addr00h).

The tcode (transaction code) defines the packet form and processing. If a tcode that can not be recognized is received, the header and data are not stored, and no interrupt is reported.

[pri] : Bits 3 to 0

For read-operation, it indicates the pri field for receive-asynchronous packet packet header (MSB:bit3, LSI:bit0).

For write-operation, this is a reserved field. Always write '0' at this field. (The pri field of transmit-asynchronous packet header is always fixed with '0h'.

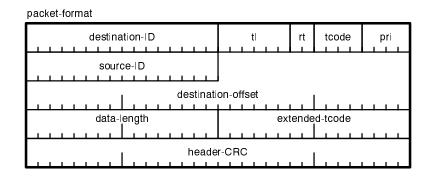

### 2.10 Xmit-/Recv-Asynchronous-data-lengthregister (write/read): Address 16h

Xmit-Asynchronous-data-length register sets the data-length field of header at asynchronous packet transmission.

Recv-Asynchronous-data-length register indicates the data-length field of received asynchronous packet header.

|          | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7     | 6     | 5      | 4 | 3 | 2 | 1 | 0 |

|----------|----|----|----|----|----|----|---|-----|-------|-------|--------|---|---|---|---|---|

| Function | -  | -  | -  | -  |    |    |   |     |       | data- | length |   |   |   |   |   |

| R/W      |    |    |    |    |    |    |   |     |       |       |        |   |   |   |   |   |

|          | 1  |    |    |    |    |    |   |     |       |       |        |   |   |   |   | 1 |

| Default  |    |    |    |    |    |    |   | all | - '0' |       |        |   |   |   |   |   |

[UNUSED] : Bits 15 to 12 Reserved field. For read-operation, it always indicates '0h'. For write-operation, always write '0h' to this field.

[data-length] : Bits 11 to 0

For read-operation, it indicates the lower 12-bit of data-length for receive-asynchronous packet header (MSB:bit11, LSB:bit0)

For write-operation, set the lower 12-bit of data-length for transmit-asynchronous packet header (MSB:bit11, LSB:bit0)

- Note 1: When the actual data length of packet received was shorter than the value that is written in the header of the packet, the chip pads "0" or "1" data according to the pad bit setting in mode - control register to the received packet and stores it in the transmit/receive - FIFO or asynchronous receive - FIFO. Then, it reports "Data length short error (Asynchronous)" interrupt (31h).

- Note 2: When the actual data-length of packet received was longer than the value that is written in the header of the packet, the chip stores the data in the FIFO up to the data-length specified by the data-length field and discards the remained data. Then, it reports "Data length long error (Asynchronous)" interrupt (32h).

- Note 3 : If the transmit data is stored in the asynchronous transmit FIFO, the data length that can be specified in this field is 0 to 128 byte.

- Note 4: If the transmit data is stored in the transmit/receive FIFO, the data length that can be specified in this field is 1 to 2048 byte regardless of the bank configuration.

- Note 5 :The chip makes the packetization to the data as specified in this field to read out the data from the FIFO.

- Note 6 : If this field contains a small value that does not reach a quadlet level, the chip pads '0' data until quadlet and generates a packet.

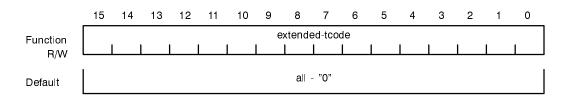

# 2.11 Xmit-/Recv-Async extended-tcoderegister (write/read): Address 18h

Xmit-Async extended-tcode register sets the ex-tcode field at asynchronous packet transmission. Recv-Async extended-tcode register indicates the ex-tcode field of received asynchronous packet header.

[extended-tcode]

For read-operation, it indicates the extended-tcode for receive-ASYNC-packet header (MSB:bit15, LSB:bit0)

For write-operation, set the extended-tcode for send-ASYNC-packet header (MSB:bit15, LSB:bit0) The extended-tcode field is valid only for packet transmission on lock-request and lock-response.

For other asynchronous packet transmission, 0000h is specified in the packet irrespective of the register value.

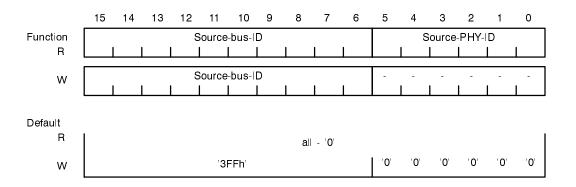

# 2.12 Xmit-ASYNC-source-bus-ID/Receive ASYNC-source-ID register (write/read) : Address 1Ah

Xmit-ASYNC-source-bus-ID register sets the source-bus-ID field at asynchronous packet header transmission.

Receive - ASYNC-source-ID register indicates the source - ID field of received asynchronous packet header.

[Source-bus-ID] :

For read-operation, this field indicates the source-bus-ID for received asynchronous packet header (MSB:bit 15, LSB:bit6).

For write-operation, set the source-bus-ID for transmit-asynchronous packet header (MSB:bit 15, LSB:bit6). Specify the source-bus-ID to this field.

FUĴÎTSU

#### [Source-PHY-ID]

For read - operation, it indicates the source - physical - ID for received asynchronous packet header (MSB: bit5, LSB: bit0).

For write-operation, set "0" to this field. (The chip always sets the current physical ID held by the PHY layer internally.)

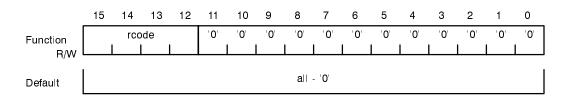

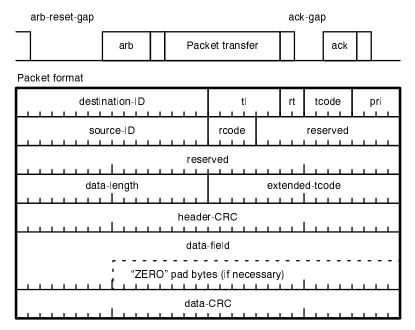

# 2.13 Xmit-/Receive Async rcoderegister (write/read): Address 1Ch

Xmit-Async rcode register sets the rcode field at asynchronous packet header transmission.

Receive - Async rcode register indicates the rcode (response code) field of received asynchronous packet header.

[rcode]

For read-operation, this field indicates the rcode (response code) for received asynchronous packet header (MSB:bit15, LSB: bit12).

For write-operation, set the rcode (response code) for transmit-asynchronous packet header (MSB:bit15, LSB: bit12).

[UNUSED] : bits 11 to 0

Read out value from this field is '0'. For write-operation, always set "0" to this field.

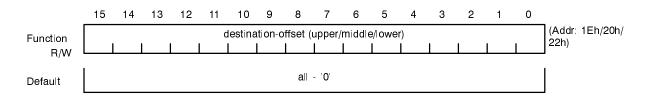

# 2.14 Xmit-/Receive Async destination-offset register (u/m/l) (write/read): Addr: 1Eh/20h/22h

Xmit-Async destination-offset register sets the destination-offset at asynchronous packet header transmission.

Receive - Async destination-offset register indicates the destination - offset of received asynchronous packet header.

#### [destination-offset]

For read-operation, it indicates the destination-offset for receive-asynchronous packet header (MSB:bit15, LSB:bit0).

For write-operation, set the destination-offset for transmit-asynchronous packet header (MSB:bit15, LSB:bit0). set the lower 48-bit of destination node address for the request packet.

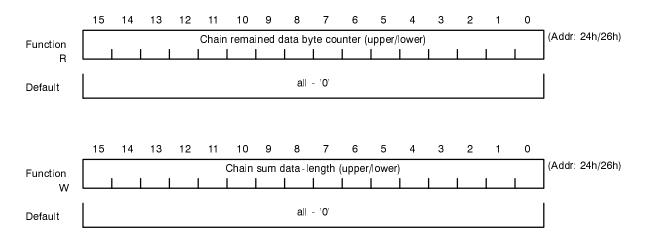

# 2.15 Chain remained data byte counter (u/l) (read)/Chain sum data-length setting register(u/l) (write) : Addr: 24h/26h

Chain remained data byte counter register indicates the remained data byte transferred to an host side in chain mode.

Chain sum data - length setting register is used for setting a sum of data - length to be transferred by chain with 'asynchronous chain' instruction.

For read operation, this register functions as a counter that indicates the remained byte count for data transferred to an host side in chain mode.

For write operation, this register is used for setting a sum of data-length to be transferred by chain with 'asynchronous chain' instruction.

#### [Chain remained data byte]

This field indicates the remained byte count for data transferred to an host side in chain mode. (MSB:bit15, LSB:bit0).

Note: This counter in decrement every packet transferred to a host side.

#### [Chain sum data - length]

This field specifies a sum of data-length transferred in chain mode. (MSB:bit15, LSB:bit0).

- Notes 1. The data-length range that can be set is from 1h to FFFFFFFh bytes.

- 2. Upon the receipt of 'asynchronous chain' instruction, the chip transmits 'read request for data block packet' that is set to Chain Xmit-data-length setting register (30h) and repeats this action until all the data specified in this field are read out.

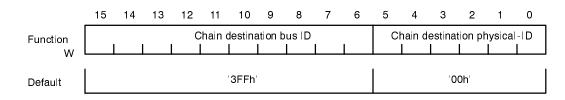

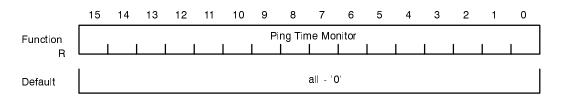

# 2.16 Ping Time Monitor register (read)/Chain Xmit-destination-ID setting register (write): Address 28h

Ping Time Monitor register displays the ping time that indicates the time until a self node receives the response.

Chain Xmit-destination-ID setting register specifies the destination IDs for bus-ID and physical-ID described in header area of Read request for data block packet automatically transmitted by chain mode data transfer.

[Chain destination bus ID] : bits15 to 6

This field specifies the destination bus-ID described in the packet header for 'read request for data block'. (MSB :bit15, LSB:bit6)

[Chain destination physical-ID] : bits 5 to 0

This field specifies the destination physical-ID described in the packet header for 'read request for data block'. (MSB :bit5, LSB:bit0)

[Ping Time Monitor] : bits15 to 0

This field displays the ping time that indicates the time until a self node receives the response. 1-bit is in 20ns unit. (Precisely, 2 times of 24.576MHz).

# 2.17 Chain Xmit-destination offset setting register (u/m/l)(write) : Address 2Ah/2Ch/2Eh

This register specifies the destination-offset for the first 'read request for data block'.

|          | 15 | 14 | 13 | 12 | 11  | 10     | 9       | 8       | 7        | 6      | 5       | 4    | 3 | 2        | 1 | 0 | _                      |

|----------|----|----|----|----|-----|--------|---------|---------|----------|--------|---------|------|---|----------|---|---|------------------------|

| Function |    |    |    |    | Cha | in des | tinatio | on offs | et (upp  | per/mi | ddle/lo | wer) |   |          |   |   | (Addr:<br>2Ah/2Ch/2Eh) |

| W        |    |    |    |    |     |        |         |         | <u> </u> | I      | I       | I    | I | <u> </u> |   |   | ]                      |

| Default  |    |    |    |    |     |        |         | all     | - '0'    |        |         |      |   |          |   |   |                        |

[Chain destination offset] : bits15 to 0

This field specifies the destination offset described in the packet header for 'read request for data block'. (MSB :bit15, LSB:bit0)

Note: Set the address for page-boundary of Initiator's memory in this field. If the starting point of data field indicated by ORB is not in the boundary, the host side should have all the responsibility to read out the data until the page boundary and execute the chain transfer.

# 2.18 Recv-packettransfer speed display register (read): Address 30h

This register indicates the transfer speed of received asynchronous packet.

|          | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7     | 6 | 5 | 4 | 3 | 2 | 1    | 0     |

|----------|----|----|----|----|----|----|---|-----|-------|---|---|---|---|---|------|-------|

| Function |    | -  | -  | -  | -  | -  | - | -   | -     | - | - | - | - | - | rec- | speed |

| R        |    |    |    |    |    |    |   |     |       |   |   |   |   |   |      |       |

| Default  |    |    |    |    |    |    |   | all | - '0' |   |   |   |   |   |      |       |

[UNUSED]: bits 15 to 2 This field always indicates '0'.

[rec-speed]: bits 1 and 0

This field indicates the transfer speed of received asynchronous packet.

It displays the value for each packet other than the followings:

- Read response packet at Read chain

- Write response packet at Write chain

Transfer speed s100 (Bit1: 0, Bit0: 0) s200 (Bit1: 0, Bit0: 1) s400 (Bit1: 1, Bit0: 0) Reserved (Bit1: 1, Bit0: 1)

PRELIMINAR Y

Notes:

1. The register does not change the value when it receives the PHY packet or Cycle-start packet.

2. Refer to the table below when an error with an interrupt code is detected when receiving packet.

When an error occurs: Data length short error (31h): Data change Data length long error (32h): Data change Packet format error (33h): No change Data end not found (34h): Data change

Header CRC error (35h): No change

Data CRC error (36h): Data change

Data length invalid (37h): Data change

# 2.19 Chain Xmit-data-length setting register (write): Address 30h

This register specifies the data-length field of packet header for 'read request for data block' packet which is automatically transmitted in the chain transfer.

|          | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7     | 6     | 5      | 4     | 3 | 2 | 1 | 0 |

|----------|----|----|----|----|----|----|---|-----|-------|-------|--------|-------|---|---|---|---|

| Function | -  | -  | -  | -  |    |    |   |     |       | Chain | data-l | ength |   |   |   |   |

| W        |    |    |    |    |    |    |   |     |       |       |        |       |   |   |   |   |

| Default  |    |    |    |    |    |    |   | all | - '0' |       |        |       |   |   |   |   |

[UNUSED]: Bits 15 to 12 Always write '0' to this field.

[Chain data-length] : bits11 to 0

This field specifies the lower 12-bit of data-length field of packet header for 'read request for data block' packet which is automatically transmitted in the chain transfer. (MSB: bit11, LSB: bit0)

Notes 1.Set a measure or multiple of the memory page size owned by an initiator node within 1 to 2048 - byte.

2.When the sum data - length is not equal to the multiple of this register, the value of this data - length field is autumatically calculated since the last packet length is the fraction.

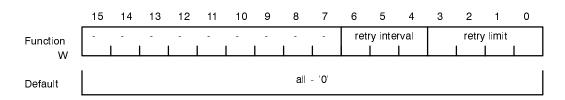

# 2.20 Chain-Retry setting register (write): Address 32h

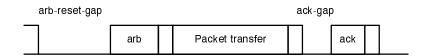

This register specifies the time interval and the maximum number of retry automatically performed when an acknowledge 'ack\_busy\_X' is received in response to 'read request for data block' packet automatically transmitted in the chain transfer.

[UNUSED]: bits 15 to 7

Always write '0' to this field.

[retry-interval]: bits 6 to 4

This field specifies the approximate time interval of retry in the chain transfer. Refer to the list of 8.29b shown below.

[retry - limit]: bits 3 to 0

This register specifies the maximum number of retry automatically performed when an acknowledge 'ack\_busy\_X' is received in response to 'read request for data block' packet automatically transmitted in the chain transfer. (MSB: bit3, LSB: bit0)

- Notes 1. Retry number that can be set is 0 to 15.

- 2. When 'ack\_pending' is not received even after retrying as number specified, the chip stops the chain transfer in a half way and reports 'Retry time out' interrupt (F6h).

Time interval

Immediately (Setting value: 000) Approx. 125 us (Setting value: 001) Approx. 250 us (Setting value: 010) Approx. 500 us (Setting value: 011) Approx. 1 ms (Setting value: 100) Approx. 2 ms (Setting value: 101) Approx. 4 ms (Setting value: 110) Approx. 8 ms (Setting value: 111)

# 2.21 Cycletimer monitor register (u/l)(read): Address 32h/34h

This register indicates the on-chip cycle-timer register value.

|          | 15 | 14 | 13 | 12 | 11 | 10  | 9     | 8      | 7        | 6       | 5     | 4 | 3 | 2 | 1 | 0 | _               |

|----------|----|----|----|----|----|-----|-------|--------|----------|---------|-------|---|---|---|---|---|-----------------|

| Function |    |    |    |    |    | Cyc | e tim | er mor | hitor (u | ipper/l | ower) |   |   |   |   |   | (Addr: 32h/34h) |

| R        |    |    |    |    |    |     |       |        |          |         |       |   |   |   |   |   | J               |

| Default  |    |    |    |    |    |     |       | all    | - '0'    |         |       |   |   |   |   |   |                 |

[Cycle timer monitor] : bits15 to 0

This field indicates the on-chip cycle-timer register value. (MSB:bit15, LSB:bit0) Note: Reading out the lower word (at address 34h) activates latching the upper word (32h) and reading out the upper word releases the latch. Therefore, a combination of reading '34h' first and then '32h' is required.

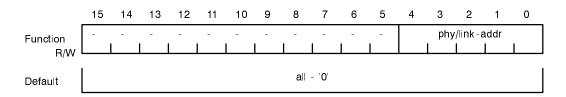

#### 2.22 PHY/LINK register address setting register (read/write): Address 38h

This register specifies the address for the indirect access to the internal PHY/LINK registers. The PHY/LINK register at the address selected by this register can be accessed through the PHY/LINK register access port.

[UNUSED]: Bits 15 to 5

For read operation, '0' is read out from these bits. For write operation, always write "0" at these bits.

[phy/link-addr.]: Bits 4 to 0

This field specifies the address for PHY/LINK register to be accessed. (MSB:bit4, LSB:bit0)

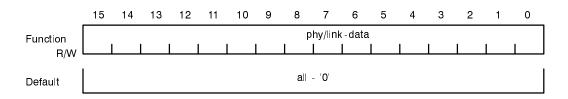

# 2.23 PHY/LINK register access port (read/write): Address 3Ah

This port is used for the indirect access to the internal PHY/LINK registers. The register at address selected by the PHY/LINK register address setting register can be accessed through this port.

[phy/link-data]: Bits 15 to 0

For read operation, contents of register selected by 'phy/link-addr' are read out. (MSB:bit15, LSB:bit0) For write operation, specify the data written to the register that 'phy/link-addr' selects.

#### 2.24 PHY/LINK Register Functional Description

The PHY/LINK Register specifies the address with the PHY/LINK register address setting register (address 38h) to enable reading out/writing to several registers through the PHY/LINK register access port.

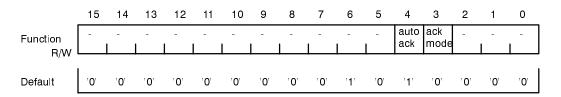

The list below shows the PHY/LINK registers on the MB86614A. Refer to the paragraphs 2.33.2 to 2.33.10 for their details.

| phy/link-addr | Register Name        |

|---------------|----------------------|

| 00h           | Physical register #0 |

| 02h           | Physical register #1 |

| 04h           | Physical register #2 |

| 06h           | Physical register #3 |

| 08h           | Physical register #4 |

| 0Ah           | Physical register #5 |

| 0Ch           | Physical register #6 |

| 0Eh           | Physical register #7 |

| 10h           | Physical register #8 |

| 12h           | Physical register #9 |

| 14h           | reserve              |

| 16h           | reserve              |

| 18h           | Link register #0     |

|               |                      |

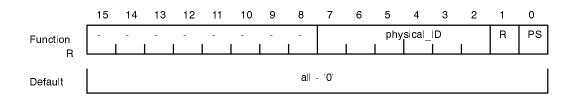

#### 2.24.1 Physical register #0 (read): phy/link-addr. 00h

This register indicates the parameters related to the connection with the 1394 bus.

[UNUSED] : bits 15 to 8

This unused field indicates '0'.

[physical\_ID]

This field indicates the number of self node determined in the self-identify process in bus reset. (MSB:bit7, LSB:bit2) This field is valid after the bus reset completed.

[R]

'0' at this bit indicates that the self node is not a root.

'1' at this bit indicates that the self node is a root.

[ PS ]

'0' at this bit indicates that the cable power being supplied to the node is below the specification.

'1' at this bit indicates that the cable power being supplied to the node is beyond the specification.

This bit is valid only when a comparator circuitry to detect the cable power is externally connected with the chip. Also the threshold level in the specification is 8V.

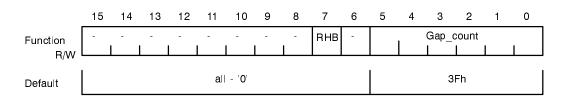

#### 2.24.2 Physical register #1 (read/write): phy/link-addr. 02h

This register specifies the gap count value and setting to be a root.

It also indicates the current gap count value and state to be a root.

Writing operation to this register is allowed only when the node is 'bus manager' or when it is 'isochronous resource manager' if 'bus manager' does not exist.

[UNUSED] : bits 15 to 8 and 6 For read operation, this unused field indicates '0'. For write operation, always write '0' at this field.

## [RHB]

When '0' is specified to this field, the chip does not intend to be a root in the next bus reset. When '1' is specified, the chip intends to be a root in the next bus reset. Note: This field is also set upon receipt of a PHY configuration packet automatically.

#### [Gap\_count]

For read operation, this field indicates the current gap\_count value. (MSB:bit5, LSB:bit0) For write operation, set a gap\_count value (MSB:bit 5, LSB:bit0)

Note: This field is also set upon receipt of a PHY configuration packet automatically. Also the gap\_count value returns to the default again with twice bus reset.

#### 2.24.3 Physical register #2 (read): phy/link-addr. 04h

This register indicates the fixed value of the physical layer parameters.

|               | 15 | 14 | 13 | 12 | 11  | 10    | 9 | 8 | 7 | 6      | 5       | 4 | 3       | 2            | 1        | 0 |

|---------------|----|----|----|----|-----|-------|---|---|---|--------|---------|---|---------|--------------|----------|---|