# ASSP Communication Control

# CMOS Wide SCSI-II Protocol Controller With PCI Interface

# **MB86605**

#### **■ DESCRIPTION**

The MB86605 is an intelligent SCSI Protocol Controller (SPC) which complies with ANSI (SCSI-2) standard and integrates a PCI local bus interface function. The specification of SCSI controller block is based on the MB86603 which is a wide SCSI-2 protocol controller with addition of some enhancements such as integration of PCI interface, enlarged "user program memory" (2 KBytes) and improvement of internal operation speed and performance. The MB86605 is capable of transferring up to 20 Mbyte/sec at the wide high speed synchronous mode. As for the SCSI bus pins, a totem pole type single-ended driver/receiver is incorporated in the device so that it can drive the SCSI bus directly. Furthermore, the MB86605 is capable of connecting the external differential type driver/receiver.

The SCSI bus sequence is controlled by commands issued from a host system. So, it supports sequential commands that perform the phase-to-phase sequences to reduce the system overhead of sequence operations.

As another key feature to reduce the system overhead, the device has a 2 Kbytes user program memory to store user program codes. Due to this, all the SCSI bus sequences including the data transfer can be performed automatically.

As the system interface block, it incorporates a 32-bit PCI local bus interface which makes MB86605 an ideal "on-board PCI-SCSI controller" as well as a "host adapter" for PCs, servers and work stations. It also supports 16-bit separate MPU and DMA buses. For the on-chip PCI bus interface, the MB86605 also incorporates a 32-bit DMA controller that is capable of supporting the scatter-gather function so that the data transfers can be controlled by both user program and the host system.

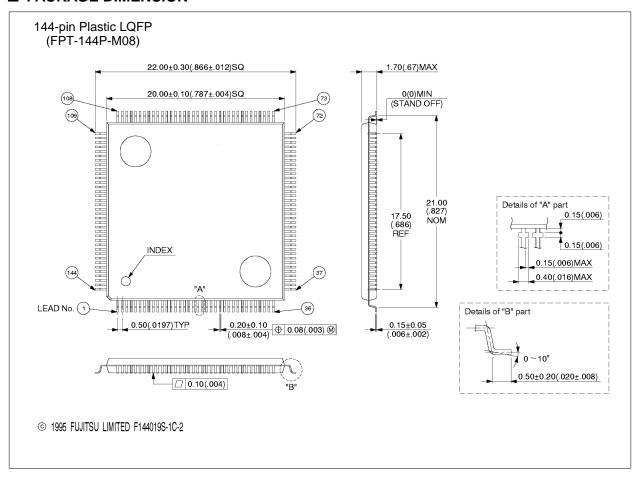

The device is fabricated by the advanced CMOS process and is housed in an 144-pin plastic Low profile shrink Quad Flat Package (Suffix: –PMT).

#### **■ PACKAGE**

#### **■ FEATURES**

SCSI Protocol Controller Block:

- · Operable as initiator and target

- · WIDE and FAST data transfer

- Synchronous transfer (max. 20 Mbytes/s: Up to 32 offset values can be set.)

- Asynchronous transfer (max. 10 Mbytes/s)

- 64-byte FIFO register for data phase

- Two types (send-only and receive-only) of 32-byte data buffers for message, command, and status phases (MCS Buffers)

- On-chip totem pole type SCSI single-ended driver/receiver

- Supports external SCSI differential driver/receiver

- On-chip memory to store transfer parameters for each ID (up to 15 connected devices)

- On-chip 16-bit transfer block counter and 24-bit transfer byte counter

- Maximum Transfer Byte : 1 Tbyte at fixed length data transfer

- : 6 Mbyte at variable length data transfer

- Supports various control commands:

- Sequential Commands : can perform phase-to-phase sequential operations (functions only when

- issuing from a system side.)

- Discrete Commands : can perform any desired sequence to program in the user program memory

- Data Transfer Commands : can program the transfer data length at the user program operation.

- On-chip direct control register for SCAM (SCSI Configured AutoMatically)

- Supports Multi Selection/Reselection Responses

- Selection and Reselection responses can be done to plural IDs.

- · On-chip 2 Kbyte User Program Memory

- Two Modes: 2 Kbyte × 1 bank and 1 Kbyte × 2 banks

(While 1 Kbyte  $\times$  2 banks are selected, host system can access another bank even if the user program is executing.)

- Access to User program : Burst transfer via I/O access port

- : Direct access to 2 Kbyte user program memory (only for PCI bus I/F mode)

- User Selectable Interrupt Report

- Unnecessary interrupt reports can be disabled depending on user's applications to reduce a system ISR overhead.

- Two automatic receive modes

- Initiator: can automatically receive information for new phase to which target switched

- Target : can automatically receive attention condition generated by initiator

- · Automatic selection/reselection

- For command issues : automatically performs to receive MSG/CMD to the selection/reselection

request from partner device

- For user program operation: pauses the program currently executed and automatically jumps to the

specified selection/reselection routine in response to the selection/reselection

request from partner device.

- Operation Clock

- System Clock: Max. 40 MHz

- Internal Processor Operating Clock: Max. 20 MHz

(Continued)

#### (Continued)

#### System Interface Block:

- Separate MPU and DMA buses called 16-bit Bus Mode

- Directly connectable to 68-series or 80-series MPU

- Two transfer modes (Program transfer and DMA transfer (slave mode))

- PCI Bus Interface Mode

- Directly connectable to the 32-bit PCI local bus.

- On-chip 32-bit DMAC for PCI bus master

- Supports the PERR&SERR function

- Supports the INTA# Interrupt Signals

- Max. 64 bytes burst transfer

- PCI system clock: Max. 33 MHz

- Data Bus Parity and Address Bus Parity (only for PCI bus interface mode) generation/check function

#### Others

- Compact 144-Pin Plastic Low Profile Shrink Quad Flat Package (LQFP, Package Suffix: -PMT)

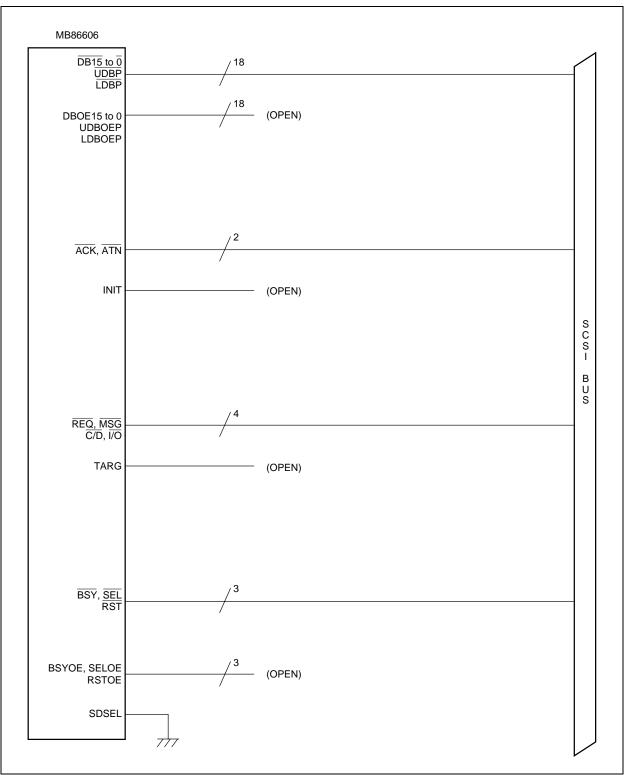

- Pin compatible with MB86606

- Supply Voltage: 5 V ±5%

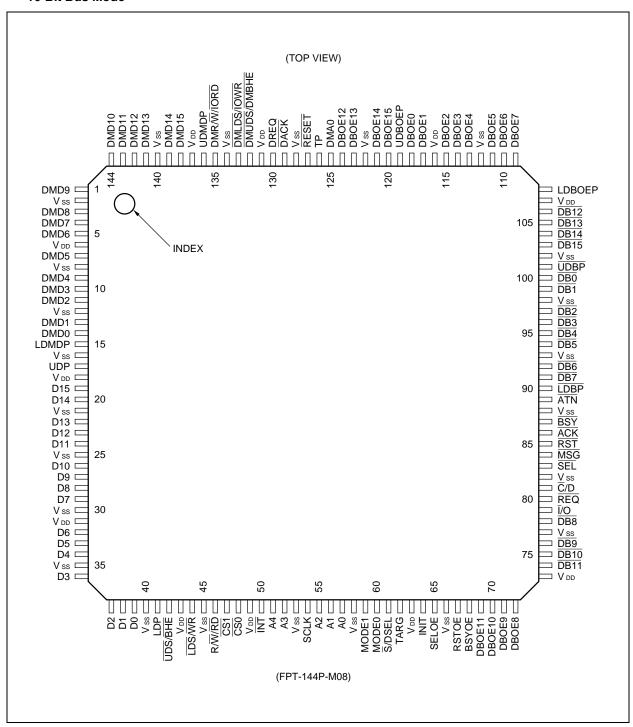

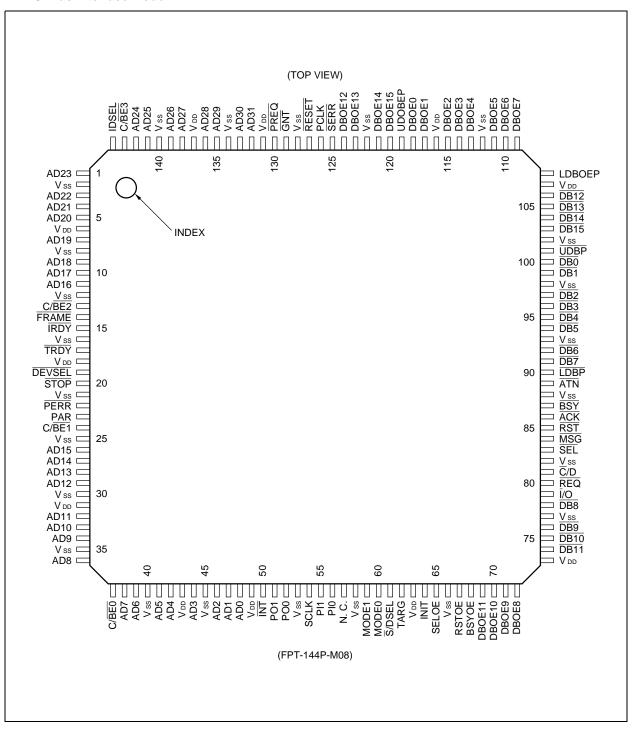

#### **■ PIN ASSIGNMENT**

#### • 16-Bit Bus Mode

#### PCI Bus Interface Mode

# ■ PIN LIST

| Pin |     | 16-bit bus mode |      |              | PCI bus<br>I/F mode |               | Pin |          | 16-bit bus mode |     |              |      | PCI bus<br>I/F mode |  |

|-----|-----|-----------------|------|--------------|---------------------|---------------|-----|----------|-----------------|-----|--------------|------|---------------------|--|

| no. | Mod | e 0 (68 I/F)    | Mod  | e 1 (80 I/F) | Mod                 | e 3 (PCI I/F) | no. | Mod      | e 0 (68 l/F)    | Mod | e 1 (80 I/F) | Mod  | Mode 3 (PCI I/F)    |  |

|     | I/O | Pin name        | I/O  | Pin name     | I/O                 | Pin name      |     | I/O      | Pin name        | I/O | Pin name     | I/O  | Pin name            |  |

| 1   | I/O | DMD9            |      |              | I/O                 | AD23          | 31  | _        | V <sub>DD</sub> |     |              |      |                     |  |

| 2   | _   | Vss             |      |              |                     |               | 32  | I/O      | D6              |     |              |      | AD11                |  |

| 3   | I/O | DMD8            | DMD8 |              |                     | AD22          | 33  | I/O      | D5              |     |              | I/O  | AD10                |  |

| 4   | I/O | DMD7            |      |              | I/O                 | AD21          | 34  | I/O      | D4              |     |              | I/O  | AD9                 |  |

| 5   | I/O | DMD6            |      |              | I/O                 | AD20          | 35  | _        | Vss             |     |              |      |                     |  |

| 6   | _   | V <sub>DD</sub> |      |              |                     |               | 36  | I/O      | D3              |     |              | I/O  | AD8                 |  |

| 7   | I/O | DMD5            |      |              | I/O                 | AD19          | 37  | I/O      | D2              |     |              | I/O  | C/BE0               |  |

| 8   |     | Vss             |      |              |                     |               | 38  | I/O      | D1              |     |              | I/O  | AD7                 |  |

| 9   | I/O | DMD4            |      |              | I/O                 | AD18          | 39  | I/O      | D0              |     |              | I/O  | AD6                 |  |

| 10  | I/O | DMD3            |      |              | I/O                 | AD17          | 40  | _        | Vss             |     |              |      | 1                   |  |

| 11  | I/O | DMD2            |      |              | I/O                 | AD16          | 41  | I/O      | LDP             |     |              | I/O  | AD5                 |  |

| 12  | _   | Vss             |      |              |                     |               | 42  | I        | UDS             | I   | BHE          | I/O  | AD4                 |  |

| 13  | I/O | DMD1            |      |              | I/O                 | C/BE2         | 43  | _        | V <sub>DD</sub> | •   | !            |      | 1                   |  |

| 14  | I/O | DMD0            |      |              | I/O                 | FRAME         | 44  | I        | LDS             | ı   | WR           | I/O  | AD3                 |  |

| 15  | I/O | LDMDP           |      |              | I/O                 | IRDY          | 45  | _        | Vss             |     | 1            |      | 1                   |  |

| 16  |     | Vss             |      |              |                     |               | 46  | I        | R/W             | I   | RD           | I/O  | AD2                 |  |

| 17  | I/O | UDP             |      |              | I/O                 | TRDY          | 47  | I        | CS1             |     |              | I/O  | AD1                 |  |

| 18  | _   | V <sub>DD</sub> |      |              |                     |               | 48  | I        | CS0             |     |              | I/O  | AD0                 |  |

| 19  | I/O | D15             |      |              | I/O                 | DEVSEL        | 49  | _        | V <sub>DD</sub> |     |              |      |                     |  |

| 20  | I/O | D14             |      |              | I/O                 | STOP          | 50  | 0/<br>OD | INT             |     |              |      |                     |  |

| 21  |     | Vss             |      |              |                     | 1             | 51  | I        | A4              |     |              | 0    | PO1                 |  |

| 22  | I/O | D13             |      |              | I/O                 | PERR          | 52  | I        | A3              |     |              | 0    | PO0                 |  |

| 23  | I/O | D12             |      |              | I/O                 | PAR           | 53  | _        | Vss             |     |              |      | 1                   |  |

| 24  | I/O | D11             |      |              | I/O                 | C/BE1         | 54  | I        | SCLK            |     |              |      |                     |  |

| 25  | _   | Vss             |      |              |                     | 1             | 55  | IU       | A2              |     |              | IU   | PI1                 |  |

| 26  | I/O | D10             |      |              | I/O                 | AD15          | 56  | IU       | A1              |     |              | IU   | PI0                 |  |

| 27  | I/O | D9              |      | I/O          | AD14                | 57            | IU  | A0       |                 |     | IU           | N.C. |                     |  |

| 28  | I/O | D8              |      |              | I/O                 | AD13          | 58  | _        | Vss             |     |              | 1    | 1                   |  |

| 29  | I/O | D7              |      |              | I/O                 | AD12          | 59  | ı        | MODE1           |     |              |      |                     |  |

| 30  | _   | Vss             |      |              |                     | 1             | 60  | ı        | MODE2           |     |              |      |                     |  |

(Continued)

| Pin |     | 16-bit bu       | us mo | ode                       | F<br>I/ | PCI bus<br>F mode     | Pin | 16-bit bus mode |                              |     |          | PCI bus<br>I/F mode |               |

|-----|-----|-----------------|-------|---------------------------|---------|-----------------------|-----|-----------------|------------------------------|-----|----------|---------------------|---------------|

| no. | Mod | e 0 (68 I/F)    | Mod   | Mode 1 (80 I/F) Mode 3 (P |         | I/F) Mode 3 (PCI I/F) |     | Mod             | e 0 (68 I/F) Mode 1 (80 I/F) |     |          | Mod                 | e 3 (PCI I/F) |

|     | I/O | Pin name        | I/O   | Pin name                  | I/O     | Pin name              |     | I/O             | Pin name                     | I/O | Pin name | I/O                 | Pin name      |

| 61  | I   | S/DSEL          |       |                           |         |                       | 91  | I/O             | DB7                          |     |          |                     |               |

| 62  | 0   | TARG            |       |                           |         |                       | 92  | I/O             | DB6                          |     |          |                     |               |

| 63  | _   | V <sub>DD</sub> |       |                           |         |                       | 93  | _               | Vss                          |     |          |                     |               |

| 64  | 0   | INIT            |       |                           |         |                       | 94  | I/O             | DB5                          |     |          |                     |               |

| 65  | 0   | SELOE           |       |                           |         |                       | 95  | I/O             | DB4                          |     |          |                     |               |

| 66  |     | Vss             |       |                           |         |                       | 96  | I/O             | DB3                          |     |          |                     |               |

| 67  | 0   | RSTOE           |       |                           |         |                       | 97  | I/O             | DB2                          |     |          |                     |               |

| 68  | 0   | BSYOE           |       |                           |         |                       | 98  | _               | Vss                          |     |          |                     |               |

| 69  | 0   | DBOE11          |       |                           |         |                       | 99  | I/O             | DB1                          |     |          |                     |               |

| 70  | 0   | DBOE10          |       |                           |         |                       | 100 | I/O             | DB0                          |     |          |                     |               |

| 71  | 0   | DBOE9           |       |                           |         |                       | 101 | I/O             | UDBP                         |     |          |                     |               |

| 72  | 0   | DBOE8           |       |                           |         |                       | 102 | _               | Vss                          |     |          |                     |               |

| 73  | _   | V <sub>DD</sub> |       |                           |         |                       | 103 | I/O             | DB15                         |     |          |                     |               |

| 74  | I/O | DB11            |       |                           |         |                       | 104 | I/O             | DB14                         |     |          |                     |               |

| 75  | I/O | DB10            |       |                           |         |                       | 105 | I/O             | DB13                         |     |          |                     |               |

| 76  | I/O | DB9             |       |                           |         |                       | 106 | I/O             | DB12                         |     |          |                     |               |

| 77  | _   | Vss             |       |                           |         |                       | 107 | _               | V <sub>DD</sub>              |     |          |                     |               |

| 78  | I/O | DB8             |       |                           |         |                       | 108 | 0               | LDBOEP                       |     |          |                     |               |

| 79  | I/O | T/O             |       |                           |         |                       | 109 | 0               | DBOE7                        |     |          |                     |               |

| 80  | I/O | REQ             |       |                           |         |                       | 110 | 0               | DBOE6                        |     |          |                     |               |

| 81  | I/O | C/D             |       |                           |         |                       | 111 | 0               | DBOE5                        |     |          |                     |               |

| 82  | _   | Vss             |       |                           |         |                       | 112 |                 | Vss                          |     |          |                     |               |

| 83  | I/O | SEL             |       |                           |         |                       | 113 | 0               | DBOE4                        |     |          |                     |               |

| 84  | I/O | MSG             |       |                           |         |                       | 114 | 0               | DBOE3                        |     |          |                     |               |

| 85  | I/O | RST             |       |                           |         |                       | 115 | 0               | DBOE2                        |     |          |                     |               |

| 86  | I/O | ACK             |       |                           |         |                       | 116 | _               | V <sub>DD</sub>              |     |          |                     |               |

| 87  | I/O | BSY             |       |                           |         |                       | 117 | 0               | DBOE1                        |     |          |                     |               |

| 88  | _   | Vss             |       |                           |         |                       | 118 | 0               | DBOE0                        |     |          |                     |               |

| 89  | I/O | ATN             |       |                           |         |                       | 119 | 0               | UDBOEP                       |     |          |                     |               |

| 90  | I/O | LDBP            |       |                           |         |                       | 120 | 0               | DBOE15                       |     |          |                     |               |

(Continued)

(Continued)

| Continued |                 |                 |              |                  |     |                     |                 |                 |                 |       |                  |                     |          |

|-----------|-----------------|-----------------|--------------|------------------|-----|---------------------|-----------------|-----------------|-----------------|-------|------------------|---------------------|----------|

| Pin       | 16-bit bus mode |                 |              |                  |     | PCI bus<br>I/F mode |                 | 16-bit bus mode |                 |       |                  | PCI bus<br>I/F mode |          |

| no.       |                 |                 | e 1 (80 I/F) | Mode 3 (PCI I/F) |     | no.                 | Mode 0 (68 I/F) |                 | Mode 1 (80 I/F) |       | Mode 3 (PCI I/F) |                     |          |

|           | I/O             | Pin name        | I/O          | Pin name         | I/O | Pin name            |                 | I/O             | Pin name        | I/O   | Pin name         | I/O                 | Pin name |

| 121       | 0               | DBOE14          |              |                  |     |                     | 133             | I               | DMLDS           | I     | IOWR             | I/O                 | AD30     |

| 122       | _               | Vss             |              |                  |     |                     | 134             | _               | Vss             |       | •                |                     | ·        |

| 123       | 0               | DBOE13          |              |                  |     |                     |                 | I               | DMR/W           | I     | IORD             | I/O                 | AD29     |

| 124       | 0               | DBOE12          |              |                  |     |                     | 136             | I/O             | UDMDP           |       |                  | I/O                 | AD28     |

| 125       | I               | DMA0            | DMA0 OD SERR |                  |     |                     | 137             | _               | V <sub>DD</sub> |       |                  |                     |          |

| 126       | I               | TP              |              |                  | I   | PCLK                | 138             | I/O             | DMD15           |       |                  | I/O                 | AD27     |

| 127       | I               | RESET           |              |                  | •   | •                   | 139             | I/O             | DMD14           |       |                  | I/O                 | AD26     |

| 128       | _               | Vss             |              |                  |     |                     | 140             | _               | Vss             |       |                  |                     |          |

| 129       | I               | DACK            |              |                  | I   | GNT                 | 141             | I/O             | DMD13           | DMD13 |                  |                     | AD25     |

| 130       | 0               | DREQ            |              |                  | 0   | PREQ                | 142             | I/O             | DMD12           |       | I/O              | AD24                |          |

| 131       | _               | V <sub>DD</sub> |              |                  |     |                     | 143             | I/O             | DMD11           |       | I/O              | C/BE3               |          |

| 132       | Į               | DMUDS           | I            | DMBHE            | I/O | AD31                | 144             | I/O             | DMD10           |       |                  | I                   | IDSEL    |

I : Input pin O : Output pin

I/O: Input/Output pin

IU: Input pin with pull-up resistor

OD: Open-drain output pin

### **■ PIN DESCRIPTION**

### 1. SCSI Interface

| Pin no.                                                                           | Pin name                                              | I/O | Function                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------|-------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 84, 81<br>89, 79                                                                  | MSG, C/D<br>ATN, I/O                                  | I/O | These are the SCSI control signal input and output pins. They can be connected directly to a single-ended SCSI connector. Either open-drain or totem pole output can be selected.                                                                                 |

| 80, 86                                                                            | REQ, ACK                                              | I/O | These are the SCSI control signal input and output pins. They can be connected directly to a single-ended SCSI connector. The output buffer is the totem pole type.                                                                                               |

| 68<br>65<br>67                                                                    | BSYOE<br>SELOE<br>RSTOE                               | 0   | These are used for output control of SCSI control signals.  They should be used as control signals for the external differential driver/receiver circuit.                                                                                                         |

| 87<br>83<br>85                                                                    | BSY<br>SEL<br>RST                                     | I/O | These are the SCSI control signal input and output pins. They can be connected directly to a single-ended SCSI connector. The output buffer is the open-drain type.                                                                                               |

| 120, 121, 123, 124, 69 to 72<br>119<br>109 to 111, 113 to 115,<br>117, 118<br>108 | DBOE15 to DBOE8<br>UDBOEP<br>DBOE7 to DBOE0<br>LDBOEP | 0   | These are used for output control of SCSI data bus signals. They should be used as control signals for the external differential driver/receiver circuit.                                                                                                         |

| 103 to 106, 74 to 76, 78<br>101<br>91, 92, 94 to 97, 99, 100<br>90                | DB15 to DB8<br>UDBP<br>DB7 to DB0<br>LDBP             | I/O | These are used to input and output SCSI data bus signals. They can be connected directly to a single-ended SCSI connector. Either open-drain or totem pole output buffer can be selected.                                                                         |

| 64<br>62                                                                          | INIT<br>TARG                                          | 0   | These are used to output signals indicating the chip operating status.  They should be used as control signals for the external differential driver/receiver circuit.                                                                                             |

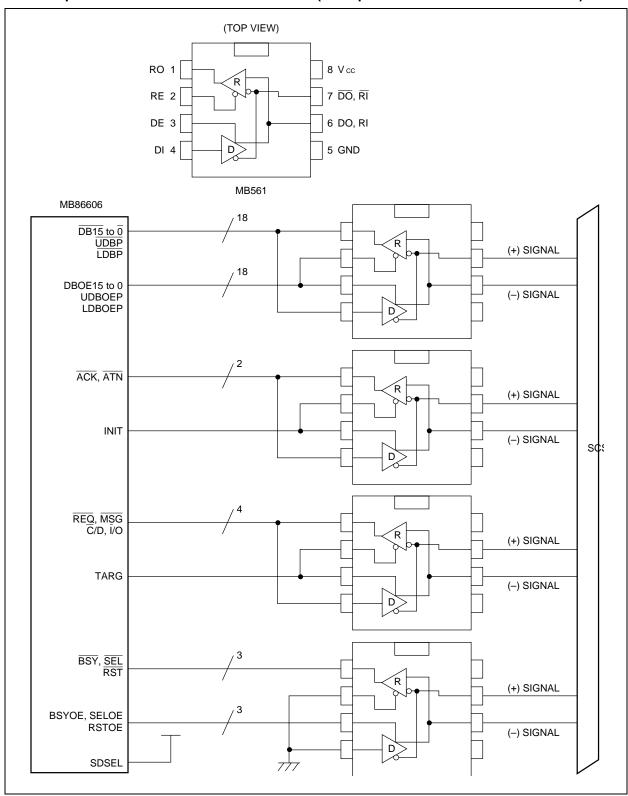

| 61                                                                                | S/DSEL                                                | I   | This is used to input signal for selecting the chip operation mode. Single-ended: Input 0 Differential-ended: Input 1 While 0 is input to this pin, all the SCSI control signals, data bus output control signals, INIT, and TARG signals are fixed with L level. |

| 54                                                                                | SCLK                                                  | I   | This pin is used for a system clock input for SCSI protocol controller block. (Max. 40 MHz)                                                                                                                                                                       |

### 2. 16-Bit Bus Mode - MPU Interface

| Pin no.                          | Pin name         | I/O | Function                                                                                                                                         |

|----------------------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 48                               | CS0              | I   | This is used to input signals for the MPU to select the SPC as the I/O device.                                                                   |

| 47                               | CS1              | I   | This is used to input select signals (external circuit select signals) for the MPU to input and output the DMA data bus data via the SPC.        |

| 19, 20, 22 to 24, 26 to 28<br>17 | D15 to D8<br>UDP | I/O | Upper byte and parity of data bus When CS0 input valid: I/O ports for internal registers in SPC When CS1 input valid: I/O ports for DMA bus data |

| 29, 32 to 34, 36 to 39<br>41     | D7 to D0<br>LDP  | I/O | Lower byte and parity of data bus When CS0 input valid: I/O ports for internal registers in SPC When CS1 input valid: I/O ports for DMA bus data |

(Continued)

# (Continued)

| Pin no.          | Pin name  | I/O | Function                                                                                                                                                                                                                                         |

|------------------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51, 52, 55 to 57 | A4 to A0  | IU  | These are used to input addresses for selecting the Internal registers.                                                                                                                                                                          |

| 46               | RD (R/W)  | I   | In 80-series mode: This is used to input the read strobe signal for reading data from the SPC to the MPU.  In 68-series mode: This is used to input the R/W control signal for reading and writing data from the MPU to the SPC.                 |

| 44               | WR (LDS)  | I   | In 80-series mode: This is used to input the write strobe signal for writing data from the MPU to the SPC.  In 68-series mode: This is used to input the LDS signal output by the MPU when the lower byte of the data bus is valid.              |

| 42               | BHE (UDS) | I   | In 80-series mode: This is used to input the BHE signal output by the MPU when the upper byte of the data bus is valid.  In 68-series mode: This is used to input the UDS signal output by the MPU when the upper byte of the data bus is valid. |

### 3. 16-Bit Bus Mode - DMA Interface

| Pin no.                           | Pin name            | I/O | Function                                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 130                               | DREQ                | 0   | This is used to output DMA transfer request signals to the DMAC. DMA data transfer between the SPC and memory is requested.                                                                                                                  |  |  |  |

| 129                               | DACK                | I   | This is used to input DMA-enabling signals from the DMAC. When the DMA enabling signal is active, DMA reading and writin are executed.                                                                                                       |  |  |  |

| 138, 139, 141 to 144, 1, 3<br>136 | DMD15 to 8<br>UDMDP | I/O | Upper byte and parity of DMA data bus When CS1 input valid: The MPU data bus is directly connected. When 80-series mode: The 2nd data is input/output. When 68-series mode: The 1st data is input/output.                                    |  |  |  |

| 4, 5, 7, 9 to 11, 13, 14<br>15    | DMD7 to 0<br>LDMDP  | I/O | Lower byte and parity of DMA data bus When CS1 input valid: The MPU data bus is directly connected. When 80-series mode: The 1st data is input/output. When 68-series mode: The 2nd data is input/output.                                    |  |  |  |

| 135                               | IORD<br>(DMR/W)     | I   | In 80-series mode: This is used to input the IORD or RD signal for outputting data from the SPC to the DMA bus. In 68-series mode: This is used to input the R/W control signal for outputting and inputting data from the DMAC to the SPC.  |  |  |  |

| 133                               | TOWR<br>(DMLDS)     | I   | In 80-series mode: This is used to input the IOWR or WR signal for inputting data from the DMA bus to the SPC.  In 68-series mode: This is used to input the LDS signal output by the DMAC when the lower byte of the DMA data bus is valid. |  |  |  |

(Continued)

### (Continued)

| Pin no. | Pin name                       | I/O | Function                                                                                                                                                                                                                                                   |

|---------|--------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132     | DMBHE<br>(DMUDS)               | I   | In 80-series mode: This is used to input the BHE signal output by the DMAC when the upper byte of the DMA data bus is valid.  In 68-series mode: This is used to input the UDS signal output by the DMAC when the upper byte of the DMA data bus is valid. |

| 125     | DMA0                           | I   | This is used to input the address data A0 signal output by the DMAC in the 80-series mode. In 68-series mode: Connect to power supply pin (VDD).                                                                                                           |

| 126     | TP<br>(Transfer<br>permission) | I   | This is used to input DMA-transfer-enabling signals. When the TP signal is active, the SPC performs the DMA transfer. When this signal becomes inactive during DMA transfer, the transfer stops temporarily at the block boundary.                         |

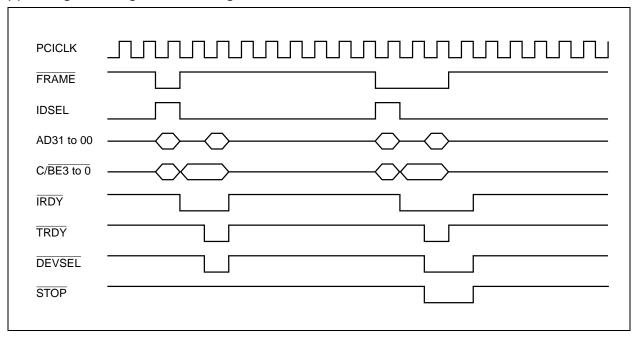

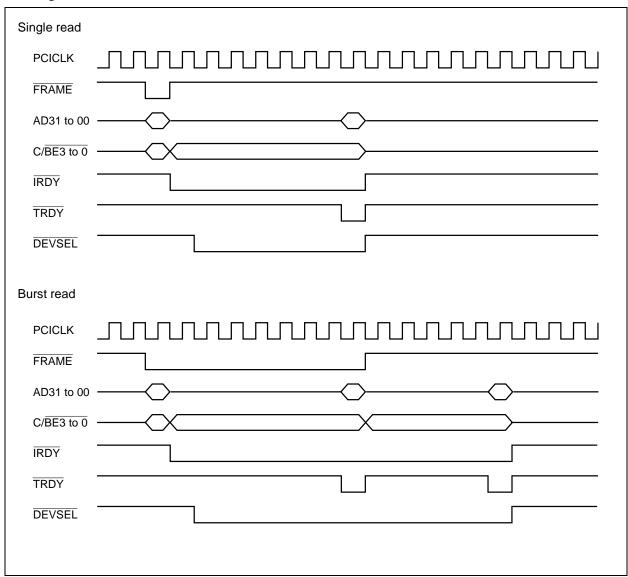

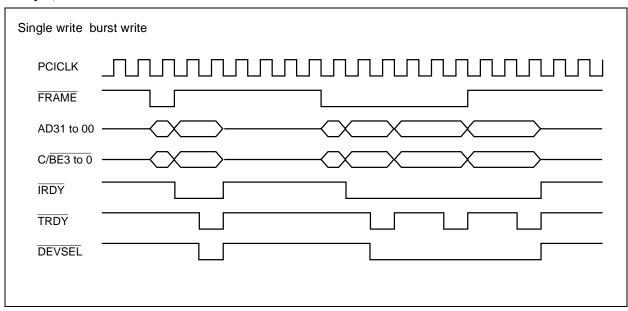

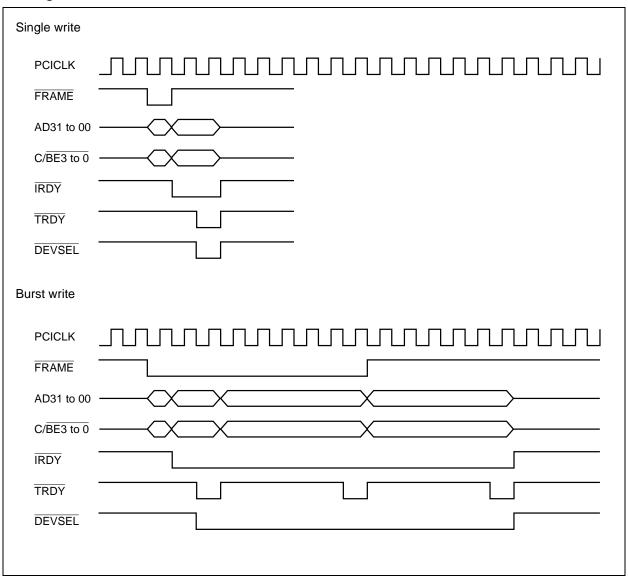

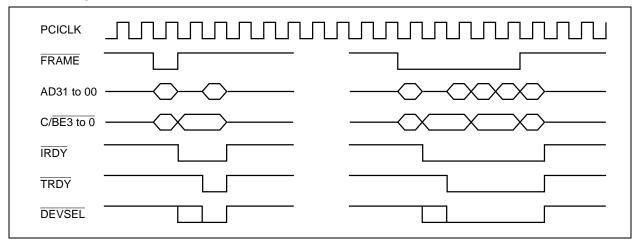

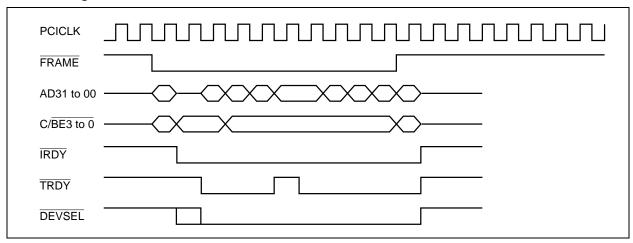

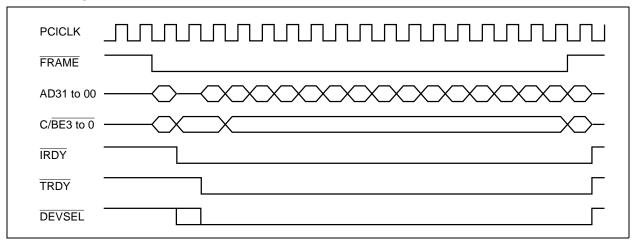

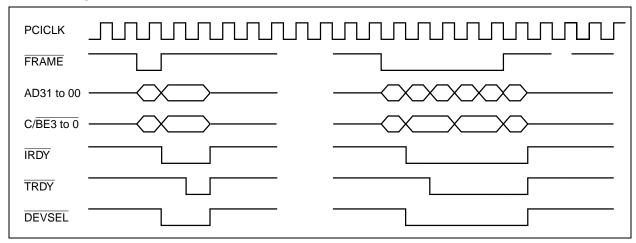

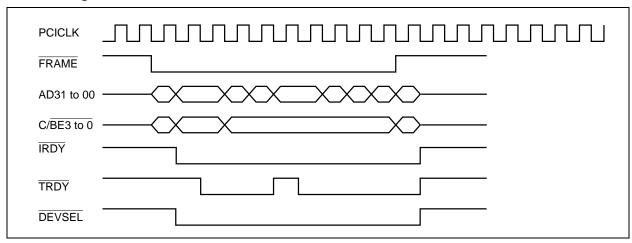

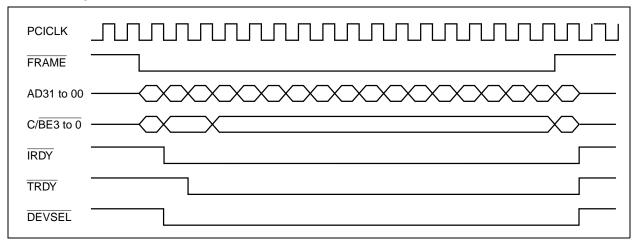

### 4. PCI Bus Interface Mode

| Pin no.                                                                                                                            | Pin name       | I/O | Function                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130                                                                                                                                | PREQ           | 0   | This pin is used to request the bus arbiter for use of the bus.                                                                                                                                                                                   |

| 129                                                                                                                                | GNT            | I   | This is the response signal input pin to the $\overline{\text{REQ}}$ signal from the bus arbiter.                                                                                                                                                 |

| 132, 133, 135, 136,<br>138, 139, 141, 142,<br>1, 3 to 5, 7, 9 to 11,<br>26 to 29, 32 to 34, 36,<br>38, 39, 41, 42, 44,<br>46 to 48 | AD31 to AD0    | I/O | PCI 32-bit address and data multiplexed pins                                                                                                                                                                                                      |

| 143, 13, 24, 37                                                                                                                    | C/BE3 to C/BE0 | I/O | Bus command and Byte Enable signals multiplexed pins.                                                                                                                                                                                             |

| 23                                                                                                                                 | PAR            | I/O | This is an even parity signal pin for the AD31 to AD0 and C/BE3 to C/BE0 signals. This PAR signal becomes valid after one clock.                                                                                                                  |

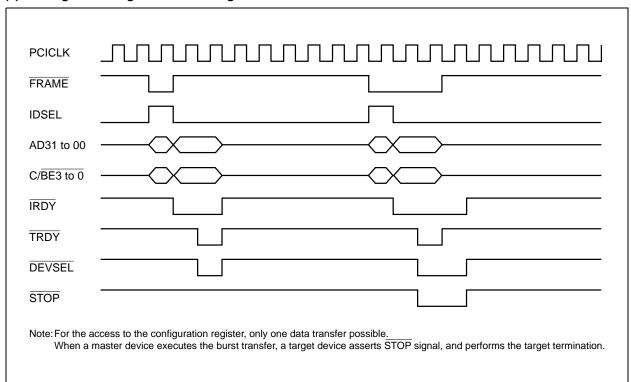

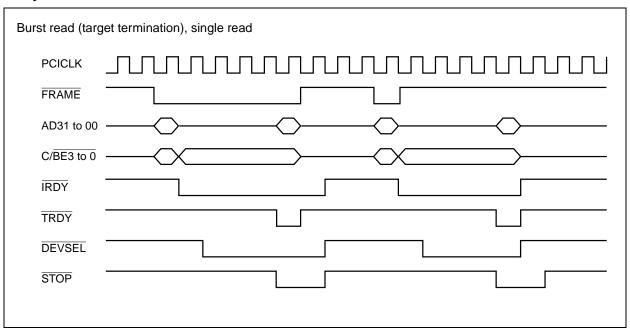

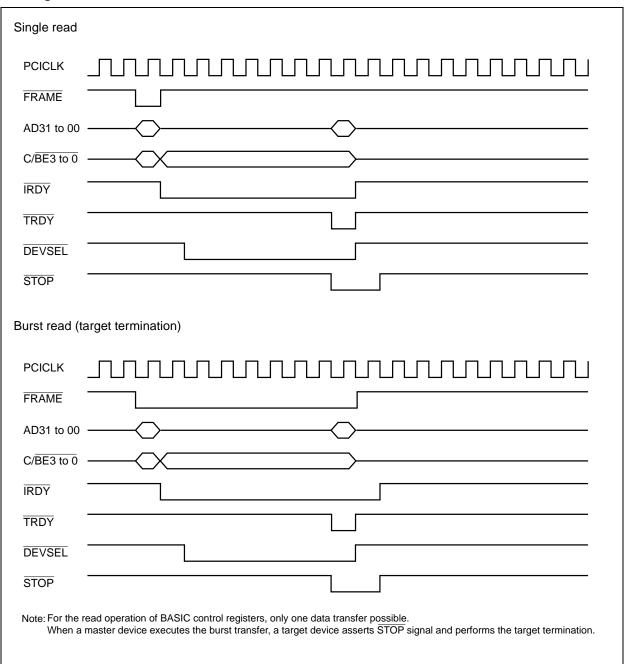

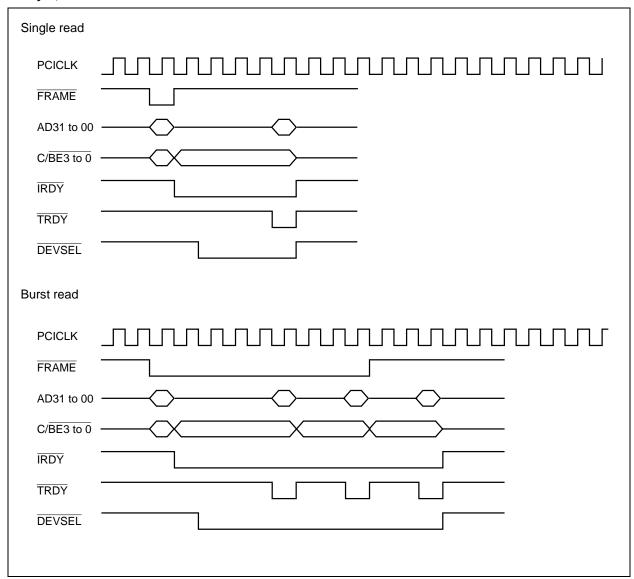

| 14                                                                                                                                 | FRAME          | I/O | This is a frame signal pin that indicates data are transferring on the bus.                                                                                                                                                                       |

| 17                                                                                                                                 | TRDY           | I/O | Data Ready signal of Target side.                                                                                                                                                                                                                 |

| 15                                                                                                                                 | IRDY           | I/O | Data Ready signal of Initiator (Bus master) side.                                                                                                                                                                                                 |

| 20                                                                                                                                 | STOP           | I/O | This is a stop request signal to stop the data transfer from target to master.                                                                                                                                                                    |

| 19                                                                                                                                 | DEVSEL         | I/O | Device select pin. While the device is a target, this pin outputs the select signal that indicates the self device is selected. While the device is a master this pin functions as an input pin to indicate that a device on the bus is selected. |

| 144                                                                                                                                | IDSEL          |     | This is a chip select signal that indicates the configuration access.                                                                                                                                                                             |

| 126                                                                                                                                | PCLK           | I   | PCI bus clock input pin. The maximum clock frequency is 33 MHz.                                                                                                                                                                                   |

| 22                                                                                                                                 | PERR           | I/O | Data parity error input and output pin.                                                                                                                                                                                                           |

| 125                                                                                                                                | SERR           | OD  | Address parity error output pin.                                                                                                                                                                                                                  |

# 5. Other Signals

| Pin no.                                                                                            | Pin name        | I/O      |                                                                                                                                                                                               |               | Function                                                                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------|--|--|--|--|

| 127                                                                                                | RESET           | 0        | This pin is us                                                                                                                                                                                | ed to input s | ystem reset signals.                                                             |  |  |  |  |

| 59, 60                                                                                             | MODE1,<br>MODE0 | I        | These pins ar listed in the ta                                                                                                                                                                |               | etting the device operation mode as                                              |  |  |  |  |

|                                                                                                    |                 |          | MODE1 MODE0 Operation Mode                                                                                                                                                                    |               |                                                                                  |  |  |  |  |

|                                                                                                    |                 |          | 0                                                                                                                                                                                             | 0             | 16-bit bus mode (68 series mode)                                                 |  |  |  |  |

|                                                                                                    |                 |          | 0                                                                                                                                                                                             | 1             | 16-bit bus mode (80 series mode)                                                 |  |  |  |  |

|                                                                                                    |                 |          | 1                                                                                                                                                                                             | 0             | Reserved                                                                         |  |  |  |  |

|                                                                                                    |                 |          | 1                                                                                                                                                                                             | 1             | PCI bus interface mode                                                           |  |  |  |  |

| 50                                                                                                 | INT             | O/<br>OD | Interrupt output pin. Either totem pole or open-drain output buffer can be selected. This pin has an internal pull-up resistor.                                                               |               |                                                                                  |  |  |  |  |

| 6, 18, 31, 43, 49, 63,<br>73, 107, 116, 131,<br>137                                                | V <sub>DD</sub> |          | Power supply pin                                                                                                                                                                              |               |                                                                                  |  |  |  |  |

| 2, 8, 12, 16, 21, 25, 30, 35, 40, 45, 53, 58, 66, 77, 82, 88, 93, 98, 102, 112, 122, 128, 134, 140 | Vss             | _        | Ground pin                                                                                                                                                                                    |               |                                                                                  |  |  |  |  |

| 51, 52                                                                                             | PO1, PO0        |          | General purpose output ports that can control the external active SCSI bus terminator etc. Initial signal level on each pin is "L". Those pins are available only for PCI bus interface mode. |               |                                                                                  |  |  |  |  |

| 55, 56                                                                                             | PI1, PI0        | IU       | General purpomode.                                                                                                                                                                            | ose input po  | rts. Available only for PCI bus interface                                        |  |  |  |  |

| 57                                                                                                 | N.C.            | _        |                                                                                                                                                                                               |               | d pins. These pins exist on the only PCI rnally pulled-up, and do not connect to |  |  |  |  |

I : Input pin

O: Output pin I/O: Input and Output pin OD : Open-drain output pin

IU: Input pin with pull-up resistor

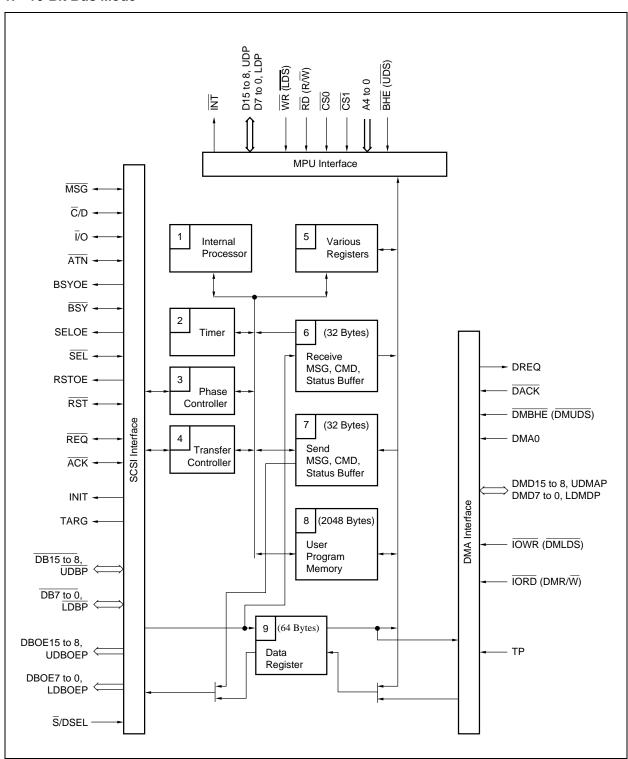

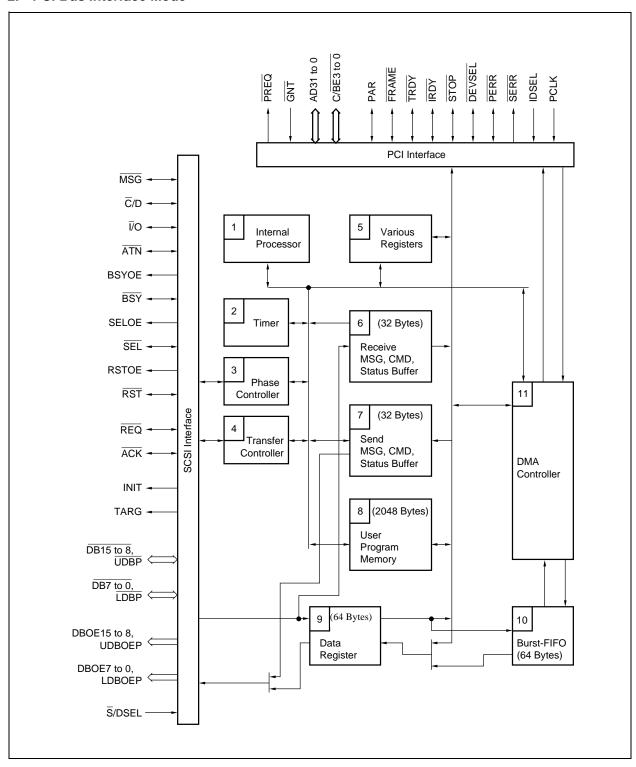

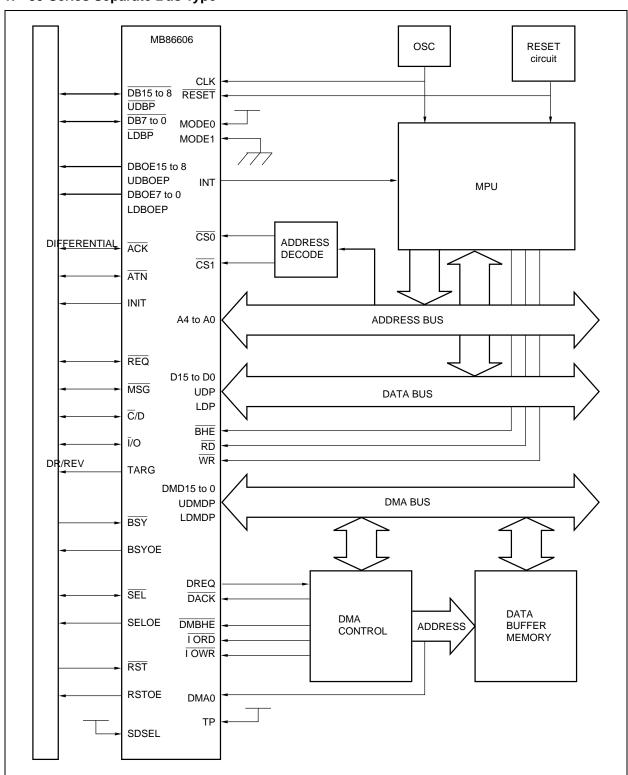

#### **■ BLOCK DIAGRAM**

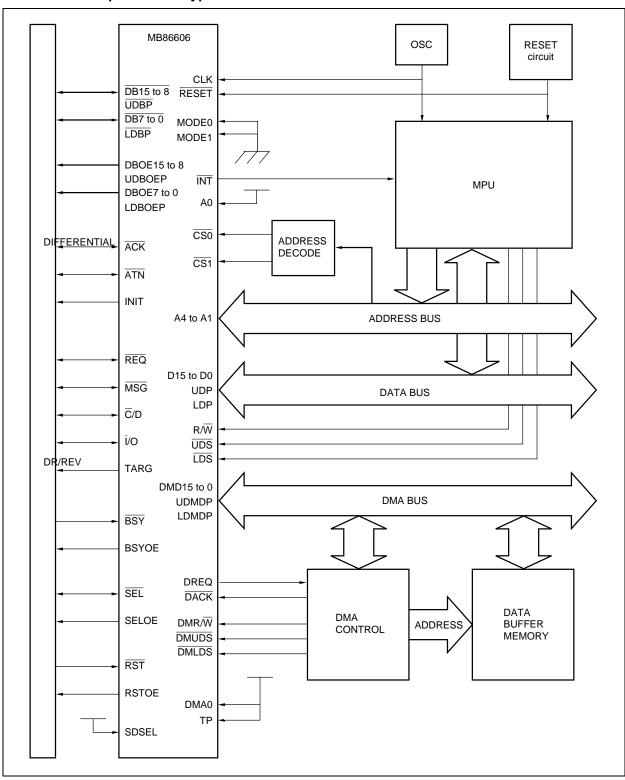

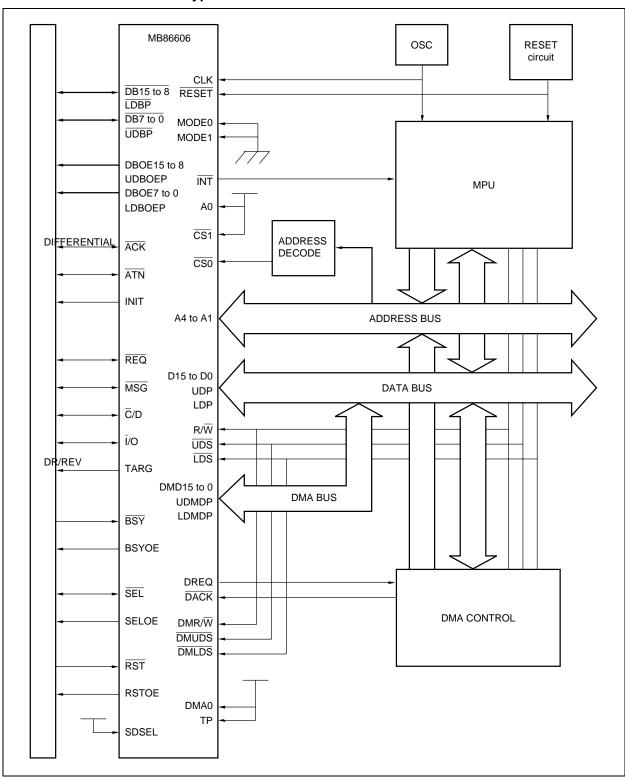

#### 1. 16-Bit Bus Mode

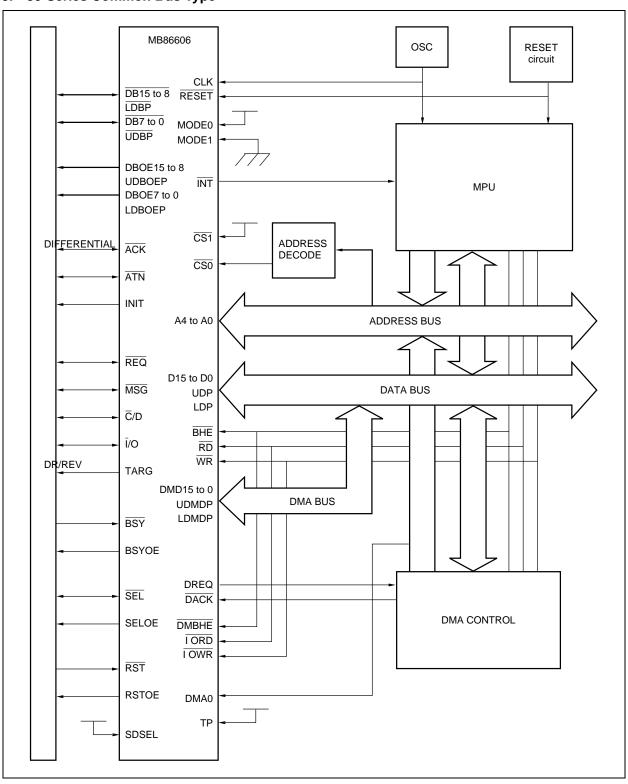

#### 2. PCI Bus Interface Mode

#### BLOCK FUNCTIONS

#### 1. Internal Processor

This processor provides the sequence control between each phase.

#### 2. Timer

This timer manages the time specified by SCSI and the following time:

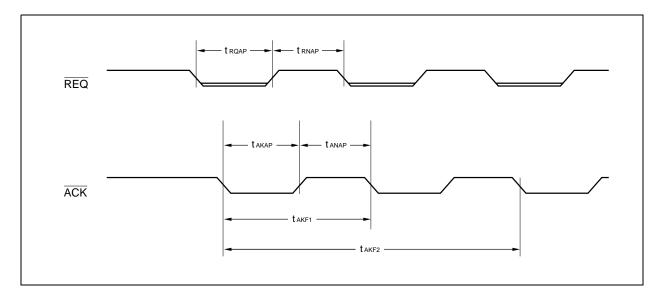

- · REQ/ACK assertion time for data at asynchronous transfer

- · Selection/reselection retry time

- Selection/reselection timeout time

- REQ/ACK timeout time during transfer

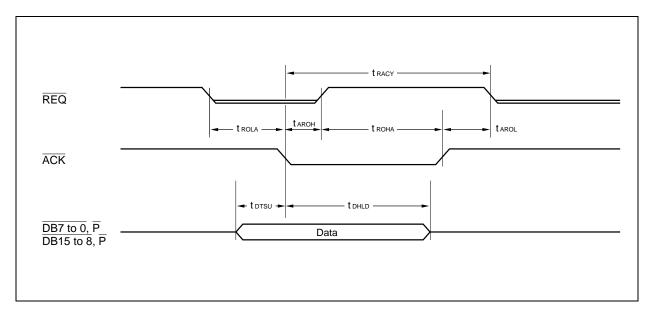

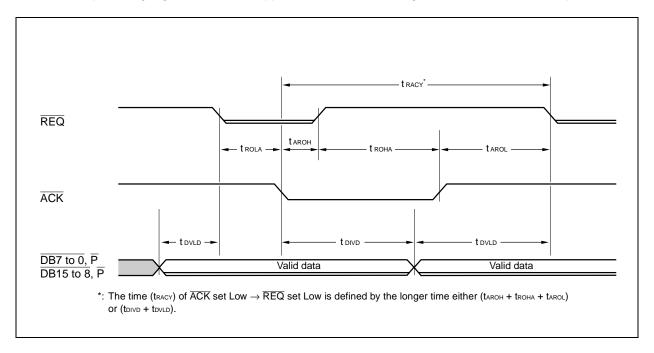

Asynchronous transfer (target) : Time required for initiator to assert ACK signal after asserting REQ

Asynchronous transfer (initiator) : Time required for target to negate REQ signal after asserting ACK signal

Synchronous transfer (target only): Time required for target to receive ACK signal for setting offset value to

0 from initiator after sending REQ signal

#### 3. Phase Controller

This controller controls the arbitration, selection/reselection, data-in/out, command, status, and message-in/out phases executed on the SCSI bus.

#### Transfer Controller

This controller controls the information (data, command, status, message) transfer phases executed on the SCSI

There are two types of transfer for executing the information transfer phases.

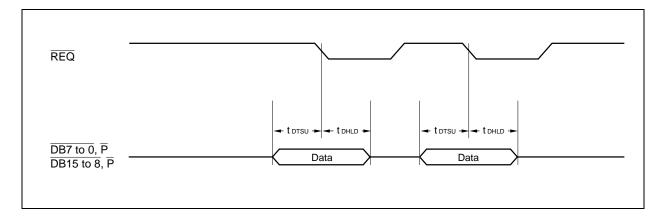

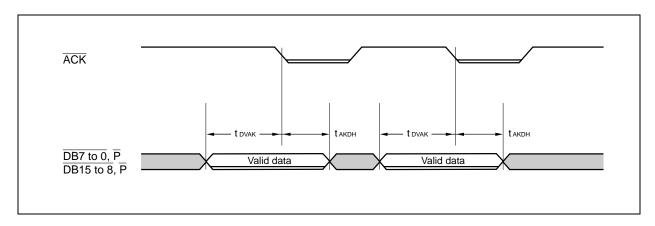

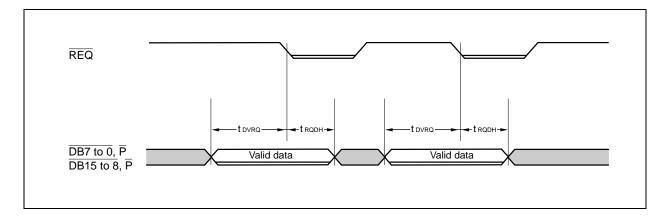

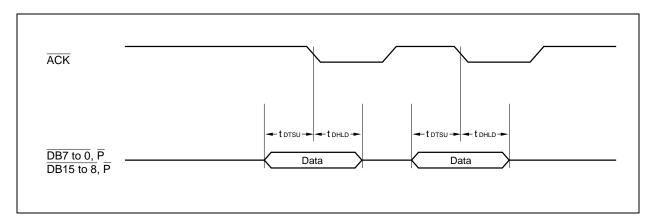

- · Asynchronous transfer: Control by interlocking REQ and ACK signals

- Synchronous transfer: Control with maximum of 32-byte offset value in data-in/out phase

Depending on the data migration, there are the following two modes.

- Program transfer: Performed via MPU interface using data registers

- Performed via DMA interface using DREQ and DACK pins • DMA transfer:

At synchronous transfer, the transfer parameters (transfer mode, minimum cycle period of REQ or ACK signal sent from SPC in synchronous transfer, and maximum value between REQ and ACK signals in synchronous transfer) can be saved for each ID and are automatically set when the data phase is started. The transfer byte count is determined by block length × number of blocks.

#### 5. Various Registers

#### · Command register

This register specifies each command with an 8-bit code.

When using the user program, specify "1" at the Bit 7. The lower 7 bits (Bit6 to Bit0) are invalid.

#### · Nexus status register

This register indicates the chip's operating condition, the nexused partner's ID, and data register status.

#### SCSI control signal status register

This register indicates the status of SCSI control signals.

#### Interrupt status register

This register indicates the interrupt status with an 8-bit code.

#### Command step register

This register indicates the execution status of each command with an 8-bit step code.

Error causes can be analyzed by referencing the interrupt status register and this register.

#### • Group 6/7 command length setting register

This register sets the group 6/7 command length not defined in the SCSI standard.

Setting this register determines the group 6/7 command length.

#### 6. Receive MSG, CMD, Status Buffer (Receive MCS Buffer)

This is a 32-byte receive-only information buffer that holds the information for the message, command, and status received from the SCSI bus.

#### 7. Send MSG, CMD, Status Buffer (Send MCS Buffer)

This is a 32-byte send-only information buffer that holds the information for the message, command, and status sent on the SCSI bus.

#### 8. User Program Memory

This is a 2048-byte program memory that stores programmable commands. It can consist of 1024-byte  $\times$  2 banks or 2048-byte  $\times$  1 bank.

#### 9. Data Register

This is a 64-byte FIFO data register that holds data in the data phase executed on the SCSI bus.

#### 10. Burst FIFO

64-byte FIFO type data buffer to perform burst transfer during the PCI bus interface mode. The device has total 128-byte FIFO with Data Register and Burst FIFO in the PCI bus interface mode.

#### 11. DMA Controller

This is a 32-bit DMA Controller that performs data transfer. This DMAC is a bus master during the PCI bus interface mode.

### ■ ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter                     | Symbol          | Rat       | Unit                  |       |  |

|-------------------------------|-----------------|-----------|-----------------------|-------|--|

| Farameter                     | Syllibol        | Min.      | Max.                  | Oilit |  |

| Power supply voltage*         | V <sub>DD</sub> | Vss - 0.5 | 6.0                   | V     |  |

| Input voltage*                | Vı              | Vss - 0.5 | V <sub>DD</sub> + 0.5 | V     |  |

| Output voltage*               | Vo              | Vss - 0.5 | V <sub>DD</sub> + 0.5 | V     |  |

| Operating ambient temperature | Тор             | -25       | +85                   | °C    |  |

| Storage temperature           | Tstg            | -40       | +125                  | °C    |  |

<sup>\*:</sup> The voltages are based on Vss (= 0 V)

WARNING: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **■ RECOMMENDED OPERATING CONDITIONS**

| Davamatar                  | C. mah al        |      | - Unit |      |       |  |

|----------------------------|------------------|------|--------|------|-------|--|

| Parameter                  | Symbol           | Min. | Тур.   | Max. | Offic |  |

| Power supply voltage*      | V <sub>DD</sub>  | 4.75 | 5.0    | 5.25 | V     |  |

| SCSI clock input frequency | fscsi            | 20.0 | _      | 40.0 | MHz   |  |

| PCI clock input frequency  | f <sub>PCI</sub> |      | _      | 33.0 | MHz   |  |

| Storage temperature        | Та               | 0    | _      | +70  | °C    |  |

<sup>\*:</sup> The voltages are based on Vss (= 0 V)

Note: The recommended operating conditions are the recommended values for assuring normal logic operation of the LSI. Requirements in electrical characteristics (DC and AC characteristics) are assured within the range of the recommended operating conditions.

### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

$(V_{DD} = +5 V \pm 5\%, V_{SS} = 0 V, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$

|             |          | Darameter      |                       |                         | Symbol          | Condition                | Va   | lue  | Unit |

|-------------|----------|----------------|-----------------------|-------------------------|-----------------|--------------------------|------|------|------|

|             |          | Parameter      |                       |                         | Symbol          | Condition                | Min. | Max. | Unit |

|             | CCCI 20  | ina            |                       |                         | Vih             | _                        | 2.0  | _    | V    |

|             | SCSI p   | oiris          |                       |                         | VIL             | _                        | _    | 0.8  | V    |

| Input       | SCLK     | pins           |                       |                         | VIH             | _                        | 2.4  | _    | V    |

| voltage *1  | SDSE     | _ pins         |                       |                         | VIL             | _                        | _    | 0.8  | V    |

|             | Othors   | -i             |                       |                         | VIH             | _                        | 2.0  | _    | V    |

|             | Other p  | DITIS          |                       |                         | VIL             | _                        | _    | 0.8  | V    |

| SCSI-pin i  | nput hys | teresis *1     |                       |                         | V <sub>HW</sub> | _                        | 0.3  | _    | V    |

|             |          |                | REQ, A                | ער                      | Vон             | Iон = -7.0 mA            | 2.0  | 3.24 | V    |

|             |          |                | KEQ, A                | JK.                     | Vol             | IoL = +48.0 mA           | _    | 0.5  | V    |

|             |          | In single-     | RST, BS               | SY, SEL                 | Vol             | IoL = +48.0 mA           | _    | 0.5  | V    |

|             | SCSI     | end mode       |                       | RST, BSY, SEL  Non-3ST. | Vol             | IoL = +48.0 mA           | _    | 0.5  | V    |

|             | pins     |                | Others                | 3ST                     | Vон             | Iон = −7.0 mA            | 2.0  | 3.24 | V    |

| Output      |          |                |                       | 331                     | Vol             | IoL = +48.0 mA           | _    | 0.5  | V    |

| voltage *1  |          | In differentia | al modo               |                         | Vон             | Iон = −7.0 mA            | 2.0  | 3.24 | V    |

|             |          | in dinerenda   | ai iiiou <del>e</del> |                         | Vol             | IoL = +3.2 mA            | _    | 0.4  | V    |

|             | DCI hu   | s interface pi | ne                    |                         | Vон             | Iон = −2.0 mA            | 4.2  | _    | V    |

|             | 1 Ci bu  | s interiace pi | 113                   |                         | Vol             | IoL = +6.0 mA            | _    | 0.55 | V    |

|             | Other p  | nine           |                       |                         | Vон             | Iон = −2.0 mA            | 4.2  | _    | V    |

|             | Outer    | лн <b>о</b>    |                       |                         | Vol             | IoL = +3.2 mA            |      | 0.4  | V    |

| Input leaka | age curr | ent            |                       |                         | lu              | VIN = 0 to VDD           | -10  | +10  | μΑ   |

| Input/outp  | ut leaka | ge current *2  |                       |                         | ILOZ            | $V_{IN} = 0$ to $V_{DD}$ | -10  | +10  | μΑ   |

| Supply cui  | rrent    |                |                       |                         | IDD             | _                        | _    | 130  | mA   |

<sup>3</sup>ST.: Three-state mode

<sup>\*1:</sup> SCSI pins are; UDBP, DB15 to DB8, LDBP, DB7 to DB0, BSY, SEL, RST, ATN, REQ, ACK, MSG, C/D and I/O. (Total 27 pins)

<sup>\*2:</sup> Leak current when the three-state output pin output and the bidirectional bus pin output are in a high impedance state.

### 2. Input/Output Pin Capacitance

| $(V_{DD} = V_{IN} = 0 \text{ V. } f = 1 \text{ MHz. } Ta = +2$ | 25°C) | Ta = + | MHz. | = 1 | V. 1 | $I_{IN} = 0$ | $(V_{DD} = V_{DD})$ | ( |

|----------------------------------------------------------------|-------|--------|------|-----|------|--------------|---------------------|---|

|----------------------------------------------------------------|-------|--------|------|-----|------|--------------|---------------------|---|

| Parameter                    | Din namo         | Pin name Symbol |      | Value |      |  |

|------------------------------|------------------|-----------------|------|-------|------|--|

| raiametei                    | Fili lialile     | Symbol          | Min. | Max.  | Unit |  |

| Input nin conscitones        | SCLK, PCLK (TP)  | C               | _    | 12    | pF   |  |

| Input pin capacitance        | Other input pins | _               | 8    | pF    |      |  |

| Output pin capacitance       |                  | Соит            | _    | 10    | pF   |  |

|                              | Non-SCSI pins    | Cı/o            | _    | 10    | pF   |  |

| Input/output pin capacitance | SCSI pins        | <b>C</b> 1/0    | _    | 25    | pF   |  |

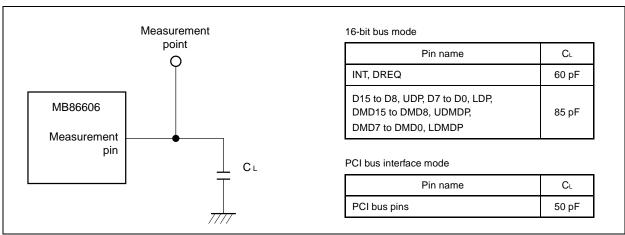

#### 3. Load Conditions for Measurement of AC Characteristics

#### (1) Non-SCSI pins

$$(V_{DD} = +5 V \pm 5\%, V_{SS} = 0 V, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$$

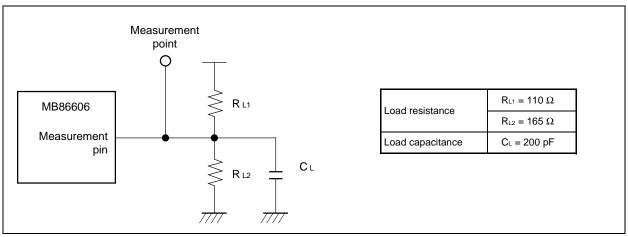

#### (2) SCSI pins

$$(V_{DD} = +5 V \pm 5\%, V_{SS} = 0 V, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$$

#### 4. AC Characteristics

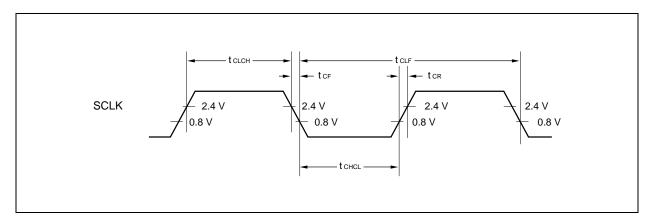

#### (1) System clock

#### • SCSI clock (SCLK pin)

| Parameter                | Symbol        |      | Unit |      |       |

|--------------------------|---------------|------|------|------|-------|

| Farameter                | Symbol        | Min. | Тур. | Max. | Oilit |

| Clock period             | tclf          | 25.0 | _    | 50.0 | ns    |

| Clock pulse width (Low)  | <b>t</b> clch | 10.0 | _    | _    | ns    |

| Clock pulse width (High) | <b>t</b> chcL | 10.0 | _    | _    | ns    |

| Clock pulse rise time    | <b>t</b> cr   | _    | _    | 5.0  | ns    |

| Clock pulse fall time    | <b>t</b> CF   | _    | _    | 5.0  | ns    |

Note: When the internal operating clock frequency is the same as the input clock frequency, (when using the device in divide-by-1 mode), the clock pulse width for L and H levels must have minimum 20.0 ns or longer. (i.e. When the clock conversion register value is 0Bh (address: 10h in the initial setting registers) and input clock frequency = 20 MHz.)

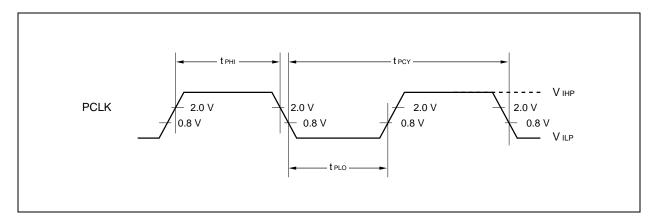

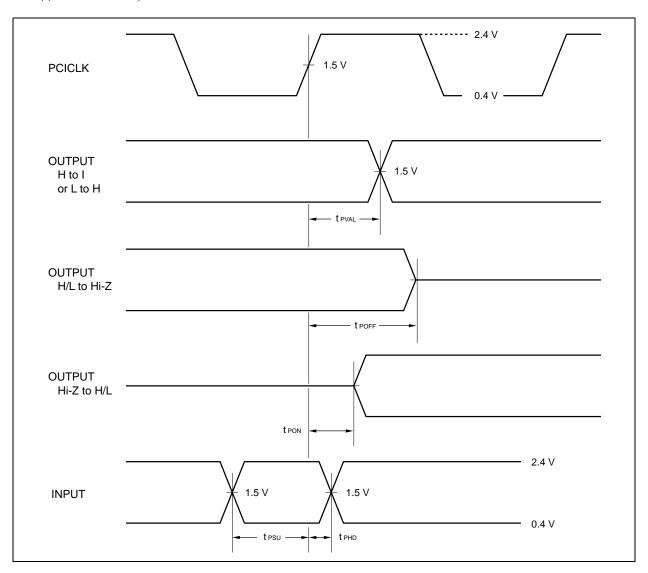

# • PCI clock (PCLK pin)

| Parameter                | Symbol       |      | Value | Unit |       |

|--------------------------|--------------|------|-------|------|-------|

| Farameter                | Symbol       | Min. | Тур.  | Max. | Oille |

| Clock frequency          | <b>t</b> PCY | 30.0 | _     | _    | ns    |

| Clock pulse width (Low)  | <b>t</b> PLO | 12.0 | _     | _    | ns    |

| Clock pulse width (High) | tрні         | 12.0 | _     | _    | ns    |

| Clock slew rate          | <b>t</b> PSR | 1.0  | _     | 4.0  | V/ns  |

| Clock amplitude          | VIHP - VILP  | 2.0  | _     | _    | ns    |

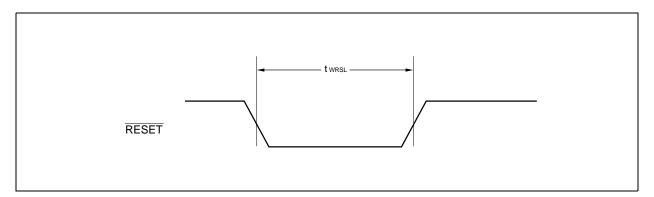

### (2) System reset

| Parameter                                 | Symbol |        | Value |      | Unit  |

|-------------------------------------------|--------|--------|-------|------|-------|

| Parameter                                 | Зуппоп | Min.   | Тур.  | Max. | Offic |

| Reset (RESET) pulse "L" level pulse width | twrsl  | 4 tclf | _     | _    | ns    |

### 5. MPU Interface

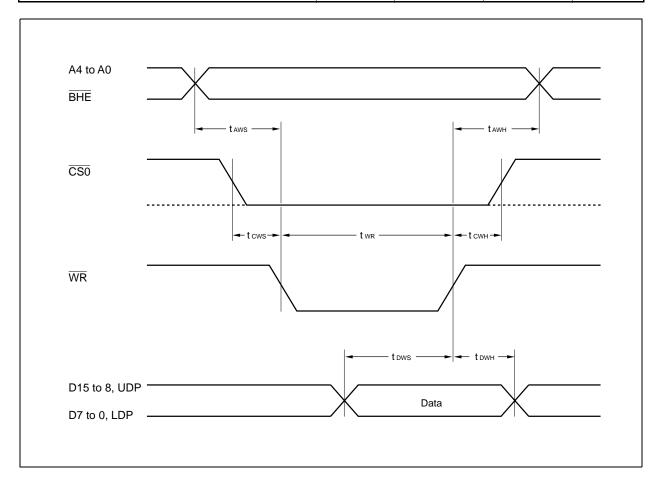

# (1) Register write timing for 80 series

| Parameter                           | Symbol       | Value |      | Unit  |

|-------------------------------------|--------------|-------|------|-------|

| Farameter                           | Symbol       | Min.  | Max. | Oille |

| Address (A4 to A0), BHE set up time | taws         | 40    | _    | ns    |

| Address (A4 to A0), hold time       | <b>t</b> awh | 20    | _    | ns    |

| CS0 set up time                     | tcws         | 20    | _    | ns    |

| CS0 hold time                       | <b>t</b> cwн | 10    | _    | ns    |

| Data set up time                    | tows         | 40    | _    | ns    |

| Data hold time                      | <b>t</b> DWH | 20    | _    | ns    |

| WR "L" level pulse width            | twr          | 70    | _    | ns    |

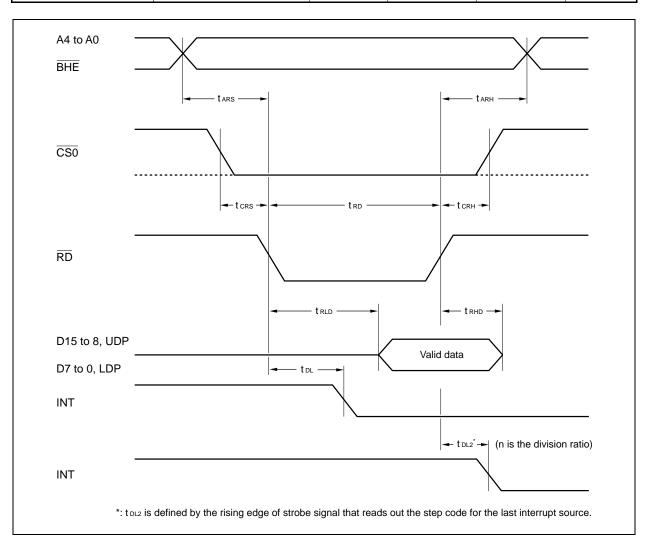

### (2) Register read timing for 80 series

| Dow                                             |                         | Coursels ad      | Va   | Unit          |      |

|-------------------------------------------------|-------------------------|------------------|------|---------------|------|

| Par                                             | ameter                  | Symbol           | Min. | Max.          | Unit |

| Address (A4 to A0), BHE                         | set up time             | tars             | 40   | _             | ns   |

| Address (A4 to A0), hold                        | time                    | tarh             | 20   | _             | ns   |

| CS0 set up time                                 |                         | tcrs             | 20   | _             | ns   |

| CS0 hold time                                   |                         | <b>t</b> crh     | 10   | _             | ns   |

| $\overline{RD}$ set Low $\rightarrow$ data outp | ut defined time         | <b>t</b> RLD     | _    | 70            | ns   |

| $\overline{RD}$ set high $	o$ data outp         | out disable time        | <b>t</b> RHD     | 5    | _             | ns   |

| RD pulse duration at Lov                        | V                       | <b>t</b> RD      | 70   | _             | ns   |

| INIT signal along time                          | Interrupt non-hold mode | tol              | _    | 50            |      |

| INT signal clear time                           | Interrupt hold mode     | t <sub>DL2</sub> | _    | n * tclf + 50 | ns   |

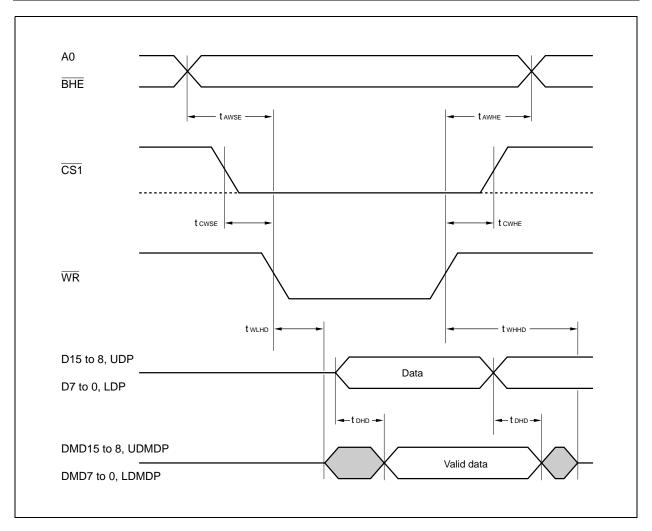

# (3) Register write timing for 80 series (for external access)

| Parameter                                                                  | Symbol        | Value |      | Unit  |

|----------------------------------------------------------------------------|---------------|-------|------|-------|

| Farameter                                                                  | Symbol        | Min.  | Max. | Offic |

| Address (A0), BHE set up time                                              | <b>t</b> awse | 40    | _    | ns    |

| Address (A0), BHE hold time                                                | <b>t</b> awhe | 20    | _    | ns    |

| CS1 set up time                                                            | tcwse         | 20    | _    | ns    |

| CST hold time                                                              | <b>t</b> cwhe | 10    | _    | ns    |

| $\overline{\text{WR}}$ set Low $	o$ DMA bus output delay time              | <b>t</b> wlhd | _     | 70   | ns    |

| $\overline{\text{WR}}$ set High $ ightarrow$ DMA bus output undefined time | <b>t</b> whhd | 5     | _    | ns    |

| MPU data bus $ ightarrow$ DMA bus output delay time                        | <b>t</b> DHD  | _     | 40   | ns    |

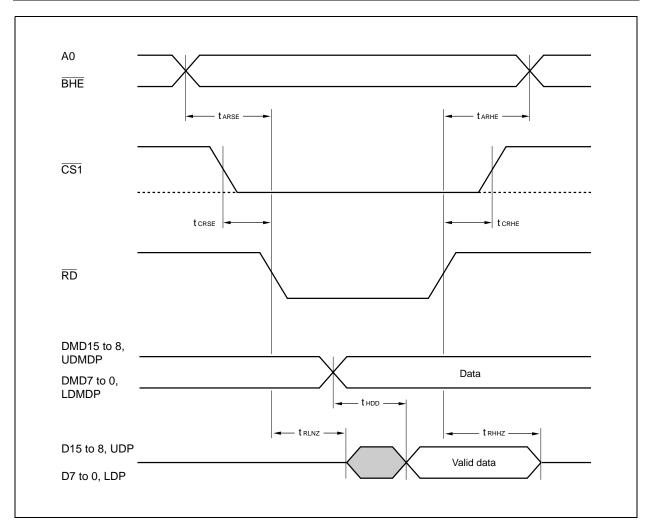

# (4) Register read timing for 80 series (for external access)

| Parameter                                                           | Symbol        | Va   | lue  | Unit  |

|---------------------------------------------------------------------|---------------|------|------|-------|

| Farameter                                                           | Syllibol      | Min. | Max. | Offic |

| Address (A0), BHE set up time                                       | <b>t</b> arse | 40   | _    | ns    |

| Address (A0), BHE hold time                                         | <b>t</b> arhe | 20   | _    | ns    |

| CS1 set up time                                                     | tcrse         | 20   | _    | ns    |

| CST hold time                                                       | <b>t</b> CRHE | 10   |      | ns    |

| $\overline{\text{RD}}$ set Low $	o$ MPU data bus output enable time | <b>t</b> rlnz | _    | 70   | ns    |

| $\overline{	t RD}$ set High $	o$ MPU data bus output disable time   | <b>t</b> RHHZ | 5    | _    | ns    |

| DMA bus $ ightarrow$ MPU data bus output delay time                 | <b>t</b> HDD  | _    | 40   | ns    |

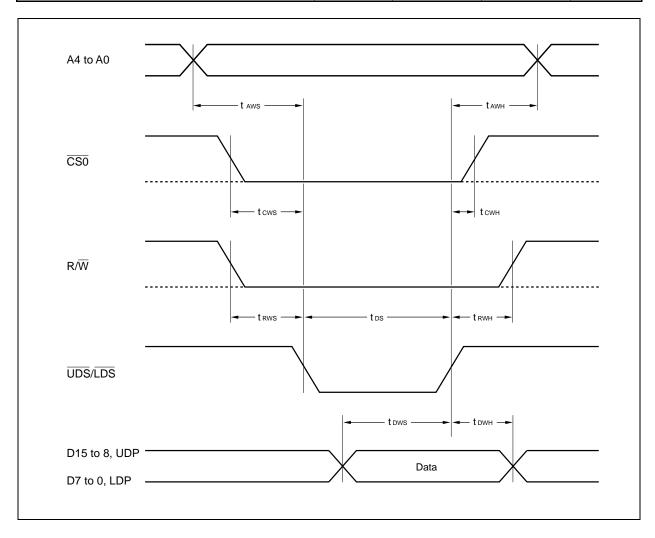

# (5) Register write timing for 68 series

| Parameter                      | Symbol       | Val  | lue  | Unit  |

|--------------------------------|--------------|------|------|-------|

| Farameter                      | Syllibol     | Min. | Max. | Offic |

| Address (A4 to A0) set up time | <b>t</b> aws | 40   | _    | ns    |

| Address (A4 to A0) hold time   | <b>t</b> awh | 20   | _    | ns    |

| CS0 set up time                | tcws         | 20   | _    | ns    |

| CS0 hold time                  | <b>t</b> cwH | 10   | _    | ns    |

| Data set up time               | tows         | 40   | _    | ns    |

| Data hold time                 | <b>t</b> DWH | 20   | _    | ns    |

| UDS/LDS "L" level pulse width  | tos          | 70   | _    | ns    |

| R/W set up time                | trws         | 20   | _    | ns    |

| R/W hold time                  | <b>t</b> RWH | 20   | _    | ns    |

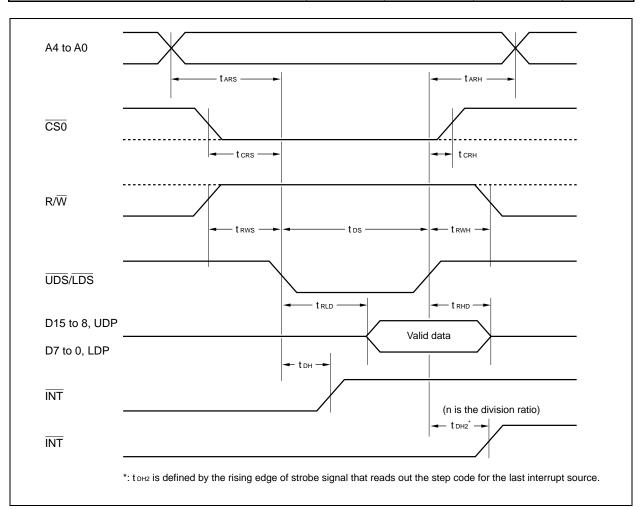

### (6) Register read timing for 68 series

| Danamatan.                     | Councile of      | V    | Unit          |      |

|--------------------------------|------------------|------|---------------|------|

| Parameter                      | Symbol           | Min. | Max.          | Unit |

| Address (A4 to A0) set up time | tars             | 40   | _             | ns   |

| Address (A4 to A0) hold time   | tarh             | 20   | _             | ns   |

| CS0 set up time                | tcrs             | 20   | _             | ns   |

| CS0 hold time                  | <b>t</b> crh     | 10   | _             | ns   |

| Data output defined time       | trld             | _    | 70            | ns   |

| Data output disable time       | <b>t</b> RHD     | 5    | _             | ns   |

| UDS/LDS "L" level pulse width  | <b>t</b> DS      | 70   | _             | ns   |

| R/W set up time                | trws             | 20   | _             | ns   |

| R/W hold time                  | tкwн             | 20   | _             | ns   |

| THE COLUMN CO.                 | tон              | _    | 50            |      |

| INT signal clear time          | t <sub>DH2</sub> | _    | n * tclf + 50 | ns   |

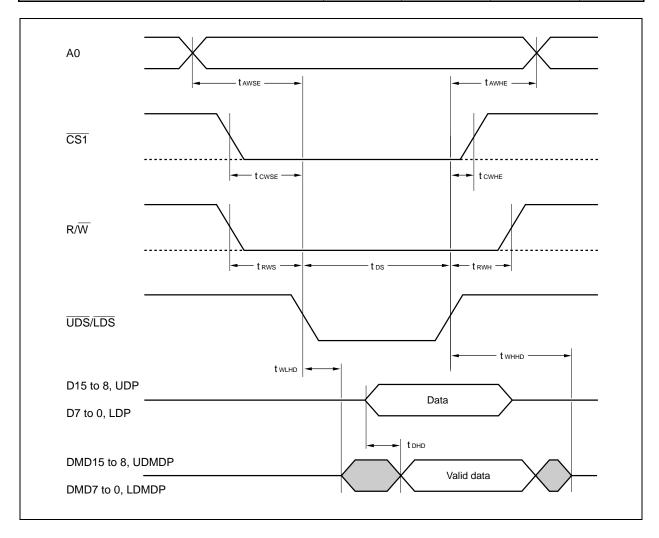

# (7) Register write timing for 68 series (for external access)

| Parameter                                                                       | Symbol        | Va   | Unit |      |

|---------------------------------------------------------------------------------|---------------|------|------|------|

|                                                                                 |               | Min. | Max. | Unit |

| Address (A0) set up time                                                        | <b>t</b> AWSE | 40   | _    | ns   |

| Address (A0) hold time                                                          | <b>t</b> AWHE | 20   | _    | ns   |

| CS1 set up time                                                                 | tcwse         | 20   | _    | ns   |

| CST hold time                                                                   | <b>t</b> cwhe | 10   | _    | ns   |

| $\overline{	extsf{UDS/LDS}}$ set Low $ ightarrow$ DMA bus output delay time     | twlhd         | _    | 70   | ns   |

| $\overline{\text{UDS/LDS}}$ set High $ ightarrow$ DMA bus output undefined time | <b>t</b> whhd | 5    | _    | ns   |

| MPU data bus $ ightarrow$ DMA bus output delay time                             | <b>t</b> DHD  | _    | 40   | ns   |

| R/W set up time                                                                 | trws          | 20   | _    | ns   |

| R/W hold time                                                                   | <b>t</b> RWH  | 20   | _    | ns   |

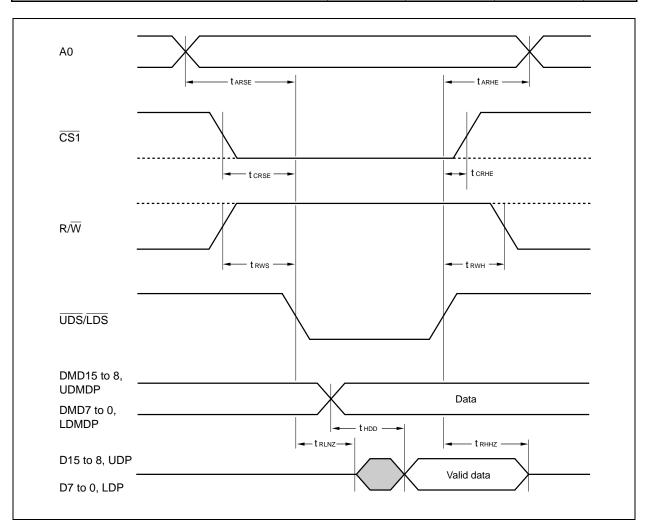

# (8) Register read timing for 68 series (for external access)

| Parameter                                                                                                    | Symbol        | Value |      | Unit |

|--------------------------------------------------------------------------------------------------------------|---------------|-------|------|------|

|                                                                                                              |               | Min.  | Max. | Unit |

| Address (A0) set up time                                                                                     | <b>t</b> arse | 40    | _    | ns   |

| Address (A0) hold time                                                                                       | <b>t</b> arhe | 20    | _    | ns   |

| CST set up time                                                                                              | tcrse         | 20    | _    | ns   |

| CST hold time                                                                                                | <b>t</b> CRHE | 10    | _    | ns   |

| $\overline{	extsf{UDS/LDS}}$ set $\overline{	extsf{Low}}  ightarrow 	extsf{MPU}$ data bus output enable time | <b>t</b> rlnz | _     | 70   | ns   |

| $\overline{	extsf{UDS/LDS}}$ set High $ ightarrow$ MPU data bus output disable time                          | <b>t</b> RHHZ | 5     | _    | ns   |

| DMA bus → MPU data bus output delay time                                                                     | <b>t</b> HDD  | _     | 40   | ns   |

| R/W set up time                                                                                              | trws          | 20    | _    | ns   |

| R/W hold time                                                                                                | <b>t</b> rwh  | 20    | _    | ns   |

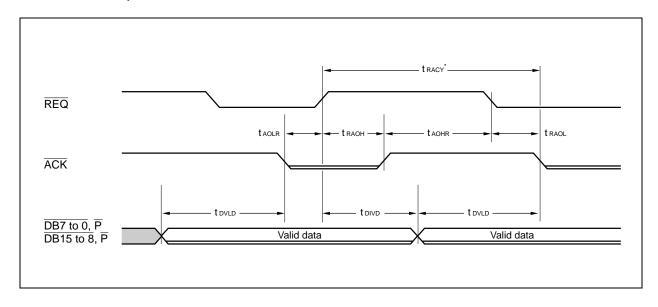

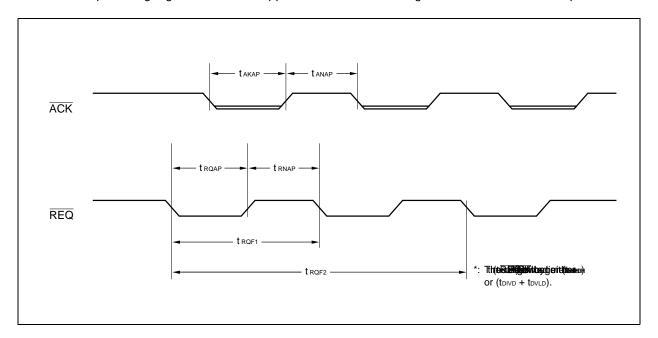

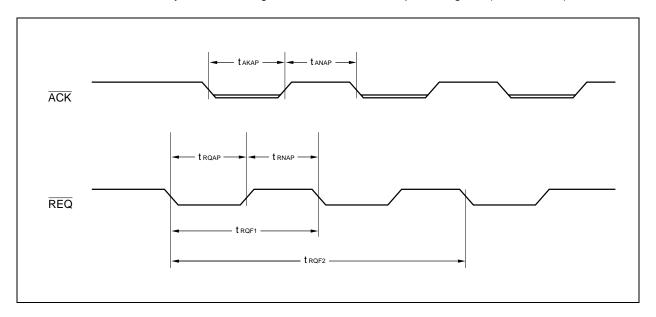

#### 6. DMA Interface

DMA access timing

The time regulations are not applicable in the following cases:

- During SCSI input and when data buffer EMPTY, or when one byte held

- During SCSI output and when data buffer FULL, or when 63 bytes held

- When parity error detected (target)

- When error stopping transfer occurs in SCSI interface

#### (1) Access cycle time (burst mode)

| Parameter         | Symbol            | Value  |      | Unit  |

|-------------------|-------------------|--------|------|-------|

|                   |                   | Min.   | Max. | Offic |

| Access cycle time | tDCY1             | 2 tclf | _    | ns    |

|                   | tDCY2             | 3 tclf | _    | ns    |

|                   | t <sub>DCY3</sub> | 4 tclf | _    | ns    |

|                   | tDCY4             | 1 tclf | _    | ns    |

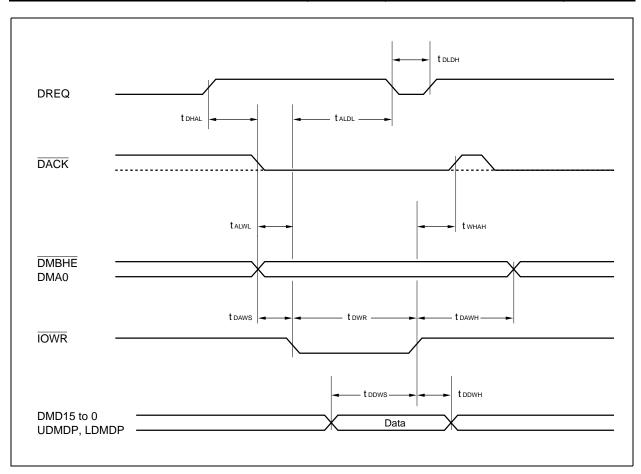

# (2) Write timing (burst mode for 80 series)

| Parameter                                | Cymah al      | Value |      | l lea it |

|------------------------------------------|---------------|-------|------|----------|

|                                          | Symbol        | Min.  | Max. | – Unit   |

| DREQ set High $\rightarrow$ DACK set Low | <b>t</b> DHAL | 0     | _    | ns       |

| TOWR set Low → DREQ set Low              | taldl         | _     | 35   | ns       |

| $DREQ\ set\ Low 	o DREQ\ set\ High$      | toldh         | 0     | _    | ns       |

| DACK set Low → IOWR set Low              | talwl         | 0     | _    | ns       |

| DMBHE, DMA0 set up time                  | tdaws         | 20    | _    | ns       |

| IOWR "L" level pulse width               | <b>t</b> DWR  | 40    | _    | ns       |

| TOWR set High → DACK set High            | twhah         | 0     | _    | ns       |

| DMBHE, DMA0 hold time                    | <b>t</b> DAWH | 20    | _    | ns       |

| Input data set up time                   | todws         | 30    | _    | ns       |

| Input data hold time                     | <b>t</b> DDWH | 10    | _    | ns       |

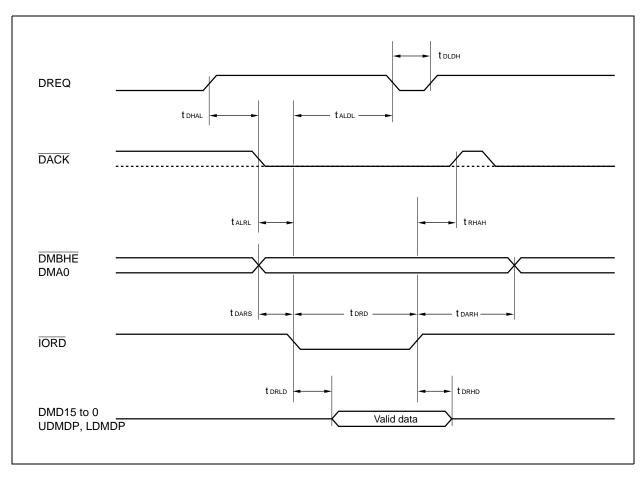

# (3) Read timing (burst mode for 80 series)

| Parameter                                       | Symbol        | Value |      | l lm:4 |

|-------------------------------------------------|---------------|-------|------|--------|

|                                                 |               | Min.  | Max. | Unit   |

| $DREQ\ set\ High \to \overline{DACK}\ set\ Low$ | <b>t</b> dhal | 0     | _    | ns     |

| IORD set Low → DREQ set Low                     | <b>t</b> aldl | _     | 35   | ns     |

| $DREQ\ set\ Low \to DREQ\ set\ High$            | <b>t</b> DLDH | 0     | _    | ns     |

| DACK set Low → IORD set Low                     | <b>t</b> alrl | 0     | _    | ns     |

| DMBHE, DMA0 set up time                         | <b>t</b> dars | 20    | _    | ns     |

| IORD "L" level pulse width                      | <b>t</b> DRD  | 40    | _    | ns     |

| IORD set High → DACK set High                   | <b>t</b> rhah | 0     | _    | ns     |

| DMBHE, DMA0 hold time                           | <b>t</b> darh | 20    | _    | ns     |

| Data output defined time                        | <b>t</b> DRLD | _     | 40   | ns     |

| Data output hold time                           | <b>t</b> DRHD | 5     | _    | ns     |

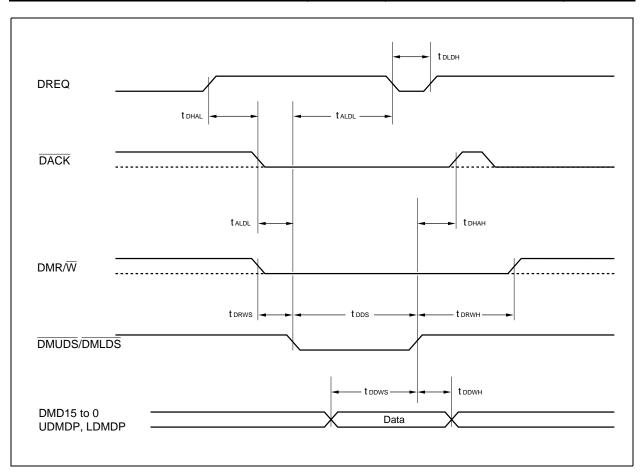

# (4) Write timing (burst mode for 68 series)

| Parameter                                       | Cymah al      | Value |      | l lmi4 |

|-------------------------------------------------|---------------|-------|------|--------|

|                                                 | Symbol        | Min.  | Max. | - Unit |

| $DREQ\ set\ High \to \overline{DACK}\ set\ Low$ | <b>t</b> DHAL | 0     | _    | ns     |

| DMUDS/DMLDS set Low → DREQ set Low              | taldl         | _     | 35   | ns     |

| DREQ set Low → DREQ set High                    | toldh         | 0     | _    | ns     |

| DACK set Low → DMUDS/DMLDS set Low              | taldl         | 10    | _    | ns     |

| R/W set up time                                 | torws         | 20    | _    | ns     |

| DMUDS/DMLDS "L" level pulse width               | tods          | 40    | _    | ns     |

| DMUDS/DMLDS set High → DACK set High            | <b>t</b> dhah | 0     | _    | ns     |

| R/W hold time                                   | <b>t</b> DRWH | 20    | _    | ns     |

| Input data set up time                          | todws         | 30    | _    | ns     |

| Input data hold time                            | <b>t</b> DDWH | 10    | _    | ns     |

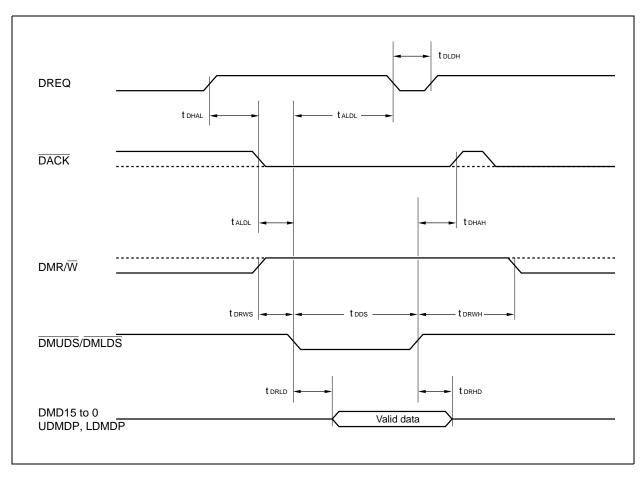

# (5) Read timing (burst mode for 68 series)

| Parameter                                                          | Symbol        | Value |      | l lm:4 |

|--------------------------------------------------------------------|---------------|-------|------|--------|

|                                                                    |               | Min.  | Max. | Unit   |