### FEATURES

- ◆ 32 dBm Linear Output Power at 12 GHz

- ◆ 7.5 dB Power Gain at 12 GHz

- ♦ 42 dBm Output IP3

- ♦ 45% Power-Added Efficiency

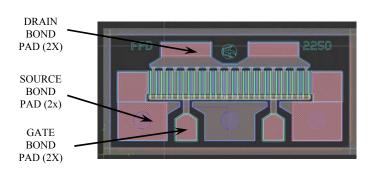

DIE SIZE (μm):: 680 x 470 DIE THICKNESS: 75 μm BONDING PADS (μm): > 85 x 60

### DESCRIPTION AND APPLICATIONS

The FPD2250 is an AlGaAs/InGaAs pseudomorphic High Electron Mobility Transistor (PHEMT), featuring a 0.25 µm by 2250 µm Schottky barrier gate, defined by high-resolution stepper-based photolithography. The recessed and offset Gate structure minimizes parasitics to optimize performance. The epitaxial structure and processing have been optimized for reliable high-power applications. The FPD2250 also features Si<sub>3</sub>N<sub>4</sub> passivation and is available in a P100 flanged ceramic package and in the low cost plastic SOT89 plastic package.

Typical applications include commercial and other narrowband and broadband high-performance amplifiers, including SATCOM uplink transmitters, PCS/Cellular low-voltage high-efficiency output amplifiers, and medium-haul digital radio transmitters.

## ELECTRICAL SPECIFICATIONS AT 22°C

| Parameter                                                  | Symbol        | <b>Test Conditions</b>                                                | Min  | Тур  | Max | Units |  |  |  |  |  |

|------------------------------------------------------------|---------------|-----------------------------------------------------------------------|------|------|-----|-------|--|--|--|--|--|

| RF SPECIFICATIONS MEASURED AT $f$ = 12 GHz USING CW SIGNAL |               |                                                                       |      |      |     |       |  |  |  |  |  |

| Power at 1dB Gain Compression                              | $P_{1dB}$     | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$                         | 31.0 | 32.0 |     | dBm   |  |  |  |  |  |

| Maximum Stable Gain (S <sub>21</sub> /S <sub>12</sub> )    | MSG           | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$                         | 8.0  | 9.0  |     | dB    |  |  |  |  |  |

| Power Gain at P <sub>1dB</sub>                             | $G_{1dB}$     | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$                         | 6.5  | 7.5  |     | dB    |  |  |  |  |  |

| Power-Added Efficiency                                     | PAE           | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS};$<br>$P_{OUT} = P_{1dB}$ |      | 45   |     | %     |  |  |  |  |  |

| Output Third-Order Intercept Point                         | IP3           | $V_{DS} = 8 \text{ V}; I_{DS} = 50\% I_{DSS}$                         |      |      |     |       |  |  |  |  |  |

| (from 15 to 5 dB below P <sub>1dB</sub> )                  |               | Matched for optimal power                                             |      | 40   |     | dBm   |  |  |  |  |  |

|                                                            |               | Tuned for best IP3                                                    |      | 42   |     |       |  |  |  |  |  |

| Saturated Drain-Source Current                             | $I_{DSS}$     | $V_{DS} = 1.3 \text{ V}; V_{GS} = 0 \text{ V}$                        | 560  | 700  | 825 | mA    |  |  |  |  |  |

| Maximum Drain-Source Current                               | $I_{MAX}$     | $V_{DS} = 1.3 \text{ V}; V_{GS} \cong +1 \text{ V}$                   |      | 1125 |     | mA    |  |  |  |  |  |

| Transconductance                                           | $G_{M}$       | $V_{DS} = 1.3 \text{ V}; V_{GS} = 0 \text{ V}$                        |      | 600  |     | mS    |  |  |  |  |  |

| Gate-Source Leakage Current                                | $I_{GSO}$     | $V_{GS} = -5 \text{ V}$                                               |      | 10   |     | μΑ    |  |  |  |  |  |

| Pinch-Off Voltage                                          | $ V_P $       | $V_{DS} = 1.3 \text{ V}; I_{DS} = 2.25 \text{ mA}$                    |      | 1.0  |     | V     |  |  |  |  |  |

| Gate-Source Breakdown Voltage                              | $ V_{BDGS} $  | $I_{GS} = 2.25 \text{ mA}$                                            | 12.0 | 14.0 |     | V     |  |  |  |  |  |

| Gate-Drain Breakdown Voltage                               | $ V_{BDGD} $  | $I_{GD} = 2.25 \text{ mA}$                                            | 14.5 | 16.0 |     | V     |  |  |  |  |  |

| Thermal Resistivity (see Notes)                            | $\theta_{JC}$ | $V_{DS} > 6V$                                                         |      | 30   |     | °C/W  |  |  |  |  |  |

Revised: 11/17/04

Email: sales@filcsi.com

### ABSOLUTE MAXIMUM RATINGS1

| Parameter                                       | Symbol    | <b>Test Conditions</b>          | Min | Max       | Units |

|-------------------------------------------------|-----------|---------------------------------|-----|-----------|-------|

| Drain-Source Voltage                            | $V_{DS}$  | $-3V < V_{GS} < +0V$            |     | 8         | V     |

| Gate-Source Voltage                             | $V_{GS}$  | $0V < V_{\rm DS} < +8V$         |     | -3        | V     |

| Drain-Source Current                            | $I_{DS}$  | For $V_{DS} > 2V$               |     | $I_{DSS}$ | mA    |

| Gate Current                                    | $I_G$     | Forward or reverse current      |     | 20        | mA    |

| RF Input Power <sup>2</sup>                     | $P_{IN}$  | Under any acceptable bias state |     | 450       | mW    |

| Channel Operating Temperature                   | $T_{CH}$  | Under any acceptable bias state |     | 175       | °C    |

| Storage Temperature                             | $T_{STG}$ | Non-Operating Storage           | -40 | 150       | °C    |

| Total Power Dissipation                         | $P_{TOT}$ | See De-Rating Note below        |     | 5.0       | W     |

| Gain Compression                                | Comp.     | Under any bias conditions       |     | 5         | dB    |

| Simultaneous Combination of Limits <sup>3</sup> |           | 2 or more Max. Limits           |     | 80        | %     |

$<sup>{}^{1}</sup>T_{Ambient} = 22^{\circ}C$  unless otherwise noted <sup>2</sup>Max. RF Input Limit must be further limited if input VSWR > 2.5:1

#### Notes:

- Operating conditions that exceed the Absolute Maximum Ratings could result in permanent damage to the device.

- Thermal Resitivity specification assumes a Au/Sn eutectic die attach onto a Au-plated copper heatsink or rib.

- Power Dissipation defined as:  $P_{TOT} = (P_{DC} + P_{IN}) P_{OUT}$ , where

P<sub>DC</sub>: DC Bias Power P<sub>IN</sub>: RF Input Power POUT: RF Output Power

Absolute Maximum Power Dissipation to be de-rated as follows above 22°C:

$P_{TOT} = 5.0W - (0.033W)^{\circ}C) \times T_{HS}$

where  $T_{HS}$  = heatsink or ambient temperature above 22°C

Example: For a 85°C heatsink temperature:  $P_{TOT} = 5.0W - (0.033 \text{ x} (85 - 22)) = 2.9W$

# HANDLING PRECAUTIONS

To avoid damage to the devices care should be exercised during handling. Proper Electrostatic Discharge (ESD) precautions should be observed at all stages of storage, handling, assembly, and testing. These devices should be treated as Class 1A per ESD-STM5.1-1998, Human Body Model. Further information on ESD control measures can be found in MIL-STD-1686 and MIL-HDBK-263.

## ASSEMBLY INSTRUCTIONS

Phone: +1 408 850-5790

Fax: +1 408 850-5766

The recommended die attach is gold/tin eutectic solder under a nitrogen atmosphere. temperature should be 280-290°C; maximum time at temperature is one minute. The recommended wire bond method is thermo-compression wedge bonding with 0.7 or 1.0 mil (0.018 or 0.025 mm) gold wire. Stage temperature should be 250-260°C.

## APPLICATIONS NOTES & DESIGN DATA

Applications Notes are available from your local Filtronic Sales Representative or directly from the factory. Complete design data, including S-parameters, noise data, and large-signal models are available on the Filtronic web site.

All information and specifications are subject to change without notice.

<sup>&</sup>lt;sup>3</sup>Users should avoid exceeding 80% of 2 or more Limits simultaneously