## FAIRCHILD

SEMICONDUCTOR

# MM74C08 Quad 2-Input AND Gate

### **General Description**

The MM74C08 employs complementary MOS (CMOS) transistors to achieve wide power supply operating range, low power consumption and high noise margin, these gates provide basic functions used in the implementation of digital integrated circuit systems. The N- and P-channel enhancement mode transistors provide a symmetrical circuit with output swing essentially equal to the supply voltage. No DC power other than that caused by leakage current is consumed during static condition. All inputs are

protected from damage due to static discharge by diode clamps to  $V_{CC}$  and GND.

#### Features

- Wide supply voltage range: 3.0V to 15V

- Guaranteed noise margin: 1.0V

- High noise immunity: 0.45 V<sub>CC</sub> (typ.)

- Low power TTL compatibility: Fan out of 2 driving 74L

- Low power consumption: 10 nW/package (typ.)

### **Ordering Code:**

| Order Number | Package Number | Package Description                                                          |

|--------------|----------------|------------------------------------------------------------------------------|

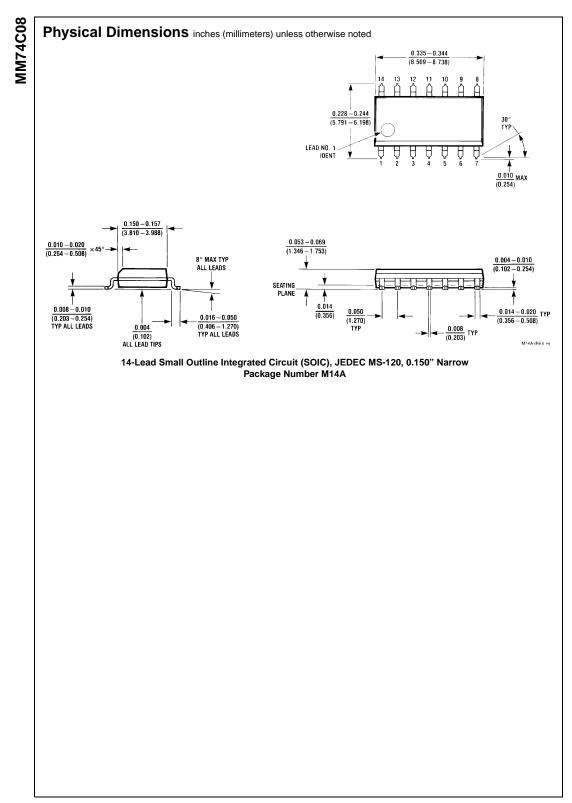

| MM74C08M     | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150" Narrow |

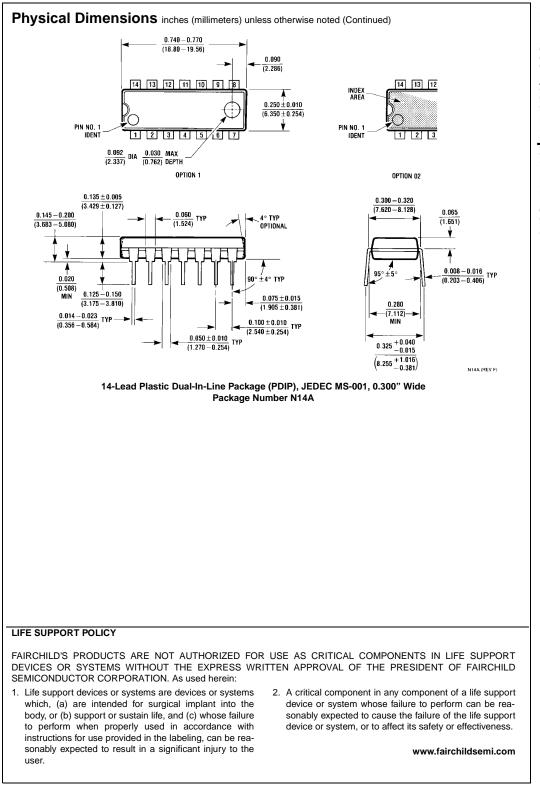

| MM74CD8N     | N14A           | 14-Lead Plastic Dual-in-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

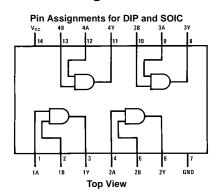

#### **Connection Diagram**

#### **Truth Table**

| Inp | Inputs |   |

|-----|--------|---|

| Α   | В      | Y |

| L   | L      | L |

| L   | Н      | L |

| н   | L      | L |

| н   | Н      | н |

H = HIGH Level L = LOW Level

© 1999 Fairchild Semiconductor Corporation DS005878.prf

www.fairchildsemi.com

## Absolute Maximum Ratings(Note 1)

| Voltage at Any Pin                  | $-0.3V$ to $V_{CC} + 0.3V$        |

|-------------------------------------|-----------------------------------|

| Operating Temperature Range         | $-40^{\circ}C$ to $+85^{\circ}C$  |

| Storage Temperature Range           | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Power Dissipation (P <sub>D</sub> ) |                                   |

| Dual-In-Line                        | 700 mW                            |

| Small Outline                       | 500 mW                            |

| Operating V <sub>CC</sub> Range     | 3.0V to 15V                       |

|                                     |                                   |

| Absolute Maximum V <sub>CC</sub> |

|----------------------------------|

| Lead Temperature                 |

| (Soldering, 10 seconds)          |

18V

260°C

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The Electrical Characteristics table provides conditions for actual device operation.

# **DC Electrical Characteristics**

| Symbol                  | Parameter                            | Conditions                                              | Min                   | Тур    | Max | Units |

|-------------------------|--------------------------------------|---------------------------------------------------------|-----------------------|--------|-----|-------|

| CMOS TO C               | MOS                                  | I                                                       |                       |        |     | 1     |

| V <sub>IN(1)</sub> Logi | Logical "1" Input Voltage            | $V_{CC} = 5.0V$                                         | 3.5                   |        |     | V     |

|                         |                                      | $V_{CC} = 10V$                                          | 8.0                   |        |     | V     |

| V <sub>IN(0)</sub>      | Logical "0" Input Voltage            | $V_{CC} = 5.0V$                                         |                       |        | 1.5 | V     |

|                         |                                      | $V_{CC} = 10V$                                          |                       |        | 2.0 | V     |

| V <sub>OUT(1)</sub>     | Logical "1" Output Voltage           | $V_{CC} = 5.0V, I_{O} = -10 \ \mu A$                    | 4.5                   |        |     | V     |

|                         |                                      | $V_{CC} = 10V$ , $I_{O} = -10 \ \mu A$                  | 9.0                   |        |     | V     |

| V <sub>OUT(0)</sub>     | Logical "0" Output Voltage           | $V_{CC} = 5.0V, I_{O} = 10 \mu A$                       |                       |        | 0.5 | V     |

|                         |                                      | $V_{CC} = 10V$ , $I_{O} = 10 \ \mu A$                   |                       |        | 1.0 | V     |

| I <sub>IN(1)</sub>      | Logical "1" Input Current            | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 15V            |                       | 0.005  | 1.0 | μΑ    |

| I <sub>IN(0)</sub>      | Logical "0" Input Current            | $V_{CC} = 15V, V_{IN} = 0V$                             | -1.0                  | -0.005 |     | μΑ    |

| I <sub>CC</sub>         | Supply Current                       | $V_{CC} = 15V$                                          |                       | 0.01   | 15  | μΑ    |

| CMOS/LPTT               |                                      |                                                         |                       |        |     |       |

| V <sub>IN(1)</sub>      | Logical "1" Input Voltage            | 74C, V <sub>CC</sub> = 4.75V                            | V <sub>CC</sub> – 1.5 |        |     | V     |

| V <sub>IN(0)</sub>      | Logical "0" Input Voltage            | 74C, V <sub>CC</sub> = 4.75V                            |                       |        | 0.8 | V     |

| V <sub>OUT(1)</sub>     | Logical "1" Output Voltage           | 74C, $V_{CC} = 4.75V$ , $I_O = -360 \mu A$              | 2.4                   |        |     | V     |

| V <sub>OUT(0)</sub>     | Logical "0" Output Voltage           | 74C, $V_{CC} = 4.75V$ , $I_{O} = 360 \ \mu A$           |                       |        | 0.4 | V     |

| OUTPUT DR               | IVE (see Family Characteristics D    | ata Sheet) T <sub>A</sub> = 25°C (short circuit current | )                     |        |     |       |

| ISOURCE                 | Output Source Current<br>(P-Channel) | $V_{CC} = 5.0V, V_{OUT} = 0V$                           | -1.75                 | -3.3   |     | mA    |

| ISOURCE                 | Output Source Current                | $V_{CC} = 10V, V_{OUT} = 0V$                            | -8.0                  | 15     |     | mA    |

|                         | (P-Channel)                          |                                                         |                       |        |     |       |

| I <sub>SINK</sub>       | Output Sink Current                  | $V_{CC} = 5.0V, V_{OUT} = V_{CC}$                       | 1.75                  | 3.6    |     | mA    |

|                         | (N-Channel)                          |                                                         |                       |        |     |       |

| I <sub>SINK</sub>       | Output Sink Current                  | $V_{CC} = 10V, V_{OUT} = V_{CC}$                        | 8.0                   | 16     |     | mA    |

|                         | (N-Channel)                          |                                                         |                       |        |     | 1     |

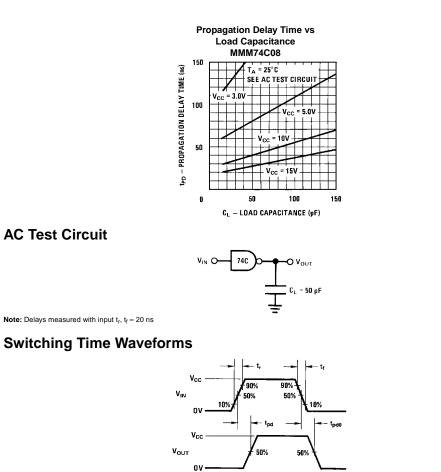

# AC Electrical Characteristics (Note 2)

| Symbol                              | Parameter                     | Conditions        | Min | Тур | Max | Units |

|-------------------------------------|-------------------------------|-------------------|-----|-----|-----|-------|

| t <sub>pd0</sub> , t <sub>pd1</sub> | Propagation Delay Time to     | $V_{CC} = 5.0V$   |     | 80  | 140 | ns    |

|                                     | Logical "1" or "0"            | $V_{CC} = 10V$    |     | 40  | 70  | ns    |

| CIN                                 | Input Capacitance             | (Note 3)          |     | 5.0 |     | pF    |

| C <sub>PD</sub>                     | Power Dissipation Capacitance | (Note 4) Per Gate |     | 14  |     | pF    |

Note 2: AC Parameters are guaranteed by DC correlated testing.

Note 3: Capacitance is guaranteed by periodic testing.

Note 4: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation see Family Characteristics Application Note— AN-90.

## **Typical Performance Characteristics**

www.fairchildsemi.com

MM74C08 Quad 2-Input AND Gate