GTLP1B153 1-Bit LVTTL/GTLP Driver/Receiver Pair

# GTLP1B153

### 1-Bit LVTTL/GTLP Driver/Receiver Pair

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

The GTLP1B153 is a 1-bit bus buffer pair with separate bit paths, that provide LVTTL-to-GTLP and GTLP-to-LVTTL signal level translation. High speed backplane operation is a direct result of GTLP's reduced output swing (<1V), reduced input threshold levels and output edge rate control. The edge rate control minimizes bus settling time. GTLP is a Fairchild Semiconductor derivative of the Gunning Transistor logic (GTL) JEDEC standard JESD8-3.

Fairchild's GTLP has internal edge-rate control and is process, voltage and temperature compensated. GTLP's I/O structure is similar to GTL and BTL but offers different output levels and receiver threshold. Typical GTLP output voltage levels are:  $V_{OL} = 0.5V$ ,  $V_{OH} = 1.5V$ , and  $V_{REF} = 1V$ .

#### Features

- Interface between LVTTL and GTLP logic levels

- Designed with edge rate control circuitry to reduce output noise in the GTLP port

- V<sub>REF</sub> pin provides external supply reference voltage for receiver threshold adjustability

- Special PVT compensation circuitry to provide consistent performance over variations of process, supply voltage and temperature

- TTL compatible driver and control inputs

- Designed using Fairchild advanced BiCMOS technology

Bushold data inputs on A Port to eliminate the need for

- external pull-up resistors for unused inputs

- Power up/down and power off high impedance for live insertion

- Open drain on GTLP to support wired-or connection

- Flow through pinout optimizes PCB layout

- A Port source/sink –24mA/+24mA

- B Port sink +50mA

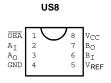

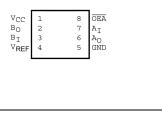

#### **Ordering Code:**

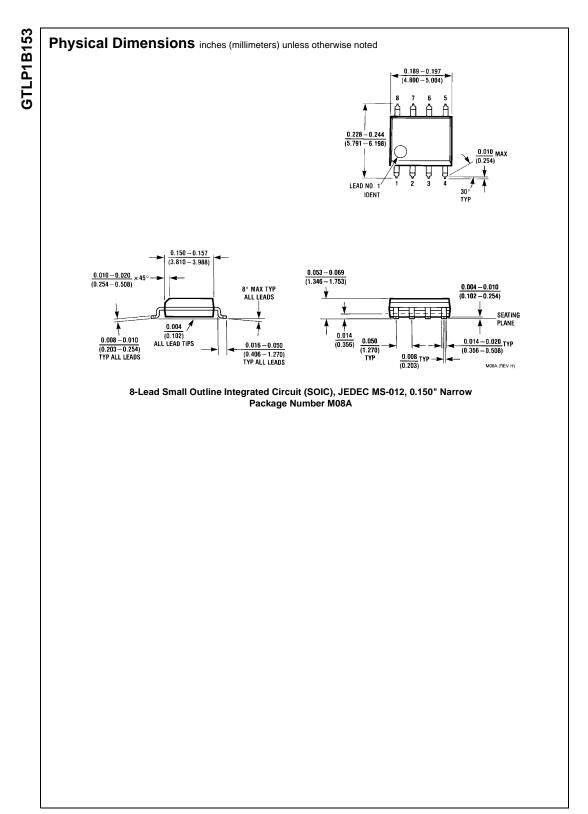

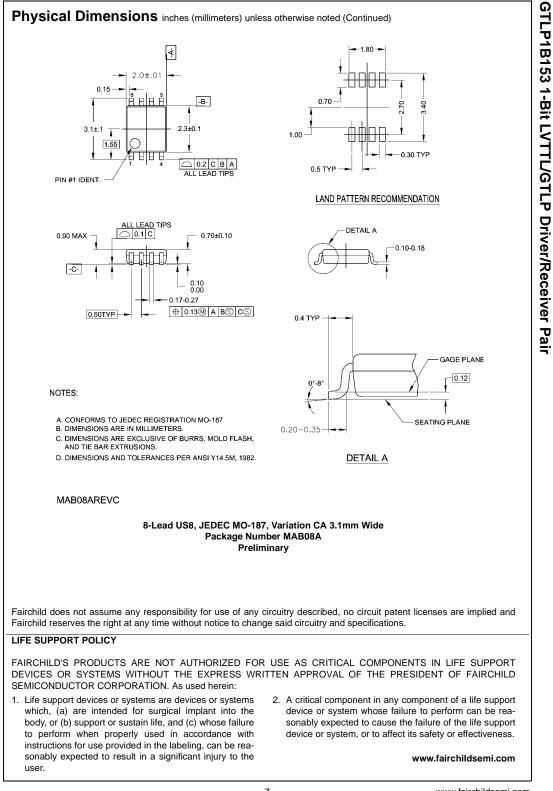

| Order Number | Package Number | Package Description                                                                            |

|--------------|----------------|------------------------------------------------------------------------------------------------|

| GTLP1B153M   | M08A           | 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow<br>[TUBE]          |

| GTLP1B153MX  |                | 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow<br>[TAPE and REEL] |

| GTLP1B153K8X |                | 8-Lead US8, JEDEC MO-187, Variation CA 3.1mm Wide<br>[TAPE and REEL]                           |

#### **Pin Descriptions**

|                                 | -                                                         |  |  |  |

|---------------------------------|-----------------------------------------------------------|--|--|--|

| Pin Names                       | Description                                               |  |  |  |

| OEA                             | LVTTL Bit Level Output Enable<br>(Active LOW for Receive) |  |  |  |

| $V_{CC}$ , GND, $V_{REF}$       | Device Supplies                                           |  |  |  |

| Β <sub>Ο</sub> , Β <sub>Ι</sub> | B Port GTLP Outputs/ Inputs                               |  |  |  |

| A <sub>O</sub> / A <sub>I</sub> | A Port LVTTL Outputs/ Inputs                              |  |  |  |

#### **Connection Diagrams**

#### SOIC

www.fairchildsemi.com

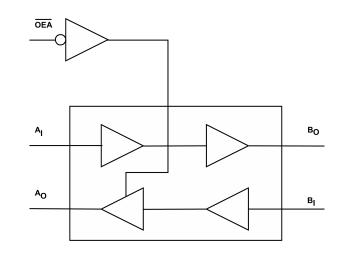

#### **Functional Description**

The GTLP1B153 is a 2-bit transceiver that supports GTLP and LVTTL signal levels. Data polarity is non-inverting and the data flow in the B-to-A direction is controlled by the OEA pin.

#### **Functional Table**

| Inp                               | uts | Outputs        | Description                      |  |  |  |

|-----------------------------------|-----|----------------|----------------------------------|--|--|--|

| OEA                               | BI  | A <sub>O</sub> | Description                      |  |  |  |

| L                                 | L   | L              | A Output Data Bit Enabled        |  |  |  |

| L                                 | н   | н              | A Output Data Bit Enabled        |  |  |  |

| Н                                 | х   | Z              | A Output Data Bit High Impedance |  |  |  |

| OEA A <sub>I</sub> B <sub>O</sub> |     | Bo             |                                  |  |  |  |

| Х                                 | L   | L              | B Output Data Bit Enabled        |  |  |  |

| Х                                 | Н   | H<br>(Note 1)  | B Output Data Bit Enabled        |  |  |  |

Note 1: Denotes that the bit would be in high impedance mode if there was no pull-up circuit due to open drain nature of the GTLP output.

#### Logic Diagram

| Absolute | Maximum | Ratings(Note 2) |

|----------|---------|-----------------|

|----------|---------|-----------------|

# Recommended Operating

GTLP1B153

| Supply Voltage (V <sub>CC</sub> )          | -0.5V to +4.6V  | Conditions                                                                                              |                                  |

|--------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------|----------------------------------|

| DC Input Voltage (VI)                      | -0.5V to +4.6V  | Supply Voltage V <sub>CC</sub>                                                                          | 3.15V to 3.45V                   |

| DC Output Voltage (V <sub>O</sub> )        |                 | Bus Termination Voltage (V <sub>TT</sub> )                                                              |                                  |

| Outputs 3-STATE                            | -0.5V to +4.6V  | GTLP                                                                                                    | 1.47V to 1.53V                   |

| Outputs Active (Note 3)                    | -0.5V to +4.6V  | V <sub>REF</sub>                                                                                        | 0.98V to 1.02V                   |

| DC Output Sink Current into                |                 | Input Voltage (V <sub>I</sub> )                                                                         |                                  |

| A Port I <sub>OL</sub>                     | 48 mA           | on A Port and Control Pins                                                                              | 0.0V to V <sub>CC</sub>          |

| DC Output Source Current from              |                 | HIGH Level Output Current (I <sub>OH</sub> )                                                            |                                  |

| A Port I <sub>OH</sub>                     | –48 mA          | A Port                                                                                                  | –24 mA                           |

| DC Output Sink Current into                |                 | LOW Level Output Current (I <sub>OL</sub> )                                                             |                                  |

| B Port in the LOW State, I <sub>OL</sub>   | 100 mA          | A Port                                                                                                  | +24 mA                           |

| DC Input Diode Current (I <sub>IK</sub> )  |                 | B Port                                                                                                  | +50 mA                           |

| V <sub>1</sub> < 0V                        | –50 mA          | Operating Temperature (T <sub>A</sub> )                                                                 | $-40^{\circ}C$ to $+85^{\circ}C$ |

| DC Output Diode Current (I <sub>OK</sub> ) |                 | Note 2: Absolute Maximum Ratings are those w                                                            |                                  |

| V <sub>O</sub> < 0V                        | –50 mA          | safety of the device cannot be guaranteed. The de<br>ated at these limits. The parametric values define |                                  |

| ESD Rating                                 | >2000V          | acteristics" table are not guaranteed at the absol                                                      |                                  |

| Storage Temperature (T <sub>STG</sub> )    | -65°C to +150°C | "Recommended Operating Conditions" table will actual device operation.                                  | define the conditions for        |

|                                            |                 | Note 3: $I_O$ Absolute Maximum Rating must be obs                                                       | erved.                           |

#### **DC Electrical Characteristics**

Over Recommended Operating Free-Air Temperature Range, V<sub>REF</sub> = 1.0V (unless otherwise noted).

| Symbol           |              | Test Conditions                       |                                                     | Min                     | Typ<br>(Note 4) | Мах                     | Units |

|------------------|--------------|---------------------------------------|-----------------------------------------------------|-------------------------|-----------------|-------------------------|-------|

| V <sub>IH</sub>  | B Port       |                                       |                                                     | V <sub>REF</sub> + 0.05 |                 | V <sub>TT</sub>         | V     |

|                  | Others       |                                       |                                                     | 2.0                     |                 |                         | v     |

| / <sub>IL</sub>  | B Port       |                                       |                                                     | 0.0                     |                 | V <sub>REF</sub> - 0.05 | V     |

|                  | Others       |                                       |                                                     |                         |                 | 0.8                     | v     |

| / <sub>REF</sub> | B Port       |                                       |                                                     | 0.7V                    | 1.0             | 1.3V                    | V     |

| V <sub>TT</sub>  | B Port       |                                       |                                                     | $V_{REF}$ + 50 mV       | 1.5             | V <sub>CC</sub>         | V     |

| V <sub>IK</sub>  |              | V <sub>CC</sub> = 3.15V               | I <sub>I</sub> = -18 mA                             |                         |                 | -1.2                    | V     |

| V <sub>он</sub>  | A Port       | V <sub>CC</sub> = Min to Max (Note 5) | I <sub>OH</sub> = -100 μA                           | V <sub>CC</sub> - 0.2   |                 |                         |       |

|                  |              | V <sub>CC</sub> = 3.15V               | I <sub>OH</sub> = -8 mA                             | 2.4                     |                 |                         | V     |

|                  |              |                                       | I <sub>OH</sub> = -24 mA                            | 2.2                     |                 |                         |       |

| / <sub>OL</sub>  | A Port       | V <sub>CC</sub> = Min to Max (Note 5) | I <sub>OL</sub> = 100 μA                            |                         |                 | 0.2                     |       |

|                  |              | V <sub>CC</sub> = 3.15V               | I <sub>OL</sub> = 8 mA                              |                         |                 | 0.4                     | V     |

|                  |              | V <sub>CC</sub> = 3.15V               | I <sub>OL</sub> = 24 mA                             |                         |                 | 0.5                     |       |

|                  | B Port       | V <sub>CC</sub> = 3.15V               | I <sub>OL</sub> = 40 mA                             |                         |                 | 0.4                     | V     |

|                  |              |                                       | I <sub>OL</sub> = 50 mA                             |                         |                 | 0.55                    | v     |

| I                | Control Pins | $V_{CC} = 3.45V$                      | $V_{I} = 3.45V$                                     |                         |                 | 5                       | μA    |

|                  |              |                                       | $V_I = 0V$                                          |                         |                 | -5                      | μΑ    |

|                  | A Port       | V <sub>CC</sub> = 3.45V               | $V_{I} = 3.45V$                                     |                         |                 | 10                      | μA    |

|                  |              |                                       | $V_I = 0V$                                          |                         |                 | -10                     | μΑ    |

|                  | B Port       | V <sub>CC</sub> = 3.45V               | V <sub>I</sub> = 3.45V                              |                         |                 | 5                       |       |

|                  |              |                                       | $V_I = 0$                                           |                         |                 | -5                      | μA    |

| OFF              | A Port,      | $V_{CC} = 0$                          | $V_{I}$ or $V_{O} = 0$ to 3.45V                     |                         |                 | 30                      | μΑ    |

|                  | Control Pins |                                       |                                                     |                         |                 |                         |       |

|                  | B Port       | $V_{CC} = 0$                          | $V_1 \text{ or } V_0 = 0 \text{ to } 3.45 \text{V}$ |                         |                 | 30                      | μΑ    |

| I (HOLD)         | A Port       | V <sub>CC</sub> = 3.15V               | V <sub>1</sub> = 0.8V                               | 75                      |                 |                         | μA    |

|                  |              |                                       | $V_I = 2.0V$                                        |                         |                 | -75                     | μΑ    |

| OZH              | A Port       | V <sub>CC</sub> = 3.45V               | $V_0 = 3.45V$                                       |                         |                 | 10                      |       |

|                  | B Port       | 1                                     | V <sub>O</sub> = 3.45V                              |                         |                 | 5                       | μA    |

www.fairchildsemi.com

# GTLP1B153

## DC Electrical Characteristics (Continued)

| Symbol             |              | Test Conditions                                |                              | Min | Typ<br>(Note 4) | Max | Units |

|--------------------|--------------|------------------------------------------------|------------------------------|-----|-----------------|-----|-------|

| l <sub>ozl</sub>   | A Port       | $V_{CC} = 3.45V$                               | $V_0 = 0V$                   |     |                 | -10 |       |

|                    | B Port       |                                                | $V_0 = 0V$                   |     |                 | -5  | μA    |

| I <sub>PU/PD</sub> | All Ports    | V <sub>CC</sub> = 0 to 1.5V                    | V <sub>I</sub> = 0 to 3.45V  |     |                 | 30  | μΑ    |

| I <sub>CC</sub>    | A Port       | $V_{CC} = 3.45V$                               | Outputs HIGH                 |     |                 | 11  |       |

|                    | or B Port    | $I_{O} = 0$                                    | Outputs LOW                  |     |                 | 11  | mA    |

|                    |              | $V_I = V_{CC}/V_{TT}$ or GND                   | Outputs Disabled             |     |                 | 11  |       |

| Δl <sub>CC</sub>   | A Port and   | V <sub>CC</sub> = 3.45V,                       | One Input at V <sub>CC</sub> |     |                 | 2   | mA    |

| (Note 6)           | Control Pins | A or Control Inputs at $V_{CC} \mbox{ or GND}$ | –0.6V                        |     |                 |     |       |

| Ci                 | Control Pins |                                                | $V_I = V_{CC},$              |     | 1               | 3   | pF    |

|                    | A and B Port |                                                | V <sub>TT</sub> or 0         |     |                 |     |       |

| с <sub>о</sub>     | A Port       |                                                | $V_I = V_{CC}$ or 0          |     |                 | 5   | pF    |

|                    | B Port       |                                                | $V_I = V_{TT}$ or 0          |     |                 | 5   | pF    |

Note 4: All typical values are at V\_{CC} = 3.3V and T\_A = 25^{\circ}C.

Note 5: For conditions shown as Min, use the appropriate value specified under recommended operating conditions.

Note 6: This is the increase in supply current for each input that is at the specified TTL voltage level rather than  $V_{CC}$  or GND.

Note: GTLP V<sub>REF</sub> and V<sub>TT</sub> are specified to 2% tolerance since signal integrity and noise margin can be significantly degraded if these supplies are noisy. In addition, V<sub>TT</sub> and R<sub>TERM</sub> can be adjusted beyond the recommended operating to accommodate backplane impedances other than 50 $\Omega$ , but must remain within the boundaries of the DC Absolute Maximum Ratings. Similarly, V<sub>REF</sub> can be adjusted to optimize noise margin.

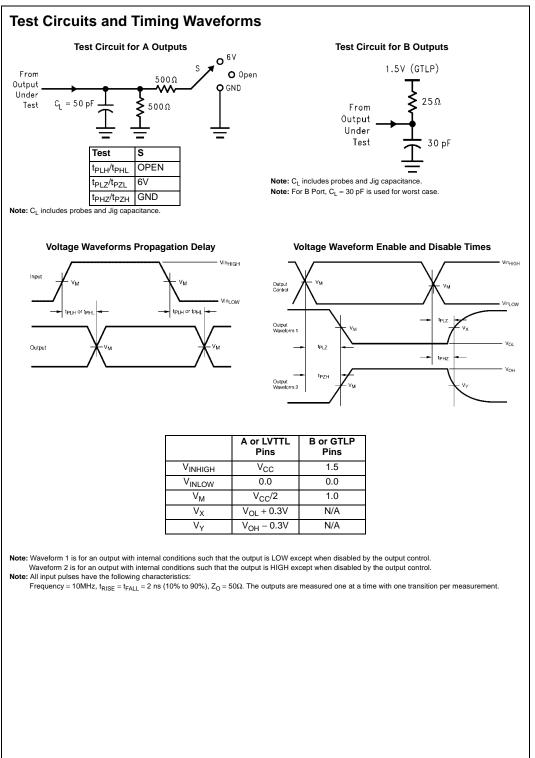

#### **AC Electrical Characteristics**

Over recommended range of supply voltage and operating free-air temperature, V<sub>REF</sub> = 1.0V (unless otherwise noted).

$C_L = 30 \text{ pF}$  for B Port and  $C_L = 50 \text{ pF}$  for A Port.

| Symbol                              | From                 | То                                      | Min | Тур      | Max | 11-14 |

|-------------------------------------|----------------------|-----------------------------------------|-----|----------|-----|-------|

|                                     | (Input)              | (Output)                                |     | (Note 7) |     | Unit  |

| t <sub>PLH</sub>                    | А                    | В                                       | 1.2 | 2.9      | 7.3 |       |

| t <sub>PHL</sub>                    | A                    | D                                       | 0.8 | 2.0      | 4.5 | ns    |

| t <sub>PLH</sub>                    | В                    | А                                       | 1.4 | 2.5      | 4.4 | ns    |

| t <sub>PHL</sub>                    | В                    | ~                                       | 1.6 | 2.7      | 5.0 | 115   |

| t <sub>RISE</sub>                   | Transition Time, B C | Transition Time, B Outputs (20% to 80%) |     |          |     | ns    |

| t <sub>FALL</sub>                   | Transition Time, B C | Transition Time, B Outputs (80% to 20%) |     |          |     | ns    |

| t <sub>RISE</sub>                   | Transition Time, C C | Transition Time, C Outputs (10% to 90%) |     |          |     | ns    |

| t <sub>FALL</sub>                   | Transition Time, C C |                                         | 2.2 |          | ns  |       |

| t <sub>PZH</sub> , t <sub>PZL</sub> |                      |                                         | 1.2 | 2.7      | 5.3 |       |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | OEA                  | A                                       | 1.4 | 2.8      | 4.9 | ns    |

Note 7: All typical values are at V\_{CC} = 3.3V, and T\_A = 25^{\circ}C.

GTLP1B153

www.fairchildsemi.com

7