April 1991 Revised August 1999

# 74FR9244

# 9-Bit Buffer/Line Driver with 3-STATE Outputs

## **General Description**

The 74FR9244 is a non-inverting 9-bit buffer and line driver designed to be employed as memory and address driver, clock driver and bus-oriented transmitter/receiver.

#### **Features**

- 3-STATE outputs drive bus lines or buffer memory address registers

- Outputs sink 64 mA and source 15 mA

- Guaranteed multiple output switching, 250 pf delays and pin-to-pin skew

- Guaranteed 4000V minimum ESD protection

- 9-Bit architecture for systems carrying parity

## **Ordering Code:**

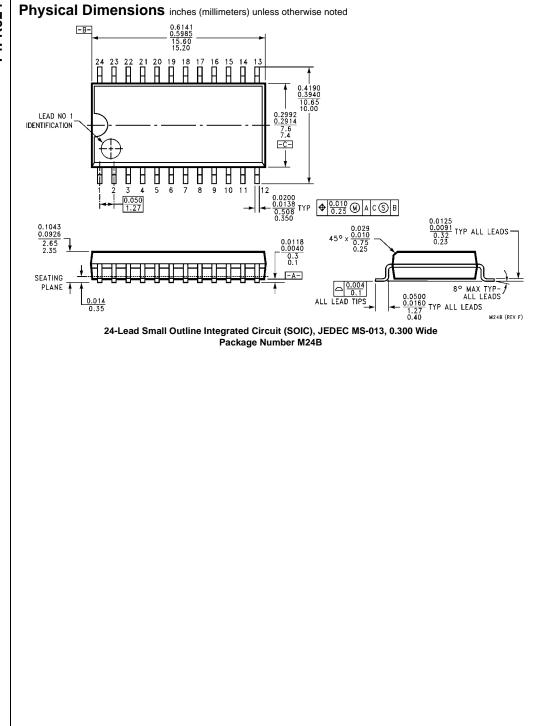

|                     | Order Number | Package Number | Package Description                                                       |

|---------------------|--------------|----------------|---------------------------------------------------------------------------|

|                     | 74FR9244SC   | M24B           | 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| 74FR9244SPC N24C 24 |              | N24C           | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

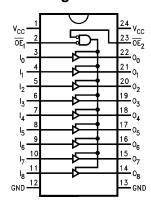

## **Connection Diagram**

# **Pin Descriptions**

| Pin Names                           | Description                      |

|-------------------------------------|----------------------------------|

| $\overline{OE}_1, -\overline{OE}_2$ | Output Enable Input (Active-LOW) |

| I <sub>0</sub> –I <sub>8</sub>      | Inputs                           |

| O <sub>0</sub> –O <sub>8</sub>      | Outputs                          |

#### **Truth Table**

| OE <sub>1</sub> | OE <sub>2</sub> | I <sub>n</sub> | O <sub>n</sub> |

|-----------------|-----------------|----------------|----------------|

| Н               | Х               | Х              | Z              |

| Х               | Н               | Х              | Z              |

| L               | L               | Н              | Н              |

| L               | L               | L              | L              |

- H = HIGH Voltage Level

- L = LOW Voltage Level X = Immaterial

- Z = High Impedance

# Absolute Maximum Ratings(Note 1)

# Recommended Operating Conditions

Storage Temperature -65°C to +150°C

$\begin{array}{ll} \mbox{Ambient Temperature Under Bias} & -55^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Junction Temperature Under Bias} & -55^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \end{array}$

$V_{CC}$  Pin Potential to Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V

Input Current (Note 2) –30 mA to +5.0 mA

Voltage Applied to Output in HIGH State (with  $V_{CC} = 0V$ )

Standard Output -0.5V to V<sub>CC</sub>

3-STATE Output -0.5V to +5.5V Current Applied to Output

in LOW State (Max) Twice The Rated I<sub>OL</sub> (mA)

ESD Last Passing Voltage (Min) 4000V

Free Air Ambient Temperature 0°C to +70°C Supply Voltage +4.5V to +5.5V

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol           | Parameter                         | Min  | Тур | Max  | Units | V <sub>CC</sub> | Conditions                 |

|------------------|-----------------------------------|------|-----|------|-------|-----------------|----------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                | 2.0  |     |      | V     |                 | Recognized HIGH Signal     |

| V <sub>IL</sub>  | Input LOW Voltage                 |      |     | 0.8  | V     |                 | Recognized LOW Signal      |

| V <sub>CD</sub>  | Input Clamp Diode Voltage         |      |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA   |

| V <sub>OH</sub>  | Output HIGH Voltage               | 2.4  |     |      | V     | Min             | I <sub>OH</sub> = -3 mA    |

|                  |                                   | 2.0  |     |      | V     | Min             | I <sub>OH</sub> = -15 mA   |

| V <sub>OL</sub>  | Output LOW Voltage                |      |     | 0.55 | V     | Min             | I <sub>OL</sub> = 64 mA    |

| I <sub>IH</sub>  | Input HIGH Current                |      |     | 5    | μΑ    | Max             | V <sub>IN</sub> = 2.7V     |

| I <sub>BVI</sub> | Input HIGH Current Breakdown Test |      |     | 7    | μΑ    | Max             | V <sub>IN</sub> = 7.0V     |

| I <sub>IL</sub>  | Input LOW Current                 |      |     | -150 | μΑ    | Max             | V <sub>IN</sub> = 0.5V     |

| V <sub>ID</sub>  | Input Leakage Test                | 4.75 |     |      | V     | 0.0             | $I_{ID} = 1.9 \mu A$ ,     |

|                  |                                   |      |     |      |       |                 | All Other Pins Grounded    |

| I <sub>OD</sub>  | Output Circuit Leakage Current    |      |     | 3.75 | μΑ    | 0.0             | V <sub>IOD</sub> = 150 mV, |

|                  |                                   |      |     |      |       |                 | All Other Pins Grounded    |

| l <sub>OZH</sub> | Output Leakage Current            |      |     | 20   | μΑ    | Max             | V <sub>OUT</sub> = 2.7V    |

| I <sub>OZL</sub> | Output Leakage Current            |      |     | -20  | μΑ    | Max             | V <sub>OUT</sub> = 0.5V    |

| los              | Output Short-Circuit Current      | -100 |     | -225 | mA    | Max             | V <sub>OUT</sub> = 0.0V    |

| I <sub>CEX</sub> | Output HIGH Leakage Current       |      |     | 50   | μΑ    | Max             | $V_{OUT} = V_{CC}$         |

| I <sub>ZZ</sub>  | Bus Drainage Test                 |      |     | 100  | μΑ    | 0.0             | V <sub>OUT</sub> = 5.25V   |

| I <sub>CCH</sub> | Power Supply Current              |      | 30  | 40   | mA    | Max             | All Outputs HIGH           |

| I <sub>CCL</sub> | Power Supply Current              |      | 60  | 75   | mA    | Max             | All Outputs LOW            |

| I <sub>CCZ</sub> | Power Supply Current              |      | 35  | 45   | mA    | Max             | Outputs 3-STATED           |

| C <sub>IN</sub>  | Input Capacitance                 |      | 8.0 |      | pF    | 5.0             |                            |

#### **AC Electrical Characteristics**

| Symbol           | Parameter           | $T_A = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |     |     | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |     | Units |

|------------------|---------------------|-------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------|-----|-------|

|                  |                     | Min                                                         | Тур | Max | Min                                                                                    | Max |       |

| t <sub>PLH</sub> | Propagation Delay   | 1.0                                                         | 2.6 | 4.1 | 1.0                                                                                    | 4.1 | ns    |

| t <sub>PHL</sub> |                     | 1.0                                                         | 1.8 | 4.1 | 1.0                                                                                    | 4.1 | 115   |

| t <sub>PZH</sub> | Output Enable Time  | 2.6                                                         | 4.8 | 7.0 | 2.6                                                                                    | 7.0 | ns    |

| t <sub>PZL</sub> |                     | 2.6                                                         | 3.9 | 7.0 | 2.6                                                                                    | 7.0 | 115   |

| t <sub>PHZ</sub> | Output Disable Time | 1.6                                                         | 3.7 | 6.1 | 1.6                                                                                    | 6.1 |       |

| t <sub>PLZ</sub> |                     | 1.6                                                         | 3.6 | 6.1 | 1.6                                                                                    | 6.1 | ns    |

#### **Extended AC Characteristics**

| Symbol            | Parameter                                         | ı | V <sub>CC</sub> =<br>C <sub>L</sub> =<br>Eight Outpu | to +70°C<br>+5.0V<br>50 pF<br>tts Switching<br>te 3) | $T_A = 0^{\circ}C$ to $+70^{\circ}C$<br>$V_{CC} = +5.0V$<br>$C_L = 250$ pF<br>(Note 4) |     | Units |

|-------------------|---------------------------------------------------|---|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------|

|                   |                                                   |   | Min                                                  | Max                                                  | Min                                                                                    | Max | Ī     |

| t <sub>PLH</sub>  | Propagation Delay                                 |   | 1.0                                                  | 6.0                                                  | 2.3                                                                                    | 8.0 | ns    |

| t <sub>PHL</sub>  |                                                   |   | 1.0                                                  | 6.0                                                  | 2.3                                                                                    | 8.0 | 115   |

| t <sub>PZH</sub>  | Output Enable Time                                |   | 2.6                                                  | 8.5                                                  |                                                                                        |     | ns    |

| $t_{PZL}$         |                                                   |   | 2.6                                                  | 8.5                                                  |                                                                                        |     | 115   |

| t <sub>PHZ</sub>  | Output Disable Time                               |   | 1.6                                                  | 6.5                                                  |                                                                                        |     | ns    |

| $t_{PLZ}$         |                                                   |   | 1.6                                                  | 6.5                                                  |                                                                                        |     | 115   |

| t <sub>OSHL</sub> | Pin-to-Pin Skew<br>for HL Transitions (Note 5)    |   |                                                      | 1.3                                                  |                                                                                        |     | ns    |

| toslh             | Pin-to-Pin Skew                                   |   |                                                      | 17                                                   |                                                                                        |     | 20    |

|                   | for LH Transitions (Note 5)                       |   | 1.7                                                  |                                                      |                                                                                        |     | ns    |

| t <sub>OST</sub>  | Pin-to-Pin Skew<br>for HL/LH Transitions (Note 5) |   |                                                      | 3.0                                                  |                                                                                        |     | ns    |

Note 3: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase, i.e., all LOW-to-HIGH, HIGH-to-LOW, 3-STATE-to-HIGH, etc.

Note 4: These specifications guaranteed but not tested. The limits represent propagation delays with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load. This specification pertains to single output switching only.

Note 5: Skew is defined as the absolute value of the difference between the actual propagation delays for any two outputs of the same device. The specification applies to any outputs switching HIGH-to-LOW, (t<sub>OSHL</sub>), LOW-to-HIGH, (t<sub>OSLH</sub>), or HIGH-to-LOW and/or LOW-to-HIGH, (t<sub>OST</sub>). Specification guaranteed with all outputs switching in phase.

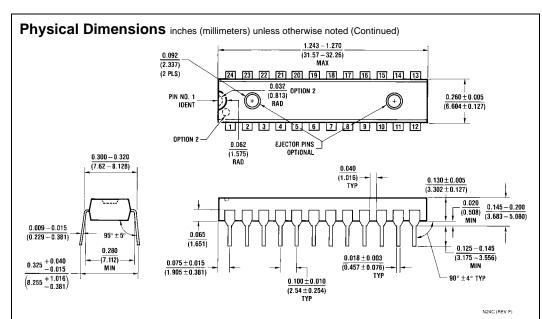

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide Package Number N24C

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com