## XRD6621

CMOS 10MSPS, 12-Bit, High Speed Analog-to-Digital Converter

April 1998-1

#### **FEATURES**

- 12-Bit Resolution

- 10 MSPS Sampling Rate

- On Chip Bandgap Reference

- DNL = ±0.4 LSB, INL = ±1.7 LSB

- Internal S/H Function

- Single Power Supply: 5V

- Differential Input

- 100% Digital Test Coverage

- Low Power: 360mW

- Latch-Up Free

- ESD Protection: 2kV Minimum

- Power Down Mode (<1mW)</li>

- 3 State Digital Outputs

#### **APPLICATIONS**

- Digital Scanners and Cameras

- Digital Copiers

- IR Image Digitizers

- Wireless Communications

- Video Capture

- XDSL Applications

#### **GENERAL DESCRIPTION**

The XRD6621 is a 12-bit Analog-to-Digital Converter. Designed using a standard 5V CMOS process, this part offers excellent performance, low power consumption and latch-up free operation.

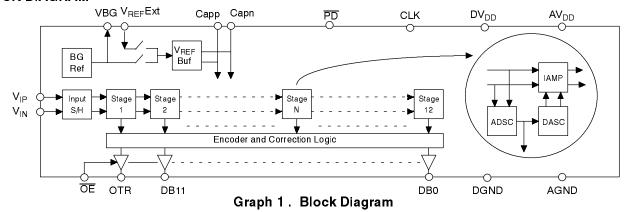

The XRD6621 uses a fully pipelined architecture. Each stage is composed of a 1-bit analog-to-digital subconverter (ADSC), a 1-bit digital-to-analog sub-converter (DASC), and a summing interstage amplifier (IAMP). By using stages with low resolution, high speed operation is possible. Digital correction logic removes any nonlinearity that would normally be caused by IAMP or ADSC offset. Overall ADC linearity depends only on capacitor ratio accuracy, thereby reducing performance variation with

temperature. All internal circuitry is fully differential for improved noise rejection.

An on-chip sample-and-hold (S/H) minimizes the input "kick-back", thereby reducing ADC input driver requirements and improves accuracy for high frequency inputs. A high accuracy on-chip reference is also provided.

The device operates from a single +5V supply. Typical power consumption is 360mW at FS=10MSPS.

The XRD6621 is specified for operation over the industrial (0 to  $+85^{\circ}$ C) temperature range.

#### **BLOCK DIAGRAM**

#### **ORDERING INFORMATION**

| Part No. Package |                              | Operating<br>Temperature Range |

|------------------|------------------------------|--------------------------------|

| XRD6621AIQ       | 32-pin TQFP (7 x 7 x 1.4mm)  | 0 to +85°C                     |

| XRD6621AIQ44     | 44-pin QFP (10 x 10 x 2.0mm) | 0 to +85°C                     |

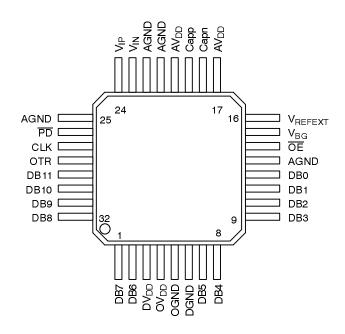

#### **PIN CONFIGURATION**

32 Lead TQFP (7 x 7 x 1.4mm)

## PIN DESCRIPTION 32 Pin TQFP

| Pin # | Symbol    | Description                                   |

|-------|-----------|-----------------------------------------------|

| 1     | DB7       | Data Output Bit 7.                            |

| 2     | DB6       | Data Output Bit 6.                            |

| 3     | $DV_DD$   | Digital Power Supply (Internal Decode Logic). |

| 4     | $OV_{DD}$ | Digital Power Supply (Output Drivers).        |

| 5     | OGND      | Digital Ground (Output Drivers).              |

| 6     | DGND      | Digital Ground (Internal Decode Logic).       |

| 7     | DB5       | Data Output Bit 5.                            |

### PIN DESCRIPTION (CONT'D)

| Pin # | Symbol       | Description                                             |

|-------|--------------|---------------------------------------------------------|

| 8     | DB4          | Data Output Bit 4.                                      |

| 9     | DB3          | Data Output Bit 3.                                      |

| 10    | DB2          | Data Output Bit 2.                                      |

| 11    | DB1          | Data Output Bit 1.                                      |

| 12    | DB0          | Data Output Bit 0 (LSB).                                |

| 13    | AGND         | Analog Ground.                                          |

| 14    | ŌĒ           | Output Enable Control.                                  |

| 15    | $V_{BG}$     | Internal Bandgap Reference Voltage.                     |

| 16    | $V_{REFEXT}$ | External Reference Input.                               |

| 17    | $AV_DD$      | Analog Power Supply.                                    |

| 18    | Capn         | Connect External Decoupling Cap for Negative Reference. |

| 19    | Сарр         | Connect External Decoupling Cap for Positive Reference. |

| 20    | $AV_DD$      | Analog Power Supply.                                    |

| 21    | AGND         | Analog Ground.                                          |

| 22    | AGND         | Analog Ground.                                          |

| 23    | $V_{IN}$     | Differential Negative Input.                            |

| 24    | $V_{IP}$     | Differential Positive Input.                            |

| 25    | AGND         | Analog Ground.                                          |

| 26    | PD           | Power Down Control.                                     |

| 27    | CLK          | Sampling Clock.                                         |

| 28    | OTR          | Out of Range Indicator.                                 |

| 29    | DB11         | Data Output Bit 11 (MSB).                               |

| 30    | DB10         | Data Output Bit 10.                                     |

| 31    | DB9          | Data Output Bit 9.                                      |

| 32    | DB8          | Data Output Bit 8.                                      |

# PIN DESCRIPTION (CONT'D) 32 Pin TQFP

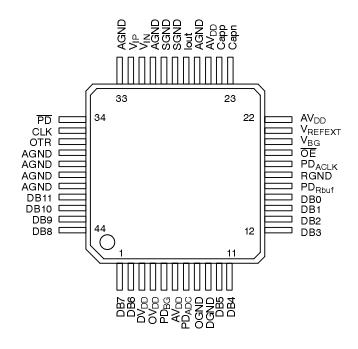

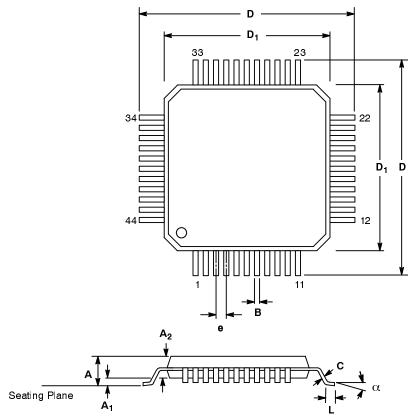

44 Lead QFP (10mm x 10mm)

# PIN DESCRIPTION 44 Pin QFP

| Pin # | Symbol            | Description                                       |

|-------|-------------------|---------------------------------------------------|

| 1     | DB7               | Data Output Bit 7.                                |

| 2     | DB6               | Data Output Bit 6.                                |

| 3     | $DV_DD$           | Digital Power Supply (Internal Decode Logic).     |

| 4     | $OV_DD$           | Digital Power Supply (Output Drivers).            |

| 5     | $PD_BG$           | Power Down Control for Bandgap Voltage Reference. |

| 6     | $AV_DD$           | Analog Power Supply.                              |

| 7     | PD <sub>ADC</sub> | Power Down Control for ADC Core.                  |

| 8     | OGND              | Digital Ground (Output Drivers).                  |

| 9     | DGND              | Digital Ground (Internal Decode Logic).           |

| 10    | DB5               | Data Output Bit 5.                                |

| 11    | DB4               | Data Output Bit 4.                                |

| 12    | DB3               | Data Output Bit 3.                                |

### PIN DESCRIPTION (CONT'D)

| Pin # | Symbol              | Description                                                       |  |  |  |  |  |

|-------|---------------------|-------------------------------------------------------------------|--|--|--|--|--|

| 13    | DB2                 | Data Output Bit 2.                                                |  |  |  |  |  |

| 14    | DB1                 | Data Output Bit 1.                                                |  |  |  |  |  |

| 15    | DB0                 | Data Output Bit 0 (LSB).                                          |  |  |  |  |  |

| 16    | PD <sub>RBUF</sub>  | Power Down Control for Reference Buffer.                          |  |  |  |  |  |

| 17    | RGND                | Analog Ground for Chopper-Stabailized Bandgap Reference.          |  |  |  |  |  |

| 18    | PD <sub>ACLK</sub>  | Power Down Control for ADC Clock Generator.                       |  |  |  |  |  |

| 19    | ŌĒ                  | Output Enable Control.                                            |  |  |  |  |  |

| 20    | $V_{BG}$            | Internal Bandgap Reference Voltage Output.                        |  |  |  |  |  |

| 21    | V <sub>REFEXT</sub> | External Reference Input.                                         |  |  |  |  |  |

| 22    | AV <sub>DD</sub>    | Analog Power Supply.                                              |  |  |  |  |  |

| 23    | Capn                | Connect External Decoupling Cap for Negative Reference.           |  |  |  |  |  |

| 24    | Сарр                | Connect External Decoupling Cap for Positive Reference.           |  |  |  |  |  |

| 25    | AV <sub>DD</sub>    | Analog Power Supply.                                              |  |  |  |  |  |

| 26    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 27    | lout                | Internal Bias Current Measurement Point. (Default is no Connect). |  |  |  |  |  |

| 28    | SGND                | Analog Ground (Connected to Substrate).                           |  |  |  |  |  |

| 29    | SGND                | Analog Ground (Connected to Substrate).                           |  |  |  |  |  |

| 30    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 31    | $V_{ N}$            | Differential Negative Input.                                      |  |  |  |  |  |

| 32    | V <sub>IP</sub>     | Differential Positive Input.                                      |  |  |  |  |  |

| 33    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 34    | PD                  | Power Down Control.                                               |  |  |  |  |  |

| 35    | CLK                 | Sampling Clock.                                                   |  |  |  |  |  |

| 36    | OTR                 | Out of Range Indicator.                                           |  |  |  |  |  |

| 37    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 38    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 39    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 40    | AGND                | Analog Ground.                                                    |  |  |  |  |  |

| 41    | DB11                | Data Output Bit 11 (MSB).                                         |  |  |  |  |  |

| 42    | DB10                | Data Output Bit 10.                                               |  |  |  |  |  |

| 43    | DB9                 | Data Output Bit 9.                                                |  |  |  |  |  |

| 44    | DB8                 | Data Output Bit 8.                                                |  |  |  |  |  |

| 1     | ı                   | ·                                                                 |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

Test Conditions: Unless otherwise specified:  $AV_{DD} = DV_{DD} = 5V$ , FS = 10MHz (50% Duty Cycle); ADCFS = 4VPP, Using External Reference = 2.48V,  $T_A = 25^{\circ}C$

| Symbol           | Parameter                     | Min. | Тур.   | Max.                       | Unit   | Conditions              |  |

|------------------|-------------------------------|------|--------|----------------------------|--------|-------------------------|--|

| Key Featur       | Key Features                  |      |        |                            |        |                         |  |

|                  | Resolution                    | 12   |        |                            | Bits   |                         |  |

| FS               | Maximum Sampling Rate         | 10   |        |                            | MSPS   |                         |  |

| Accuracy         |                               |      |        |                            |        |                         |  |

| DNL              | Differential Non-Linearity    | -0.7 | ±0.4   | +0.7                       | LSB    |                         |  |

| INL              | Integral Non-Linearity        |      | ±1.7   |                            | LSB    | Best Fit                |  |

|                  | Input Referred Offset         |      | 50     |                            | mV     |                         |  |

|                  | Input Referred Gain Error     |      | 2      |                            | %FS    |                         |  |

| CMRR             | Common Mode Rejection Ratio   |      | 64     |                            | dB     | F <sub>IN</sub> =100KHz |  |

|                  | DC PSRR from AV <sub>DD</sub> |      | 50     |                            | dB     |                         |  |

|                  | DC PSRR from DV <sub>DD</sub> |      | 80     |                            | dB     |                         |  |

|                  | Zero Error Drift              |      | 15     |                            | μV/°C  |                         |  |

|                  | Gain Error Drift              |      | 0.003  |                            | %FS/°C |                         |  |

| Bandgap R        |                               |      |        |                            |        |                         |  |

| V <sub>REF</sub> | Reference Voltage             | 1.10 | 1.24   | 1.30                       | V      |                         |  |

| $TC_BG$          | TempCo                        |      | 60     |                            | ppm/°C |                         |  |

|                  | Output Impedance              |      | 100    |                            | kΩ     |                         |  |

| Reference        | Buffer                        |      |        |                            |        |                         |  |

|                  | Gain                          |      | 1/1.24 |                            | V/V    |                         |  |

| $TC_RB$          | TempCo                        |      | 40     |                            | ppm/°C |                         |  |

|                  | Input Impedance               |      | 50     |                            | kΩ     |                         |  |

| Analog Inp       | out                           |      |        |                            |        |                         |  |

| BW               | Bandwidth(-1dB)               |      | 600    |                            | MHz    |                         |  |

| $V_{ID}$         | Differential Input Range      |      |        | ±V <sub>REF</sub><br>/1.24 | V      | 4VPP full scale max.    |  |

| $V_{ICM}$        | Common Mode Input Range       | 0    |        | $AV_DD$                    | V      |                         |  |

| $V_{REFExt}$     | External Reference Voltage    | 0.5  |        | 2.5                        | V      |                         |  |

| $R_{IN}$         | Input Resistance              |      | *      |                            |        | *See Graph 5 .          |  |

| $C_{IN}$         | Input Capacitance             |      |        | 10                         | pF     |                         |  |

## **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Symbol          | Parameter                                           | Min.                  | Тур.     | Max. | Unit     | Conditions                      |  |

|-----------------|-----------------------------------------------------|-----------------------|----------|------|----------|---------------------------------|--|

| AC Parameters   |                                                     |                       |          |      |          |                                 |  |

| SNR             | Signal-to-Noise Ratio<br>(F <sub>IN</sub> =1.0MHz)  | 64<br>63              | 67<br>66 |      | dB<br>dB | XRD6621AIQ44<br>XRD6621AIQ      |  |

| SNR             | Signal-to-Noise Ratio<br>(F <sub>IN</sub> =3.6MHz)  | 62                    | 66       |      | dB       | Both packages                   |  |

| SNR             | Signal-to-Noise Ratio<br>(F <sub>IN</sub> = 10MHz)  |                       | 62       |      | dB       |                                 |  |

| THD             | Total Harmonic Distortion (F <sub>IN</sub> =1.0MHz) | 70                    |          |      | dB       |                                 |  |

| THD             | Total Harmonic Distortion (F <sub>IN</sub> =3.6MHz) | 60                    |          |      | dB       |                                 |  |

| SINAD           | SNR + Distortion<br>(F <sub>IN</sub> = 1.0 MHz)     | 63<br>62              | 66<br>65 |      | dB<br>dB | XRD6621AIQ44<br>XRD6621AIQ      |  |

| SINAD           | SNR + Distortion<br>(F <sub>IN</sub> = 3.6 MHz)     | 60                    | 64       |      | dB       | Both packages                   |  |

| SINAD           | SNR + Distortion<br>(F <sub>IN</sub> = 10 MHz)      |                       | 60       |      | dB       |                                 |  |

| ENOB            | Effective Bits (F <sub>IN</sub> =1.0MHz)            |                       | 10.7     |      | Bits     |                                 |  |

| ENOB            | Effective Bits (F <sub>IN</sub> =3.6MHz)            |                       | 10.7     |      | Bits     |                                 |  |

| ENOB            | Effective Bits<br>(FIN = 10MHZ)                     |                       | 9.7      |      | Bits     |                                 |  |

| IMD             | Intermodulation Distortion                          | -64                   | -67      |      | dBc      |                                 |  |

| SFDR            | Spurious-Free Dynamic<br>Range                      | 75                    | 80       |      | dBc      | F <sub>IN</sub> = 1.0MHz        |  |

| DG              | Differential Gain                                   |                       | 0.5      |      | %        |                                 |  |

| DP              | Differential Phase                                  |                       | 0, 1     |      | ٥        |                                 |  |

| FPBW            | Full Power Bandwidth                                |                       | 70       |      | MHz      |                                 |  |

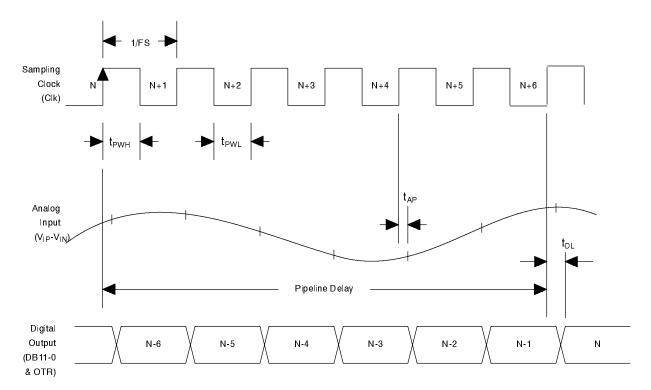

| $t_{AP}$        | Aperture Delay Time                                 |                       | 3        |      | ns       |                                 |  |

| ∆ta             | Aperture Jitter                                     |                       | 7        |      | ps-rms   |                                 |  |

| Digital Input   | ts                                                  |                       |          |      |          |                                 |  |

| $V_{IH}$        | Digital Input High Voltage                          | AV <sub>DD</sub> -1   |          |      | V        |                                 |  |

| $V_{IL}$        | Digital Input Low Voltage                           |                       |          | 1    | V        |                                 |  |

| I <sub>IN</sub> | DC Leakage Currents                                 |                       | 70       |      | μΑ       |                                 |  |

|                 | Input Capacitance                                   |                       | 10       |      | pF       |                                 |  |

| Digital Outp    | uts                                                 | 1                     |          |      | 1        |                                 |  |

| V <sub>OH</sub> | Output High Voltage                                 | DV <sub>DD</sub> -0.5 |          |      | V        | $C_L = 75pf, R_L = 1m\Omega$    |  |

| V <sub>OL</sub> | Output Low Voltage                                  |                       |          | 0.4  | V        | $C_L = 75pF$ , $R_L = 1m\Omega$ |  |

| CL              | Max Capacitive Load                                 |                       | 75       |      | pF       |                                 |  |

#### **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Symbol            | Parameter                     | Min. | Тур. | Max. | Unit             | Conditions                               |

|-------------------|-------------------------------|------|------|------|------------------|------------------------------------------|

| OZ                | High-Z Leakage                | -10  |      | 10   | μΑ               |                                          |

| t <sub>DL</sub>   | Data Valid Delay              |      | 18   |      | ns               |                                          |

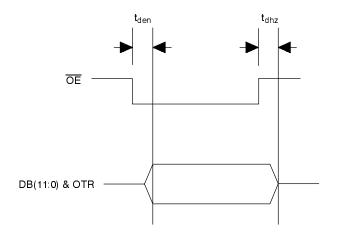

| t <sub>DEN</sub>  | Data Enable Delay             |      | 10   |      | ns               |                                          |

| t <sub>DHZ</sub>  | Data High-Z Delay             |      | 8    |      | ns               |                                          |

|                   | Pipeline Delay (Latency)      |      | 6    |      | cycles           | Relationship between CLK and data output |

| Power Supp        | olies                         |      |      |      |                  |                                          |

| PDI <sub>DD</sub> | Power Down (I <sub>DD</sub> ) |      | 500  |      | μΑ               |                                          |

| AV <sub>DD</sub>  | Operating Voltage             |      | 5    |      | V                |                                          |

| DV <sub>DD</sub>  | Digital Supply Voltage        |      | 5    |      | V                |                                          |

| OV <sub>DD</sub>  | Digital Output Voltage        |      |      |      | DV <sub>DD</sub> |                                          |

| <sub>VDD</sub>    | Supply Current                |      | 72   | 75   | mA               |                                          |

#### Specifications are subject to change without notice

#### ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND                                              | Package Power Dissipation Rating to 75°C       |

|---------------------------------------------------------------------|------------------------------------------------|

| V <sub>BT</sub> & V <sub>BB</sub> V <sub>DD</sub> +0.5 to GND -0.5V | 32-pinTQFP 1000mW                              |

| V <sub>IN</sub> V <sub>DD</sub> +0.5 to GND -0.5V                   | Derates above 75°C 18mW/°C                     |

|                                                                     | Lead Temperature (Soldering 10 seconds) +300°C |

| All Inputs                                                          | 44-pin PQFP 110°mW                             |

| All Outputs V <sub>DD</sub> +0.5 to GND -0.5V                       | Derates above 75° C 15mW/°C                    |

| Storage Temperature65 to +150°C                                     | ESD 2KV                                        |

#### Notes:

$^{3}$   $V_{DD}$  refers to  $AV_{DD}$  and  $DV_{DD}$ . GND refers to AGND and DGND.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

Graph 2. Timing Diagram

Graph 3. Data Delay and Data Enable Timing

#### THEORY OF OPERATION

#### Analog Input (VIP, VIN)

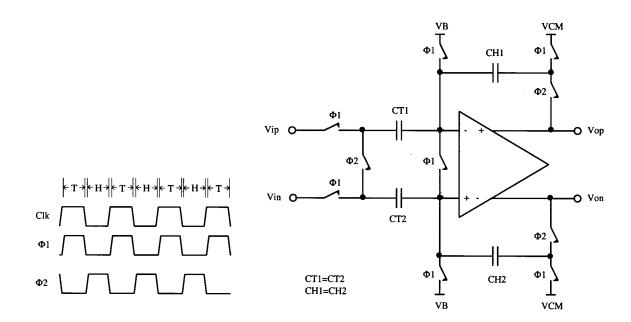

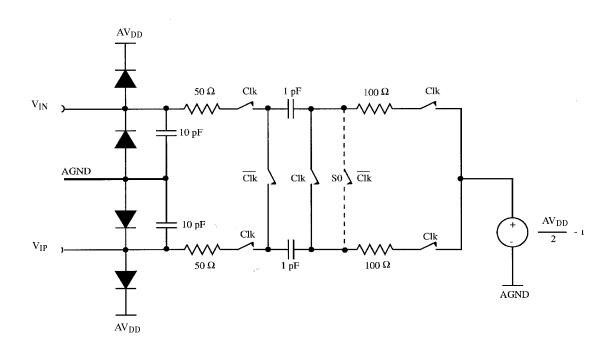

Internally, the XRD6621 is a fully differential part. However, the ADC can be easily configured to use single-ended input instead. Due to differential architecture of the ADC, using input differential signals will lead to better common-mode distortion and noise performance. The input has a wide common-mode compliance range and a very good common-mode rejection. *Graph 4* shows the simplified schematic of the input Track/Hold. The operation of switches is controlled by internally generated non-overlapping signals  $\Phi 1$  and  $\Phi 2$ .

In track mode, capacitors CT1 and CT2 configured in series charge up to the input differential voltage, while the bottom plates of CT1 and CT2 are held at an internally generated bias voltage VB. During the hold time the charge stored in CT1 and CT2 will be transferred to hold capacitors CH1 and CH2. Consequently the output voltage represents the input voltage at the sampling moment. The equivalent circuit of the input Track/Hold stage is shown in *Graph 5*. Note that switch S0 does not exist physically. It is added to model virtual ground at the input of the Track/Hold Op Amp during hold time.

Graph 4. XRD6621 Simplified Block Diagram of Track/Hold Circuit

Graph 5. Simplified Input Circuit

#### Out of Range Indicator (OTR)

The out of range indicator is used to indicate a fault condition. This signal will go high if the input exceeds the conversion range of the ADC, i.e. the input is above  $+V_{REF}/1.24$  or below  $-V_{REF}/1.24$ . This bit can be combined with the MSB to indicate if the input is too positive or too negative. This bit will also go high if the correction range of the digital correction logic is exceeded. This is typically caused by running the ADC with a Vref that is too small.

#### Output Enable (OE)

This signal controls the tri-state drivers on the digital outputs DB11-DB0 and OTR. During normal operation  $\overline{\text{OE}}$  should be held low so that all outputs are enabled. If  $\overline{\text{OE}}$  is driven high DB11-0 and OTR go into high impedance mode. This control operates asynchronous to the clock and will only control the output drivers. The internal output registers will get updated independent of  $\overline{\text{OE}}$  setting.

#### Power Down Control (PD's)

Depending on the package, the XRD6621 has a number of power down modes available. In the 32-pin package, the only control is PD. Pulling PD signal low will disconnect the input clock, turn off all internal cells and set the output word DB11-0 and OTR to DGND. If high impendance outputs are desired in PD mode, OE should be pulled high. The turn on time from switching out of power down mode will be set by the time it takes for the internal V<sub>BEE</sub> buffer to charge up the external decoupling caps connected to Capp and Capn. Typically for 2.2μF decoupling caps this time will be about 30ms. In the 44-pin package, there are four more power down controls available for different internal cells. Typically these controls would be used only for debugging purposes. Table 1 explains which cell each power down option controls.

| Pin<br>Name        | Effected Cell                                                                                                                                                                          |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PD <sub>ADC</sub>  | The bias current to the core ADC is shut-<br>down. The master bias generator, reference<br>buffer and bandgap reference will still oper-<br>ate. (44 pin package only)                 |  |  |  |  |  |  |

| PD <sub>RBuf</sub> | The bias current to the reference buffer is shutdown. This allows for an external reference buffer to be used. (44 pin package only)                                                   |  |  |  |  |  |  |

| PD <sub>BG</sub>   | The bias current and clock input to the chopper stabilized bandgap reference is shut off. This reduces power supply noise from the F <sub>CLK</sub> /20 chopper. (44 pin package only) |  |  |  |  |  |  |

| PD <sub>ACLK</sub> | The main input clock is shut off. The bandgap clock is unaffected. (44 pin package only)                                                                                               |  |  |  |  |  |  |

| PD                 | PD <sub>BG</sub> , PD <sub>ACLK</sub> are activated and the output register clock is shut off.                                                                                         |  |  |  |  |  |  |

Table 1. Power Down Controls

#### **Power Supplies**

Internally the XRD6621 contains several independent power supplies. One set of supplies is  $AV_{DD}$  and AGND. These supplies connect to all of the sensitive analog and digital circuitry. This circuitry includes the core of the ADC (ADC op-amps and comparators), the master bias generator, the bandgap reference, bandgap reference buffer, and master clock generator. The next supply is  $DV_{DD}$  and DGND. This supply is connected to the digital

correction logic.  $OV_{DD}$  may be connected to a lower power supply (such as 3.3V or 3.0V) to simplify interfacing to lower voltage logic. DGND may also be lifted above AGND. All of the inputs to the ADC are relative to  $AV_{DD}$ . This was done to avoid generating non-50% duty cycle clocks with slow rise/fall time sampling clocks. RGND should be connected to AGND, (44 pin package only). This is the reference ground for  $V_{BG}$  and  $V_{RG}$  and  $V_{RG}$ .

Internally, the bulk node of all NMOS devices (i.e. the substrate) is connect to a separate supply line called SGND. This separate supply line is used to help isolate power supply coupling from AGND and DGND. In the 32-pin package, SGND is connected to AGND.  $\mbox{DV}_{DD}$  and DGND are connected only to the internal digital decode logic.  $\mbox{OV}_{DD}$  and OGND are connected only to the digital output drivers. Internally, there is also a shielding line that helps to isolate very sensitive nodes. This line is connected internally to AGND.

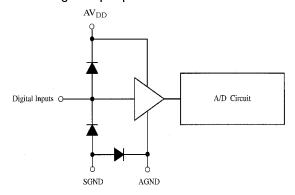

Graph 6 shows the power supply connection as it pertains to digital input pins.

Graph 6 . XRD6621 Power Supply Connection for Digital Inputs.

#### **Logic Output Interface**

The digital output drive circuitry of the XRD6621 is designed to operate from the analog and digital supplies. The  $OV_{DD}$  pin of the XRD6621 is a separate power supply dedicated to the logic output drivers.  $OV_{DD}$  is not connected internally to any of the other power supplies. *Graph 7* illustrates the power supply circuitry of the XRD6621.

Graph 7 . XRD6621 Power Supply Circuit Provides a Separate Supply Line for Digital Output Pins

$\mbox{OV}_{\mbox{DD}}$  and OGND connected directly to the digital output pins. OGND is not common to the XRD6621 substrate. The XRD6621 substrate is common to the packages' SGND pins for the 44-pin QFP package and AGND pins for the 32-pin TQFP. Best Spectral performance is obtained with  $\mbox{OV}_{\mbox{DD}}$  lowered to 3.3V.

#### Reference Control (V<sub>BG</sub>, Vref<sub>Ext</sub>, Capp, Capn)

The XRD6621 includes an onboard chopper stabilized bandgap reference with a nominal output voltage of Vref. The bandgap will not function when the ADC is not clocked.

A high impedance output version of internal bandgap voltage is available on pin  $V_{BG}$ . This voltage must be buffered, and should be decoupled to RGND (AGND 32 pin package), before it is used. An external override control is available. If an input below approximately  $AV_{DD}$ -1V is applied to  $Vref_{Ext}$  then the external applied voltage is used for Vref. This option allows the use of an alternate bandgap reference or the use of an external op-amp to gain up or to attenuate  $V_{BG}$  to change the full scale range of the ADC.  $V_{REFExt}$  should be pulled up to  $AV_{DD}$  to select the internal bandgap reference voltage.

$V_{REF}$  (either externally applied or from the bandgap reference) is buffered by the reference buffer. This buffer has a nominal gain of 1/1.24 resulting in an input to the ADC of 1V when using the internal reference. A 1V input corresponds to a 2VPP full scale voltage on the ADC. The pins Capp and Capn connect to the output of the reference buffer and must be bypassed with capacitors. A parallel combination of a 2.2 $\mu$ F tantalum and a 0.1 $\mu$ F low inductance ceramic capacitor is recommended.

In the 44 pin package it is possible to shut off the reference buffer and connect an external buffer. The reference buffer is shut off by pulling PD<sub>RBUF</sub> high. In this mode of operation, the external buffer must generate a differential reference voltage centered near AV<sub>DD</sub>/2.

#### **Digital Testing**

As with any ADC that includes error correction, it is possible that a fault in the digital correction logic would not be detected with standard all codes testing. The XRD6621 includes a special mode that will guarantee 100% stuck-at-fault coverage. To initiate the test,  $V_{BG}$  should be pulled to  $AV_{DD}$  and a positive full scale input should be applied. The output code should be verified to be DB11=1, DB10-0=0. That, in combination with the standard all codes test, will ensure 100% stuck-at-fault coverage. This test is performed on all parts shipped.

#### **Default Modes**

Default settings are provided for all options through the use of internal  $100k\Omega$  equivalent pull-up or pull-down resistors. *Table 2* shows the default settings.

| Pin<br>Name        | Default Setting                             |  |  |  |

|--------------------|---------------------------------------------|--|--|--|

| PD <sub>ADC</sub>  | SGND - Core of ADC is on                    |  |  |  |

| PD <sub>Rbuf</sub> | SGND - Reference buffer is on               |  |  |  |

| PD <sub>BG</sub>   | SGND - Bandgap reference is on              |  |  |  |

| PD <sub>ACLK</sub> | SGND - Two phase clock generator is running |  |  |  |

| ŌĒ                 | SGND - Outputs are enabled                  |  |  |  |

| PD                 | AV <sub>DD</sub> - part is powered on       |  |  |  |

Table 2. Default Digital Control Settings

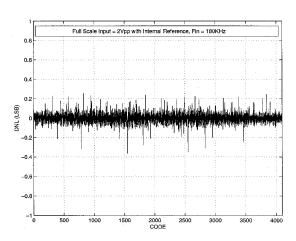

Graph 1. DNL Vs. Code

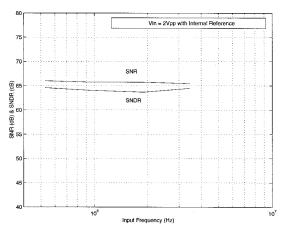

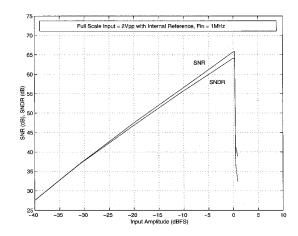

Graph 2 . SNR and SNDR vs. Fin, Internal Reference

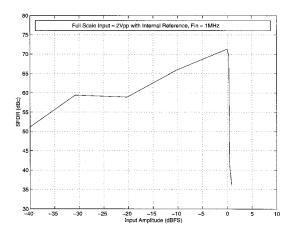

Graph 3. SNR and SNDR vs. Fin, Input Amplitude

Graph 4. SFDR vs. Input Amplitude

Graph 5. Best Fit INL Vs. Code

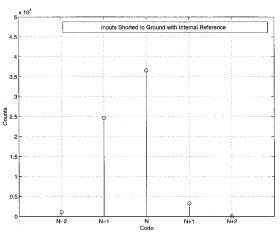

Graph 6 . Output Noise Histogram

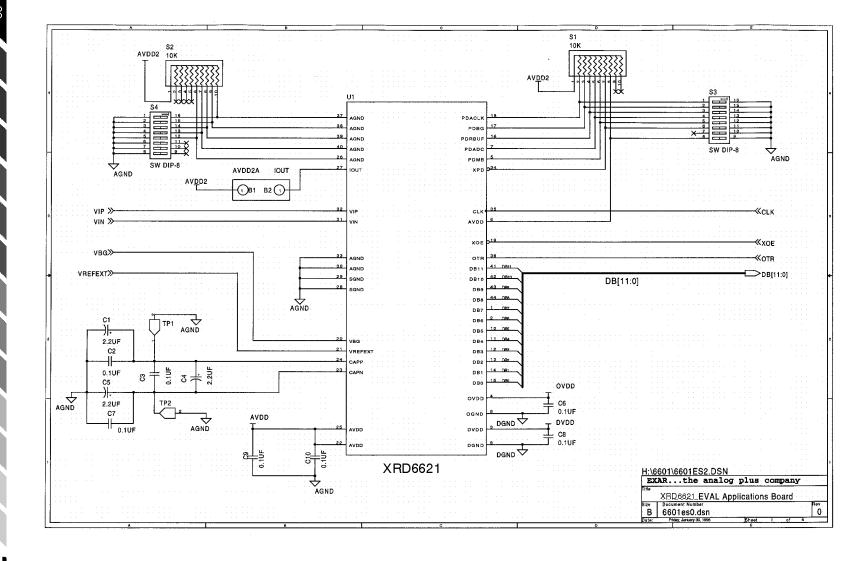

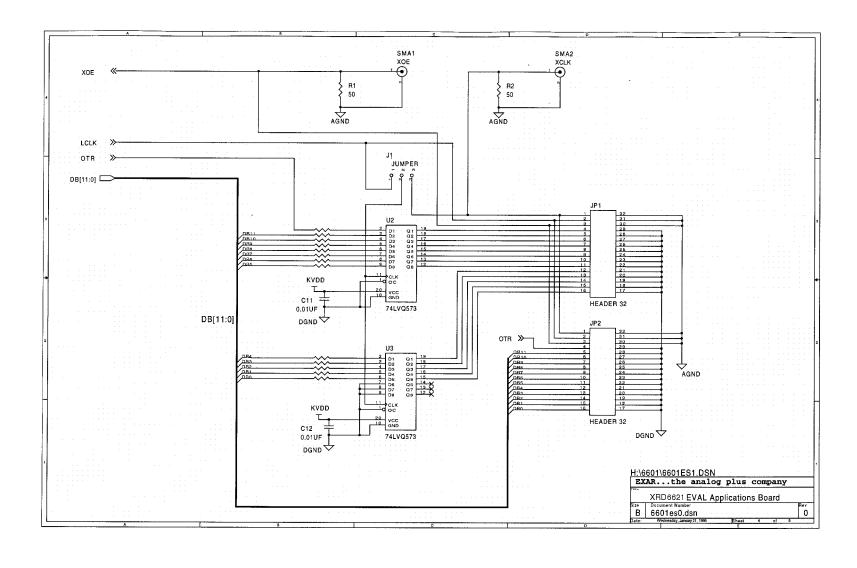

Graph 7. Application Schematic Sheet 1 of 6

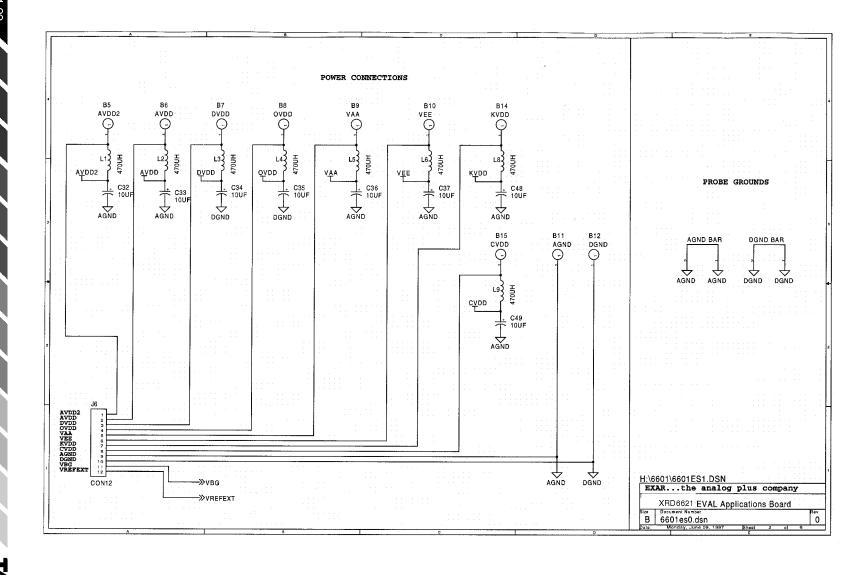

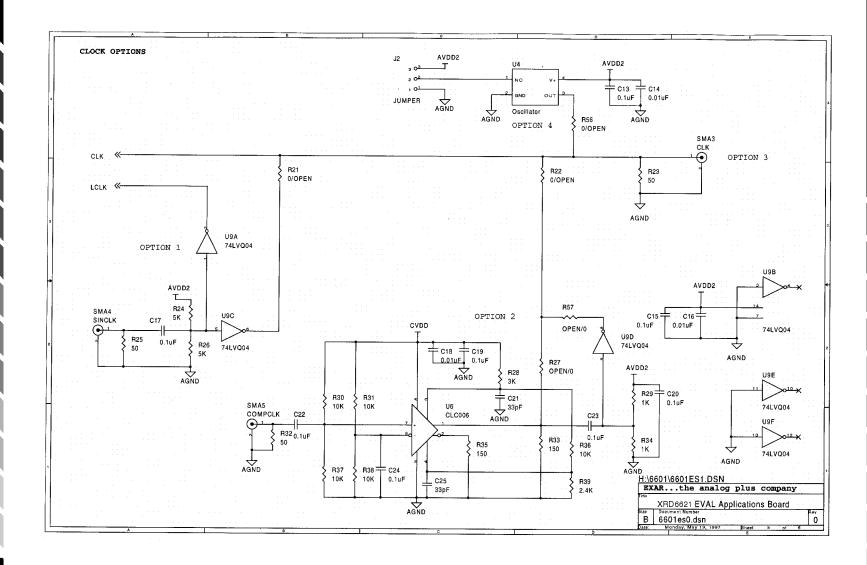

Graph 8. Application Schematic Sheet 2 of 6

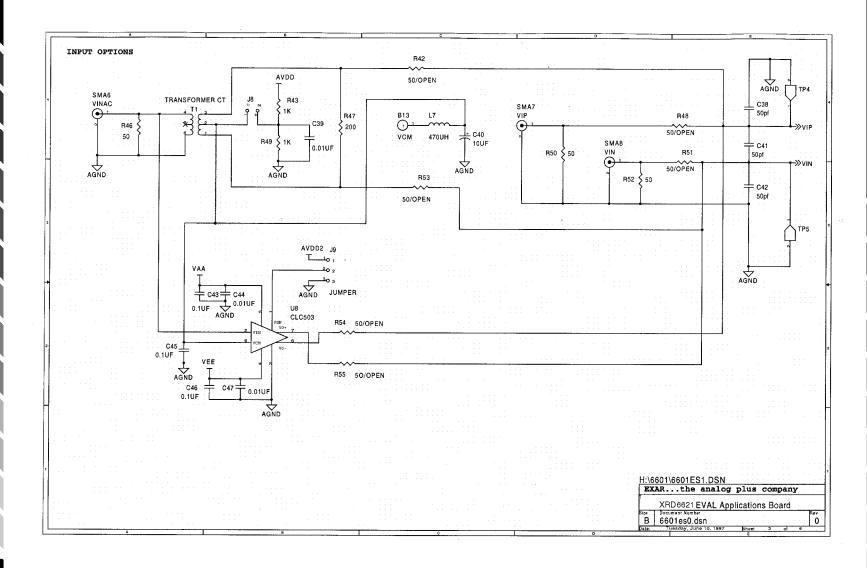

Graph 9. Application Schematic Sheet 3 of 6

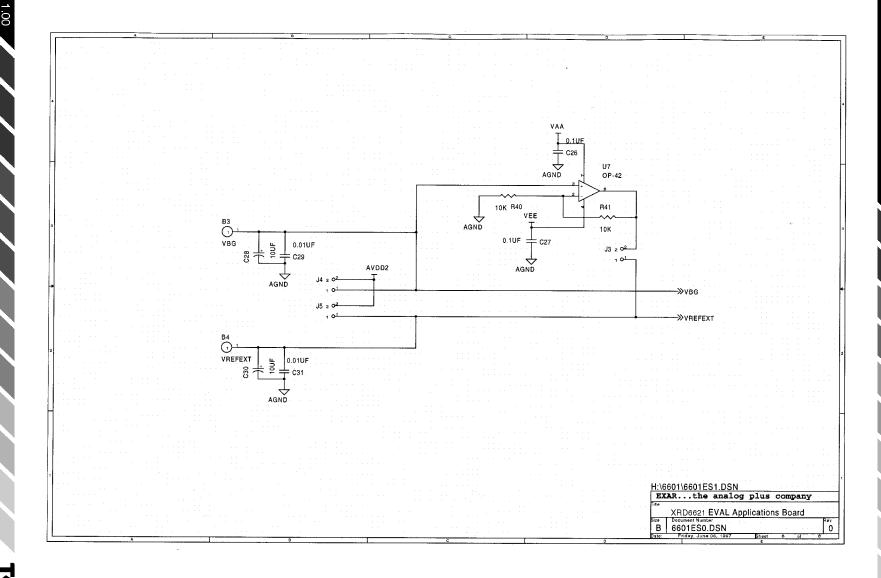

Graph 10. Application Schematic Sheet 4 of 6

19

Graph 11 . Application Schematic Sheet 5 of 6

M O I

Graph 12. Application Schematic Sheet 6 of 6

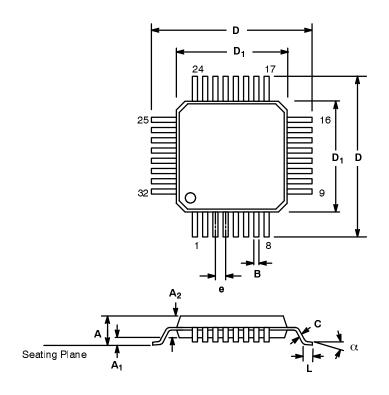

# 32 LEAD THIN QUAD FLAT PACK (7 x 7 x 1.4 mm TQFP)

Rev. 2.00

|                | INC   | HES        | MILLIM | ETERS |

|----------------|-------|------------|--------|-------|

| SYMBOL         | MIN   | MIN MAX    |        | MAX   |

| А              | 0.055 | 0.063      | 1.40   | 1.60  |

| A <sub>1</sub> | 0.002 | 0.006      | 0.05   | 0.15  |

| A <sub>2</sub> | 0.053 | 0.057      | 1.35   | 1.45  |

| В              | 0.012 | 0.018      | 0.30   | 0.45  |

| С              | 0.004 | 0.008      | 0.09   | 0.20  |

| D              | 0.346 | 0.362      | 8.80   | 9.20  |

| D <sub>1</sub> | 0.272 | 0.280      | 6.90   | 7.10  |

| е              | 0.03  | 0.0315 BSC |        | BSC   |

| L              | 0.018 | 0.030      | 0.45   | 0.75  |

| α              | o°    | 7°         | o°     | 7°    |

Note: The control dimension is the millimeter column

# 44 LEAD PLASTIC QUAD FLAT PACK (10 mm X 10 mm X 2.0 mm, QFP)

Rev. 1.00

1.95 mm Form

|                | INCHES     |       | MILLIMETERS |       |

|----------------|------------|-------|-------------|-------|

| SYMBOL         | MIN        | MAX   | MIN         | МАХ   |

| А              | 0.078      | 0.085 | 1.97        | 2.35  |

| A <sub>1</sub> | 0.001      | 0.010 | 0.02        | 0.25  |

| A <sub>2</sub> | 0.077      | 0.083 | 1.95        | 2.00  |

| В              | 0.012      | 0.018 | 0.30        | 0.45  |

| С              | 0.005      | 0.009 | 0.13        | 0.23  |

| D              | 0.537      | 0.557 | 13.65       | 14.15 |

| D <sub>1</sub> | 0.390      | 0.398 | 9.90        | 10.10 |

| е              | 0.0315 BSC |       | 0.80 BSC    |       |

| L              | 0.026      | 0.037 | 0.65        | 0.95  |

| α              | o°         | 7°    | 0°          | 7°    |

Note: The control dimension is the millimeter column

## **Notes**

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1998 EXAR Corporation

Datasheet January 1998

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.