# THC63LVD824

Single(135MHz)/Dual(170MHz) Link LVDS Receiver for XGA/SXGA/SXGA+/UXGA

#### **General Description**

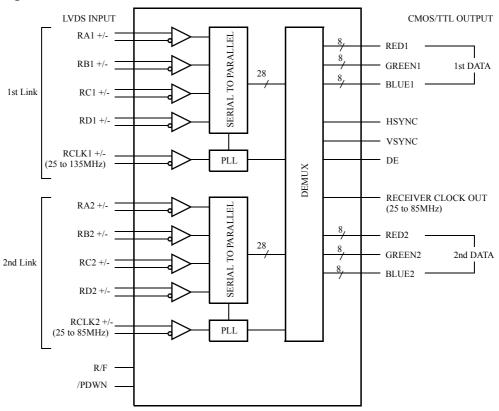

The THC63LVD824 receiver is designed to support Single Link transmission between Host and Flat Panel Display up to SXGA+ resolutions and Dual Link transmission between Host and Flat Panel Display up to UXGA resolutions. The THC63LVD824 converts the LVDS data streams back into 48bits of CMOS/TTL data with falling edge or rising edge clock for convenient with a variety of LCD panel controllers.

In Single Link, data transmit clock frequency of 135MHz, 48bits of RGB data are transmitted at an effective rate of 945Mbps per LVDS channel. Using a 135MHz clock, the data throughput is 472Mbytes per second.

In Dual Link, data transmit clock frequency of 85MHz, 48bits of RGB data are transmitted at an effective rate of 595Mbps per LVDS channel. Using a 85MHz clock, the data throughput is 595Mbytes per second.

#### **Features**

- Wide dot clock range: 25-170MHz suited for VGA, SVGA, XGA, SXGA, SXGA+ and UXGA

- PLL requires No external components

- Supports Single Link up to 135MHz dot clock for SXGA+

- Supports Dual Link up to 170MHz dot clock for UXGA

- 50% output clock duty cycle

- TTL clock edge programmable

- TTL output driverbility selectable for lower EMI

- Power down mode

- Low power single 3.3V CMOS design

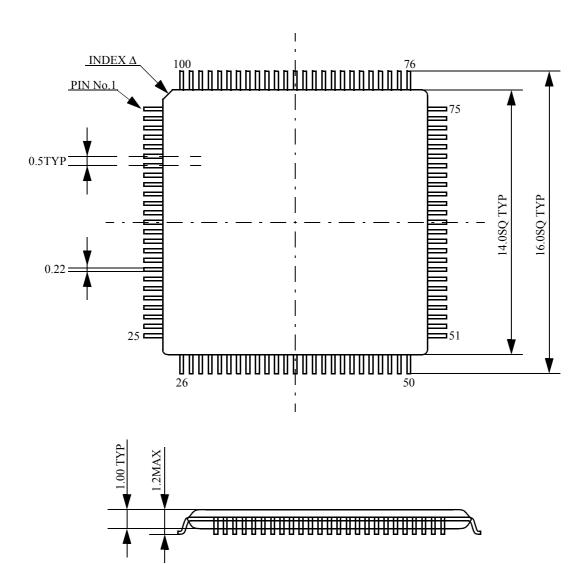

- 100pin TQFP

- THC63LVDF84B compatible

#### **Block Diagram**

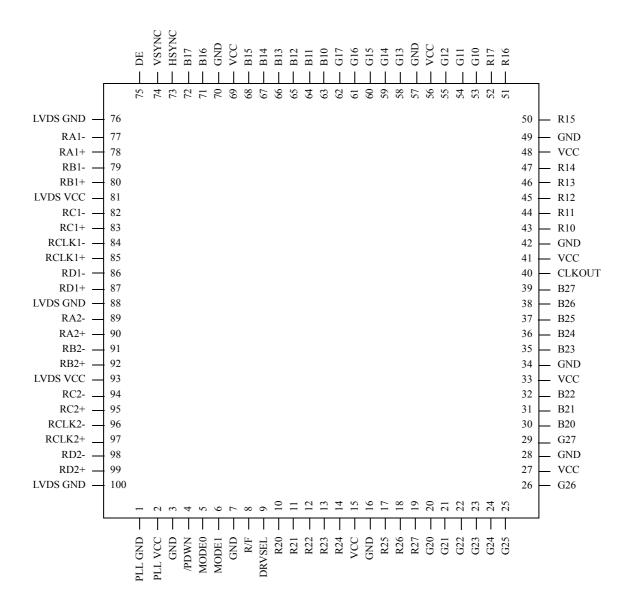

### Pin Out

## Pin Description

| Pin Name       | Pin #                               | Type    | Description                                                           |  |  |

|----------------|-------------------------------------|---------|-----------------------------------------------------------------------|--|--|

| RA1+, RA1-     | 78, 77                              | LVDS IN |                                                                       |  |  |

| RB1+, RB1-     | 80, 79                              | LVDS IN | The let I inly The let mined innect data suban Dual I inly            |  |  |

| RC1+, RC1-     | 83, 82                              | LVDS IN | The 1st Link. The 1st pixel input data when Dual Link.                |  |  |

| RD1+, RD1-     | 87, 86                              | LVDS IN |                                                                       |  |  |

| RCLK1+, RCLK1- | 85, 84                              | LVDS IN | LVDS Clock Input for 1st Link.                                        |  |  |

| RA2+, RA2-     | 90, 89                              | LVDS IN |                                                                       |  |  |

| RB2+, RB2-     | 92, 91                              | LVDS IN | The 2nd Link There wise are disabled when Single Link                 |  |  |

| RC2+, RC2-     | 95, 94                              | LVDS IN | The 2nd Link. These pins are disabled when Single Link.               |  |  |

| RD2+, RD2-     | 99, 98                              | LVDS IN |                                                                       |  |  |

| RCLK2+, RCLK2- | 97, 96                              | LVDS IN | LVDS Clock Input for 2nd Link.                                        |  |  |

| R17 ~ R10      | 52, 51, 50, 47,<br>46, 45, 44, 43   | OUT     |                                                                       |  |  |

| G17 ~ G10      | 62, 61, 60, 59,<br>58, 55, 54, 53   | OUT     | The 1st Pixel Data Outputs.                                           |  |  |

| B17 ~ B10      | 72, 71, 68, 67,<br>66, 65, 64, 63   | OUT     |                                                                       |  |  |

| R27 ~ R20      | 19, 18, 17, 14,<br>13, 12, 11, 10   | OUT     |                                                                       |  |  |

| G27 ~ G20      | 29, 26, 25, 24,<br>23, 22, 21, 20   | OUT     | The 2nd Pixel Data Outputs.                                           |  |  |

| B27 ~ B20      | 39, 38, 37, 36,<br>35, 32, 31, 30   | OUT     |                                                                       |  |  |

| DE             | 75                                  | OUT     | Data Enable Output.                                                   |  |  |

| VSYNC          | 74                                  | OUT     | Vsync Output.                                                         |  |  |

| HSYNC          | 73                                  | OUT     | Hsync Output.                                                         |  |  |

| CLKOUT         | 40                                  | OUT     | Clock Output.                                                         |  |  |

| DRVSEL         | 9                                   | IN      | Output Driverbility Select.                                           |  |  |

| DRVSLL         | ,                                   | 111     | H: High power, L: Low power.                                          |  |  |

| R/F            | 8                                   | IN      | Output Clock Triggering Edge Select.                                  |  |  |

| 10/1           | Ö                                   | 111     | H: Rising edge, L: Falling edge.                                      |  |  |

| MODE1, MODE0   | 6, 5                                | IN      | Pixel Data Mode.    MODE1   MODE0   Mode                              |  |  |

| /PDWN          | 4                                   | IN      | H: Normal operation, L: Power down (all outputs are pulled to ground) |  |  |

| VCC            | 15, 27, 33, 41,<br>48, 56, 69       | Power   | Power Supply Pins for TTL outputs and digital circuitry.              |  |  |

| GND            | 3, 7, 16, 28, 34,<br>42, 49, 57, 70 | Ground  | Ground Pins for TTL outputs and digital circuitry.                    |  |  |

| LVDS VCC       | 81,93                               | Power   | Power Supply Pins for LVDS inputs.                                    |  |  |

| LVDS GND       | 76, 88, 100                         | Ground  | Ground Pins for LVDS inputs.                                          |  |  |

| Pin Name | Pin # | Type   | Description                         |

|----------|-------|--------|-------------------------------------|

| PLL VCC  | 2     | Power  | Power Supply Pin for PLL circuitry. |

| PLL GND  | 1     | Ground | Ground Pin for PLL circuitry.       |

# Absolute Maximum Ratings 1

| Supply Voltage (V <sub>CC</sub> )   | -0.3V ~ +4.0V                |

|-------------------------------------|------------------------------|

| CMOS/TTL Input Voltage              | $-0.3V \sim (V_{CC} + 0.3V)$ |

| CMOS/TTL Output Voltage             | $-0.3V \sim (V_{CC} + 0.3V)$ |

| LVDS Receiver Input Voltage         | $-0.3V \sim (V_{CC} + 0.3V)$ |

| Output Current                      | -30mA ~ 30mA                 |

| Junction Temperature                | +125°C                       |

| Storage Temperature Range           | -55°C ~+125°C                |

| Lead Temperature (Soldering, 10sec) | +230°C                       |

| Maximum Power Dissipation @+25°C    | 1.0W                         |

#### **Electrical Characteristics**

### **CMOS/TTL DC Specifications**

$V_{CC} = 3.0 V \sim 3.6 V$ ,  $Ta = -10 °C \sim +70 °C$

|                  |                           |                                                               | CC   |      |          |       |

|------------------|---------------------------|---------------------------------------------------------------|------|------|----------|-------|

| Symbol           | Parameter                 | Conditions                                                    | Min. | Тур. | Max.     | Units |

| $V_{IH}$         | High Level Input Voltage  |                                                               | 2.0  |      | $V_{CC}$ | V     |

| V <sub>IL</sub>  | Low Level Input Voltage   |                                                               | GND  |      | 0.8      | V     |

| $V_{OH}$         | High Level Output Voltage | $I_{OH}$ = -2mA, -4mA (data)<br>$I_{OH}$ = -4mA, -8mA (clock) | 2.4  |      |          | V     |

| V <sub>OL</sub>  | Low Level Output Voltage  | $I_{OL}$ = 2mA, 4mA (data)<br>$I_{OL}$ = 4mA, 8mA (clock)     |      |      | 0.4      | V     |

| I <sub>INC</sub> | Input Current             | $0V \le V_{\rm IN} \le V_{\rm CC}$                            |      |      | ±10      | μΑ    |

## **LVDS Receiver DC Specifications**

$V_{CC} = 3.0 V \sim 3.6 V$ ,  $Ta = -10 \,^{\circ}C \sim +70 \,^{\circ}C$

| Symbol   | Parameter                         | Conditions             | Min. | Тур. | Max. | Units |

|----------|-----------------------------------|------------------------|------|------|------|-------|

| $V_{TH}$ | Differential Input High Threshold | $V_{OC} = 1.2V$        |      |      | 100  | mV    |

| $V_{TL}$ | Differential Input Low Threshold  | $V_{OC} = 1.2V$        | -100 |      |      | mV    |

| I        | Innut Current                     | $V_{IN} = 2.4 V / 0 V$ |      |      | ±20  | 4     |

| INL      | Input Current                     | $V_{CC} = 3.6V$        |      |      | ±20  | μΑ    |

<sup>1. &</sup>quot;Absolute Maximum Ratings" are those valued beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

# **Supply Current**

$V_{CC} = 3.0V \sim 3.6V$ ,  $Ta = -10 \,^{\circ}C \sim +70 \,^{\circ}C$

| Symbol            | Parameter                             | Conditi                                          | on(*)                               | Тур. | Max.     | Units |

|-------------------|---------------------------------------|--------------------------------------------------|-------------------------------------|------|----------|-------|

| In and            | Receiver Supply                       | VESA SXGA (60Hz),<br>f <sub>CLKOUT</sub> = 54MHz | MODE<1:0>=LH<br>CL=8pF,<br>Vcc=3.3V | 57   | 66       | mA    |

| I <sub>RCCG</sub> | Current (256 Gray Scale Pattern)      | VESA UXGA (60Hz),<br>f <sub>CLKOUT</sub> = 81MHz | MODE<1:0>=LL<br>CL=8pF,<br>Vcc=3.3V | 85   | 97       | mA    |

| Lagari            | Receiver Supply Current               | VESA SXGA (60Hz),<br>f <sub>CLKOUT</sub> = 54MHz | MODE<1:0>=LH<br>CL=8pF,<br>Vcc=3.3V | 87   | 99       | mA    |

| I <sub>RCCW</sub> | (Double Checker Pattern)              | VESA UXGA (60Hz),<br>f <sub>CLKOUT</sub> = 81MHz | MODE<1:0>=LL<br>CL=8pF,<br>Vcc=3.3V | 148  | 66<br>97 | mA    |

| I <sub>RCCS</sub> | Receiver Power Down<br>Supply Current | /PDWN = L                                        |                                     |      | 10       | μΑ    |

<sup>(\*)</sup> VESA is a trademark of the Video Electronics Standards Association.

#### 256 Gray Scale Pattern

#### **Double Checker Pattern**

# **Switching Characteristics**

$V_{CC} = 3.0V \sim 3.6V$ ,  $Ta = -10 \,^{\circ}C \sim +70 \,^{\circ}C$

| Symbol             | Par                    | ameter                                                        | Min.                         | Тур.                  | Max.                         | Units |

|--------------------|------------------------|---------------------------------------------------------------|------------------------------|-----------------------|------------------------------|-------|

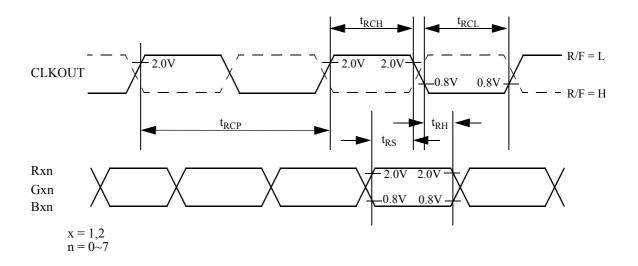

| t                  | CL VOLIT Davied        | Dual-in / Dual-out                                            | 11.76                        | t <sub>RCIP</sub>     | 40.0                         | ns    |

| t <sub>RCP</sub>   | CLKOUT Period          | Single-in / Dual-out                                          | 14.8                         | 2t <sub>RCIP</sub>    | 80.0                         | ns    |

| t <sub>RCH</sub>   | CLKOUT High Ti         | me                                                            |                              | $\frac{t_{RCP}}{2}$   |                              | ns    |

| t <sub>RCL</sub>   | CKLOUT Low Tir         | me                                                            |                              | $\frac{t_{RCP}}{2}$   |                              | ns    |

| t <sub>RS</sub>    | TTL Data Setup to      | CLKOUT                                                        | $0.3t_{RCP}$                 |                       |                              | ns    |

| t <sub>RH</sub>    | TTL Data Hold fro      | om CKLOUT                                                     | $0.3t_{RCP}$                 |                       |                              | ns    |

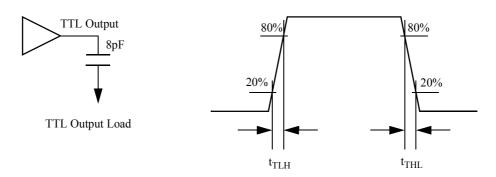

| t <sub>TLH</sub>   | TTL Low to High        | Transition Time                                               |                              | 3.0                   | 5.0                          | ns    |

| $t_{\mathrm{THL}}$ | TTL High to Low        | Transition Time                                               |                              | 3.0                   | 5.0                          | ns    |

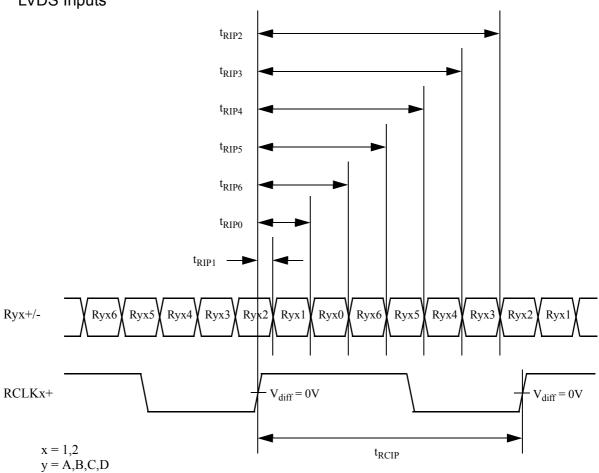

| t <sub>RIP1</sub>  | Input Data Position    | $n0 (t_{RCIP} = 7.4 ns)$                                      | -0.25                        | 0.0                   | +0.25                        | ns    |

| t <sub>RIP0</sub>  | Input Data Position    | $11 (t_{RCIP} = 7.4 ns)$                                      | $\frac{t_{RCIP}}{7} - 0.25$  | t <sub>RCIP</sub> 7   | $\frac{t_{RCIP}}{7} + 0.25$  | ns    |

| t <sub>RIP6</sub>  | Input Data Position    | $n2 (t_{RCIP} = 7.4 ns)$                                      | $2\frac{t_{RCIP}}{7} - 0.25$ | $2\frac{t_{RCIP}}{7}$ | $2\frac{t_{RCIP}}{7} + 0.25$ | ns    |

| t <sub>RIP5</sub>  | Input Data Position    | $13 (t_{RCIP} = 7.4 ns)$                                      | $3\frac{t_{RCIP}}{7} - 0.25$ | $3\frac{t_{RCIP}}{7}$ | $3\frac{t_{RCIP}}{7} + 0.25$ | ns    |

| t <sub>RIP4</sub>  | Input Data Position    | $14 (t_{RCIP} = 7.4 ns)$                                      | $4\frac{t_{RCIP}}{7} - 0.25$ | $4\frac{t_{RCIP}}{7}$ | $4\frac{t_{RCIP}}{7} + 0.25$ | ns    |

| t <sub>RIP3</sub>  | Input Data Position    | $15 (t_{RCIP} = 7.4 ns)$                                      | $5\frac{t_{RCIP}}{7} - 0.25$ | $5\frac{t_{RCIP}}{7}$ | $5\frac{t_{RCIP}}{7} + 0.25$ | ns    |

| t <sub>RIP2</sub>  | Input Data Position    | $\frac{1}{16} \left( t_{\text{RCIP}} = 7.4 \text{ns} \right)$ | $6\frac{t_{RCIP}}{7} - 0.25$ | $6\frac{t_{RCIP}}{7}$ | $6\frac{t_{RCIP}}{7} + 0.25$ | ns    |

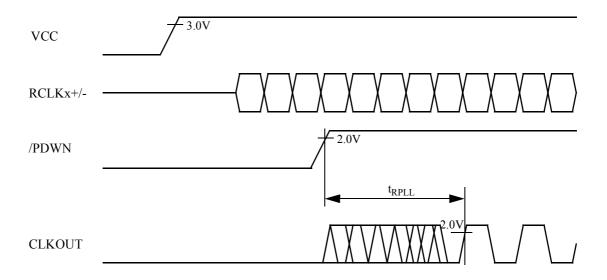

| t <sub>RPLL</sub>  | Phase Lock Loop S      | Set                                                           |                              |                       | 10.0                         | ms    |

| t <sub>RCIP</sub>  | CLKIN Period           |                                                               | 7.4                          |                       | 40.0                         | ns    |

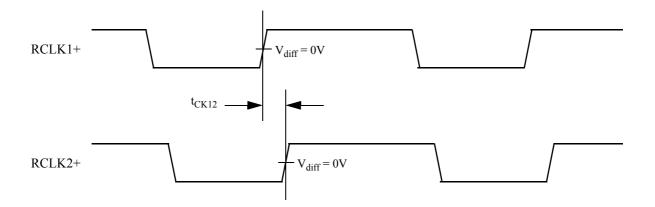

| t <sub>CK12</sub>  | Skew Time betwee RCLK2 | n RCLK1 and                                                   |                              |                       | ±0.3t <sub>RCIP</sub>        | ns    |

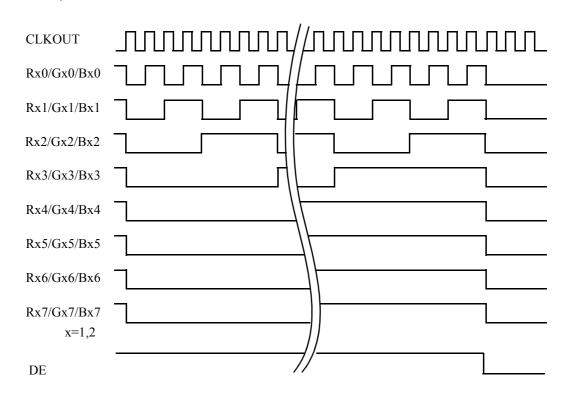

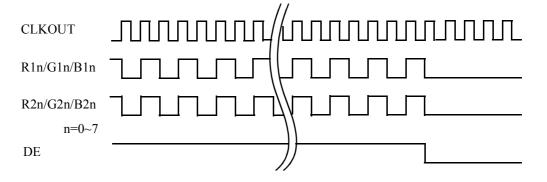

# AC Timing Diagrams TTL Outputs

# AC Timing Diagrams TTL Outputs

### Phase Lock Loop Set Time

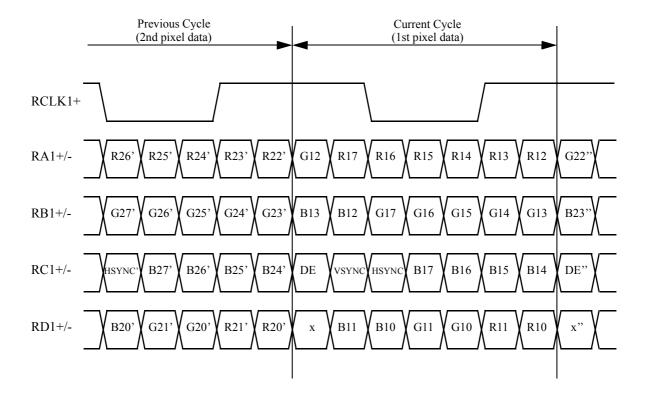

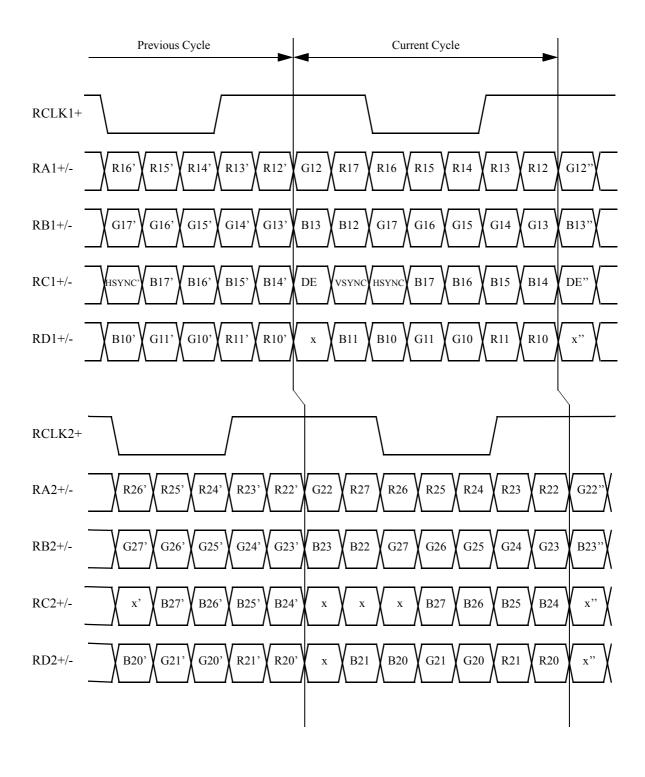

## Pixel Map Table for Single/Dual Link

| 1st Pixel Data     |     |           |       | 2nd Pixel Data      |     |         |       |

|--------------------|-----|-----------|-------|---------------------|-----|---------|-------|

| 824 TTL Output Pin | TFT | Γ Panel I | Data  | 824 TTL Output Pin  | TF  | T Panel | Data  |

| 824 TTL Output Fin |     | 24Bit     | 18Bit | 824 I IL Output Fin |     | 24Bit   | 18Bit |

| R10                | LSB | R10       | -     | R20                 | LSB | R20     | -     |

| R11                |     | R11       | -     | R21                 |     | R21     | -     |

| R12                |     | R12       | R10   | R22                 |     | R22     | R20   |

| R13                |     | R13       | R11   | R23                 |     | R23     | R21   |

| R14                |     | R14       | R12   | R24                 |     | R24     | R22   |

| R15                |     | R15       | R13   | R25                 |     | R25     | R23   |

| R16                |     | R16       | R14   | R26                 |     | R26     | R24   |

| R17                | MSB | R17       | R15   | R27                 | MSB | R27     | R25   |

| G10                | LSB | G10       | -     | G20                 | LSB | G20     | -     |

| G11                |     | G11       | -     | G21                 |     | G21     | -     |

| G12                |     | G12       | G10   | G22                 |     | G22     | G20   |

| G13                |     | G13       | G11   | G23                 |     | G23     | G21   |

| G14                |     | G14       | G12   | G24                 |     | G24     | G22   |

| G15                |     | G15       | G13   | G25                 |     | G25     | G23   |

| G16                |     | G16       | G14   | G26                 |     | G26     | G24   |

| G17                | MSB | G17       | G15   | G27                 | MSB | G27     | G25   |

| B10                | LSB | B10       |       | B20                 | LSB | B20     | -     |

| B11                |     | B11       | -     | B21                 |     | B21     | -     |

| B12                |     | B12       | B10   | B22                 |     | B22     | B20   |

| B13                |     | B13       | B11   | B23                 |     | B23     | B21   |

| B14                |     | B14       | B12   | B24                 |     | B24     | B22   |

| B15                |     | B15       | B13   | B25                 |     | B25     | B23   |

| B16                |     | B16       | B14   | B26                 |     | B26     | B24   |

| B17                | MSB | B17       | B15   | B27                 | MSB | B27     | B25   |

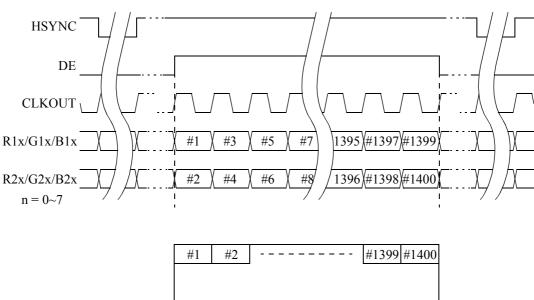

## 824 TTL Data Output Timing for Single/Dual Link

Example: SXGA+(1400 x 1050)

# AC Timing Diagrams LVDS Inputs

Note:

$$V_{diff} = (Ryx+) - (Ryx-), (RCLKx+) - (RCLKx-)$$

### LVDS Data Inputs Timing Diagrams in Single Link

### LVDS Data Inputs Timing Diagrams in Dual Link

# <u>Package</u>

UNITS:mm

#### **Notes to Users:**

- 1. The contents of this data sheet are subject to change without prior notice.

- 2. Circuit diagrams shown in this data sheet are examples of application. Therefore, please pay sufficient attention when designing circuits. Even if there are incorrect descriptions, we are not responsible for any problem due to them. Please note that incorrect descriptions sometimes cannot be corrected immediately if found.

- 3. Our copyright and know-how are included in this data sheet. Duplication of the data sheet and disclosure to other persons are strictly prohibited without our permission.

- 4. We are not responsible for any problems of industrial proprietorship occurring during THC63LVD824 use, except for those directly related to THC63LVD824's structure, manufacture or functions. THC63LVD824 is designed on the premise that it should be used for ordinary electronic devices. Therefore, it shall not be used for applications that require extremely high-reliability (space equipment, nuclear control equipment, medical equipment that affects people's lives, etc.). In addition, when using THC63LVD824 for traffic signals, safety devices and control/safety units in transportation equipment, etc., appropriate measures should be taken.

- 5. We are making the utmost effort to improve the quality and reliability of our products. However, there is a very slight possibility of failure in semiconductor devices. To avoid damage to social or official organizations, much care should be taken to provide sufficient redundancy and fail-safe design.

- 6. No radiation-hardened design is incorporated in THC63LVD824.

- 7. Judgment on whether THC63LVD824 comes under strategic products prescribed by the Foreign Exchange and Foreign Trade Control Law is the user's responsibility.

- 8. This technical document was provisionally created during development of THC63LVD824, so there is a possibility of differences between it and the product's final specifications. When designing circuits using THC63LVD824, be sure to refer to the final technical documents.

THine Electronics, Inc.

Wakamatsu Bldg, 6F 3-3-6, Nihombashi-Honcho, Chuo-ku, Tokyo, 103-0023 Japan

Tel: 81-3-3270-0666 Fax: 81-3-3270-0688