# SSC P111

## PL Media Interface IC, CEBus Compliant

### Features

- Integrates Power Amplifier, and Tri-state functions for CEBus Power Line (PL) physical interfaces

- Replaces approximately 30 discrete components to save board space and increase reliability

- Implements high-drive Output Amplifier (6 Vp-p into 10 ohm load) to increase performance under low impedance conditions

- Output Amplifier is a Class AB configuration for increased efficiency and lower power consumption

- Incorporates built-in over temperature protection circuit for improved system reliability

- Serves as companion IC to Intellon SSC P300 and SSC P200 Network Controller ICs

- 16 pin SOIC package

| VSS<br>VDD<br>VSS<br>TXO<br>VSS<br>VDD<br>TP0<br>TS | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | SSC<br>P111 | 16 NC<br>15 VSS<br>14 NC<br>13 CEXT<br>12 NC<br>11 BIAS<br>10 VDD<br>9 TXI |

|-----------------------------------------------------|--------------------------------------|-------------|----------------------------------------------------------------------------|

| TS 🗆                                                | 8                                    |             |                                                                            |

|                                                     |                                      |             |                                                                            |

#### Introduction

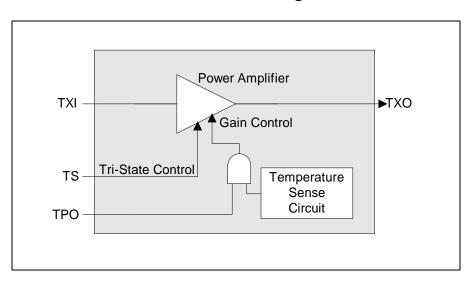

The SSC P111 PL Media Interface IC provides the functions of Output Power Amplifier and Output Tri-state Switch for power line transceiver products. The Output Power Amplifier meets the requirements specified by the EIA-600 (CEBus Standard) for output voltage levels into typical and low impedance power line loads and incorporates over-temperature protection for improved system reliability. The IC replaces approximately 30 of the discrete components normally used in support of PL transceivers and reduces required printed circuit board area by up to 50%.

## **SSC P111 Description**

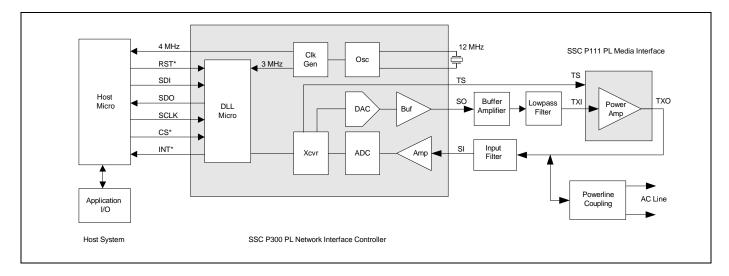

In an SSC P111 design the Signal Out (SO) from the SSC P300 or P200 is buffered and filtered before entering the P111 Power Amplifier. The output waveform is amplified by the Power Amplifier and then applied to the external Power Line Coupling/Filter network. Received power line analog signals pass through the external power line Coupling/Filter network to the Input Filter. This bandpass filter passes the chirp frequency band (100 to 400 kHz) to the SSC P300 or P200 SI input pin. The Tri-state (TS) signal from the SSC P300 or P200 disconnects the SSC P111 IC Power Amplifier from the coupling network when the system is in the receive mode and places the SSC P111 Power Amplifier in a power-down state. The Temp Sense circuitry reduces the Power Amplifier fixed gain from 2 to 1, which will lower the output transistor power dissipation under output overload conditions.

| Symbol               | Parameter                              | Min | Typical | Max   | Unit | Notes |

|----------------------|----------------------------------------|-----|---------|-------|------|-------|

| Z <sub>IN</sub> (PA) | Power Amplifier Input Resistance       | 1.4 | 2       | 2.7   | KΩ   |       |

| A <sub>V</sub> (PA)  | Power Amplifier Voltage Gain           | 1.8 | 2       | 2.2   | V/V  |       |

| V <sub>IN</sub> (PA) | Input Voltage range of Power Amplifier |     | 3       | 3.5   | Vac  |       |

| PM(PA)               | Phase Margin of Power Amplifier        |     | 78      |       | Deg  |       |

| G <sub>BW</sub> (PA) | Gain Bandwidth of Power Amplifier      | 1.1 |         | 2.1   | MHz  |       |

| VIH                  | Minimum High-level Input Voltage       | 4.0 |         |       | V    | (1)   |

| V <sub>IL</sub>      | Maximum Low-level Input Voltage        |     |         | 0.5   | V    | (1)   |

| l <sub>IL</sub>      | Maximum Input Leakage Current          |     |         | +/-10 | μA   | (1)   |

| Hys                  | Minimum Input Hysteresis               | 350 |         |       | mV   | (1)   |

| T <sub>enbl</sub>    | TS to Power Amp output signal valid    |     |         | 500   | ns   |       |

| T <sub>disabl</sub>  | TS to Power Amp output tristate        |     |         | 50    | ns   |       |

| I <sub>DD</sub> (TX) | Supply Current (Transmit)              |     | 140     | 250   | mA   | (2)   |

| I <sub>DD</sub> (RX) | Supply Current (Receive)               |     | 10      | 20    | mA   |       |

|                      | Latchup                                | 150 |         |       | mA   | (3)   |

Notes: 1) Input Signal TS 2) Typical value for driving 10 Ohm, AC coupled load 3) JEDEC JC-40.2

# Typical Application Using SSC P111 IC with SSC P300

# **Ordering Information**

| Part No. | Description                            | Tube Qty. | Package     |  |

|----------|----------------------------------------|-----------|-------------|--|

| SSC P111 | PL Media Interface IC, CEBus Compliant | 45        | 16 pin SOIC |  |