## **DY8000 Family**

### Features

- Up to 6,272 Logic Cells

- Patented Active Repeater<sup>TM</sup> Architecture

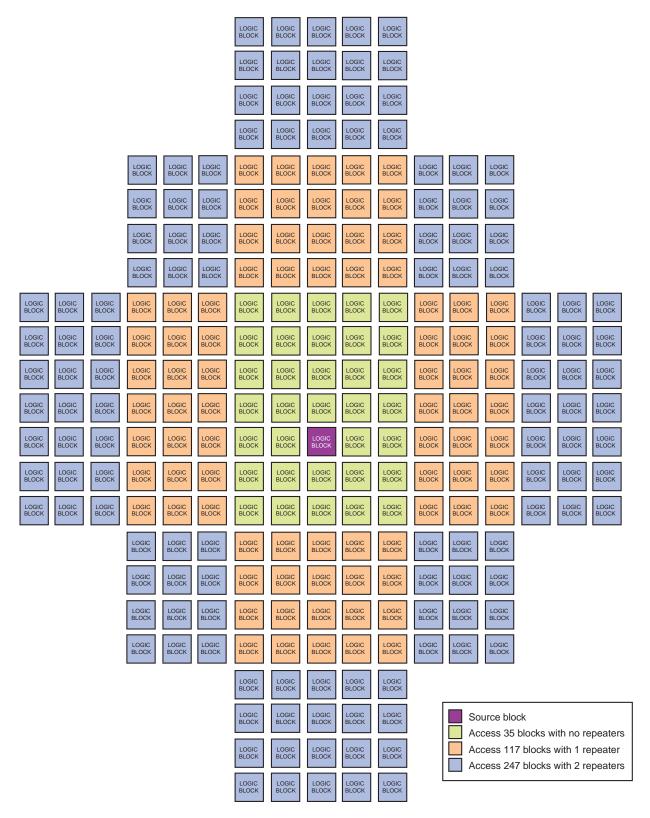

- 5 x 7 Routing Region Access 35 Logic Blocks With No Repeaters, 117 Blocks With 1 Repeater

- 4-bit Carry Routing For Wide, Fast MUX, AND/ OR, XOR, Counters and Arithmetic logic

- Supports Four 66MHz, 64-Bit, Zero-Wait-State PCI Soft Cores for PCI Bridges

- I/O Data-Transfer Rates up to 250MHz

- 21 Selectable I/O Levels Including TTL, CMOS, GTL, GTLP, AGTLP, AGP, CTT, HSTL and SSTL I/O Levels

- LVDS and LV-PECL Inputs

- Differential I/O

- Registered Output Enable in Every I/O

- 32-Bit Dual-Port SRAM in Every Logic Block With Sub-6ns Access

- Two On-Chip PLLs

- 8 to 200MHz Range

- Programmable Latency in 80ps Steps

- Clock Multiplication and Division by 2, 3, 4, 6 and 8

- Lock Indicators

- External Feedback for System-Level Clock Generation

- Ten Low-Skew Clock Trees

- SRAM-Based In-System Reprogrammable

- Dynamic Single-Block Reconfigurability

- 2.5 V Core with Multiple-Voltage Selectable I/O (5V-Tolerant)

- Hot-Swappable

- JTAG Programming and Boundary-Scan (IEEE1149.1)

### **Applications Examples**

- Gigabit Ethernet

- ATM

- Fibre Channel

- Frame Relay

- SONET

- High-Speed Image Processing

- Servers and Supercomputers

- PCI Bridges

- Semiconductor Testers

- ASIC Emulation

- On-the-Fly-Reconfigurable Systems

| Device | Logic<br>Cells | Gates   | Logic<br>Blocks | Max Dual-Port<br>SRAM Bits | Flip- flops | I/O Blocks |

|--------|----------------|---------|-----------------|----------------------------|-------------|------------|

| DY8105 | 6,272          | 105,000 | 3,136           | 100,352                    | 7,168       | 404        |

| DY8080 | 4,608          | 80,000  | 2,304           | 73,728                     | 5,376       | 362        |

| DY8055 | 3,200          | 55,000  | 1,600           | 51,200                     | 3,840       | 320        |

| DY8035 | 2,048          | 35,000  | 1,024           | 32,768                     | 2,560       | 256        |

| DY8020 | 1,152          | 20,000  | 576             | 18,432                     | 1,536       | 192        |

Table 1: DY8000 Family

## **Table of Contents**

| Features                                             | 1  |

|------------------------------------------------------|----|

| Applications Examples                                | 1  |

| DY8000 Enhancements                                  | 3  |

| High-Performance Active Repeater Technology          | 4  |

| Top-Level Architecture                               |    |

| Routing Architecture                                 |    |

| Input/Output Blocks                                  |    |

| External Reference Voltage                           |    |

| Mixing Different I/O Levels                          |    |

| Logic Blocks                                         |    |

| SRAM                                                 |    |

| Clock Distribution                                   |    |

| Phase-Locked Loops                                   |    |

| JTAG                                                 |    |

| Product Specifications                               |    |

| Maximum Ratings                                      |    |

| Recommended Operating Conditions                     |    |

| Clock and Set/Reset Buffer Switching Characteristics |    |

| I/O Block Switching Characteristics                  |    |

| Logic Block Switching Characteristics                |    |

| Pin Description                                      |    |

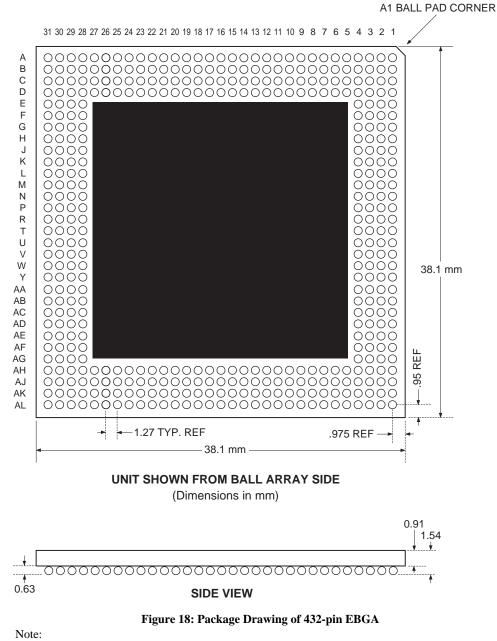

| 432-Pin EBGA                                         |    |

| 432-Pin EBGA - Internal VCC and Ground Connections   |    |

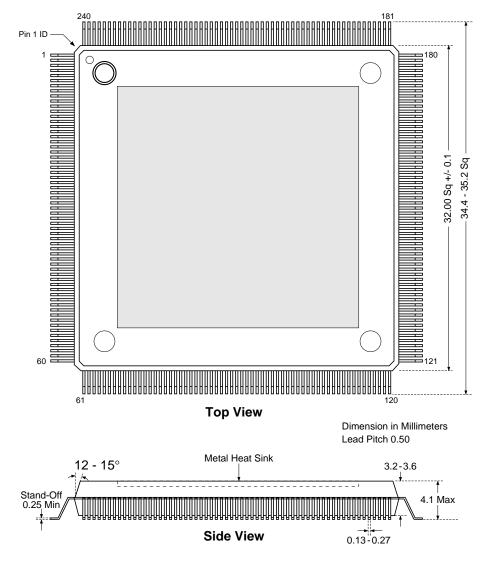

| 240-Pin EQFP                                         |    |

| Package Drawings                                     |    |

| 432-Pin EBGA                                         |    |

| 240-Pin Thermal Enhanced EQFP                        |    |

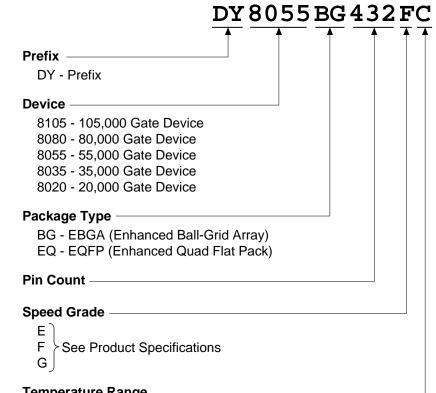

| Ordering Information                                 | 43 |

# DY8000 Enhancements

The DY8000 family incorporates numerous improvements:

- Higher Density

- Up to 6,272 Logic Cells, 105,000 Usable Gates

- Higher Speed

- Faster Process (.25 micron)

- Larger Routing Region

- 5 columns by 7 rows

- 4-bit Carry Routing

- Wide, Fast MUX, AND/OR, XOR, Counter and Arithmetic Logic

- Sub 6ns SRAM Access Time

- Supports 4, 64-bit, 66MHz PCI Soft Cores for Bridge Applications

- 21 Programmable I/O Levels

- LV-TTL

- LV-CMOS

- LV-CMOS2 (2.5 volt)

- LV-CMOS1 (1.5 volt)

- GTL

- GTL2 (2.5 volt)

- GLTP

- GTLP2 (2.5 volt)

- AGTLP

- SSTL Class 2 Level 1

- SSTL Class 2 Level 2

- SSTL Class 3 Level 1

- SSTL Class 3 Level 2

- HSTL Class I

- HSTL Class III

- HSTL Class IV

- AGP

- CTT

- LV-PECL Inputs Only

- LV-PECL2 (2.5 volt) Inputs Only

- LVDS Inputs Only

- Differential I/O Capability on Adjacent I/O

- 4 Global External I/O References

- 2 Internal I/O References

- LV-PECL and GTL

- Additional Flip Flop in Every I/O for Registered OE

- Selectable Global and Local OE Routing

- JTAG Programming

# High-Performance Active Repeater Technology

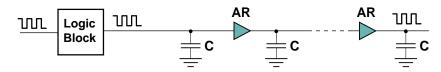

Active Repeater Routing, illustrated in Figure 2, is the enabling technology behind DynaChip's patented Fast Field Programmable Gate Arrays.

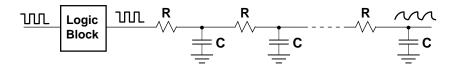

Conventional FPGA devices use pass gates to create programmable interconnections. When using multiple pass gates to create a net, they act like series resistors with distributed capacitance to ground, as shown in Figure 1. Nets formed as a series of these pass gates slow down dramatically as the number of programmable connections increases, resulting in long, unpredictable delays, especially for those nets which must traverse a long physical distance or drive a large number of loads.

In contrast, DynaChip DY8000-family devices use Active Repeaters to create programmable interconnections. As shown in Figure 2, these repeaters buffer the signal at every interconnection point and isolate the capacitance of the rest of the net.

The result is fast, predictable performance even for long, high-fanout nets.

Figure 1: Pass Gates in Series Delay and Degrade Signals

Figure 2: DynaChip's Active Repeaters Build Fast, Predictable Interconnect

Figure 3 illustrates a comparison of net delays between the two circuit technologies as the number of programmable interconnection points grows.

In FPGA devices using pass gate-based interconnect, net delays increase quadratically with the number of interconnection points, resulting in performance bottlenecks for long and/or heavily-loaded nets.

Conversely, using Active Repeater interconnect produces net delays which increase only linearly with the number of interconnection points, and are not affected by increased fanout, resulting in higher performance and superior predictability.

Figure 3: Active Repeater<sup>TM</sup> vs. Pass Gate Delays

### **Top-Level Architecture**

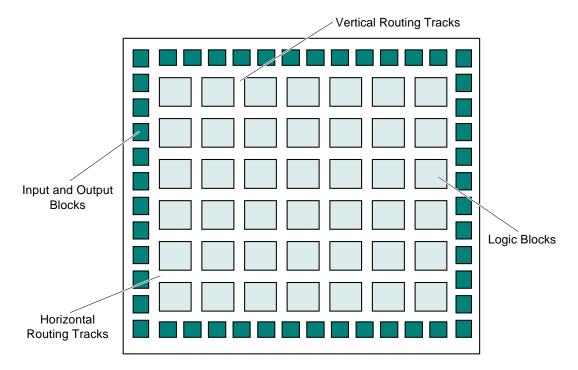

Figure 4 illustrates the architecture common to all DY8000 family devices, but for a reduced number of blocks. A border of I/O blocks forms the outer perimeter of the device. A rectangular array of logic blocks occupies the device's interior. The spaces between these logic blocks form channels, which are filled by horizontal and vertical routing tracks.

The structure of the individual DY8000 routing tracks is entirely different from the corresponding structures in conventional FPGAs. The illustrations in Figure 1, Figure 2, and Figure 3 emphasize the effect of these differences. Using Active Repeaters eliminates the need for numerous levels of routing tracks of varying lengths, resulting in more predictable convergence to optimized solutions.

Figure 4: Overview of DY8000 Architecture

### **Routing Architecture**

Dynachip's Active Repeater technology provides higher performance than more complex multi-level routing architectures.

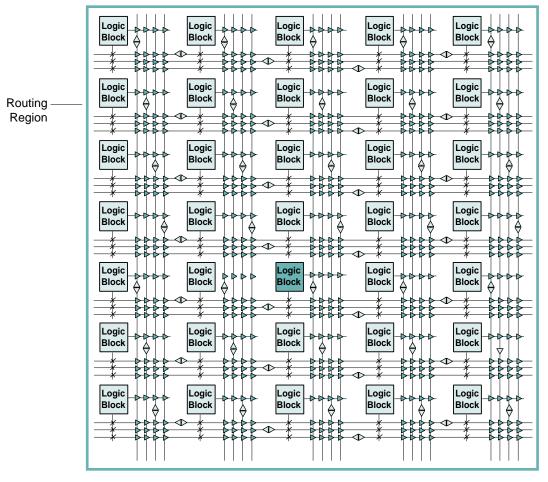

As shown in Figure 5, a routing region consists of logic blocks and a set of horizontal and vertical routing tracks, interconnected by buffers controlled by programmable configuration SRAM bits. All routing is programmed by selecting which of these buffers to turn on; there are no pass gates or other passive routing types.

Active Repeater buffers drive fixed loads and are optimized for those loads. As a result, their logic delays are fixed and the performance of large complex user designs is determinate and predictable. There are four types of Active Repeater buffers:

- Horizontal (Horizontal-to-Horizontal Bidirectional Buffers)

- Vertical (Vertical-to-Vertical Bidirectional Buffers)

- Vertical-to-Horizontal Connection Buffers

- Horizontal-to-Vertical Connection Buffers

As shown in Figure 5, each DY8000 logic block has its own 35-block local routing region; 5 columns wide by 7 rows high. The Active Repeaters are staggered so that every block has an associated routing region, which overlaps the routing regions of nearby blocks.

Routing regions are connected via bidirectional Active Repeater buffers. A signal which has passed through an Active Repeater is available throughout the next routing region.

- Active Repeater

- Connection Buffer

- $\times$  Input Connection

#### **Figure 5: Routing Architecture**

The 5 x 7 routing regions allow a logic block to drive up to 35 blocks with zero repeaters and no additional routing delays. As shown in Figure 6, adding a single repeater delay allows a logic block to drive up to 117 blocks with a routing delay of only 500ps. With 2 repeater delays a logic block can drive 247 blocks. Since every interconnect is fully buffered, repeater delays are additive and the resulting 2 repeater net has a delay of only 1.0ns. This enables even high fanout nets to have extremely high performance.

The DY8000 AC parameters presented in Table 19 allow designers to accurately estimate performance because they include all connection buffer delays and other routing delays within the logic block's 5x7 routing region. The DY8000 parameters presented in Table 20 show logic block delays without any connection buffer or routing delays and are useful for comparing the DY8000 to other FPGA technologies.

Figure 6: Routing Region With No Interconnect Delay

For a signal driving a block or blocks within the next region, the fixed delay through one Active Repeater is added to the logic block delay. Thereafter, an additional Active Repeater delay is added for every 3 columns or 4 rows the signal traverses.

Active Repeater delays are the only routing delays in a DY8000 device. Active Repeaters performance values are given in Table 23 at the end of this data sheet.

Each logic block typically implements twenty logic gates or thirty-two SRAM bits. The total logic and memory resources which may be reached with 0, 1, or 2 Active Repeater delays are shown in Table 2.

| Active Repeater<br>Delays | Logic Blocks | Gates | SRAM Bits |

|---------------------------|--------------|-------|-----------|

| 0                         | 35           | 700   | 1,120     |

| 1                         | 117          | 2,340 | 3,744     |

| 2                         | 247          | 4,940 | 8,151     |

Table 2: Accessing Neighboring Logic Blocks

### **Input/Output Blocks**

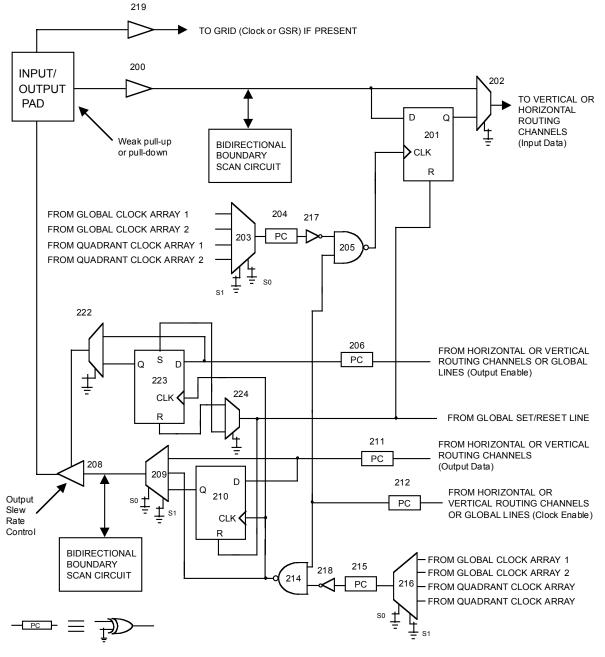

DY8000 I/O block structure is illustrated in Figure 7. Each I/O block includes an input flipflop, an output flip-flop and an OE flip-flop. Each I/O block includes JTAG Boundary Scan logic, conformant to the IEEE 1149.1 Specification.

Figure 7: Input/Output Block

The numbers within the logic symbols are used by DynaTool to identify particular logic elements.

Every I/O can be programmed to any of the following levels.

- AGP

- AGTLP

- CTT

- GTL

- GTL2 (2.5 volt)

- GLTP

- GTLP2 (2.5 volt)

- HSTL Class I

- HSTL Class III

- HSTL Class IV

- LV-CMOS

- LV-CMOS1 (1.5 volt)

- LV-CMOS2 (2.5 volt)

- LVDS (inputs only)

- LV-PECL (inputs only)

- LV-PECL2 (2.5 volt) inputs only

- LV-TTL

- SSTL Class 2 Level 1

- SSTL Class 2 Level 2

- SSTL Class 3 Level 1

- SSTL Class 3 Level 2

When programmed to LVDS, LV-PECL or LV-PECL2 levels, the I/O can be used only as inputs.

Adjacent I/O can be configured as a differential pair. Differential signaling can be used with any of the supported I/O levels.

### **External Reference Voltage**

The DY8000 I/O blocks can use external reference voltages. Up to 4 external reference voltages can be applied. Any I/O block may be programmed to use any of the four externally-supplied reference voltages. Recommended reference voltages for supported I/O levels are shown in Table 3.

| Required Compatibility | Reference Voltage             |

|------------------------|-------------------------------|

| GTL                    | 0.8V ± 5%                     |

| GTLP                   | 1.0V ± 5%                     |

| LV-PECL, LV-PECL2      | (V <sub>CC</sub> - 1.3V) ± 5% |

| AGP                    | 1.30                          |

| СТТ                    | 1.50                          |

| HSTL I                 | .75                           |

| HSTL III               | .90                           |

| HSTL IV, AGTLP         | .90                           |

| SSTL3 I                | 1.50                          |

| SSTL3 II               | 1.50                          |

| SSTL2 I                | 1.25                          |

| SSTL2 II               | 1.25                          |

Table 3: Recommended Settings for Reference-Voltage Input

Using an external reference voltage is mandatory for GTLP, AGTLP, HSTL, SSTL, CTT, LV-PECL2, LV-CMOS2 and AGP, and optional for GTL and LV-PECL. If the external reference voltage is not used for GTL and LV-PECL, internal voltage reference is provided. LV-TTL and LV-CMOS always use an internal reference.

### **Mixing Different I/O Levels**

Input reference voltages are selectable on a pin-by-pin basis allowing the user to mix input levels with no limitations.

Output level selectability is determined by  $V_{\rm CCO}$  settings which are applied on an I/O group basis. A group consists of all the I/O contained within a half side of the device. Up to 8 different groups are available. The following table shows input and output levels that can be mixed within a group and the required  $V_{\rm CCO}$  setting.

| V <sub>CCO</sub> Setting | 3.3V                 | 2.5V                 | 1.5V               |

|--------------------------|----------------------|----------------------|--------------------|

| Supported Output Levels  | AGP                  | GTL                  | AGTLP              |

|                          | GTL                  | GTL2                 | GTL                |

|                          | GTLP                 | GTLP                 | GTL2               |

|                          | LV-TTL               | GTLP2                | GTLP               |

|                          | LV-CMOS              | LV-CMOS2             | GTLP2              |

|                          | CTT                  | SSTL Class 2 Level 1 | HSTL Class 1       |

|                          | SSTL Class 3 Level 1 | SSTL Class 2 Level 2 | HSTL Class III     |

|                          | SSTL Class 3 Level 2 |                      | HSTL Class IV      |

|                          |                      |                      | LV-CMOS1           |

| Supported Input Levels   | AGP                  | AGP                  | AGP                |

|                          | AGTLP                | AGTLP                | AGTLP              |

|                          | CTT                  | CTT                  | CTT                |

|                          | GTL                  | GTL                  | GTL                |

|                          | GTL2                 | GTL2                 | GTL2               |

|                          | GTLP                 | GTLP                 | GTLP               |

|                          | GTLP2                | GTLP2                | GTLP2              |

|                          | HSTL Class 1         | HSTL Class 1         | HSTL Class 1       |

|                          | HSTL Class III       | HSTL Class III       | HSTL Class III     |

|                          | HSTL Class IV        | HSTL Class IV        | HSTL Class IV      |

|                          | LV-CMOS              | LV-CMOS              | LV-CMOS            |

|                          | LV-CMOS1             | LV-CMOS1             | LV-CMOS1           |

|                          | LV-CMOS2             | LV-CMOS2             | LV-CMOS2           |

|                          | LV-TTL               | LV-TTL               | LV-TTL             |

|                          | LV-PECL              | LV-PECL              | LV-PECL            |

|                          | LV-PECL2             | LV-PECL2             | LV-PECL2           |

|                          | LVDS                 | LVDS                 | LVDS               |

|                          | SSTL Class 2 Level 1 |                      | SSTL Class 2 Level |

|                          | SSTL Class 2 Level 2 |                      |                    |

|                          | SSTL Class 3 Level 1 | SSTL Class 3 Level 1 | SSTL Class 3 Level |

|                          | SSTL Class 3 Level 2 | SSTL Class 3 Level 2 | SSTL Class 3 Level |

Table 4: I/O Levels for V<sub>CCO</sub> Settings

### Logic Blocks

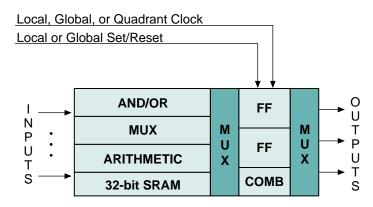

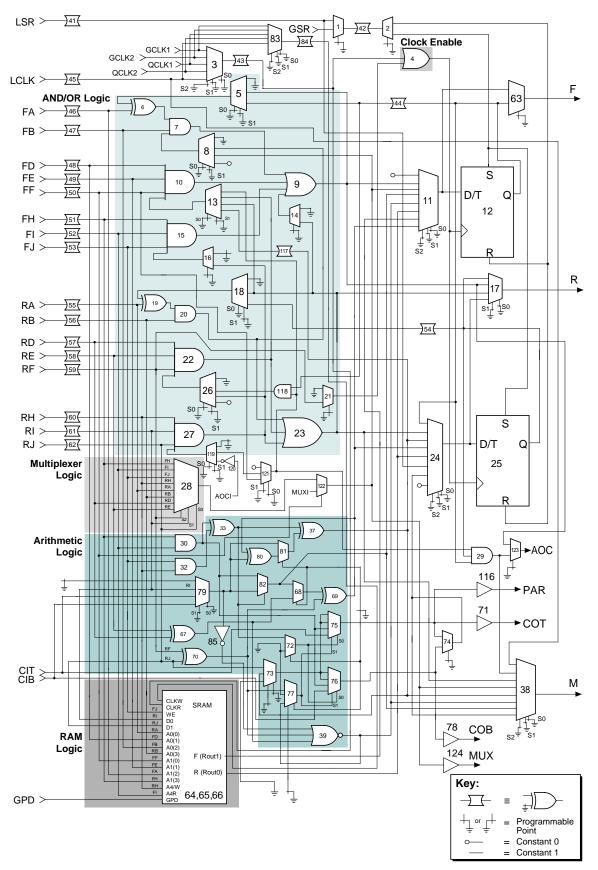

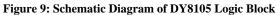

The DY8000 Logic Block, simplified in Figure 8, and shown fully in Figure 9, contains AND, OR, and XOR gates, flip-flops, muxes, and a 32-bit, two-clock, two-port SRAM, making this block versatile and powerful. DynaTool<sup>TM</sup> (DynaChip's development system) automatically maps logic from the designer's application into these logic block resources.

One logic block may implement a two-bit full adder or identity comparator, a nine-input AND gate, a seven-input XOR parity tree, an 8:1 multiplexer, and other logic functions of comparable complexity.

The logic block includes sixteen general purpose logic inputs, plus Clock and Set/Reset inputs. All inputs are equipped with polarity control circuits, which may be programmed to pass their signals either as noninverted (true) or as inverted (false). There are also two Global Clock Inputs, two Quadrant Clock Inputs, a Global Set/Reset Input, and 4 carry signals.

There are three logic outputs that may be driven by the logic blocks' combinatorial logic, its flip-flops, or its SRAM. Two of the logic outputs can be direct or registered. The third output is always direct.

Figure 8: Conceptual Diagram of Logic Block

The functional areas shown in Figure 8 are the AND/OR logic section, multiplexer section, arithmetic logic section, and the thirty two-bit, two-clock, two-port SRAM section.

Each block includes two flip-flops that are configurable to either a D-type or T-type element. Both flip-flops are clocked from one of five sources (local clock (LCLK)), two global clocks (GCLK1 or GCLK2), or two quadrant clocks (QCLK1 or QCLK2), which serve this region. Flip-flops can be programmed to be active on either the rising or the falling clock edge.

The two flip-flops share a common set/reset signal from either of two sources: local interconnect (LSR), or the FPGA's global set/reset (GSR). The set/reset input has programmable polarity control. You may choose assertive-HIGH operation or assertive-LOW operation for resetting the two flip-flops, although your choice must be the same for both. Likewise, you may configure the two flip-flops together to use either a set operation or a reset operation.

### SRAM

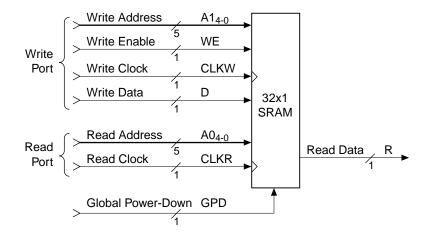

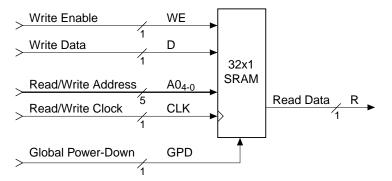

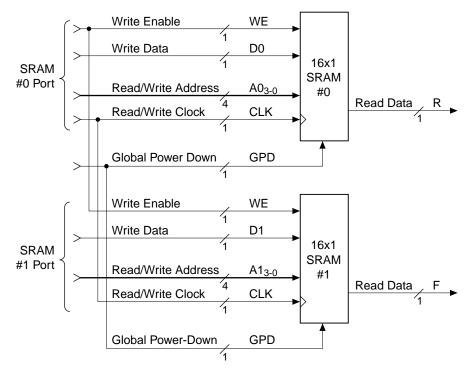

Each logic block in a DY8000-family FPGA includes 32 bits of fully-synchronous dual-port, two-clock SRAM with three configuration options:

- One 32x1 two-port SRAM.

- One 32x1 single-port SRAM.

- Two separate 16x1 single-port SRAMs.

Functional block diagrams corresponding to each of these configurations are shown in Figure 10, Figure 11, and Figure 12. All signals are one-bit except for addresses, which are five-bit for the two 32x1 configurations, and four-bit for the double-16x1 configuration.

The SRAM has separate read and write clocks. Either of these clocks may originate from any of five sources: local interconnect (LCLK), either of the FPGA's two global clocks (GCLK1 or GCLK2), or either of the FPGA's two quadrant clocks (QCLK1 or QCLK2) serving that region of the chip. For the two single-port configurations, the write clock and the read clock are automatically tied together.

For any of the three SRAM configurations, both writing and reading are synchronous operations.

Figure 10: 32x1 Two-Port SRAM

Figure 11: 32x1 Single-Port SRAM

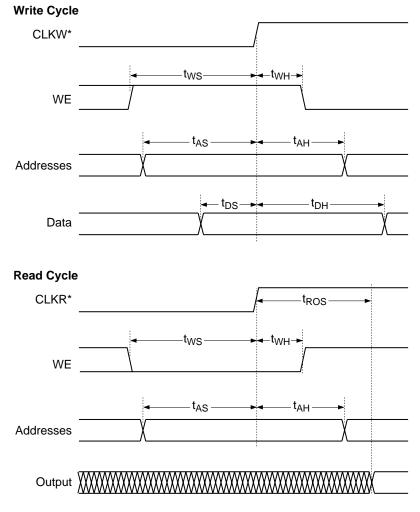

On a rising edge (a LOW-to-HIGH transition) of the write clock, the WE, address, and data inputs are latched. If WE is HIGH, the data is written to the RAM in the same clock cycle. Writing is a single-clock operation. While a write operation is in progress, the state of the SRAM's data output(s) is indeterminate.

Figure 12: Two Separate 16x1 Single-Port SRAMs

On a rising edge of the read clock, the RAM outputs are latched and are available at the RAM output(s). Reading is a single-clock operation.

The two-port SRAM configuration has a separate write port and read port, with separate read address and clock signals. Single-port configurations have common read/write clocks and addresses.

For two single-port configurations, SRAM is in write mode whenever WE is asserted and in read mode whenever WE is not asserted.

For two-port configurations, the SRAM is always in read mode regardless of the state of WE, except when a read-write collision occurs; that is, when an attempt is made to read and write the same location at the same time. In this case, writing takes precedence over reading, and the data output is indeterminate.

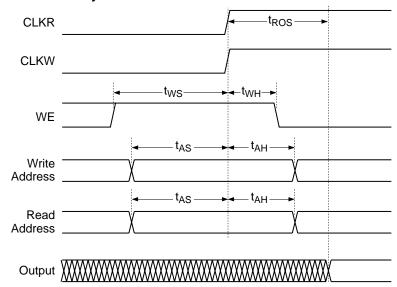

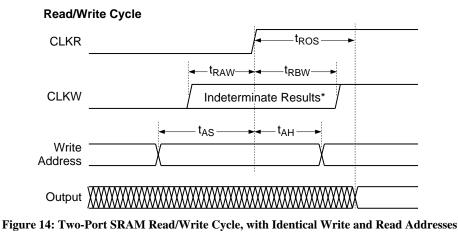

Timing waveforms for the SRAM write and read operations are shown in Figure 13, Figure 14, and Figure 15. Figure 13 and Figure 14 apply to the 32x1 two-port configuration. Figure 13 is for the common case where the write and read addresses are not the same, and Figure 14 applies to the 'read-write collision' case where the addresses are the same. Figure 15 applies to both the 32x1 single-port configuration and the two-16x1 single-port configuration.

#### **Read/Write Cycle**

Figure 13: Two-Port SRAM Read/Write Cycle, with Differing Write and Read Addresses

\* If the rising edge of CLKW occurs in this region, the output is indeterminate.

Figure 15: Read/Write Cycle Timing for Single-Port SRAM Configurations

\* For single-port operation, CLKW and CLKR are automatically tied together.

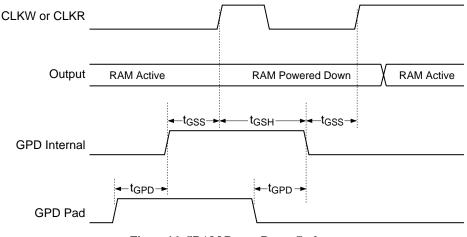

The SRAM may be powered down by using the Global Power-Down (GPD) signal. This signal must meet setup-time and hold-time conditions with respect to a clock (write or read), if the entry or exit from powered-down mode is to be effective as of that clock. In powered-down mode, the SRAM bits retain their previously stored information, but cannot be written into or read from as long as the powered-down mode remains in effect, as illustrated in Figure 16.

Figure 16: SRAM Power-Down Cycle

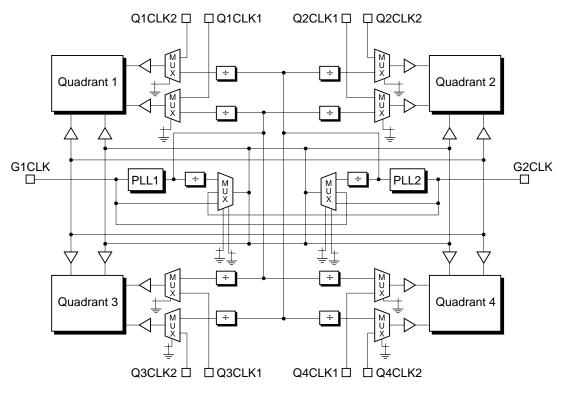

### **Clock Distribution**

DY8000-family FPGAs have ten low-skew clock distribution networks. Two of these are global networks which access the entire device; the other eight are quadrant networks which access one quarter of the device. Each of the ten clock networks can be driven from a package pin, from the PLLs, or from signals generated within the FPGA. A signal on any of the ten clock networks can be driven off-chip through package pins.

Every logic block can use any of five clock signals:

- either of the two global clocks

- either of the two quadrant clocks in the quadrant

- local interconnect clock (LCLK) generated by the user's logic

Every I/O block can use any of four clock signals:

- either of the two global clocks

- either of the two quadrant clocks in the quadrant.

#### **Phase-Locked Loops**

DY8000 devices contain two PLLs for clock latency reduction, clock multiplication, and clock division. The PLLs support a clock frequency of 8MHz to 200MHz. Each of the two PLLs drive one global clock network and four quadrant-clock networks. The PLLs multiply and divide clock signals by 1, 2, 3, 4, 6, or 8. Table 5 shows the supported input frequency range for different multiplication factors. By default, the PLL reduces clock latency to zero. The latency may be programmed in 80ps increments over the range of -2ns to +2ns.

A filter is required for the PLL power supply. Refer to DynaChip's PLL application note for more information on the filter requirements. External resistors can be connected to device pins PLL1\_RES and PLL2\_RES for signal optimization.

PLL1 can drive GCLK1, QCLK1TL, QCLK1TR, QCLK1BL, and QCLK1BR. PLL2 can drive GCLK2, QCLK2TL, QCLK2TR, QCLK2BL, and QCLK2BR.

| Multiplier | Minimum Input<br>Frequency | Maximum Input<br>Frequency |

|------------|----------------------------|----------------------------|

| 1          | 12.5                       | 200                        |

| 2          | 24                         | 80                         |

| 3          | 19                         | 52                         |

| 4          | 14                         | 40                         |

| 6          | 10                         | 26                         |

| 8          | 8                          | 20                         |

Table 5: PLLs' Supported Input Frequency Ranges

Figure 17 shows, in simplified form, the clock networks for the entire chip.

Figure 17: PLL and Clock Networks

Note:

All MUXs have another input which comes from the "derived clock" output of the logic blocks that drive the 10 clock trees.

If the jitter of the incoming clock is 100ps or less, then the jitter of the clock signal produced by the PLL is less than 350ps over commercial voltage and temperature range, or 450ps over industrial voltage and temperature range.

A programmable external feedback option and lock signals are provided for each PLL so they can be used to generate system-level clocks.

# JTAG

All devices in the DY8000 family provide JTAG (Joint Test Action Group) Boundary Scan, conformant to the IEEE1149.1 specification. This feature simplifies the testing of boards incorporating devices in surface-mount packages, or in packages with closely-spaced pins.

Four JTAG instructions are supported, as shown in Table 6.

| JTAG Instruction | Register | Opcode |

|------------------|----------|--------|

| SAMPL/PRE        | BSC      | 1000   |

| EXTEST           | BSC      | 0000   |

| BYPASS           | BYPASS   | 1111   |

| IDCODE           | ID       | 1101   |

**Table 6: JTAG Instructions**

The JTAG ID register is read when the DY8000 device is reset, and when the 1101 opcode is loaded. Upon power-up, the opcode defaults to 1101. Internal pullup resistors are provided on the TDI and TMS pins.

# **Product Specifications**

### **Maximum Ratings**

| Symbol                             | Description                                               | Value                         | Unit     |

|------------------------------------|-----------------------------------------------------------|-------------------------------|----------|

| V <sub>CC_INT</sub>                | $V_{CC}$ Pin Potential to GND Lead for $V_{CC\_INT}$ Pins | -0.5 to +3.0                  | V        |

| V <sub>CC_PLL</sub>                | $V_{CC}$ Pin Potential to GND Lead for $V_{CC\_PLL}$ Pins | -0.5 to +3.0                  | V        |

| V <sub>CCO</sub>                   | $V_{CC}$ Pin Potential to GND Lead for $V_{CC\_O}$ Pins   | -0.5 to +4.0                  | V        |

| V <sub>CCI</sub>                   | $V_{CC}$ Pin Potential to GND Lead for $V_{CC\_I}$ Pins   | -0.5 to +4.0                  | V        |

| V <sub>IN5V</sub> <sup>(4)</sup>   | Input Voltage (5V Tolerant Mode)                          | -0.5 to +5.5                  | V        |

| V <sub>IN3V</sub> <sup>(4)</sup>   | Input Voltage (3V Tolerant Mode)                          | -0.5 to +3.6                  | V        |

| V <sub>IN2.5V</sub> <sup>(4)</sup> | Input Voltage (2.5V Tolerant Mode)                        | -0.5 to +3.0                  | V        |

| V <sub>TS</sub>                    | Voltage Applied to 3-State Output<br>Normal Pins          | -0.5 to V <sub>CC</sub> + 0.5 | V        |

| T <sub>VCC</sub>                   | Supply Voltage Rise Time, 1V to 3V                        | 500                           | ms       |

| T <sub>STORE</sub>                 | Storage Temperature (Ambient)                             | -65 to +150                   | °C       |

| TJ                                 | Junction Temperature<br>Ceramic<br>Plastic                | +150<br>+125                  | °C<br>°C |

| T <sub>SOL</sub> <sup>(3)</sup>    | Soldering Temperature                                     | +260                          | °C       |

Table 7: Absolute Maximum Rating

Notes:

- Permanent damage to the device may occur if the Absolute Maximum ratings are exceeded. These are stress ratings only. Functional operation of the device at these or any other conditions, other than those listed under the Recommended Operating Conditions, is not implied.

- (2) Exposure to Absolute Maximum Ratings conditions for extended periods of time may degrade device reliability.

- (3) T<sub>SOL</sub> should occur for no more than 10 seconds. (EBGA package only.)

- (4) On power-up, all I/O are 5V tolerant. After programming, I/O with 3.3V V<sub>CCO</sub> are 5V tolerant, I/O with 2.5V V<sub>CCO</sub> are 3V tolerant and I/O with 1.5V V<sub>CCO</sub> are 2.5V tolerant.

### **Recommended Operating Conditions**

| Symbol                          | Description                                                       | Min          | Max             | Unit |

|---------------------------------|-------------------------------------------------------------------|--------------|-----------------|------|

|                                 | Supply Voltage Relative to GND Lead for $V_{CC_{INT}}$ Pins:      |              |                 |      |

| V <sub>CCINT</sub>              | Commercial: 0° C to 85° C Junction                                | 2.37         | 2.63            | V    |

|                                 | Industrial: –40° C to 100° C Junction                             | 2.25         | 2.75            | V    |

|                                 | Supply Voltage Relative to GND Lead for V <sub>CC PLL</sub> Pins: |              |                 |      |

| V <sub>CCPLL</sub>              | Commercial: 0° C to 85° C Junction                                | 2.37         | 2.63            | V    |

|                                 | Industrial: –40° C to 100° C Junction                             | 2.25         | 2.75            | V    |

|                                 | Supply Voltage Relative to GND Lead for V <sub>CC_I</sub> Pins:   |              |                 |      |

| V <sub>CCI</sub> <sup>(2)</sup> | Commercial: 0° C to 85° C Junction                                | 3.14         | 3.47            | V    |

|                                 | Industrial: –40° C to 100° C Junction                             | 3.0          | 3.6             | V    |

|                                 | Supply Voltage Relative to GND Lead for V <sub>CC_0</sub> Pins:   |              |                 |      |

| V <sub>CCO</sub>                | Commercial: 0° C to 85° C Junction                                | Varies Based | on I/O Settings | V    |

|                                 | Industrial: -40° C to 100° C Junction                             | Varies Based | on I/O Settings | V    |

| T <sub>IN</sub>                 | Input Signal Rise or Fall Time                                    | -            | 250             | ns   |

#### **Table 8: Recommended Operating Conditions**

- (1) All junction temperatures above those listed as Recommended Operating Conditions are unsafe, and may destroy the device.

- (2) For reduced power consumption,  $V_{CCI}$  can be supplied at 2.5V if  $V_{CCO}$  is 2.5V or less.

| Symbol                | Parameter                                           | Min | Max  | Test Conditions                      | Units |

|-----------------------|-----------------------------------------------------|-----|------|--------------------------------------|-------|

| V <sub>IMAX5V</sub>   | Max. Voltage Applied to Input<br>(5V Tolerant Mode) | -   | 5.5  |                                      | V     |

| V <sub>IMAX3V</sub>   | Max. Voltage Applied to Input (3V Tolerant Mode)    | -   | 3.6  |                                      | V     |

| V <sub>IMAX2.5V</sub> | Max. Voltage Applied to Input (2.5V Tolerant Mode)  | -   | 3.0  |                                      | V     |

| $V_{DR}^{(3)}$        | Data-Retention Voltage                              | 2.0 | -    |                                      | V     |

| I <sub>DDQ</sub>      | Quiescent Current (9)                               | -   | 10   | V <sub>CC</sub> = Max; All I/Os Open | mA    |

| I <sub>IL</sub>       | Leakage Current                                     | -10 | +10  |                                      | μA    |

| I <sub>PU</sub>       | Pad Pullup Current (When Selected)                  | -   | -150 | $V_{IN} = 0V$<br>$V_{CCO} = 3.3V$    | μA    |

| I <sub>PD</sub>       | Pad Pulldown Current (When Selected)                | -   | -200 | V <sub>IN</sub> = 5.5V               | μA    |

| C <sub>IN</sub>       | Input Capacitance                                   | -   | 8.0  | EBGA Package                         | pF    |

### **DC Characteristics**

Table 9: DC Electrical Characteristics over Operating Conditions

Notes:

- (1) All GTL outputs should be terminated to  $V_{TT}$  through a 50  $\Omega$  resistor.

- (2) ALL GTLP outputs should be terminated to  $V_{TT}$  through a 25 $\Omega$  termination, configured as a pair of 50 $\Omega$  resistors, one at each end of the net.

- (3) Below this voltage, configuration data may be lost.

- (4) All I/O power-up is 5V tolerant.

| Input/OUtput |        | V <sub>IL</sub>         | VII                     | н                      | V <sub>OL</sub>        |                        | I <sub>OL</sub> | I <sub>ОН</sub> |

|--------------|--------|-------------------------|-------------------------|------------------------|------------------------|------------------------|-----------------|-----------------|

| Standard     | V, Min | V, Max                  | V, Min                  | V, Max                 | V, Max                 | V, Min                 | mA              | mA              |

| AGP          | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | 10% V <sub>CCO</sub>   | 90% $V_{CCO}$          | Note 1          | Note 1          |

| AGTLP        | -0.5   | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | -               | -               |

| CTT          | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.4 | V <sub>REF</sub> + 0.4 | 8               | -8              |

| GTL          | -0.5   | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> + 0.05 | 3.6                    | 0.4                    | -                      | 40              | -               |

| GTL+         | -0.5   | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.6                    | -                      | 36              | -               |

| HSTL I       | -0.5   | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 8               | -8              |

| HSTL III     | -0.5   | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 24              | -8              |

| HSTL IV      | -0.5   | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 48              | -8              |

| LVCMOS2      | -0.5   | 0.7                     | 1.7                     | 5.5                    | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | 1.5             | -0.5            |

| LVDS         | -0.5   | 0.8                     | 2.0                     | V <sub>CC</sub> + 0.5  | -                      | -                      | -               | -               |

| LVPECL       | 1.5    | 1.8                     | 2.2                     | 2.4                    | -                      | -                      | -               | -               |

| LVPECL2      | 0.7    | 1.0                     | 1.4                     | 1.6                    | -                      | -                      | -               | -               |

| LVTTL        | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.4                    | 2.4                    | 24              | -24             |

| PCI, 3.3V    | -0.5   | 44% V <sub>CCINT</sub>  | 60% V <sub>CCINT</sub>  | V <sub>CCO</sub> + 0.5 | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note 2          | Note 2          |

| PCI, 5.0V    | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.55                   | 2.4                    | Note 2          | Note 2          |

| SSTL2 I      | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.5 | V <sub>REF</sub> + 0.5 | 7.6             | -7.6            |

| SSTL2 II     | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.5 | V <sub>REF</sub> + 0.5 | 15.2            | -15.2           |

| SSTL3 I      | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.6 | V <sub>REF</sub> + 0.6 | 8               | -8              |

| SSTL3 II     | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.8 | V <sub>REF</sub> + 0.8 | 16              | -16             |

#### **Table 10: DC Input and Output Levels**

Notes:

(1) Tested to AGP specification.

(2) Tested to PCI specification.

|                                                    |                    | S                                                    |      |      |       |

|----------------------------------------------------|--------------------|------------------------------------------------------|------|------|-------|

| Description                                        | Symbol             | -E                                                   | -F   | -G   | Units |

|                                                    |                    | Max                                                  | Max  | Max  |       |

| Global Clock Delay with PLL                        | T <sub>GCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |      |      |       |

| Global Clock Delay without PLL <sup>(1, 2)</sup>   | Т <sub>GCKD</sub>  | 6.4                                                  | 5.8  | 5.2  | ns    |

| Global Clock Skew                                  | T <sub>GCKS</sub>  | 0.18                                                 | 0.18 | 0.18 | ns    |

| Quadrant Clock Delay with PLL                      | T <sub>QCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |      |      |       |

| Quadrant Clock Delay without PLL <sup>(1, 2)</sup> | T <sub>QCKD</sub>  | 4.7                                                  | 4.3  | 3.9  | ns    |

| Quadrant Clock Skew                                | T <sub>QCKS</sub>  | 0.18                                                 | 0.18 | 0.18 | ns    |

| Clock Min Pulse Width HIGH                         | T <sub>MPH</sub>   | 2.2                                                  | 2.0  | 1.8  | ns    |

| Clock Min Pulse Width LOW                          | T <sub>MPL</sub>   | 2.2                                                  | 2.0  | 1.8  | ns    |

| Global Set/Reset Delay                             | T <sub>GSR</sub>   | 9.9                                                  | 9.0  | 8.1  | ns    |

### **Clock and Set/Reset Buffer Switching Characteristics**

Table 11: Clock and Set/Reset Buffer Switching Characteristics (Input Set to TTL)

Notes:

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip-flop clock input.

- (2) Default programming of the PLL offsets actual clock delays, forcing them to 0.0ns.

- (3) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (4) Clock delays are also referred to as latency.

|                                                    |                    | 5                                                    |      |      |       |

|----------------------------------------------------|--------------------|------------------------------------------------------|------|------|-------|

| Description                                        | Symbol             | -E                                                   | -F   | -G   | Units |

|                                                    |                    | Max                                                  | Max  | Мах  |       |

| Global Clock Delay with PLL                        | T <sub>GCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |      |      |       |

| Global Clock Delay without PLL <sup>(1, 2)</sup>   | T <sub>GCKD</sub>  | 7.0                                                  | 6.4  | 5.8  | ns    |

| Global Clock Skew                                  | T <sub>GCKS</sub>  | 0.18                                                 | 0.18 | 0.18 | ns    |

| Quadrant Clock Delay with PLL                      | T <sub>QCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |      |      |       |

| Quadrant Clock Delay without PLL <sup>(1, 2)</sup> | Т <sub>QCKD</sub>  | 5.4                                                  | 4.9  | 4.4  | ns    |

| Quadrant Clock Skew                                | T <sub>QCKS</sub>  | 0.18                                                 | 0.18 | 0.18 | ns    |

| Clock Min Pulse Width HIGH                         | T <sub>MPH</sub>   | 2.2                                                  | 2.0  | 1.8  | ns    |

| Clock Min Pulse Width LOW                          | T <sub>MPL</sub>   | 2.2                                                  | 2.0  | 1.8  | ns    |

| Global Set/Reset Delay                             | T <sub>GSR</sub>   | 10.6                                                 | 9.6  | 8.6  | ns    |

Table 12: Clock and Set/Reset Buffer Switching Characteristics (Input Set to LV-PECL or LVDS)

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip-flop clock input.

- (2) Default programming of the PLL offsets actual clock delays, forcing them to 0.0ns.

- (3) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (4) Clock delays are also referred to as latency.

|                                                    |                    | 5                                                    | Speed Grade |      |       |

|----------------------------------------------------|--------------------|------------------------------------------------------|-------------|------|-------|

| Description                                        | Symbol             | -E                                                   | -F          | -G   | Units |

|                                                    |                    | Max                                                  | Max         | Max  |       |

| Global Clock Delay with PLL                        | T <sub>GCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |             |      |       |

| Global Clock Delay without PLL <sup>(1, 2)</sup>   | T <sub>GCKD</sub>  | 6.5                                                  | 5.9         | 5.3  | ns    |

| Global Clock Skew                                  | T <sub>GCKS</sub>  | 0.18                                                 | 0.18        | 0.18 | ns    |

| Quadrant Clock Delay with PLL                      | T <sub>QCKDP</sub> | Programmable from -2ns to +2ns<br>in 80ps increments |             |      |       |

| Quadrant Clock Delay without PLL <sup>(1, 2)</sup> | T <sub>QCKD</sub>  | 4.8                                                  | 4.4         | 4.0  | ns    |

| Quadrant Clock Skew                                | T <sub>QCKS</sub>  | 0.18                                                 | 0.18        | 0.18 | ns    |

| Clock Min Pulse Width HIGH                         | T <sub>MPH</sub>   | 2.2                                                  | 2.0         | 1.8  | ns    |

| Clock Min Pulse Width LOW                          | T <sub>MPL</sub>   | 2.2                                                  | 2.0         | 1.8  | ns    |

| Global Set/Reset Delay                             | T <sub>GSR</sub>   | 10.0                                                 | 9.1         | 8.2  | ns    |

#### Table 13: Clock and Set/Reset Buffer Switching Characteristics (input set to AGP, CTT, GTL, GTLP, HSTL, SSTL)

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip-flop clock input.

- (2) Default programming of the PLL offsets actual clock delays, forcing them to 0.0ns.

- (3) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (4) Clock delays are also referred to as latency.

### **I/O Block Switching Characteristics**

|                                                              |                     | Sp  |     |     |       |

|--------------------------------------------------------------|---------------------|-----|-----|-----|-------|

| Description                                                  | Symbol              | -E  | -F  | -G  | Units |

|                                                              |                     | Max | Max | Max |       |

| Input Buffer Combinatorial Delay                             | T <sub>INPD</sub>   | 2.5 | 2.3 | 2.1 | ns    |

| Input Flip-flop Setup Time (Global Clock)                    | T <sub>INIS1</sub>  | 1.7 | 1.5 | 1.4 | ns    |

| Input Flip-flop Hold Time (Global Clock)                     | T <sub>INIH1</sub>  | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop Clock to Output (Global Clock)               | T <sub>INCO1</sub>  | 1.7 | 1.5 | 1.4 | ns    |

| Output Buffer Combinatorial Delay (No Load) <sup>(2,3)</sup> | T <sub>OUTIS1</sub> | 4.0 | 3.6 | 3.2 | ns    |

| Output Flip-flop Setup Time (Global Clock)                   | T <sub>OUTIS2</sub> | 2.4 | 2.2 | 2.0 | ns    |

| Output Flip-flop Hold Time (Global Clock)                    | T <sub>OUTIH1</sub> | 0.0 | 0.0 | 0.0 | ns    |

| Output Flip-flop Clock to Output (Global Clock,              | T <sub>OUTCO1</sub> | 2.8 | 2.5 | 2.3 | ns    |

| No Load) <sup>(2,3)</sup>                                    | 001001              | 2.0 | 2.0 | 2.0 |       |

| I/O Flip-flop Clock Enable Setup Time                        | T <sub>CES1</sub>   | 2.1 | 1.9 | 1.7 | ns    |

| I/O Flip-flop Clock Enable Hold Time                         | T <sub>CEH1</sub>   | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop GSR Set/Reset Delays                         | T <sub>GSRI</sub>   | 2.5 | 2.3 | 2.1 | ns    |

| Output Flip-flop GSR Set/Reset Delays                        | T <sub>GSRO</sub>   | 3.5 | 3.2 | 2.9 | ns    |

| Input Flip-flop GSR Set/Reset Setup Time                     | T <sub>GSRIS1</sub> | 0.3 | 0.3 | 0.3 | ns    |

| Output Flip-flop GSR Set/Reset Setup Time                    | T <sub>GSROS1</sub> | 0.3 | 0.3 | 0.3 | ns    |

#### Table 14: Input and Output Buffer Parameters (I/O Set to TTL)

- (1) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading.

| Fast Slew Rate:   | 12ps/pF |

|-------------------|---------|

| Medium Slew Rate: | 25ps/pF |

| Clow Clow Data  | 55-00 |

|-----------------|-------|

| Slow Slew Rate: | 55ps/ |

|                 |       |

- Slow Slew Rate: 55ps/pF (3) The maximum loading for outputs switching at the same time in the same direction is shown below. One power/ground pin pair is provided for each eight I/O blocks on the device. Fast Slew Rate:

- 200pf between each power/ground pair 300pf between each power/ground pair

- Medium Slew Rate:

- Slow Slew Rate: 400pf between each power/ground pair

- (4) Each output pin has individual slew-rate control.

- (5) For  $V_{CCI} = 3.3V$ .

|                                             |                      | Sp  |     |     |       |

|---------------------------------------------|----------------------|-----|-----|-----|-------|

| Description                                 | Symbol               | -E  | -F  | -G  | Units |

|                                             |                      | Max | Max | Max |       |

| OE to Pad Active (No Load) <sup>(2,3)</sup> | T <sub>3SOE</sub>    | 3.2 | 2.9 | 2.6 | ns    |

| OE to Pad Hi-Z (No Load) (2,3)              | T <sub>3SOD</sub>    | 3.6 | 3.3 | 3.0 | ns    |

| OE Flip-flop Clock to Pad Active (No Load)  | T <sub>Q3SOE</sub>   | 2.1 | 1.9 | 1.7 | ns    |

| OE Flip-flop Clock to Hi-Z (No Load)        | T <sub>Q3SOD</sub>   | 2.4 | 2.2 | 2.0 | ns    |

| OE Flip-flop Setup Time                     | T <sub>OEIS</sub>    | 2.2 | 2.0 | 1.8 | ns    |

| OE Flip-flop Hold Time                      | T <sub>OEIH</sub>    | 0.0 | 0.0 | 0.0 | ns    |

| OE Flip-flop GSR Set/Reset Delay            | T <sub>OEGSRI</sub>  | 3.6 | 3.3 | 3.0 | ns    |

| OE Flip-flop GSR Setup Time                 | T <sub>OEGSRIS</sub> | 0.6 | 0.5 | 0.5 | ns    |

Table 15: Three-state Buffer Delays (I/O Set to TTL)

Notes:

- (1) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading:

- Fast Slew Rate:12ps/pFMedium Slew Rate:25ps/pF

- Slow Slew Rate: 25ps/pF

- (3) Each output pin has individual slew-rate control.

- (4) Should be measured with output held at  $V_{OL} + 0.5V$ .

- (5) For  $V_{CCI} = 3.3V$ .

|                                                                         |                     | Sp  |     |     |       |

|-------------------------------------------------------------------------|---------------------|-----|-----|-----|-------|

| Description                                                             | Symbol              | -E  | -F  | -G  | Units |

|                                                                         |                     | Max | Max | Max |       |

| Input Buffer Combinatorial Delay                                        | T <sub>INPD</sub>   | 2.6 | 2.4 | 2.2 | ns    |

| Input Flip-flop Setup Time (Global Clock)                               | T <sub>INIS1</sub>  | 1.8 | 1.6 | 1.4 | ns    |

| Input Flip-flop Hold Time (Global Clock)                                | T <sub>INIH1</sub>  | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop Clock to Output (Global Clock)                          | T <sub>INCO1</sub>  | 1.7 | 1.5 | 1.4 | ns    |

| Output Buffer Combinatorial Delay (No Load) <sup>(2)</sup>              | T <sub>OUTIS1</sub> | 3.2 | 2.9 | 2.6 | ns    |

| Output Flip-flop Setup Time (Global Clock)                              | T <sub>OUTIS2</sub> | 2.4 | 2.2 | 2.0 | ns    |

| Output Flip-flop Hold Time (Global Clock)                               | T <sub>OUTIH1</sub> | 0.0 | 0.0 | 0.0 | ns    |

| Output Flip-flop Clock to Output (Global Clock, No Load) <sup>(2)</sup> | T <sub>OUTCO1</sub> | 1.8 | 1.6 | 1.4 | ns    |

| I/O Flip-flop Clock Enable Setup Time                                   | T <sub>CES1</sub>   | 2.1 | 1.9 | 1.7 | ns    |

| I/O Flip-flop Clock Enable Hold Time                                    | T <sub>CEH1</sub>   | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop GSR Set/Reset Delays                                    | T <sub>GSRI</sub>   | 2.5 | 2.3 | 2.1 | ns    |

| Output Flip-flop GSR Set/Reset Delays                                   | T <sub>GSRO</sub>   | 1.9 | 1.7 | 1.5 | ns    |

| Input Flip-flop GSR Set/Reset Setup Time                                | T <sub>GSRIS1</sub> | 0.3 | 0.3 | 0.3 | ns    |

| Output Flip-flop GSR Set/Reset Setup Time                               | T <sub>GSROS1</sub> | 0.3 | 0.3 | 0.3 | ns    |

Table 16: Input and Output Buffer Parameters (I/O set to AGP, CTT, GTL, GTLP, HSTL, SSTL)

- (1) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading: GTL: 7ps/pF

- GTLP: 4ps/pF

- (3) For  $V_{CCI} = 3.3V$ .

|                                            |                      | Sp  |     |     |       |

|--------------------------------------------|----------------------|-----|-----|-----|-------|

| Description                                | Symbol               | -E  | -F  | -G  | Units |

|                                            |                      | Max | Мах | Max |       |

| OE to Pad Active (No Load) <sup>(2)</sup>  | T <sub>3SOE</sub>    | 3.2 | 2.9 | 2.6 | ns    |

| OE to Pad Hi-Z (No Load) (2)               | T <sub>3SOD</sub>    | 3.6 | 3.3 | 3.0 | ns    |

| OE Flip-flop Clock to Pad Active (No Load) | T <sub>Q3SOE</sub>   | 2.1 | 1.9 | 1.7 | ns    |

| OE Flip-flop Clock to Hi-Z (No Load)       | T <sub>Q3SOD</sub>   | 2.4 | 2.2 | 2.0 | ns    |

| OE Flip-flop Setup Time                    | T <sub>OEIS</sub>    | 2.2 | 2.0 | 1.8 | ns    |

| OE Flip-flop Hold Time                     | T <sub>OEIH</sub>    | 0.0 | 0.0 | 0.0 | ns    |

| OE Flip-flop GSR Set/Reset Delay           | T <sub>OEGSRI</sub>  | 3.6 | 3.3 | 3.0 | ns    |

| OE Flip-flop GSR Setup Time                | T <sub>OEGSRIS</sub> | 0.6 | 0.5 | 0.5 | ns    |

Table 17: Three-state Buffer Delays (I/O set to AGP, CTT, GTL, GTLP, HSTL, SSTL)

Notes:

- (1) All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading: GTL: 7ps/pF

GTLP: 4ps/pF

(3) Should be measured with output held at  $V_{OL}$  + 0.5V.

(4) For  $V_{CCI} = 3.3V$ .

|                                                |                     | Sp  |     |     |       |

|------------------------------------------------|---------------------|-----|-----|-----|-------|

| Description                                    | Symbol              | -E  | -F  | -G  | Units |

|                                                |                     | Max | Max | Max |       |

| Input Buffer Combinatorial Delay               | T <sub>INPD</sub>   | 3.2 | 2.9 | 2.6 | ns    |

| Input Flip-flop Setup Time (Global Clock)      | T <sub>INIS1</sub>  | 2.3 | 2.1 | 1.9 | ns    |

| Input Flip-flop Hold Time (Global Clock)       | T <sub>INIH1</sub>  | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop Clock to Output (Global Clock) | T <sub>INCO1</sub>  | 1.7 | 1.5 | 1.4 | ns    |

| I/O Flip-flop Clock Enable Setup Time          | T <sub>CES1</sub>   | 2.1 | 1.9 | 1.7 | ns    |

| I/O Flip-flop Clock Enable Hold Time           | T <sub>CEH1</sub>   | 0.0 | 0.0 | 0.0 | ns    |

| Input Flip-flop GSR Set/Reset Delays           | T <sub>GSRI</sub>   | 2.5 | 2.3 | 2.1 | ns    |

| Input Flip-flop GSR Set/Reset Setup Time       | T <sub>GSRIS1</sub> | 0.3 | 0.3 | 0.3 | ns    |

#### Table 18: Input Buffer Parameters (I/O Set to LV-PECL or LVDS)

Note:

All delays are specified over commercial voltage and temperature range. For industrial voltage and temperature range, add 5%.

### **Logic Block Switching Characteristics**

| 3-Input AND/OR to Flip-flop DelayTA6-Input AND/OR to Flip-flop DelayTA9-Input AND/OR to Flip-flop DelayTA7-Input XOR to Flip-flop DelayTX8:1 Multiplexer Data to Flip-flopTM8:1 Multiplexer Select to Flip-flopTM2-Bit Adder/Multiplier to Flip-flop (Sum)TA3-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA7-Input XOR Combinatorial DelayTA | VMbol<br>NNDR3 4<br>NNDR6 4<br>NNDR9 4<br>VNDR9 4<br>VUXR8 4<br>VUXR8 4<br>NDCR 4<br>NDC3 4 | -E<br>Max<br>2.6<br>3.0<br>3.3<br>3.4<br>2.8<br>2.9<br>3.3 | -F<br>Max<br>2.3<br>2.7<br>3.0<br>3.1<br>2.5<br>2.6 | -G<br>Max<br>2.1<br>2.4<br>2.7<br>2.8<br>2.3 | Units<br>ns<br>ns<br>ns<br>ns |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|-------------------------------|

| 6-Input AND/OR to Flip-flop DelayTA9-Input AND/OR to Flip-flop DelayTA7-Input XOR to Flip-flop DelayTx8:1 Multiplexer Data to Flip-flopTm8:1 Multiplexer Select to Flip-flopTm2-Bit Adder/Multiplier to Flip-flop (Sum)TA3-Input AND/OR Combinatorial DelayTa9-Input AND/OR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa      | NDR6<br>NDR9<br>(ORR7<br>/UXR8<br>UXSR8<br>DDCR<br>NDC3                                     | 2.6<br>3.0<br>3.3<br>3.4<br>2.8<br>2.9                     | 2.3<br>2.7<br>3.0<br>3.1<br>2.5                     | 2.1<br>2.4<br>2.7<br>2.8                     | ns<br>ns                      |

| 6-Input AND/OR to Flip-flop DelayTA9-Input AND/OR to Flip-flop DelayTA7-Input XOR to Flip-flop DelayTx8:1 Multiplexer Data to Flip-flopTm8:1 Multiplexer Select to Flip-flopTm2-Bit Adder/Multiplier to Flip-flop (Sum)TA3-Input AND/OR Combinatorial DelayTa9-Input AND/OR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa      | NDR6<br>NDR9<br>(ORR7<br>/UXR8<br>UXSR8<br>DDCR<br>NDC3                                     | 3.0<br>3.3<br>3.4<br>2.8<br>2.9                            | 2.7<br>3.0<br>3.1<br>2.5                            | 2.4<br>2.7<br>2.8                            | ns<br>ns                      |

| 9-Input AND/OR to Flip-flop DelayTA7-Input XOR to Flip-flop DelayTx8:1 Multiplexer Data to Flip-flopTh8:1 Multiplexer Select to Flip-flopTh2-Bit Adder/Multiplier to Flip-flop (Sum)TA3-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA7-Input XOR Combinatorial DelayTA7-Input XOR Combinatorial DelayTa7-Input XOR Combinatorial DelayTa                                         | NDR9<br>(ORR7<br>MUXR8<br>UXSR8<br>NDDCR<br>NNDC3                                           | 3.3<br>3.4<br>2.8<br>2.9                                   | 3.0<br>3.1<br>2.5                                   | 2.7<br>2.8                                   | ns                            |

| 7-Input XOR to Flip-flop DelayTx8:1 Multiplexer Data to Flip-flopTm8:1 Multiplexer Select to Flip-flopTm2-Bit Adder/Multiplier to Flip-flop (Sum)Tm3-Input AND/OR Combinatorial DelayTm6-Input AND/OR Combinatorial DelayTm9-Input AND/OR Combinatorial DelayTm7-Input XOR Combinatorial DelayTm7-Input XOR Combinatorial DelayTm                                                                         | KORR7<br>MUXR8<br>UXSR8<br>NDDCR<br>NNDC3                                                   | 3.4<br>2.8<br>2.9                                          | 3.1<br>2.5                                          | 2.8                                          | -                             |

| 8:1 Multiplexer Data to Flip-flopT_N8:1 Multiplexer Select to Flip-flopT_M2-Bit Adder/Multiplier to Flip-flop (Sum)T_A3-Input AND/OR Combinatorial DelayT_A6-Input AND/OR Combinatorial DelayT_A9-Input AND/OR Combinatorial DelayT_A7-Input XOR Combinatorial DelayT_A                                                                                                                                   | AUXR8<br>UXSR8<br>ADDCR<br>ANDC3                                                            | 2.8<br>2.9                                                 | 2.5                                                 |                                              | ns                            |

| 8:1 Multiplexer Select to Flip-flopT_M2-Bit Adder/Multiplier to Flip-flop (Sum)T_A3-Input AND/OR Combinatorial DelayT_A6-Input AND/OR Combinatorial DelayT_A9-Input AND/OR Combinatorial DelayT_A7-Input XOR Combinatorial DelayT_X                                                                                                                                                                       | NDC3                                                                                        | 2.9                                                        |                                                     | 2.3                                          |                               |

| 2-Bit Adder/Multiplier to Flip-flop (Sum)TA3-Input AND/OR Combinatorial DelayTA6-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA7-Input XOR Combinatorial DelayTA                                                                                                                                                                                                                  | ADDCR<br>ANDC3                                                                              |                                                            | 2.6                                                 |                                              | ns                            |

| 3-Input AND/OR Combinatorial DelayTA6-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA7-Input XOR Combinatorial DelayTa                                                                                                                                                                                                                                                             | NDC3                                                                                        | 3.3                                                        |                                                     | 2.3                                          | ns                            |

| 6-Input AND/OR Combinatorial DelayTA9-Input AND/OR Combinatorial DelayTA7-Input XOR Combinatorial DelayTa                                                                                                                                                                                                                                                                                                 |                                                                                             |                                                            | 3.0                                                 | 2.7                                          | ns                            |

| 9-Input AND/OR Combinatorial Delay     T <sub>A</sub> 7-Input XOR Combinatorial Delay     T <sub>X</sub>                                                                                                                                                                                                                                                                                                  |                                                                                             | 2.8                                                        | 2.5                                                 | 2.3                                          | ns                            |

| 7-Input XOR Combinatorial Delay T <sub>X</sub>                                                                                                                                                                                                                                                                                                                                                            | NDC6                                                                                        | 3.2                                                        | 2.9                                                 | 2.6                                          | ns                            |

|                                                                                                                                                                                                                                                                                                                                                                                                           | NDC9                                                                                        | 3.6                                                        | 3.2                                                 | 2.9                                          | ns                            |

| O lanut Componentes Combinatorial Dalay                                                                                                                                                                                                                                                                                                                                                                   | (ORC7                                                                                       | 3.6                                                        | 3.2                                                 | 2.9                                          | ns                            |

| 2-Input Comparator Combinatorial Delay T <sub>C</sub>                                                                                                                                                                                                                                                                                                                                                     | COMP3                                                                                       | 3.7                                                        | 3.3                                                 | 3.0                                          | ns                            |

| Adder/Multiplier Delay (Sum) T                                                                                                                                                                                                                                                                                                                                                                            | ADDC                                                                                        | 3.8                                                        | 3.4                                                 | 3.1                                          | ns                            |

| 8:1 Multiplexer Data Combinatorial Delay T <sub>N</sub>                                                                                                                                                                                                                                                                                                                                                   | /UXC8                                                                                       | 3.0                                                        | 2.7                                                 | 2.4                                          | ns                            |

| 8:1 Multiplexer Select Combinatorial Delay T <sub>N</sub>                                                                                                                                                                                                                                                                                                                                                 | /UXS8                                                                                       | 3.1                                                        | 2.8                                                 | 2.5                                          | ns                            |

| Carry Chain Initial Delay T                                                                                                                                                                                                                                                                                                                                                                               | CRYI                                                                                        | 2.7                                                        | 2.4                                                 | 2.2                                          | ns                            |

| Carry Chain Delay Per 2 Bits T                                                                                                                                                                                                                                                                                                                                                                            | CRY                                                                                         | 0.3                                                        | 0.3                                                 | 0.2                                          | ns                            |

| Carry Chain Final Delay T                                                                                                                                                                                                                                                                                                                                                                                 | CRYF                                                                                        | 2.3                                                        | 2.0                                                 | 1.8                                          | ns                            |

| D-Flip-flop Setup Time                                                                                                                                                                                                                                                                                                                                                                                    | T <sub>SU</sub>                                                                             | 0.4                                                        | 0.4                                                 | 0.3                                          | ns                            |

| D-Flip-flop Hold Time                                                                                                                                                                                                                                                                                                                                                                                     | T <sub>HD</sub>                                                                             | 0.0                                                        | 0.0                                                 | 0.0                                          | ns                            |

| T-Flip-flop Setup Time T                                                                                                                                                                                                                                                                                                                                                                                  | Г <sub>SUT</sub>                                                                            | 0.5                                                        | 0.5                                                 | 0.4                                          | ns                            |

| T-Flip-flop Hold Time T                                                                                                                                                                                                                                                                                                                                                                                   | тно                                                                                         | 0.0                                                        | 0.0                                                 | 0.0                                          | ns                            |

| Flip-flop Clock to Out (GCLK or QCLK) T                                                                                                                                                                                                                                                                                                                                                                   | COG                                                                                         | 1.1                                                        | 1.0                                                 | 0.9                                          | ns                            |

| Flip-flop Clock to Out (LCLK) T                                                                                                                                                                                                                                                                                                                                                                           | COL                                                                                         | 3.3                                                        | 3.0                                                 | 2.7                                          | ns                            |

| GSR Set/Reset Delay T                                                                                                                                                                                                                                                                                                                                                                                     | GSR                                                                                         | 2.4                                                        | 2.2                                                 | 1.9                                          | ns                            |