# ACC2087 ENHANCED SUPER CHIP

# DATA BOOK ADVANCED INFORMATION

AUGUST 1996 Revision 1.1 \_\_\_\_\_ 2087

#### **ACC Microelectronics Corporation**

2500 Augustine Drive, Santa Clara, CA 95054 Phone: (408) 980-0622 Fax: (408) 980-0626

Copyright 1996 ACC Microelectronics Corporation. All rights reserved. P/N 520141 Revision 1.1 August 1996

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of ACC Microelectronics Corporation.

ACC Microelectronics Corporation makes no warranty for the use of its products and bears no responsibility for any errors which might be appear in this document. Specifications are subject to change without notice.

ACC Micro is a trademark of ACC Microeletronics Corporation.

IBM, AT, XT, PS/2, Micro Channel are trademarks of International Business Machines.

Pentium, Intel are trademarks of Intel Corporation. M1 is a trademark of Cyrix Corporation. K5 is a trademark of Advanced Micro Devices

# **Table of Contents**

| Title |                                                  | Page |

|-------|--------------------------------------------------|------|

| 1.0   | ACC2087 Introduction                             | 1    |

|       | 1.1 ACC2087 Features                             | 1    |

|       | 1.2 ACC2087 System Block Diagram                 | 1    |

|       | 1.3 ACC2087 Internal Block Diagram               | 3    |

| 2.0   | ACC2087 Functional Description                   | 4    |

|       | 2.1 CPU Interface                                | 4    |

|       | 2.2 80387 Interface Control                      | 4    |

|       | 2.3 Clock Generator                              | 4    |

|       | 2.4 Clock Mode Selection                         | 5    |

|       | 2.5 Stop Grant, Stop Clock, for 1X Clock Scaling | 6    |

|       | 2.6 Clock Throttling                             | 7    |

|       | 2.7 Local Bus Peripheral Support                 | 7    |

|       | 2.8 Intel System Management Mode Interface       | 8    |

|       | 2.9 Power Management Features                    | 10   |

|       | 2.10 Shadow Register Table Description           | 11   |

|       | 2.11 High Performance Cache Controller           | 14   |

|       | 2.12 Memory Controller                           | 15   |

|       | 2.13 Memory Mapping                              | 16   |

|       | 2.14 Shadow RAM                                  | 16   |

|       | 2.15 Interrupt Controllers                       | 16   |

|       | 2.16 DMA                                         | 16   |

|       | 2.17 Memory Mapper                               | 17   |

|       | 2.18 Timer/Counter                               | 17   |

|       | 2.19 ACC2087 I/O Address Map                     | 17   |

|       | 2.20 PIO                                         | 17   |

|       | 2.21 DMA Arbitration Logic                       | 17   |

|       | 2.22 Refresh Generation Logic                    | 17   |

|       | 2.23 Staggered Refresh Logic                     | 18   |

|       | 2.24 NMI and Port B Logic                        | 18   |

|       | 2.25 Bus Controller and Converter                | 18   |

|       | 2.26 Turbo Speed Control Logic                   | 19   |

|       | 2.27 8-bit/16-bit ROM Options                    | 20   |

|       | 2.28 128K/64K ROM BIOS Range                     | 20   |

|       | 2.29 Reset and Shutdown Logic                    | 20   |

|       | 2.30 OS/2 Optimization                           | 21   |

|       | 2.31 Floppy Disk Drives                          | 22   |

|       | 2.32 Serial Port Interface                       | 38   |

|       | 2.33 Parallel Port Interface                     | 51   |

### Table of Contentscontd.

| Title |                                                                  | Page |

|-------|------------------------------------------------------------------|------|

| 3.0   | ACC2087 Pin Description                                          | 56   |

|       | 3.1 ACC2087 Pin Descriptions                                     | 56   |

|       | 3-1 Clock Interface                                              | 56   |

|       | 3-2 Reset Interface                                              | 56   |

|       | 3-3 CPU Interface                                                | 56   |

|       | 3-4 Power Management/Cache/DRAM/AT Multiplex Interface           | 59   |

|       | 3-5 Dedicated Power Management Interface                         | 60   |

|       | 3-6 Dedicated Cache Interface                                    | 61   |

|       | 3-7 DRAM Interface                                               | 62   |

|       | 3-8 AT Bus Interface                                             | 62   |

|       | 3-9 Keyboard/Mouse Interface                                     | 65   |

|       | 3-10 FDC Interface                                               | 65   |

|       | 3-11 COM1 Interface                                              | 66   |

|       | 3-12 COM2 Interface                                              | 66   |

|       | 3-13 IDE and LPT1 Interface                                      | 67   |

|       | 3.2 ACC2087 Numerical Pin List                                   | 68   |

|       | 3.3 ACC2087 Desktop vs. Notebook Multiplexed Pin Summary         | 69   |

|       | 3.4 ACC2087 Pins Status for Various CPU Types                    | 69   |

|       | 3.5 ACC2087 Numerical Pin List with Multifunction pins and Power |      |

|       | Plane Description                                                | 70   |

| 4.0   | ACC2087 Register Settings                                        | 73   |

|       | 4.1 ACC2087 Register Settings                                    | 73   |

| 5.0   | ACC2087 Upgrade Advanced Parallel Port                           | 112  |

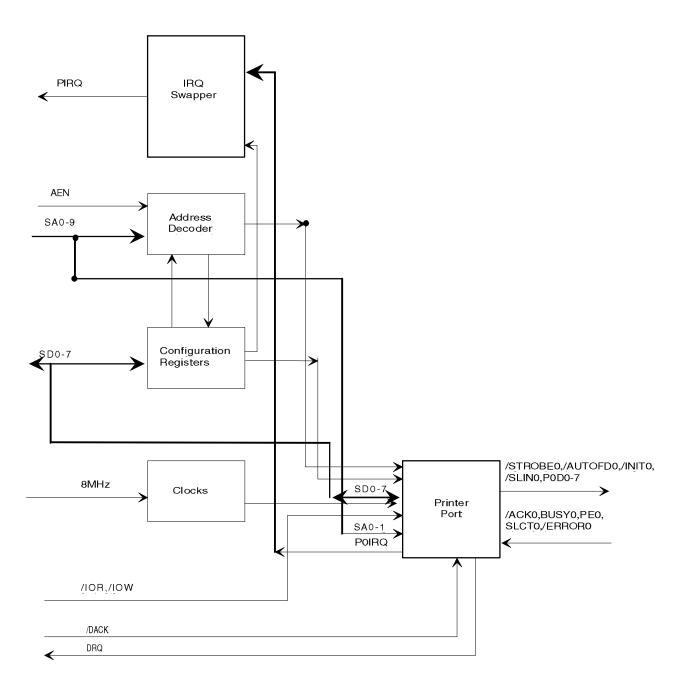

|       | 5.1 Description, Features, and Block Diagram                     | 112  |

|       | 5.2 Features                                                     | 112  |

|       | 5.3 Block Diagram                                                | 112  |

|       | 5.4 Programmable Configuration Registers                         | 114  |

|       | 5.5 Parallel Port Interface                                      | 115  |

| 6.0   | ACC2087 DC Specifications                                        | 116  |

| 7.0   | ACC2087 AC Specifications                                        | 125  |

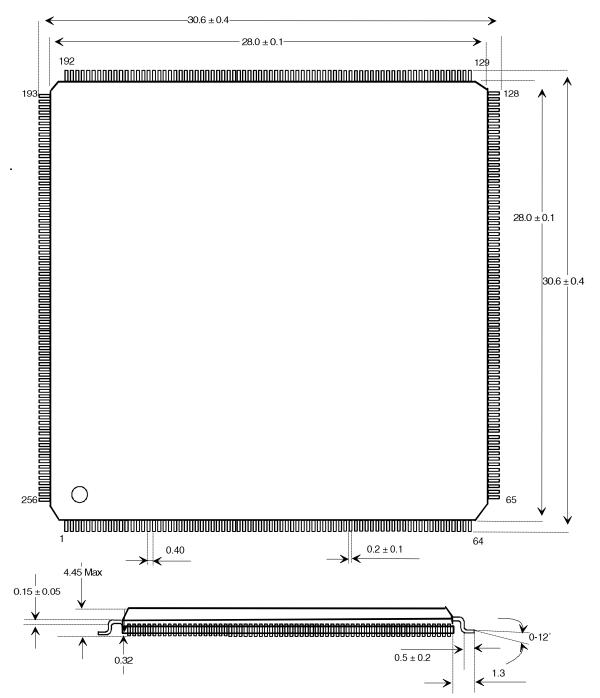

| 8.0   | ACC2087 Package Specifications                                   | 150  |

### Appendix A-1 List of Sales Representatives

## Section 1

### Introduction

### **1.1 2087 Features**

- Supports Intel iDX4, AMD AM486, Cyrix 5x86, TI 486s, and IBM Blue Lightning microprocessor with operation up to 50 MHz

- ♦ 3.3V / 5.0V mixed voltage system design

- Level 1 Write Back Cache

- Level 2 Cache Controller

- Support either write back or write through implementation

- Up to 2 MB in cache size

- High Performance DRAM Controller

Supports four banks of 32-bit DRAM, Fast Page Mode only, allowing up to 64 MB memory

- Integrated Peripheral Controller: 2 x 8237, 2 x 8259, 1 x 8254, 1 x 74612

- Integrated Floppy Disk Controller supports two floppy disk drives

- Supports one IDE interface

- Supports two high speed 16C550 compatible UARTs with 16 Byte FIFOs

- Supports one bi-directional Parallel port with ECP mode

- Support PPM mode where Floppy Disk Drive can be used on Parallel Port

- PS/2 compatible Keyboard Controller and Mouse

- Power Management Control

- Power-On Suspend

- Power-Off Suspend

- Doze / Idle Detection

- Suspend / resume Button

- APM support

SMM / SMI

- Stop Clock Protocol

- Battery monitoring signal and dedicated low-battery warning alarm

- Supports Flash EPROM

- Local Bus IDE

- Fast reset / Fast gate A20 (Port 92)

- 256-pin PQFP device

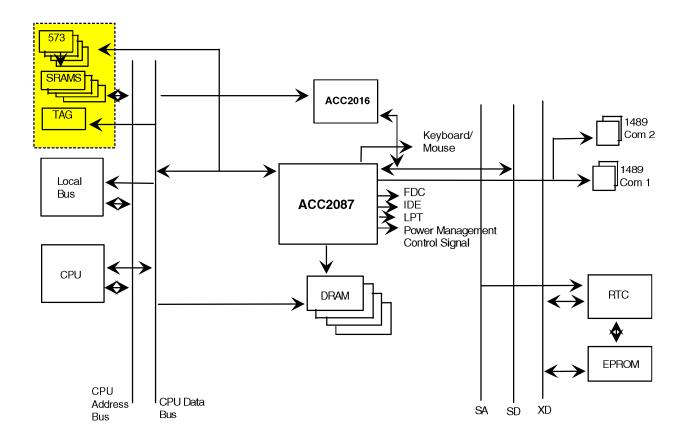

# 1.2 2087 System Block Diagram

2087

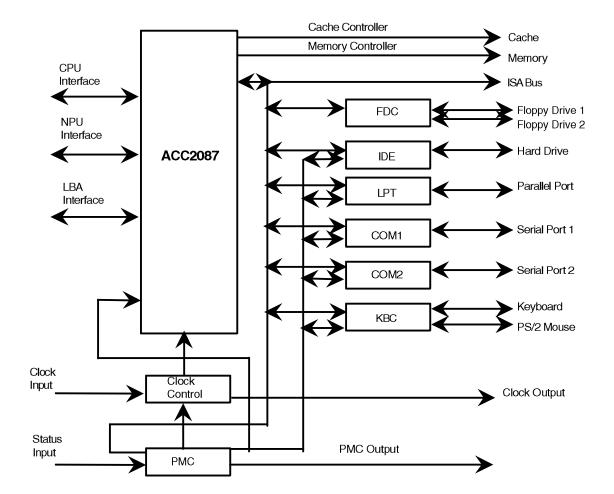

## 1.3 2087 Internal Block Diagram

# Section 2

# **Functional Description**

### 2.1 CPU Interface

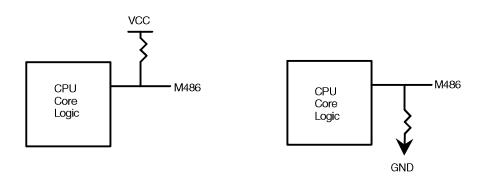

The ACC2087 supports the 486 and 386DX CPUs. The CPU interface selection is determined by detecting a pull up or pull down resistor on pin 172 (M486) during the reset period. A pull up resistor on pin 172 will trigger the ACC2087 operating in the 486 mode. A pull down resistor on pin 172 will trigger the ACC2087 operating in the 386DX mode.

486DX mode configuration

386 mode configuration

### 2.2 80387 Interface Control

The 80387 interfaces directly to the 386DX with the error-reporting logic built in the ACC2087. A coprocessor error is sent to the ACC2087, generating an interrupt request to the CPU, followed by a service request. A write operation to I/O port 0F0 will clear the interrupt request.

### 2.3 Clock Generator

The ACC2087 Clock Generator provides flexible clock signals to support internal and external timing requirements. Clock outputs for the CPU, the NPU, and the Keyboard Controller are generated from these inputs. Three clock sources (CLKSRC, X24M and X14M) are used to derive the system clock output (SYSCLK).

Signal X14M interfaces to a 14.318 MHz crystal to generate a 14.318 MHz frequency. A 24 MHz crystal is used by signal X24M to provide all timing signal for the integrated floppy disk controller. The CLKSRC input is the same input to the CPU clock. CLKSRC input must be driven by an external oscillator. This input is one or two times of the CPU operation clock and provides turbo mode operation in 1x or 2x clock mode, respectively.

The AT Bus clock can be derived from three sources: CLKSRC, X14M, and X24M (by programming register 6h, bit 4-0). CLKSRC can be divided to an approximated 16MHz frequency, or use the 14.318 MHz directly, or it can be generated from the external 24 MHz directly.

#### 2.4 Clock Mode Selection

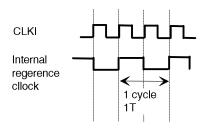

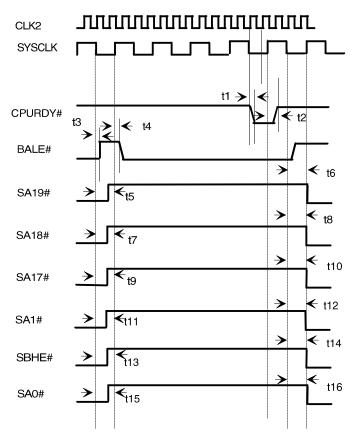

The ACC2087 supports both 1x clock and 2x clock. The clock phase is determined by selecting pin 51, CLKX1 signal for 1x clock from the ACC2087 or by selecting pin 49, CLKX2 signal for 2x clock from the ACC2087.

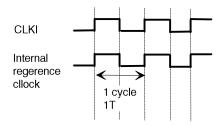

The 2x clock has a clock source, which is two times the CPU operation clock. In 2x clock, every cycle consists of two CLKI periods. 2x clock can be used for both the 486DX/SX systems or 386DX systems. In 486 mode, the ACC2087 provides a dedicated 486 Clock, which is a half of the CLKSRC. This pin, (pin 49) CLKx2, is actually the phase 1 reference clock.

#### 2x clock

The 1x clock has a clock source which is one times of the CPU operation clock. In 1x clock, every CLKI input period becomes one completed cycle. 1x clock is used primarily for the 486 systems. CLKx1 can be used as 486 CPU clock input.

1x clock

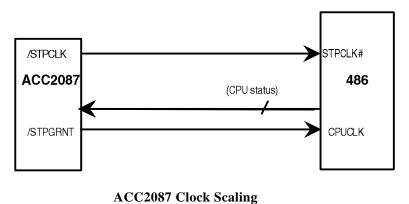

#### 2.5 Stop Grant, Stop Clock, for 1X Clock Scaling:

In a Notebook system, the ability to switch CPU clock is a very important feature for power saving. The ACCACC2087 supports this feature by providing the interface to the CPU for Stop Grant and Stop Clock for 1x Clock Scaling functions.

**1x Clock Stop-Grant Protocol**

2X Clock Mode: When Register 20h bit 5 and Register 8h bit 3-0 of the ACC2087 are set, the "Turbo" pin can toggle CPU clock between turbo and sleep frequency. The CPU clock can also be switched between turbo and sleep frequency by programming Register 1Bh bit 0 to toggle the frequency.

1X Clock Mode: When Register 20h bit 3 is set to zero, ACC2087 will toggle between turbo and sleep frequency.

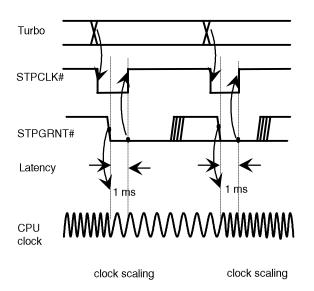

### 2.6 Clock Throttling:

To further reduce the power consumption in the Notebook system, the ACC2087 supports another mode called Clock Throttling. After scaling the CPU clock, the ACC2087 can periodically assert the STPCLK# request which will force the CPU into Stop Grant State. Hence the CPU power can be further reduced.

#### 2.7 Local Bus Peripheral Support Master / DMA Mode and SMM Support in Local Bus Cycle

The ACC2087 supports VL-Bus with master and DMA modes. To further enhance the flexibility, the local bus can be detected under System Management Mode (SMM).

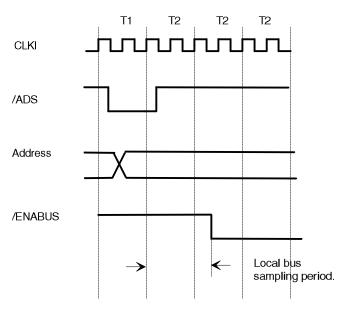

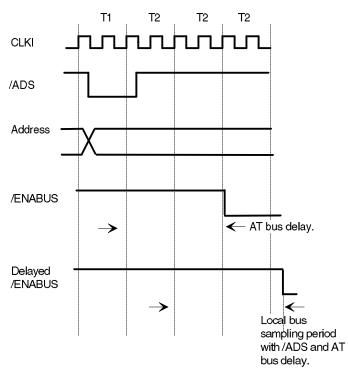

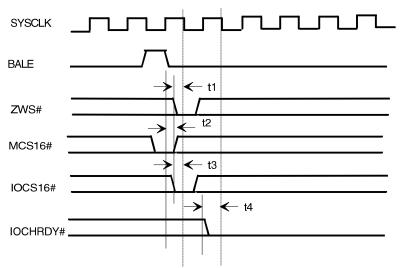

The ACC2087 determines whether the cycle is a local bus cycle or not by detecting the existence of the local bus cycle signal, signaled by a local bus device. When the ACC2087 Register 1Bh, bit 4, is set to one, pin 127 (READY0#, LBA#) becomes the LBA# pin. This pin is connected to the local bus device's local bus acknowledge signal. When LBA# is asserted low, the ACC2087 will terminate all the bus cycles, and relinquish the control to the local bus. The ACC2087 starts to sense the LBA# pin status from the end of T1 until the beginning of the ENABUS# as shown below.

**Local Bus Detection**

For local bus devices operating with a fast speed CPU clock, the ACC2087 offers an option to delay the ADS# one cycle internally to detect the local bus acknowledge or delay the AT bus for one cycle as shown below. Register 1Ah, bit 7, programs the ACC2087 internal ADS# timing. Register 18h, bit 6, programs the AT bus cycle delay.

2087

Local Bus Delay Option

#### 2.8 Intel System Management Mode Interface (SMM)

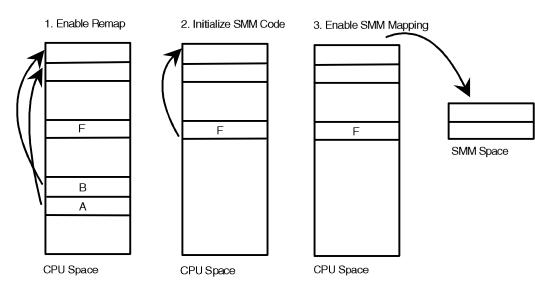

System Management Mode (SMM) is designed to handle power management interrupts that are totally transparent to the existing programs, operating systems and CPU operation modes. The ACC2087 contains dedicated logic to interface with SMM implemented by the Intel SL-enhanced 486 for battery-powered portable computers. The ACC2087 utilizes the DRAMs located between segments A000h and B000h as the separate SMM memory (SMRAM) required by SMM functions.

Before activating the SMM function, the system BIOS first needs to load the SMM service routine into the separate SMM memory (SMRAM). During power-up, the system BIOS can turn on the ACC2087 remap feature so that memory physically located between segment A000h to segment B000h can be accessed logically through locations between X + 128K and X if X memory is installed in the system. The system BIOS then loads the SMM code into this area, disables the remap and then enables ACC2087 SMM support. The remap space is now reserved for SMM. Two 64K blocks are available and one can be programmed as segment 3000h for executing the SMI handler. The remap function will not be available when SMM is used.

SM-RAM Mapping and Initializing for System Management Mode

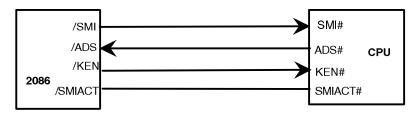

The power management interrupt generated by the ACC2087 is connected to the CPU SMI# pin. The SMM interface circuit has been integrated in the ACC2087 to handle SMM cycle, memory map, and CPU internal cache.

The ACC2087 will enter SMM cycles when it detects SMIACT# being asserted low by the CPU. The physical memory (30000h - 3FFFh) dedicated to System Management Mode (SMM) will be enabled. CPU will use this dedicated SMRAM to perform SMM state save and state restore starting at address location 3FFFh, proceeding downward in a stack-like fashion and execute the SMI handler starting at address location 38000h. Register 1Fh in the ACC2087 contains the SMI enable bits. Setting bit 4 to one will enable the SMM. While bit 5 provides the access to the SMRAM starting at segment 3000h.

System Management Mode Interface (Intel SL-Enhanced CPU)

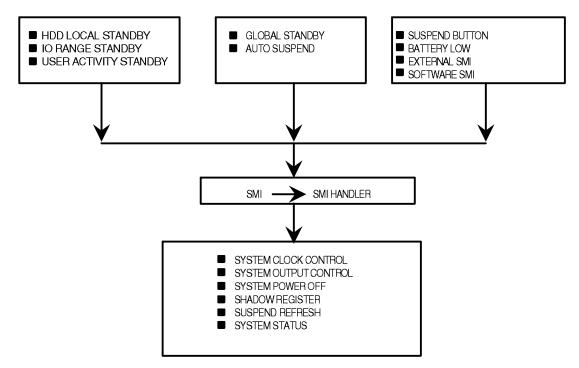

### 2.9 **Power Management Features**

The ACC2087 provides a powerful mechanism of system power management that is completely transparent to the operating system and application software. It was designed from the system level to synthesize and manage power consumption for the lowest power operation while maintaining system performance in the portable system.

The ACC2087 implements four special power saving modes to provide the most sophisticated system information needed for power management application. They are "Local Standby", "Global Standby", "Suspend / Resume", and "Doze" mode. The ACC2087 also provides a dedicated battery low input pin (LBAT#) and warning timer for an external battery pack. A transition on LBAT# should trigger this programmed warning timer. A 1khz tone will be generated through the speaker output as soon as the LBAT# transition is detected. If no transition has been detected, upon warning timer time-out, an SMI will be generated.

### Local Standby Mode (LSM)

The "Local Standby" mode provides three dedicated local standby control circuits to monitor activity on HDD, I/O address for general chip select (GCS), and VRAM, Keyboard/Mouse, respectively. When the associated programmed timer is timed out, an optional SMI will be generated and status bit will be set. Any break event such as hard disk access will generate SMI and bring system back to normal operation.

#### Global Standby Mode (GSM)

When the system has been idle for a programmed standby timer count, and there is no screen activity for a programmed VRAM count, the system can go into global standby mode. All of the peripheral devices can be powered off and the CPU clock can be stopped under global standby mode.

#### Suspend and Resume Mode

The suspend mode can be entered by pressing the suspend/resume button or receiving a low battery input. In addition to the suspend / resume button, the ACC2087 has two user-defined buttons, User button and Standby button, which can bring the system to suspend mode.

The suspend to disk and resume feature is also supported by the ACC2087 through the SL-compatible shadow register.

### Doze Mode

Doze mode provides a mechanism that allows power saving even between the keystrokes. This mechanism utilizes the Frequency Modulation (FM) and Pulse Modulation (PM) techniques which are commonly used in the

telecommunications field. This mode is used not only to provide the temperature control when CPU is busy (non-Doze) but also to further reduce power consumption when CPU is not busy (Doze).

Architecture of System and Power Management

#### 2.10 Shadow Register Table Description

All defined register bits in the ACC2087 are readable and writeable to support the Intel SL type of shadow register. Also the F2 register is now readable to further support the power-saving feature.

Through the shadow registers, the ACC2087 can be powered off and its current state can be suspended to the disk. The device then can be powered back on to the same state as before the last power off when it is desired. This suspend and resume capability minimizes the system's battery power consumption.

Table 1.0 summarizes all of the shadow registers and their descriptions.

1. All the registers listed are originally write-only in ISA standard. The shadow mechanism makes them readable through the 0F2h/0F3h indexing scheme.

2. For some DMA registers that contain 2 bytes but have only one index assigned, the following sequence must be followed:

- cli ;make sure the sequence will not be broken

- out 0f2h, indx ;output index, clear the byte pointer, point to low byte

- mov ah, al ;save it somewhere

- in al, of 3h ;high byte, byte pointer will not be changed, stay at high byte.

- \* Any write to 0F2h with index 0Axh will clear the byte pointer, which will set pointer to low byte. The first read from 0F3h after writing the index will set the pointer to high byte.

- \* Only one byte pointer is shared by all paired register sets.

- \* The first read from 0F3h will return the low byte, the second read will return the high byte.

3. For those registers that do not use all the bits, unused bits status are undefined. Software needs to mask out these bits when it restores.

- 4. For DMA base address registers, word count registers, channel mode registers, and channel mask registers, the value read back from the shadow registers are the original values loaded.

- 5. The value read back from shadow registers for the timer count are the original values loaded.

# ACC Micro<sup>™</sup>\_\_\_\_\_

## Shadow Register Table

| Register Name         | SL Mnemonic | Original | Index | Comment |

|-----------------------|-------------|----------|-------|---------|

|                       |             | Address  |       |         |

| DMA CH0 Base Address  | SHDMA0BA    | 00H      | 0A0H  | 2 bytes |

| DMA CH0 Count         | SHDMA0WC    | 01h      | 0A1h  | 2 bytes |

| DMA CH1 Base Address  | SHDMA1BA    | 02h      | 0A2h  | 2 bytes |

| DMA CH1 Count         | SHDMA1WC    | 03h      | 0A3h  | 2 bytes |

| DMA CH2 Base Address  | SHDMA2BA    | 04h      | 0A4h  | 2 bytes |

| DMA CH2 Count         | SHDMA2WC    | 05h      | 0A5h  | 2 bytes |

| DMA CH3 Base Address  | SHDMA3BA    | 06h      | 0A6h  | 2 bytes |

| DMA CH3 Count         | SHDMA3WC    | 07h      | 0A7h  | 2 bytes |

| DMA CH0 Mode          | SHDMA0MOD   | 0Bh      | 0C0h  | 1 byte  |

| DMA CH1 Mode          | SHDMA1MOD   | 0Bh      | 0C1h  | 1 byte  |

| DMA CH2 Mode          | SHDMA2MOD   | 0Bh      | 0C2h  | 1 byte  |

| DMA CH3 Mode          | SHDMA3MOD   | 0Bh      | 0C3h  | 1 byte  |

| DMA CNTLR 1 Mask Reg. | SHDMAMSK1   | 0Fh      | 0C4h  | 1byte   |

| PIC1 ICW2             | SHINT1ICW2  | 21h      | 0D0h  | 1 byte  |

| PIC1 ICW4             | SHINT1ICW4  | 21h      | 0D1h  | 1 byte  |

| PIC1 OCW3             | SHINT10CW3  | 20h      | 0D2h  | 1 byte  |

| NMI Mask & RTC index  | SHNMIMASK   | 70h      | 0D6h  | 1 byte  |

| TMR 1 CNTR 0 cnt low  | SHT1CH0CL   | 40h      | 0CAh  | 1byte   |

| TMR 1 CNTR 0 cnt high | SHT1CH0CH   | 40h      | 0CBh  | 1 byte  |

| TMR 1 CNTR 1 cnt low  | SHT1CH1CL   | 41h      | 0CCh  | 1 byte  |

| TMR 1 CNTR 1 cnt high | SHT1CH1CH   | 41h      | 0CDh  | 1 byte  |

| TMR 1 CNTR 2 cnt low  | SHT1CH2CL   | 42h      | 0CEh  | 1 byte  |

| TMR 1 CNTR 2 cnt high | SHT1CH2CH   | 42h      | 0CFh  | 1 byte  |

| DMA CH4 Base Address  | SHDMA4BA    | 0C0h     | 0A8h  | 2 bytes |

| DMA CH4 Count         | SHDMA4WC    | 0C2h     | 0A9h  | 2 bytes |

| DMA CH5 Base Address  | SHDMA5BA    | 0C4h     | 0AAh  | 2 bytes |

| DMA CH5 Count         | SHDMA5WC    | 0C6h     | 0ABh  | 2 bytes |

| DMA CH6 Base Address  | SHDMA6BA    | 0C8h     | 0ACh  | 2 bytes |

| DMA CH6 Count         | SHDMA6WC    | 0CAh     | 0ADh  | 2 bytes |

| DMA CH7 Base Address  | SHDMA7BA    | 0CCh     | 0AEh  | 2 bytes |

| DMA CH7 Count         | SHDMA7WC    | 0CEh     | 0AFh  | 2 bytes |

| DMA CH4 Mode          | SHDMA4MOD   | 0D6h     | 0C5h  | 1 byte  |

| DMA CH5 Mode          | SHDMA5MOD   | 0D6h     | 0C6h  | 1 byte  |

| DMA CH6 Mode          | SHDMA6MOD   | 0D6h     | 0C7h  | 1 byte  |

| DMA CH7 Mode          | SHDMA7MOD   | 0D6h     | 0C8h  | 1 byte  |

| DMA CNTLR 2 Mask Reg. | SHDMAMSK2   | 0DEh     | 0C9h  | 1 byte  |

| PIC2 ICW2             | SHINT2ICW2  | 0A1h     | 0D3h  | 1 byte  |

| PIC2 ICW4             | SHINT2ICW4  | 0A1h     | 0D4h  | 1 byte  |

| PIC2 OCW3             | SHINT2OCW3  | 0A0h     | 0D5h  | 1 byte  |

### 2.11 High Performance Cache Controller

The integrated ACC2087 cache controller supports a direct mapped cache from 32 Kbytes up to 2 Mbytes in size. The direct mapped architecture means that a specified line in the cache is capable of caching only a certain range of memory addresses. The low order address bits choose the location (index) while the high order address bits (tag) identify the entry.

As for write policy, the ACC2087 supports either write through or write back cache implementations. In addition, the ACC2087 cache architecture can be used in both 386DX and 486 applications. For a 386DX design, the ACC2087 cache controller can be used to support a primary cache. In a 486 AT system, if the internal cache of the 486 is enabled, the ACC2087 direct mapped cache can be used as secondary cache.

#### Write Back Cache Policy

The write back cache policy implemented in the ACC2087 allows the system to minimize the frequency of unnecessary slow DRAM updates. For instance, when there are consecutive write hit cycles, the ACC2087 simply updates the cache without introducing any memory delay.

A write back cache design allows the write hit cycles to be completed in zero wait state accesses without updating the system main memory. Therefore, "stale" data is created where cache data and main memory data are not coherent. A write back cache design uses a "dirty" bit to keep track of whether each cache data line is a "clean" or "dirty" line. A "clean" line, dirty bit = 0, means the cache data and the corresponding main memory are identical. A "dirty" line, dirty bit = 1, indicates the cache data has been modified, which at some point must be written back to main memory.

Following is the write back cache mechanism for ACC2087:

#### Write Hit

In a cache write hit cycle, the ACC2087 will write to cache and set the "dirty" bit to 1.

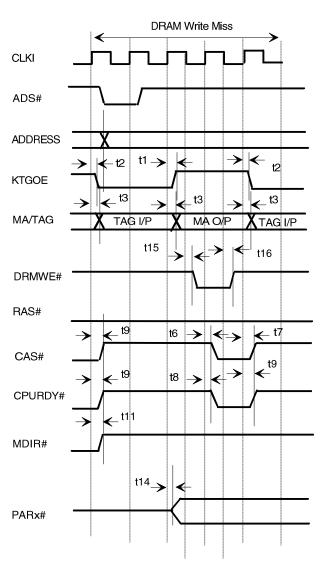

#### Write Miss

In a cache write miss cycle, the ACC2087 will write to DRAM directly.

#### Read Hit

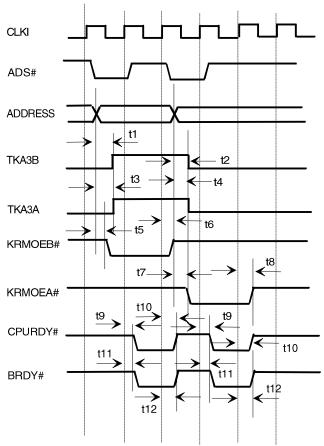

In a cache read hit cycle, the ACC2087 will read from cache directly.

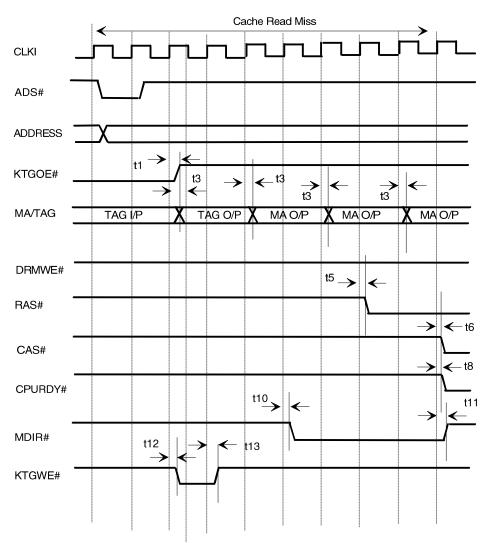

#### **Read Miss**

In a cache read miss cycle, the ACC2087 will examine the "dirty" bit status. If it is non-dirty, cache will be updated directly. If it is dirty, cache data will be "write back" before being updated.

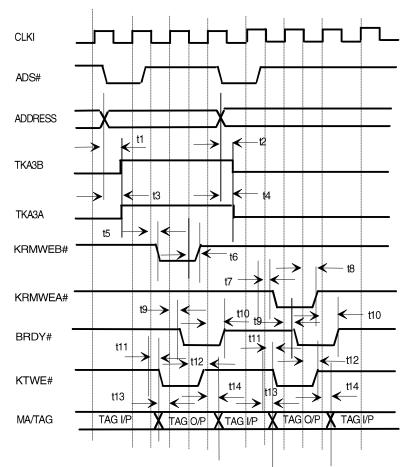

The ACC2087 write back cache is enabled by programming configuration register 1E. When bit 3 in Register 1Eh is set to 1, write back is enabled and the ACC2087 will use integrated comparators for determining cache hit or miss status.

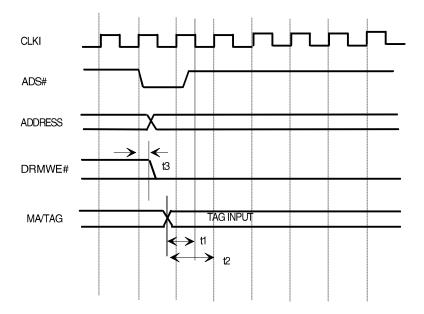

As described earlier, "dirty" status must be updated as well as detected for write back mode. MA10 becomes the dirty bit status signal (DIRTY) and NA# becomes the dirty bit write enable signal (DTYWE#). Refer to figure 1.4.

### Posted Write and Write Through

The ACC2087 cache controller supports write-through and post write cache update options to prevent old data from being used.

The write-through option is the simplest way to keep cache coherent. In a cache write hit cycle, the memory controller will update the DRAM at the same time that it is written to the cache. The ACC2087 cache controller default mode is write-through mode.

#### Write Back Cache Circuit Block Diagram

The ACC2087 also supports posted write cache system by programming Configuration Register 4h, bit 7=1. The posted write option allows the data to be buffered before updating to the main memory. The system performance is therefore increased, since the processor can start a new cycle before the write cycle to the main memory is completed.

#### Cache Burst and Line Size

The ACC2087 supports a flexible line size structure and cache burst. The ACC2087 supports 32 bit, 64 bit, or 128 bit line sizes. Configuration Register 4h, bits 2 and 1 determine the line size. In the case of a cache read hit cycle, the ACC2087 will pull the burst ready signal, BRDY#, low and fill the 486 internal cache lines quickly. A 128 bit line size requires only 5 cycles to fill the cache lines. A 64 bit line size requires 3 cycles.

In the case of a read miss cycle, the ACC2087 burst mode will generate four continuous DRAM read cycles for a 128 bit line size to fill both 486 internal and external cache. For a 64 bit line size, the ACC2087 burst mode will generate two burst cycles instead of four.

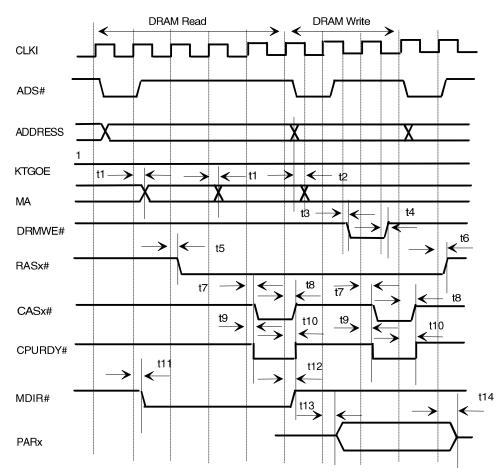

#### 2.12 Memory Controller

The Memory Controller is a key feature of the ACC2087. This versatile circuit provides complete control of up to 64 megabytes of system DRAM. In any control mode, it generates up to four Row Address Strobes (RAS#0-3) and one Memory Write Enable signal (WEN#). The Memory Controller also provides the interface to transfer control to a DMA controller or an AT Bus master.

The ACC2087 Memory Controller supports 256KB, 512KB, 1MB and 4MB DRAM devices. The ACC2087 provides all control signals and programmable control to support 256Kx1, 512Kx1, 1Mx1, 1Mx4, 4Mx1 and 4Mx4 (symmetrical only).

### 2.13 Memory Mapping

Memory Mapping translates system RAM within the 640 KB to 1MB range, which is reserved for the system ROM and BIOS application, to an accessible address range above the physical RAM space. For example, if 4 MB of memory are installed, and the memory mapping feature is on, the DRAMs in the 640 KB to 1MB range are mapped to an address immediately above 4 MB.

Memory Mapping is enabled by bit 7 of Register 0h in the configuration registers. When Shadow RAM is enabled simultaneously with Memory Mapping, the quantity of RAM available for Memory Mapping is reduced. If Shadow RAM segment F is enabled, 320KB of RAM can be mapped. If Shadow segment E is enabled, 256KB of RAM can be mapped. If any of the segments C0, C1, or D is enabled, 128 KB of RAM can be mapped. This mapping function can be used in all memory options, except option 24.

#### 2.14 Shadow RAM

Shadow RAM provides an option to transfer BIOS or video-extension BIOS program codes into system RAM. This option provides significant performance improvement for applications requiring intensive BIOS calls.

Shadow RAM implements an alternate BIOS source by copying the complete EPROM program code into system RAM. This is referred to as "shadowing" because the DRAM and EPROM are both located in the same physical address space. This change is transparent to the rest of the system. ROM can then be disabled, allowing the RAM to respond in its place.

The ACC2087 Shadow RAM is configured in five independent segments: 00C0000 to 00C7FFF (Shadow C0), 00C8000 to 00CFFFF (Shadow C1), 00D0000 to 00DFFFF (Shadow D), 00E0000 to 00EFFFF (Shadow E), and 00F0000 to 00FFFFF (Shadow F). Each segment can be enabled for shadow operation individually or simultaneously.

Enabling a Shadow RAM segment requires two steps. The "shadow enable" configuration bit for the segment to be shadowed must be set to allow the transfer of code from EPROM to DRAM. The second step sets the "Shadow Read Only" configuration bit of the corresponding segment to protect the Shadow RAM. Interrupt Controllers

#### 2.15 Interrupt Controllers

There are two programmable interrupt controllers for the ACC2087. They are fully compatible with Intel's 8259 controller, providing up to 15 interrupt sources

(14 external and 1 internal). The internal line connects to the 8254 Counter 0 output.

These interrupt controllers prioritize interrupt requests to the CPU.

#### 2.16 DMA

The ACC2087 has two DMA controllers, compatible with the Intel 8237, which provide a total of seven external DMA channels.

Combined with the Memory Mapper, each DMA channel has a 24-bit address output to access data throughout the 64 megabyte system address space.

### 2.17 Memory Mapper

The ACC2087 has a built-in logic equivalent to the 74LS612, generating the upper address bits during a DMA cycle.

### 2.18 Timer/Counter

The ACC2087 provides three internal counters, which are compatible with the 8254. The clock input for each counter is tied to a clock of 1.19 MHz, which is derived by dividing the

14.318 MHz crystal input by 12. The output of Counter 0 is connected to the IRQ0 input of interrupt controller 1. Counter 1 initiates a refresh cycle and Counter 2 generates sound waveforms for the speaker.

### 2.19 ACC2087 I/O Address Map

The ACC2087 I/O address decode is fully compatible to the IBM PC/AT requirements. The ACC2087 has decoded the I/O address range from 000 to 0FF to allow users to use the I/O areas not used by the IBM PC/AT.

| Hex Range | Device                                             |

|-----------|----------------------------------------------------|

| 000-00F   | DMA controller 1, 8237A-5                          |

| 020-021   | Interrupt controller 1, 8259A, Master              |

| 040-043   | Timer, 8254                                        |

| 060/064   | Integrated Keyboard Controller                     |

| 060-064   | External Keyboard Controller                       |

| 070-071   | Real-time clock, NMI (non-maskable interrupt) mask |

| 080-08F   | DMA page register, 74LS612                         |

| 092       | Alternative Gate A20 and FAST RESET Register.      |

| 0A0-0A1   | Interrupt controller 2, 8259A                      |

| 0C0-0DF   | DMA controller 2, 8237A-5                          |

| 0F0       | Clear Math Coprocessor Busy                        |

| 0F1       | Reset Math Coprocessor                             |

| 0F2       | ACC2087 Configuration Register Index               |

| 0F3       | ACC2087 Configuration Register Data                |

| 0F8-0FF   | Math Coprocessor                                   |

### 2.20 PIO

The PIO is the system configuration to control the speaker port. It also has circuitry to detect refresh. This condition can be read back as Bit 4 of I/O Port 61h.

### 2.21 DMA Arbitration Logic

There are two possible sources for a hold request to the CPU. Either the DMA controller issues a hold request or the output of Counter 1 in the 8254 makes a low to high transition. The HOLD line is active when either source is requesting a hold. The ACC2087 contains the logic to do the arbitration.

#### 2.22 Refresh Generation Logic

The ACC2087 contains circuitry to perform DRAM refresh cycle. Refresh circuitry contains an 8-bit counter for address SA0-7 during a refresh. In addition, three more address counter bits are presented inside the ACC2087 to support refresh for DRAMs up to 4M bits.

#### 2.23 Staggered Refresh Logic

The ACC2087 refresh logic works to perform a periodic refresh for both system DRAM and extended RAM on the AT Bus. The ACC2087 initiates a refresh cycle by driving its REFRESH# output low, and driving the refresh address onto the MA Bus, simultaneously generating staggered refresh pulses on the four RAS outputs. The RAS outputs are staggered to reduce the current drain caused by the refresh operation. During each refresh cycle, the ACC2087 drives the current refresh address onto the AT address bus. This provides the refresh address for extended memory.

#### 2.24 NMI and Port B Logic

The ACC2087 contains non-maskable interrupt (NMI) signal generation logic. An NMI can be caused by an I/O error or by a parity error. Port B identifies the source of the error. At power up, the NMI signal is masked off. NMI is enabled by writing to I/O address 070 with bit 7 low; NMI is disabled by writing to I/O address 070 with bit 7 high.

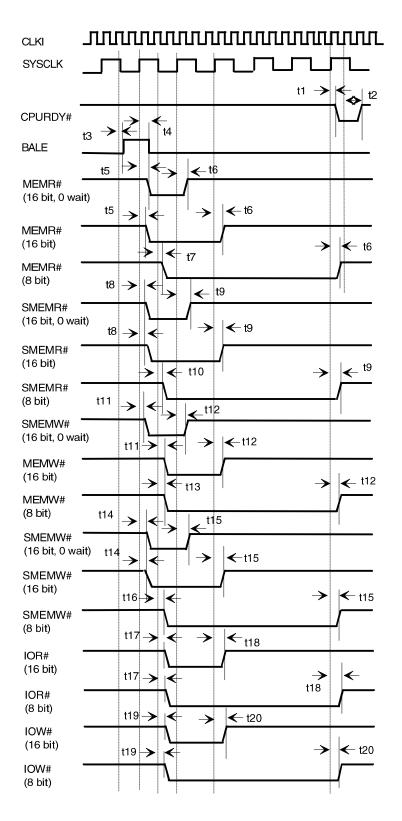

#### 2.25 Bus Controller and Converter

The flexible ACC2087 Bus Controller provides all of the control logic needed to interface to the CPU, alternate masters, local memory, primary or secondary cache and the AT bus. Each access may be initiated by the ACC2087 decoding the address and cycle type provided on the local CPU bus. The cycle type is determined by monitoring the signals D/-C, W/-R and M/-IO.

The bus controller has seven modes of operation which are defined as follows:

#### Local Memory Mode

Local memory mode is entered if the CPU addresses are part of the installed memory and the cycle is defined as a memory access.

#### Local Peripheral Mode

Local Peripheral Mode is entered when the ACC2087 LBA# signal is asserted during the local bus cycle. The ACC2087 will ignore all transactions when LBA# is properly asserted. The local bus peripheral decodes the local address for accesses to the local bus device. The peripheral will assert LBA# and properly complete the cycle. When the local peripheral bus interface is enabled, READY# is not available for coprocessors. The Weitek device should be treated as a local peripheral device. The 387 accesses will always include one wait state.

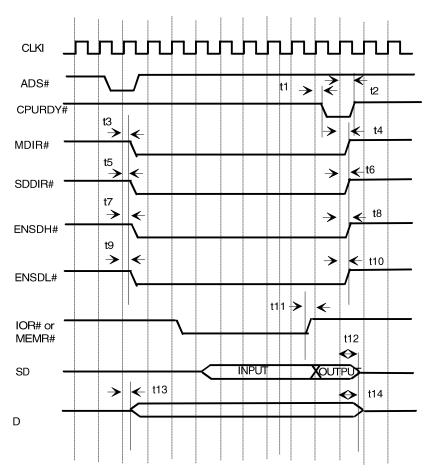

#### AT CPU Mode

This mode is active when HLDA is low. The CPU bus controller generates IOR#, IOW#, INTA#, MEMR#, and MEMW# signals.

#### DMA Mode

DMA mode is active if HLDA and AEN are active. The DMA controller drives the IOR#, IOW#, MEMR#, and MEMW# signals.

### Refresh Mode

Refresh mode is active when HLDA and REFRESH# are active. MEMR# becomes active at this time to perform a refresh on both AT bus and local DRAM.

#### Master Mode

Master mode is active when HLDA is active and a card in the AT slot pulls MASTER# low. The card controls system address, data line and control line.

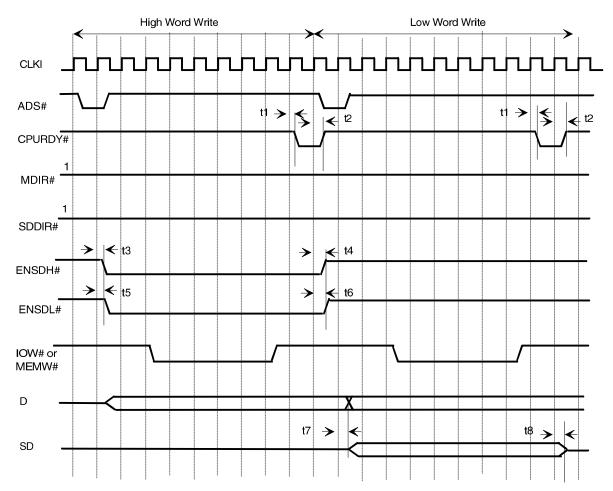

#### Bus Conversion Mode

The ACC2087 contains logic to convert between 16-bit and 8-bit data accessing. During a bus conversion cycle, the AT bus command strobe (MEMR#, MEMW#, IOR#, or IOW#) is activated two times.

#### 2.26 Turbo Speed Control Logic

The CPU clock frequency can be switched between CLKSRC and the AT clock. The frequency switch can be generated through either hardware or software. A TURBO pin is provided to support a front panel turbo speed switch. TURBO high selects CLKSRC as the CPU clock. TURBO low selects AT Bus clock as the CPU clock.

For power conservation, a standby mode clock control is provided. A system needs to pre-select the standby frequency first, then BIOS will monitor the activity of the system. If all pre-defined conditions of the standby mode are satisfied, the system will go into the standby mode by programming bit 3 of Register 8h to 1 or if the Turbo/Sleep bit has been set to 1. The Turbo pin, when driven low, will force the system into sleep mode.

The standby mode CPU operating frequency can be pre-set by programming bits 2-0 of configuration Register 8h. If AT Bus clock source is at 16 MHz, the standby frequencies output of CLKOUT are set as follows:

| Bit 2 | Bit 1 | Bit 0 | Frequency |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | 16 MHz    |

| 1     | 0     | 0     | 9 MHz     |

| 1     | 0     | 1     | 4 MHz     |

| 1     | 1     | 0     | 2 MHz     |

| 1     | 1     | 1     | 1 MHz     |

2087

#### 2.27 8-bit/16-bit ROM Options

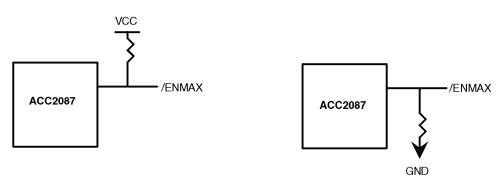

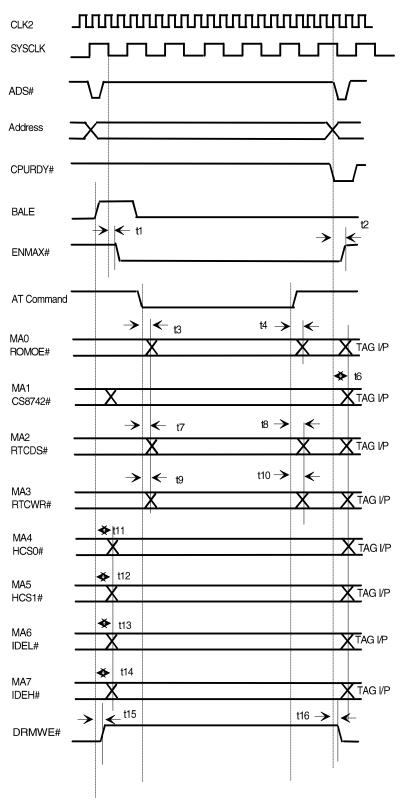

The ACC2087 supports both 8-bit and 16-bit ROM data buses. It is configured by a pull-up or a pull-down resistor on pin 139, ENMAX#, as demonstrated below:

8-bit ROM configuration

16-bit ROM configuration

#### 2.28 128K/64K ROM BIOS Range

The ROM BIOS range can be set to two different sizes 64K or 128K to accommodate various application requirements. Refer to Configuration Register 0h definition to configure the size of the ROM BIOS range.

#### 2.29 Reset and Shutdown Logic

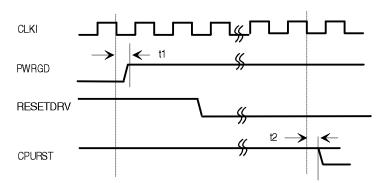

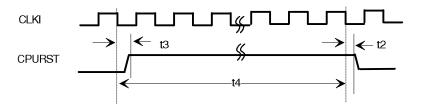

The reset and shutdown logic contains the circuitry for the RESET and CPURDY# signals. Reset circuitry generates two resets. One is for the general system reset with power on and the other is for the CPU. The PWRGOOD signal generates a system reset and is synchronized to CPUCLK. When the SWRESET# signal is generated from the integrated/external keyboard controller (called a warm reset), CPURST is activated to reset the CPU. CPURST is asserted for at least sixteen CPUCLK cycles and then deactivated for proper CPU operation.

#### 2.30 OS/2 Optimization

The ACC2087 implements OS/2 optimization, which is a more efficient way to switch back and forth between real and protected modes in an OS/2 environment when frequent DOS calls are made. Conventional methods require the processor to communicate with the integrated /external keyboard controller in switching to protected mode and activating gate A20.

With OS/2 optimization, the ACC2087 allows control of software CPU reset and A20 gating through Port 92h.

#### Configuration Register Port 92h, Fast A20 Gate, and Alternative RESET Control

| Bit | Function      |

|-----|---------------|

| 7-2 | Reserved      |

| 1   | Fast Gate A20 |

| 0   | Fast reset    |

- Bit 1 This bit controls CPU address bit A20. When set to 1, it enables A20. When set to 0, this bit makes the A20 Signal inactive, thus preventing the Address bus from going beyond the 0FFFFFh boundary in Real Mode. It is much faster than Gate A20 signal because it is just a simple I/O write operation. Default is 0.

- Bit 0 By setting this bit to 1, application software can reinitialize the microprocessor and switch the operation from Protected Mode to Real Mode. Setting this bit does not reset the whole system, it only affects the CPU. This reset function is the same as that of the integrated/external keyboard controller's "KBRST" signal. However, it provides a faster reset sequence. This bit can be read by application software to determine if it is a hot rest or cold boot. It can only be set to 0 by writing a 0 to bit 0 of the register or by power up. Default is 0.

With the ACC2087, designers can build an IBM PC/XT or AT compatible Floppy Disk Drive with fast access time, high reliability and low cost per bit capability. The ACC2087 integrates the functions of a standard floppy disk drive controller.

Data separator Write precompensation circuit Decode logic Data rate selection Clock generation Drive interface drivers and receivers.

This integration greatly reduces the number of components required to interface floppy disk drives to a microprocessor system.

The ACC2087 supports up to two floppy disk drives. It is compatible with IBM System 34 double density format (MFM), and Sony EMCA format.

The ACC2087 contains the decode logic for the internal registers, the write logic and the read logic. The system address decoder is compatible with the IBM PC drive system. Handshaking signals are provided to make DMA operation easy to incorporate with the aid of an external DMA control chip. The ACC2087 operates in either DMA or Non-DMA modes. In the Non-DMA mode, the ACC2087 generates interrupts to the processor each time a data byte is made available. In DMA mode, the processor only needs to load the command into the ACC2087 which will control all data transfers.

The Data Separator in the ACC2087 minimizes read error rates for high performance floppy disk drives. The on-chip phase locked loop digital circuit adjusts the clock used during data read to keep it in phase with the data signal. Write pre compensation is included in addition to the formatting, encoding/decoding, stepper motor control, and status sensing functions. All inputs are TTL compatible, and outputs are high current, open drain with direct drive interface.

Using a single 24 MHz crystal input, the ACC2087's internal Clock Generation circuit provides all timing signals for the sampling clock, write clock, and master clock. It generates 8 and 4 MHz to handle standard data rates of 500 and 250 Kb/s and 4.8 MHz to support a 300 Kb/s data rate.

The ACC2087 executes the following fifteen commands from the microprocessor.

Read Data Read Deleted Data Read a Track Read ID Write Data Write Deleted Data Format a Track Scan Equal Scan Low or Equal Scan High or Equal Recalibrate Sense Interrupt Status Specify Sense Drive Status Seek

### **FDC Register Descriptions**

There are six floppy disk controller registers in the ACC2087, three registers for the status of signals used in diskette operations, one for data register, and two controller registers. The I/O addresses of these registers are described in the tables below.

| Address |           | Registers              |                           |

|---------|-----------|------------------------|---------------------------|

| Primary | Secondary | READ                   | WRITE                     |

| 3F0     | 370       | Input Register         |                           |

| 3F2     | 372       |                        | Digital output register   |

| 3F4     | 374       | Main status register   |                           |

| 3F5     | 375       | Data register          | Data register             |

| 3F7     | 377       | Digital input register | Diskette control register |

#### **Input Register** (HEX 3F0) (R)

The Input Register is a general purpose input register.

| Bit | Function                            |

|-----|-------------------------------------|

| 7-6 | 0                                   |

| 5   | General purpose programmable bit 5. |

| 4   | General purpose programmable bit 4. |

| 3   | General purpose programmable bit 3. |

| 2   | General purpose programmable bit 2. |

| 1   | General purpose programmable bit 1. |

| 0   | General purpose programmable bit 0. |

### Digital Output Register. (HEX 3F2) (8-bits) (W).

The Digital Output Register controls drive motors, drive selection, and feature enable. All bits are cleared by the I/O reset line.

| Bit | Function                      |

|-----|-------------------------------|

| 7-6 | Reserved.                     |

| 5   | Motor Enable 1.               |

| 4   | Motor Enable 0.               |

| 3   | DMA and Interrupt Enable.     |

| 2   | Floppy Disk Controller reset. |

| 1,0 | Drive Select 0,1              |

|     | b1 b0                         |

|     | 0 0 Select drive 0.           |

|     | 0 1 Select drive 1.           |

|     | 1 0 Reserved.                 |

|     | 1 1 Reserved.                 |

#### Main Status Register (HEX 3F4) (R)

The main status register controls data flow between the microprocessor and the controller.

| Bit | Function                                                                                 |

|-----|------------------------------------------------------------------------------------------|

| 7   | Request for Master. = 1 Data Register ready for transfer.                                |

| 6   | Data Input/Output. = 1 Data transfer from controller; = 0 Data transfer from the SD bus. |

| 5   | Execution Mode (Non-DMA mode). =1 Execution                                              |

| 4   | Controller Busy. = 1 Controller busy.                                                    |

| 3   | Drive 3 Busy. = 1 Diskette 3 in seek mode. Drive 3 busy.                                 |

| 2   | Drive 2 Busy. = 1 Diskette 2 in seek mode. Drive 2 Busy.                                 |

| 1   | Drive 1 Busy. = 1 Diskette 1 in seek mode. Drive 1 Busy.                                 |

| 0   | Drive 0 Busy. = 1 Diskette 0 in seek mode. Drive 0 Busy.                                 |

#### Data Register (HEX 3F5) (R/W)

The Data Register consists of four status registers in a stack. Only one register is presented to the data bus at a time. It stores data, commands and parameters, and provides diskette/drive status information. Data bytes are passed through the data register to program or obtain results after a command.

# ACC Micro™\_\_\_\_\_

### Status Register 0 (ST0)

| Bit | Function                                                                                       |  |  |

|-----|------------------------------------------------------------------------------------------------|--|--|

| 7-6 | IC (Interrupt Code).                                                                           |  |  |

|     | <u>7 6</u>                                                                                     |  |  |

|     | 0 0 Normal termination of command.                                                             |  |  |

|     | 0 1 Abnormal termination of command.                                                           |  |  |

|     | 1 0 Invalid command issue.                                                                     |  |  |

|     | 1 1 Abnormal termination because the ready signal from FDD changed state during                |  |  |

|     | command                                                                                        |  |  |

|     | execution.                                                                                     |  |  |

| 5   | SE, (seek end). $= 1$ Seek end.                                                                |  |  |

| 4   | EC (Equipment Check). = 1 When a fault signal is received from the FDD, or the track 0 signals |  |  |

|     | fails to occur after 77 step pulses; $= 0$ No error.                                           |  |  |

| 3   | NR (Not Ready). = 1 Drive is not ready; = 0 Drive is ready.                                    |  |  |

| 2   | HD (Head address). = 1 Head 1 select; = 0 Head 2 select.                                       |  |  |

| 1-0 | US1,US0 (Unit select).                                                                         |  |  |

|     | 1  0                                                                                           |  |  |

|     | 0 0 Drive 0 select.                                                                            |  |  |

|     | 0 1 Drive 1 select.                                                                            |  |  |

|     | 1 0 Drive 2 select.                                                                            |  |  |

|     | 1 1 Drive 3 select.                                                                            |  |  |

### Status Register 1 (ST1)

| Bit | Function                                                                                                              |

|-----|-----------------------------------------------------------------------------------------------------------------------|

| 7   | EN (End of Cylinder). $= 1$ When the FDC tries to access a sector beyond the final sector of a cylinder.              |

| 6   | Not used. This bit is always 0.                                                                                       |

| 5   | DE (Data Error). = 1 When the FDC detects a CRC error in either the ID field or data field.                           |

| 4   | OR (Over Run). = 1 If the FDC is not serviced by the host system during data transfer within a certain time interval. |

| 3   | Not used. This bit is always 0.                                                                                       |

| 2   | ND (No Data). = 1 During execution of Read, Write or Verify Data if the specified sector cannot be found.             |

| 1   | NW (Not Writable). = 1 Set if the "write Protect" signal is detected from the diskette drive during the execution.    |

| 0   | Missing Address Mark. = 1 When the FDC cannot detect the data address mark or deleted data address mark.              |

# ACC Micro<sup>™</sup>\_\_\_\_\_

### Status Register 2 (ST2)

| Bit | Function                                                                                          |

|-----|---------------------------------------------------------------------------------------------------|

| 7   | Not used. Always $= 0$ .                                                                          |

| 6   | CM (Control Mark). = 1 If deleted data is encountered during execution of the Read Data or Scan   |

|     | command.                                                                                          |

| 5   | DD (Data Error in Data Field). = 1 If the FDC detects a CRC error in the data field.              |

| 4   | WC (Wrong Cylinder). = 1 Wrong cylinder.                                                          |

| 3   | SH (Scan Equal Hit). = 1 During execution of the Scan command, if the condition "equal" is        |

|     | satisfied.                                                                                        |

| 2   | SN (Scan Not Satisfy). = 1 During execution of the Scan command, if the FDC cannot find a sector. |

| 1   | BC (Bad Cylinder). = 1 Bad cylinder.                                                              |

| 0   | MD (Missing Address mark in Data Field). = 1 When data is read from the medium, if the FDC        |

|     | cannot find a data address mark or deleted data address mark.                                     |

#### Status Register 3 (ST3)

| Bit | Function             |

|-----|----------------------|

| 7   | FT, Fault.           |

| 6   | WP, Write Protected. |

| 5   | RY, Ready.           |

| 4   | T0, Track 0.         |

| 3   | TS, Two-Side.        |

| 2   | HD, Head Address.    |

| 1   | US1, Unit Select 1.  |

| 0   | US0, Unit Select 0.  |

### **Digital Input Register** (HEX 3F7) (R)

The Digital Input Register is for diagnostic purposes.

| Bit | Function                 |

|-----|--------------------------|

| 7   | Diskette Change (DSKCHG) |

| 6-0 | Tri-State                |

2087

#### Diskette Control Register (HEX 3F7) (W)

The Diskette Control Register sets the precompensation.

| Bit | Function                                                                                                                                     |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7-2 | Reserved                                                                                                                                     |  |  |  |  |  |  |

| 1-0 | Transfer Rates Select and Reduced Write Current Control<br>00 500Kb/s RWC#=1<br>01 300Kb/s RWC#=0<br>10 250Kb/s RWC#=0<br>11 Reserved RWC#=0 |  |  |  |  |  |  |

#### Commands

The diskette controller in ACC2087 is capable of performing fifteen commands. Each command is initiated by a multi-byte transfer from the microprocessor. The result can also be a multi-byte transfer back to the microprocessor. Each command consists of three phases: Command, Execution, and Result.

#### Command

The microprocessor issues all required information to the controller to perform a specific operation.

#### Execution

The controller performs the specified operation.

#### Result

After completing the operation, status information and other housekeeping information are made available to the microprocessor.

#### **Command Symbol Descriptions**

- A0 Address Line 0. A0 controls the selection of main status register (A0=0) or data register (A0=1).

- **C** Cylinder Number. Current or selected cylinder (track), numbers 0 through 76.

- **D** Data. Data pattern to be written into a sector.

- **D7 -D0** Data Bus. 8 bit data bus, where D7 stand for the most significant bit, and D0 stands for the least significant bit.

- **DTL** Data Length. The value of this byte is normally ignored by the controller. However a byte must be written at this location.

- **EOT** End of Track. The final sector number on a cylinder.

- **H** Head Address. Head number 0 or 1, as specified in the ID field.

- **HD** Head. Selected head number 0 or 1. (H=HD in all commands)

- HLT Head Load Time. The head load time in the selected FDD (2 to 254 ms in 2 ms increments.)

- **HUT** Head Unload Time. Time after a Read or Write operation. (16 to 240 ms in 16 ms increments).

- MF Must be 1 to select MFM mode.

- **MT** Multitrack. If MT is high, a multitrack operation is performed. If MT=1 after finishing a read/write operation on side 0, FDC automatically starts searching for sector 1 on side 1.

- **N** Number. The number of data bytes written in a sector.

**NCN** New Cylinder Number. New cylinder number reached as a result of the seek operation; desired position of head.

- **ND** Non-DMA Mode.

- **PCN** Present Cylinder Number. Cylinder number at the completion of the Sense Interrupt Status command, current position of the head.

- **R** Record. The sector number to be read or written.

- **R/W** Read/Write. Either a Read or Write signal.

- **SC** Sector. Number of sectors per cylinder.

- **SK** Skip. Skip deleted data address mark.

- **SRT** Stepping Rate. These bits indicate the stepping rate for the FDD (1 to 16 ms in 1 ms increments). Stepping rate applies to all drives (FH=1ms, EH=2 ms, etc.).

#### ST0-ST3

Status 0-Status 3. One of the four registers that store status information after a command has been executed. This information is available during the result phase after command execution. These registers must not be confused with the main status register (selected by A0=0). ST0-ST3 are read only after a command has been executed and only if they contains information relevant to the command.

- **STP** Scan Test. If STP=1 during a scan operation, the data in contiguous sectors is compared byte by byte with data sent from the processor (or DMA). If STP=2, alternate sectors are read and compared.

- **US0-1** Unit Select. Selected drive number 0 or 1.

# ACC Micro<sup>™</sup>\_\_\_\_\_

### **Command Format**

The following commands can be issued to the controller. An "x" indicates a "don't care" condition.

#### **READ DATA**

#### **Command Phase**

|        | 7                              | 6               | 5  | 4 | 3 | 2  | 1   | 0   |

|--------|--------------------------------|-----------------|----|---|---|----|-----|-----|

| Byte 0 | MT                             | MF              | SK | 0 | 0 | 1  | 1   | 0   |

| Byte 1 | х                              | х               | х  | х | х | HD | US1 | US0 |

| Byte 2 | Cylinde                        | Cylinder Number |    |   |   |    |     |     |

| Byte 3 | Head Address                   |                 |    |   |   |    |     |     |

| Byte 4 | Sector Number                  |                 |    |   |   |    |     |     |

| Byte 5 | Number of Data Bytes in Sector |                 |    |   |   |    |     |     |

| Byte 6 | End of Track                   |                 |    |   |   |    |     |     |

| Byte 7 | Gap Length                     |                 |    |   |   |    |     |     |

| Byte 8 | Data Length                    |                 |    |   |   |    |     |     |

#### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

# ACC Micro™\_\_\_\_\_

### **READ DELETED DATA**

#### **Command Phase**

|        | 7                              | 6               | 5  | 4 | 3 | 2  | 1   | 0   |

|--------|--------------------------------|-----------------|----|---|---|----|-----|-----|

| Byte 0 | MT                             | MF              | SK | 0 | 1 | 1  | 0   | 0   |

| Byte 1 | х                              | х               | х  | х | х | HD | US1 | US0 |

| Byte 2 | Cylinde                        | Cylinder Number |    |   |   |    |     |     |

| Byte 3 | Head Address                   |                 |    |   |   |    |     |     |

| Byte 4 | Sector Number                  |                 |    |   |   |    |     |     |

| Byte 5 | Number of Data Bytes in Sector |                 |    |   |   |    |     |     |

| Byte 6 | End of Track                   |                 |    |   |   |    |     |     |

| Byte 7 | Gap Length                     |                 |    |   |   |    |     |     |

| Byte 8 | Data Length                    |                 |    |   |   |    |     |     |

#### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

#### **READ A TRACK**

#### **Command Phase**

| Byte 0 | 0                              | MF              | SK | 0 | 0 | 0  | 1   | 0   |

|--------|--------------------------------|-----------------|----|---|---|----|-----|-----|

| Byte 1 | х                              | х               | х  | х | х | HD | US1 | US0 |

| Byte 2 | Cylinde                        | Cylinder Number |    |   |   |    |     |     |

| Byte 3 | Head Address                   |                 |    |   |   |    |     |     |

| Byte 4 | Sector Number                  |                 |    |   |   |    |     |     |

| Byte 5 | Number of Data Bytes in Sector |                 |    |   |   |    |     |     |

| Byte 6 | End of Track                   |                 |    |   |   |    |     |     |

| Byte 7 | Gap Length                     |                 |    |   |   |    |     |     |

| Byte 8 | Data Length                    |                 |    |   |   |    |     |     |

# ACC Micro<sup>™</sup>\_\_\_\_\_

### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

#### **READ ID**

#### **Command Phase**

|        | 7 | 6  | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|---|----|---|---|---|----|-----|-----|

| Byte 0 | 0 | MF | 0 | 0 | 1 | 0  | 1   | 0   |

| Byte 1 | Х | Х  | Х | Х | Х | HD | US1 | US0 |

#### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

### WRITE DATA

#### **Command Phase**

|        | 7                              | 6  | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|--------------------------------|----|---|---|---|----|-----|-----|

| Byte 0 | MT                             | MF | 0 | 0 | 0 | 1  | 0   | 1   |

| Byte 1 | х                              | х  | х | х | х | HD | US1 | US0 |

| Byte 2 | Cylinder Number                |    |   |   |   |    |     |     |

| Byte 3 | Head Address                   |    |   |   |   |    |     |     |

| Byte 4 | Sector Number                  |    |   |   |   |    |     |     |

| Byte 5 | Number of Data Bytes in Sector |    |   |   |   |    |     |     |

| Byte 6 | End of Track                   |    |   |   |   |    |     |     |

| Byte 7 | Gap Length                     |    |   |   |   |    |     |     |

| Byte 8 | Data Length                    |    |   |   |   |    |     |     |

# ACC Micro<sup>™</sup>\_\_\_\_\_

#### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

#### WRITE DELETED DATA Command Phase

|        | 7                              | 6  | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|--------------------------------|----|---|---|---|----|-----|-----|

| Byte 0 | MT                             | MF | 0 | 0 | 1 | 0  | 0   | 1   |

| Byte 1 | х                              | Х  | х | х | х | HD | US1 | US0 |

| Byte 2 | Cylinder Number                |    |   |   |   |    |     |     |

| Byte 3 | Head Address                   |    |   |   |   |    |     |     |

| Byte 4 | Sector Number                  |    |   |   |   |    |     |     |

| Byte 5 | Number of Data Bytes in Sector |    |   |   |   |    |     |     |

| Byte 6 | End of Track                   |    |   |   |   |    |     |     |

| Byte 7 | Gap Length                     |    |   |   |   |    |     |     |

| Byte 8 | Data Length                    |    |   |   |   |    |     |     |

### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

#### FORMAT A TRACK Command Phase

|        | 7                              | 6  | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|--------------------------------|----|---|---|---|----|-----|-----|

| Byte 0 | 0                              | MF | 0 | 0 | 1 | 1  | 0   | 1   |

| Byte 1 | Х                              | х  | Х | Х | Х | HD | US1 | US0 |

| Byte 2 | Number of Data Bytes in Sector |    |   |   |   |    |     |     |

| Byte 3 | Sectors per Cylinder           |    |   |   |   |    |     |     |

| Byte 4 | Gap Length                     |    |   |   |   |    |     |     |

| Byte 5 | Data                           |    |   |   |   |    |     |     |

## ACC Micro™\_\_\_\_\_

## **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

## SCAN EQUAL

## **Command Phase**

|        | 7            | 6               | 5        | 4        | 3 | 2  | 1   | 0   |  |  |  |

|--------|--------------|-----------------|----------|----------|---|----|-----|-----|--|--|--|

| Byte 0 | MT           | MF              | SK       | 1        | 0 | 0  | 0   | 1   |  |  |  |

| Byte 1 | х            | х               | х        | х        | х | HD | US1 | US0 |  |  |  |

| Byte 2 | Cylinde      | Cylinder Number |          |          |   |    |     |     |  |  |  |

| Byte 3 | Head Address |                 |          |          |   |    |     |     |  |  |  |

| Byte 4 | Sector       | Sector Number   |          |          |   |    |     |     |  |  |  |

| Byte 5 | Numbe        | r of Data       | Bytes ir | n Sector |   |    |     |     |  |  |  |

| Byte 6 | End of       | Track           |          |          |   |    |     |     |  |  |  |

| Byte 7 | Gap Le       | Gap Length      |          |          |   |    |     |     |  |  |  |

| Byte 8 | Scan Test    |                 |          |          |   |    |     |     |  |  |  |

## **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

## SCAN LOW OR EQUAL

### **Command Phase**

|        | 7       | 6                  | 5          | 4        | 3 | 2  | 1   | 0   |  |  |  |

|--------|---------|--------------------|------------|----------|---|----|-----|-----|--|--|--|

| Byte 0 | MT      | MT MF SK 1 1 0 0 1 |            |          |   |    |     |     |  |  |  |

| Byte 1 | х       | х                  | х          | х        | х | HD | US1 | US0 |  |  |  |

| Byte 2 | Cylinde | Cylinder Number    |            |          |   |    |     |     |  |  |  |

| Byte 3 | Head A  | Head Address       |            |          |   |    |     |     |  |  |  |

| Byte 4 | Sector  | Number             |            |          |   |    |     |     |  |  |  |

| Byte 5 | Numbe   | r of Data          | ı Bytes ir | n Sector |   |    |     |     |  |  |  |

| Byte 6 | End of  | Track              |            |          |   |    |     |     |  |  |  |

| Byte 7 | Gap Le  | Gap Length         |            |          |   |    |     |     |  |  |  |

| Byte 8 | Scan Te | Scan Test          |            |          |   |    |     |     |  |  |  |

### **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

## SCAN HIGH OR EQUAL

### **Command Phase**

|        | 7                  | 6               | 5          | 4        | 3 | 2  | 1   | 0   |  |  |  |  |

|--------|--------------------|-----------------|------------|----------|---|----|-----|-----|--|--|--|--|

| Byte 0 | MT MF SK 1 1 1 0 1 |                 |            |          |   |    |     |     |  |  |  |  |

| Byte 1 | х                  | х               | х          | х        | х | HD | US1 | US0 |  |  |  |  |

| Byte 2 | Cylinde            | Cylinder Number |            |          |   |    |     |     |  |  |  |  |

| Byte 3 | Head Address       |                 |            |          |   |    |     |     |  |  |  |  |

| Byte 4 | Sector             | Sector Number   |            |          |   |    |     |     |  |  |  |  |

| Byte 5 | Numbe              | r of Data       | a Bytes in | n Sector |   |    |     |     |  |  |  |  |

| Byte 6 | End of             | Track           |            |          |   |    |     |     |  |  |  |  |

| Byte 7 | Gap Le             | Gap Length      |            |          |   |    |     |     |  |  |  |  |

| Byte 8 | Scan Test          |                 |            |          |   |    |     |     |  |  |  |  |

## ACC Micro™\_\_\_\_\_

## **Result Phase**

| Byte 0 | Status Register 0              |

|--------|--------------------------------|

| Byte 1 | Status Register 1              |

| Byte 2 | Status Register 2              |

| Byte 3 | Cylinder Number                |

| Byte 4 | Head Address                   |

| Byte 5 | Sector Number                  |

| Byte 6 | Number of Data Bytes in Sector |

## RECALIBRATE

**Command Phase** (This command has no result phase.)

|        | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|---|---|---|---|---|---|-----|-----|

| Byte 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1   | 1   |

| Byte 1 | Х | Х | Х | Х | Х | 0 | US1 | US0 |

## SENSE INTERRUPT STATUS

### **Command Phase**

|        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

| Byte 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

### **Result Phase**

| Byte 0 | Status Register 0       |

|--------|-------------------------|

| Byte 1 | Present Cylinder Number |

#### Specify

Command Phase (This command has no result phase.)

|        | 7 | 6   | 5   | 4 | 3 | 2   | 1 | 0  |

|--------|---|-----|-----|---|---|-----|---|----|

| Byte 0 | 0 | 0   | 0   | 0 | 0 | 0   | 1 | 1  |

| Byte 1 |   | SRT |     |   |   | HUT |   |    |

| Byte 2 |   |     | HLT |   |   |     |   | ND |

## SENSE DRIVE STATUS

## **Command phase**

|        | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|---|---|---|---|---|----|-----|-----|

| Byte 0 | 0 | 0 | 0 | 0 | 0 | 1  | 0   | 0   |

| Byte 1 | Х | Х | х | х | Х | HD | US1 | US0 |

## ACC Micro™\_\_\_\_\_

## **Result Phase**

| Byte 0 | Status 3 Register |

|--------|-------------------|

## SEEK

**Command Phase** (This command has no result phase.)

|        | 7                            | 6 | 5 | 4 | 3 | 2  | 1   | 0   |

|--------|------------------------------|---|---|---|---|----|-----|-----|

| Byte 0 | 0                            | 0 | 0 | 0 | 1 | 1  | 1   | 1   |

| Byte 1 | Х                            | х | х | х | х | HD | US1 | US0 |

| Byte 2 | New Cylinder Number for Seek |   |   |   |   |    |     |     |

## INVALID

### **Result Phase**

The following status byte is returned to the microprocessor when an invalid command is received.

| Byte 0 Status 0 Register |

|--------------------------|

|--------------------------|

## Floppy Disk Drive Support on Parallel Port

The ACC2087 allows the floppy disk control signals to be multiplex to the parallel port pins for external floppy disk drive support. To enable this function, set Register BEh, bit 2 to one to enable this function. Table 1.0 summarizes the FDC signals which are multiplexed with the parallel port pins.

| FDD Connector Pin # | FDC mode | Parallel Port Mode | Parallel Port<br>Connector Pin # |

|---------------------|----------|--------------------|----------------------------------|

| 32                  | HEAD#    | ERROR#             | 15                               |

| 22                  | WDATA#   | PE                 | 12                               |

| 24                  | WE#      | SLCT               | 13                               |

| 16                  | MOIN#    | BUSY               | 11                               |

| 12                  | DSIN#    | ACK#               | 10                               |

| 2                   | RWC#     | AUTOFD#            | 14                               |

| 18                  | DIR#     | INIT#              | 16                               |

| 20                  | STEP#    | SLIN#              | 17                               |

| 8                   | INDEX#   | PD0                | 2                                |

| 26                  | TRK0#    | PD1                | 3                                |

| 28                  | WD#      | PD2                | 4                                |

| 30                  | RDDATA#  | PD3                | 5                                |

| 34                  | DSKCHG#  | PD4                | 6                                |

The ACC2087 supports two NS16C550 compatible serial ports. Each serial port interface converts data from peripheral devices or modems from serial-in-data to parallel-out-data. Data transmitted from the CPU is converted from parallel-in-data to serial-out-data. The status of the UART can be read during any CPU operation. Status includes type and condition of the transfer operations in progress, and error conditions.

Each serial port interface has three types of internal registers: Control, Status, and Data registers.

## **Control registers**

Bit Rate Select Register DLL (Divisor Latch LSB). Bit Rate Select Register DLM (Divisor Latch MSB). Line Control Register. Interrupt Enable Register. Interrupt Identification Register. FIFO Control Register. Modem Control Register.

## Status registers

Line Status Registers Modem Status Register

## Data registers

Receiver Buffer Register Transmitter Holding Register Scratch Register

Table 1 summarizes the serial port registers.

## Table 1 Serial Port Register Summary

| Register            | Bit 7            | Bit 6            | Bit 5        | Bit 4       | Bit 3                 | Bit 2                  | Bit 1              | Bit 0          |

|---------------------|------------------|------------------|--------------|-------------|-----------------------|------------------------|--------------------|----------------|

| Receiver            | Data             | Data             | Data         | Data        | Data                  | Data                   | Data               | Data           |

| Buffer              | Bit 7 (MSB)      | Bit 6            | Bit 5        | Bit 4       | Bit 3                 | Bit 2                  | Bit 1              | Bit 0 (LSB)    |

| Register            |                  |                  |              |             |                       |                        |                    |                |

| (read only)         |                  |                  |              |             |                       |                        |                    |                |

| Transmitt-er        | Data Bit 7       | Data Bit 6       | Data Bit 5   | Data Bit 4  | Data Bit 3            | Data Bit 2             | Data Bit 1         | Data Bit 0     |

| Holding             |                  |                  |              |             |                       |                        |                    |                |

| Register            |                  |                  |              |             |                       |                        |                    |                |

| (write onl<br>only) |                  |                  |              |             |                       |                        |                    |                |

| Divisor             | Bit 7            | Bit 6            | Bit 5        | Bit 4       | Bit 3                 | Bit 2                  | Bit 1              | Bit 0          |

| Latch (LS)          | Dit /            | DII 0            | BR 5         | DII 4       | DII 5                 | DIL 2                  | DITI               | DIU            |

| Divisor             | Bit 15           | Bit 14           | Bit 13       | Bit 12      | Bit 11                | Bit 10                 | Bit 9              | Bit 8          |