## **ChromaCast**

82C205

LCD Monitor Controller

# Advance Information CONFIDENTIAL

Revision 1.0 912-1000-024 7/8/99

#### Copyright

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, manual, or otherwise, without the prior written permission of OPTi Inc., 1440 McCarthy Blvd. Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

1440 McCarthy Blvd. Milpitas, CA 95035

Tel: (408) 486-8000 Fax: (408) 486-8001

WWW: http://www.opti.com

### **Table of Contents**

| 1. | FE/   | ATUF | RES                                  | 1  |

|----|-------|------|--------------------------------------|----|

| 2. | OV    | ERV  | IEW                                  |    |

|    |       |      |                                      |    |

| 3. |       |      | DEFINITIONS                          |    |

|    | 3.1.  |      | DIAGRAM                              |    |

|    | 3.2.  |      | LISTING                              |    |

| 3  | 3.3.  |      | NAL DESCRIPTIONS                     |    |

|    | 3.3.  |      | Terminology/Nomenclature Conventions |    |

|    | 3.3.  |      | CPU and System Interface             |    |

|    | 3.3.  |      | NTSC/PAL Decoder Interface           |    |

|    | 3.3.  |      | DRAM Interface                       |    |

|    | 3.3.  |      | Panel Interface Signals              |    |

| _  | 3.3.  |      | Power and Ground Signals             |    |

|    | 3.4.  |      | T MODE SIGNALS                       |    |

|    | 3.5.  |      | WER AND GROUND PINS                  |    |

| 3  | 3.6.  |      | NER UP STRAPPING ASSIGNMENTS         |    |

|    | 3.6.  |      | Panel Type                           |    |

|    | 3.6.  |      | Register Base Address Strapping      |    |

| 4. | FUI   |      | ONAL DESCRIPTION                     |    |

| 4  | l.1.  |      | ERNAL BLOCK DIAGRAM                  |    |

| 4  | l.2.  |      | RO-CONTROLLER INTERFACE              |    |

| 4  | l.3.  |      | JT SOURCE                            |    |

| 4  | 1.4.  |      | OMATIC RESOLUTION DETECTION          |    |

| 4  | l.5.  |      | MODE                                 |    |

| 4  | l.6.  | FUL  | L SCALE AND CENTERING OPTIONS        | 16 |

| 4  | l.7.  |      | NTRAST/BRIGHTNESS CONTROL            |    |

| 4  | l.8.  | ON   | SCREEN DISPLAY                       | 16 |

| 4  | l.9.  | DITI | HERING                               | 17 |

| 4  | 1.10. | V    | ERSATILE PANEL SUPPORT               | 17 |

| 4  | 1.11. | С    | CLOCK GENERATION                     | 17 |

| 4  | 1.12. | D    | PRAM INTERFACE                       | 18 |

| 5. | RE    | GIST | ER DESCRIPTIONS                      | 19 |

| 5  | 5.1.  | REV  | /ISION REGISTER                      | 19 |

| 5  | 5.2.  | Sys  | STEM CONTROL REGISTER                | 19 |

### **Advance Information**

### 82C205

|    | 5.3.  | MEMORY CONTROL REGISTERS                  | . 19 |

|----|-------|-------------------------------------------|------|

|    | 5.4.  | OSD REGISTERS                             | . 22 |

|    | 5.5.  | DITHER REGISTER SETTINGS                  | . 23 |

|    | 5.6.  | CAPTURE CRTC REGISTERS                    | . 23 |

|    | 5.7.  | Scaling Registers                         | . 25 |

|    | 5.8.  | CONTRAST AND BRIGHTNESS CONTROL REGISTERS | . 27 |

|    | 5.9.  | VIDEO INPUT SOURCE SELECTION REGISTERS    | . 27 |

|    | 5.10. | RESOLUTION DETECTION REGISTERS            | . 28 |

|    | 5.11. | TV DECODER INTERFACE REGISTERS            | . 29 |

|    | 5.12. | DISPLAY HORIZONTAL SCALING                | . 30 |

|    | 5.13. | DISPLAY CRTC REGISTERS                    | . 30 |

|    | 5.14. | PANEL REGISTERS                           | . 33 |

|    | 5.15. | BANDWIDTH CONSERVATION REGISTERS          | . 34 |

|    | 5.16. | INTERRUPT CONTROL REGISTERS               | . 34 |

|    | 5.17. | CLUT Access Control                       | . 35 |

|    | 5.18. | ADC AND PLL CONTROL REGISTERS             | . 35 |

|    | 5.19. | POWER MANAGEMENT REGISTERS                | . 35 |

|    | 5.20. | CLUT REGISTERS                            | . 36 |

|    | 5.21. | STATUS REGISTERS                          | . 38 |

|    | 5.22. | I/O CONTROL REGISTERS                     | . 39 |

| õ. | TIM   | ING INFORMATION AND WAVEFORMS             | . 40 |

|    | VERTI | CAL TIMING FOR TFT PANEL                  | . 40 |

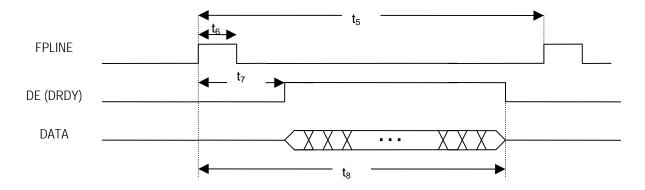

|    | 6.2.  | HORIZONTAL TIMING FOR TFT PANEL           | . 41 |

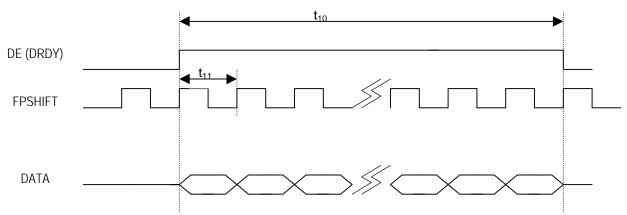

|    | DETAI | OF PIXEL CLOCK TIMING                     | . 41 |

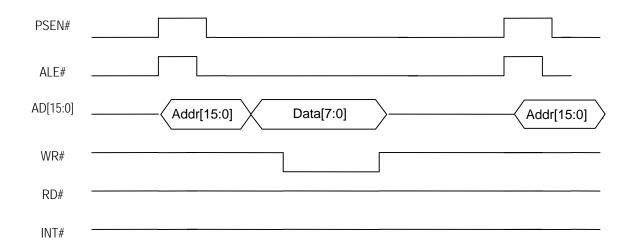

|    | 6.4.  | MICRO-CONTROLLER INTERFACE                | . 41 |

| 7  | ასგ   | -DIN DOED MECHANICAL DRAWING              | 47   |

#### 1. Features

#### **Digital Input Support**

- 24-bit digital input

- 300 Mb/sec data rate

### Full Screen Image Scaling At All Resolutions

Incoming video scaled via high quality interpolation/decimation filters to full panel screen size

#### Multiple LCD Panel Type Support

- 9, 12, 18, 24, 36 bit TFT panel resolution from 640x480 up to 1280x1024

- Drives Single/Multiple Pixels per Clock

- 90 Hz panel refresh rate for TFT

#### Super OSD Support

- 16-color OSD support

- Transparent, translucent, inverted video, and blinking color attribute support

#### Multi-sync support

- Supports incoming video with resolutions from 640x480 up to 1280x1024

- Automatic incoming resolution detection

- Horizontal frequency from 15 to 70 kHz

- Vertical frequency from 40 to 85 Hz

#### Host Interface

• Direct 8-bit micro-controller interface (8051-compatible)

#### **LCD TV Support**

- Direct video decoder interface support for LCD TV applications

- High quality scale up algorithm for TV input

#### **VESA Compliant**

- DPMS for Display Power Management

- FPDI-1 Flat Panel Display Interface

- LVDS and PanelLink transceiver interface for FPDI-2 (24 bpp mode)

#### Electrical/Physical Specification

- 0.35 **m**m process

- 3.3 Volt power supply

- 5V-tolerant I/O

- 208 PQF package

### **Advance Information**

82C205

Page 2 Revision 1.0

#### 2. Overview

This data book describes the ChromaCast 82C205 LCD monitor controller, a cost reduced solution for LCD (liquid crystal display) monitor control from OPTi Inc. The ChromaCast solution supports a 64-bit DRAM interface for data buffering, an 8051-compatible micro-controller interface, a 24-bit digital interface that can be used with an RGB A/D converter, a PanelLink™ receiver, or an NTSC/PAL decoder, and direct drive control for TFT panels.

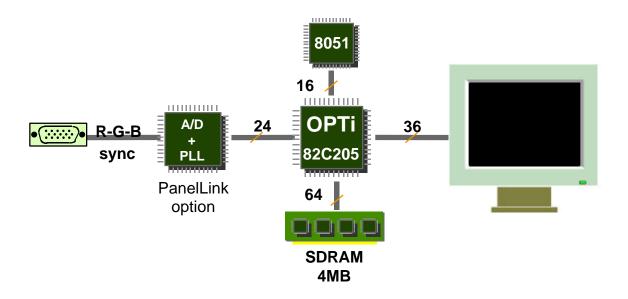

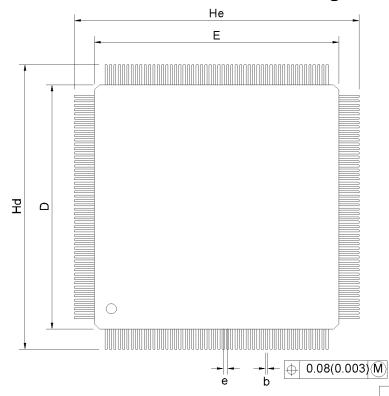

ChromaCast 82C205 is packaged in a 208-pin PQF package. 82C205 is a cost-effective, high-performance universal panel controller. Figure 1 shows a system configuration using the 82C205.

Figure 1. ChromaCast 82C205 System Diagram

912-1000-024 Page 3

### **Advance Information**

82C205

Page 4 Revision 1.0

### 3. Signal Definitions

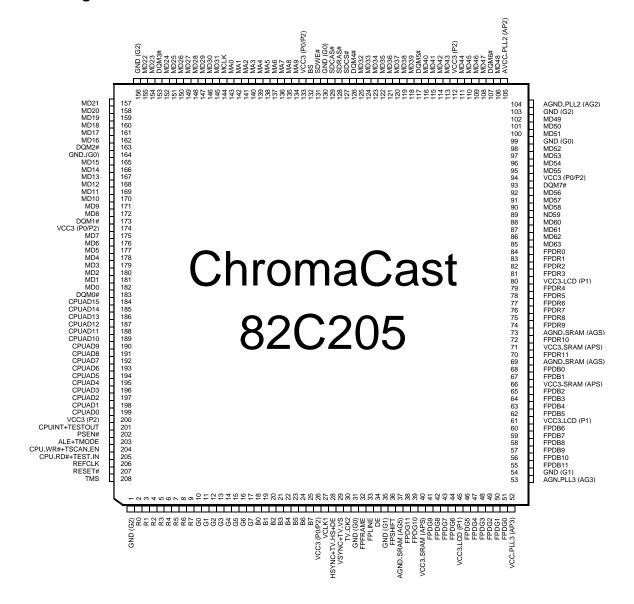

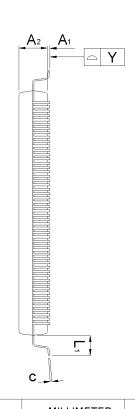

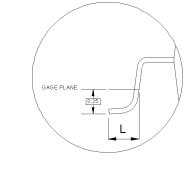

#### 3.1. Pin Diagram

912-1000-024 Page 5

### 3.2. Pin Listing

| Pin<br>No. | Signal Name  |

|------------|--------------|

| 1          | GND (G2)     |

| 2          | R0           |

| 3          | R1           |

| 4          | R2           |

| 5          | R3           |

| 6          | R4           |

| 7          | R5           |

| 8          | R6           |

| 9          | R7           |

| 10         | G0           |

| 11         | G1           |

| 12         | G2           |

| 13         | G3           |

| 14         | G4           |

| 15         | G5           |

| 16         | G6           |

| 17         | G7           |

| 18         | В0           |

| 19         | B1           |

| 20         | B2           |

| 21         | B3           |

| 22         | B4           |

| 23         | B5           |

| 24         | B6           |

| 25         | B7           |

| 26         | VCC3 (P0/P2) |

| 27         | VCLK1        |

| 28         | HSYNC+TV_HS  |

| 29         | VSYNC+TV_VS  |

| 30         | TV_CK2       |

| 31         | GND (G0)     |

| 32         | FPFRAME      |

| 33         | FPLINE       |

| 34         | DE           |

| Pin<br>No. | Signal Name     |

|------------|-----------------|

| 35         | GND (G1)        |

| 36         | FPSHIFT         |

| 37         | AGND_SRAM (AGS) |

| 38         | FPDG11          |

| 39         | FPDG10          |

| 40         | VCC3_SRAM (APS) |

| 41         | FPDG9           |

| 42         | FPDG8           |

| 43         | FPDG7           |

| 44         | FPDG6           |

| 45         | VCC3_LCD (P1)   |

| 46         | FPDG5           |

| 47         | FPDG4           |

| 48         | FPDG3           |

| 49         | FPDG2           |

| 50         | FPDG1           |

| 51         | FPDG0           |

| 52         | VCC3_PLL3 (AP3) |

| 53         | AGND_PLL3 (AG3) |

| 54         | GND (G1)        |

| 55         | FPDB11          |

| 56         | FPDB10          |

| 57         | FPDB9           |

| 58         | FPDB8           |

| 59         | FPDB7           |

| 60         | FPDB6           |

| 61         | VCC3_LCD (P1)   |

| 62         | FPDB5           |

| 63         | FPDB4           |

| 64         | FPDB3           |

| 65         | FPDB2           |

| 66         | VCC3_SRAM (APS) |

| 67         | FPDB1           |

| 68         | FPDB0           |

| Pin<br>No. | Signal Name     |

|------------|-----------------|

| 69         | AGND_SRAM (AGS) |

| 70         | FPDR11          |

| 71         | VCC3_SRAM (APS) |

| 72         | FPDR10          |

| 73         | AGND_SRAM (AGS) |

| 74         | FPDR9           |

| 75         | FPDR8           |

| 76         | FPDR7           |

| 77         | FPDR6           |

| 78         | FPDR5           |

| 79         | FPDR4           |

| 80         | VCC3_LCD (P1)   |

| 81         | FPDR3           |

| 82         | FPDR2           |

| 83         | FPDR1           |

| 84         | FPDR0           |

| 85         | MD63            |

| 86         | MD62            |

| 87         | MD61            |

| 88         | MD60            |

| 89         | MD59            |

| 90         | MD58            |

| 91         | MD57            |

| 92         | MD56            |

| 93         | DQM7#           |

| 94         | VCC3 (P0/P2)    |

| 95         | MD55            |

| 96         | MD54            |

| 97         | MD53            |

| 98         | MD52            |

| 99         | GND (G0)        |

| 100        | MD51            |

912-1000-024

Page 6 Revision 1.0

| Pin<br>No. | Signal Name     |

|------------|-----------------|

| 101        | MD50            |

| 102        | MD49            |

| 103        | GND (G2)        |

| 104        | AGND_PLL2 (AG2) |

| 105        | AVCC_PLL2 (AP2) |

| 106        | MD48            |

| 107        | DQM6#           |

| 108        | MD47            |

| 109        | MD46            |

| 110        | MD45            |

| 111        | MD44            |

| 112        | VCC3 (P2)       |

| 113        | MD43            |

| 114        | MD42            |

| 115        | MD41            |

| 116        | MD40            |

| 117        | DQM5#           |

| 118        | MD39            |

| 119        | MD38            |

| 120        | MD37            |

| 121        | MD36            |

| 122        | MD35            |

| 123        | MD34            |

| 124        | MD33            |

| 125        | MD32            |

| 126        | DQM4#           |

| 127        | SDCS#           |

| 128        | SDRAS#          |

| 129        | SDCAS#          |

| 130        | GND (G0)        |

| 131        | SDWE#           |

| 132        | BS              |

| 133        | VCC3 (P0/P2)    |

| 134        | MA9             |

| 135        | MA8             |

| 136        | MA7             |

| Pin<br>No. | Signal Name |

|------------|-------------|

| 137        | MA6         |

| 138        | MA5         |

| 139        | MA4         |

| 140        | MA3         |

| 141        | MA2         |

| 142        | MA1         |

| 143        | MA0         |

| 144        | MCLK        |

| 145        | MD31        |

| 146        | MD30        |

| 147        | MD29        |

| 148        | MD28        |

| 149        | MD27        |

| 150        | MD26        |

| 151        | MD25        |

| 152        | MD24        |

| 153        | DQM3#       |

| 154        | MD23        |

| 155        | MD22        |

| 156        | GND (G2)    |

| 157        | MD21        |

| 158        | MD20        |

| 159        | MD19        |

| 160        | MD18        |

| 161        | MD17        |

| 162        | MD16        |

| 163        | DQM2#       |

| 164        | GND (G0)    |

| 165        | MD15        |

| 166        | MD14        |

| 167        | MD13        |

| 168        | MD12        |

| 169        | MD11        |

| 170        | MD10        |

| 171        | MD9         |

| 172        | MD8         |

| Pin<br>No. | Signal Name      |

|------------|------------------|

| 173        | DQM1#            |

| 174        | VCC3 (P0/P2)     |

| 175        | MD7              |

| 176        | MD6              |

| 177        | MD5              |

| 178        | MD4              |

| 179        | MD3              |

| 180        | MD2              |

| 181        | MD1              |

| 182        | MD0              |

| 183        | DQM0#            |

| 184        | CPUAD15          |

| 185        | CPUAD14          |

| 186        | CPUAD13          |

| 187        | CPUAD12          |

| 188        | CPUAD11          |

| 189        | CPUAD10          |

| 190        | CPUAD9           |

| 191        | CPUAD8           |

| 192        | CPUAD7           |

| 193        | CPUAD6           |

| 194        | CPUAD5           |

| 195        | CPUAD4           |

| 196        | CPUAD3           |

| 197        | CPUAD2           |

| 198        | CPUAD1           |

| 199        | CPUAD0           |

| 200        | VCC3 (P2)        |

| 201        | CPUINT+TESTOUT   |

| 202        | PSEN#            |

| 203        | ALE+TMODE        |

| 204        | CPU_WR#+TSCAN_EN |

| 205        | CPU_RD#+TEST_IN  |

| 206        | REFCLK           |

| 207        | RESET#           |

| 208        | TMS              |

#### 3.3. Signal Descriptions

#### 3.3.1. Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term "assert", or "assertion", indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term "negate", or "negation", indicates that a signal is inactive.

#### 3.3.2. CPU and System Interface

| Signal Name              | Pin<br>No.      | Signal<br>Type | Signal Description                                                                                                                                                                                                |

|--------------------------|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU_RD#<br>TEST_IN       | 205             | I              | CPU active low read strobe when TMS=0. Test Input for Nand Tree and Tri-state tests when TMS=1                                                                                                                    |

| CPU_WR#<br>TSCAN_EN      | 204             | I              | CPU active low write strobe when TMS=0. Reserved Input for tests when TMS=1                                                                                                                                       |

| ALE+TMODE                | 203             | I              | CPU Address latch enable. ChromaCast latches address from CPU address/data bus at negative edge of ALE. When TMS=1, TMODE selects between NAND tree and tri-state testing (see Section 3.4, "Test Mode Signals"). |

| CPUAD_[15:5] CPUAD_[7:0] | 190<br>-<br>199 | I<br>I/O       | CPU address/data bus bits [15:0] Low Byte ([7:0]) is multiplexed data and the lower address byte. Upper Byte (15:8) is upper address byte.                                                                        |

| CPUINT +<br>TESTOUT      | 201             | 0              | CPU active low interrupt when TMS=0. Test Output for Nand Tree and Tri-state Tests when TMS=1                                                                                                                     |

| RESET#                   | 207             | I              | ChromaCast System Reset (active low). The minimum RESET time is 1ms, i.e. the RESET signal should stays active for at least 1ms after power is stabilized.                                                        |

| REFCK                    | 206             | I              | Reference Clock. 14.318 MHz reference clock driven externally.  This same 14MHz clock must be used to drive the external microcontroller.                                                                         |

| PSEN#                    | 202             | I              | Program strobe enable. Active low signal indicates that the CPU needs to fetch a progarm instruction.                                                                                                             |

| TMS                      | 208             | I              | Test Mode Select – Sets test mode at power-up (see Secton 3.4, "Test Mode Signals").  TMS=0: Normal operation TMS=1: Test mode                                                                                    |

Page 8 Revision 1.0

#### 3.3.3. NTSC/PAL Decoder Interface

| Signal Name    | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                 |

|----------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R[7:0]         | 2-9        | I              | Digital Red Input                                                                                                                                                                  |

| G[7:0]         | 10-<br>17  | I              | Digital Green Input  OR – Digital Luminance Data input for 16-bit NTSC/PAL Decoder Interface or Digital Luminance and Chrominance Data input for 8-bit NTSC/PAL Decoder Interface. |

| B[7:0]         | 18-<br>25  | I              | Digital Blue Input  OR – Digital Chrominance Data input for 16-bit NTSC/PAL Decoder Interface.                                                                                     |

| VCLK1          | 27         | I              | Video Capture Clock from external line-locked PLL                                                                                                                                  |

| TV_CK2         | 30         | I              | Clock from the NTSC/PAL Decoder.                                                                                                                                                   |

| HSYNC<br>TV_HS | 28         | I              | Horizontal Sync signal from VGA  – OR –  HREF signal from NTSC/PAL Decoder                                                                                                         |

| VSYNC          | 29         | I              | Vertical Sync signal from VGA  – OR –                                                                                                                                              |

| TV_VS          |            |                | Odd/Even flag from NTSC/PAL Decoder.                                                                                                                                               |

#### 3.3.4. DRAM Interface

| Signal Name | Pin<br>No.  | Signal<br>Type | Signal Description                                           |

|-------------|-------------|----------------|--------------------------------------------------------------|

| DQM#[7:0]   | 93,         | 0              | Data Mask (DQM) for SDRAM.                                   |

|             | 107,        |                |                                                              |

|             | 117,        |                |                                                              |

|             | 126,        |                |                                                              |

|             | 153,        |                |                                                              |

|             | 163,        |                |                                                              |

|             | 173,<br>183 |                |                                                              |

|             |             | _              |                                                              |

| BS          | 132         | 0              | SDRAM Bank Select (Active low)                               |

| MCLK        | 144         | I/O            | Memory clock for Memory Controller and SDRAM.                |

|             |             |                | Internal MCK PLL or External oscillator provides this clock. |

| MD[63:0]    | See         | I/O            | Memory data bus (64-bit).                                    |

|             | Sec         |                |                                                              |

|             | 3.1         |                |                                                              |

| MA[9:0]     | 134         | 0              | Memory address bus signals.                                  |

|             | -           |                |                                                              |

|             | 143         |                |                                                              |

| SDRAS#      | 128         | 0              | SDRAM RAS (Active Low)                                       |

| SDCAS#      | 129         | 0              | SDRAM CAS (Active Low)                                       |

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description             |

|-------------|------------|----------------|--------------------------------|

| SDCS#       | 127        | 0              | SDRAM Chip Select (Active Low) |

|             |            |                | EDO RAS (Active Low)           |

| SDWE#       | 131        | 0              | Write Enable (Active Low)      |

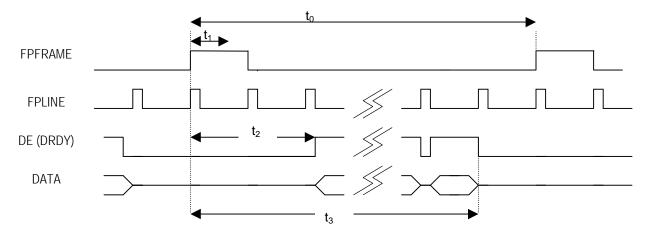

### 3.3.5. Panel Interface Signals

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                                        |

|-------------|------------|----------------|-------------------------------------------------------------------------------------------|

| FPFRAME     | 32         | 0              | Flat panel FRAME signal. Analogous to vertical sync. Programmable polarity.               |

| FPLINE      | 33         | 0              | Flat panel line signal. Analogous to horizontal sync. Programmable polarity.              |

| FPSHIFT     | 36         | 0              | Shift clock. Analogous to pixel clock. Shift Clock can be programmed to be gated by DE.   |

| DE          | 34         | 0              | Panel enable (data ready) signal for display. Also known as DRDY.                         |

| FPDR[11:0]  | 70-<br>83  | 0              | Flat Panel Red Display Data for TFT Mode (See Section 3.3.6.1 below for complete mapping) |

| FPDG[11:0]  | 39-<br>57  | 0              | Flat Panel Green Display Data (See Section 3.3.6.1 below for complete mapping)            |

| FPDB[11:0]  | 55-<br>68  | 0              | Flat Panel Blue Display Data (See Section 3.3.6.1 below for complete mapping)             |

### 3.3.6. Power and Ground Signals

| Signal Name        | Pin<br>No.       | Signal<br>Type | Signal Description                                               |

|--------------------|------------------|----------------|------------------------------------------------------------------|

| VCC3 (P0/P2)       | 26,              | Р              | Core power plane. Also supplies I/O power for CPU, YUV and DRAM. |

|                    | 94,<br>112,      |                |                                                                  |

|                    | 133,             |                |                                                                  |

|                    | 174,             |                |                                                                  |

|                    | 200              |                |                                                                  |

| VCC_SRAM           | 40,              | Р              | SRAM power plane                                                 |

| (APS)              | 66,<br>71        |                |                                                                  |

| VCC DILA           |                  | Ъ              | DLL2 nower plans                                                 |

| VCC_PLL2<br>(AP2)  | 105              | Р              | PLL2 power plane                                                 |

| VCC3_PLL3<br>(AP3) | 52               | Р              | PLL3 power plane                                                 |

| VCC3_LCD<br>(P1)   | 45,<br>61,<br>80 | Р              | Power plane for LCD                                              |

Page 10 Revision 1.0

| Signal Name        | Pin<br>No.                       | Signal<br>Type | Signal Description                |

|--------------------|----------------------------------|----------------|-----------------------------------|

| AGND_SRAM<br>(AGS) | 37,<br>69,<br>73                 | Р              | Analog ground for SRAM            |

| AGND_PLL2<br>(AG2) | 104                              | Р              | Analog ground for PLL2            |

| AGND_PLL3<br>(AG3) | 53                               | Р              | Analog ground for PLL3            |

| GND (G0)           | 31,<br>99,<br>130,<br>164        | G              | Digital ground for core plane     |

| GND<br>(G1 and G2) | 1,<br>35,<br>54,<br>103,<br>156, | G              | Digital ground for all I/O planes |

### 3.3.6.1. TFT Panel Data Pin Mapping

(O: pixel#1,3,5...; E: pixel#2,4,6...)

| Mode      | Red (O)   | Red (E)     | Green (O) | Green (E)   | Blue (O)  | Blue (E)    |

|-----------|-----------|-------------|-----------|-------------|-----------|-------------|

| A-333-S09 | FPDR[7:5] |             | FPDG[7:5] |             | FPDB[7:5] |             |

| A-333-S18 | FPDR[7:5] | FPDR[15:13] | FPDG[7:5] | FPDG[15:13] | FPDB[7:5] | FPDB[15:13] |

| A-444-S12 | FPDR[7:4] |             | FPDG[7:4] |             | FPDB[7:4] |             |

| A-444-S24 | FPDR[7:4] | FPDR[15:12] | FPDG[7:4] | FPDG[15:12] | FPDB[7:4] | FPDB[15:12] |

| A-666-S18 | FPDR[7:2] |             | FPDG[7:2] |             | FPDB[7:2] |             |

| A-666-S36 | FPDR[7:2] | FPDR[15:10] | FPDG[7:2] | FPDG[15:10] | FPDB[7:2] | FPDB[15:10] |

| A-888-S24 | FPDR[7:0] |             | FPDG[7:0] |             | FPDB[7:0] |             |

### 3.4. Test Mode Signals

| Signal Name | Pin<br>No. | Signal<br>Type | Signal                                       | Description  |                                           |  |  |

|-------------|------------|----------------|----------------------------------------------|--------------|-------------------------------------------|--|--|

| TMS         | 208        | I              | Test M                                       | lode Select  | <ul> <li>Sets mode at power-up</li> </ul> |  |  |

|             |            |                | TMS                                          | TMODE        | Operation Mode                            |  |  |

|             |            |                | 0                                            | 0            | Normal                                    |  |  |

|             |            |                | 0                                            | 1            | Reserved                                  |  |  |

|             |            |                | 1                                            | 0            | NAND-tree operation                       |  |  |

|             |            |                | 1                                            | 1            | Tri-state operation                       |  |  |

| TESTIN      | 205        | I              | Test Input for Nand Tree and Tri-state tests |              |                                           |  |  |

| TESTOUT     | 201        | 0              | Test O                                       | utput for Na | nd Tree and Tri-state Tests               |  |  |

### 3.5. Power and Ground Pins

| Signal Name        | Pin<br>No.       | Signal<br>Type |

|--------------------|------------------|----------------|

| GND (G0)           | 31               | G              |

| GND (G0)           | 99               | G              |

| GND (G0)           | 130              | G              |

| GND (G0)           | 164              | G              |

| GND (G1)           | 35               | G              |

| GND (G1)           | 54               | G              |

| GND (G2)           | 1                | G              |

| GND (G2)           | 103              | G              |

| GND (G2)           | 156              | G              |

| AGND_SRAM<br>(AGS) | 37,<br>69,<br>73 | G              |

| Signal Name        | Pin<br>No. | Signal<br>Type |

|--------------------|------------|----------------|

| AGND_PLL2<br>(AG2) | 104        | G              |

| AGND_PLL3<br>(AG3) | 53         | G              |

| VCC3 (P0/P2)       | 26         | Р              |

| VCC3 (P0/P2)       | 94         | Р              |

| VCC3 (P0/P2)       | 133        | Р              |

| VCC3 (P0/P2)       | 174        | Р              |

| VCC3 (P2)          | 112        | Р              |

| VCC3 (P2)          | 200        | Р              |

| VCC3_LCD (P1)      | 45         | Р              |

| VCC3_LCD (P1)      | 61         | Р              |

| Signal Name        | Pin<br>No. | Signal<br>Type |

|--------------------|------------|----------------|

| VCC3_LCD (P1)      | 80         | Р              |

| AVCC_PLL2<br>(AP2) | 105        | Ρ              |

| VCC3_PLL3<br>(AP3) | 52         | Р              |

| VCC3_SRAM<br>(APS) | 40         | Р              |

| VCC3_SRAM<br>(APS) | 66         | Р              |

| VCC3_SRAM<br>(APS) | 71         | Р              |

Page 12 Revision 1.0

### 3.6. Power Up Strapping Assignments

### 3.6.1. Panel Type

| Signal Name | Signal Description                                                                                    |

|-------------|-------------------------------------------------------------------------------------------------------|

| MD[9:6]     | At power-up, these pins strap the panel type. A $4.7 \text{K}\Omega$ resistor to ground represents 0. |

|             | 0000 = Reserved                                                                                       |

|             | 0001 = Reserved                                                                                       |

|             | 0010 = Reserved                                                                                       |

|             | 0100 = A333-S09                                                                                       |

|             | 0101 = A444-S12                                                                                       |

|             | 0110 = A666-S18                                                                                       |

|             | 0111 = A888-S24                                                                                       |

|             | 1000 = A333-S18                                                                                       |

|             | 1001 = A444-S24                                                                                       |

|             | 1010 = A666-S36                                                                                       |

|             | 1011 = Reserved                                                                                       |

|             | 1100 = Reserved                                                                                       |

|             | 1101 = Reserved                                                                                       |

|             | 1110 = Reserved                                                                                       |

|             | 1111 = Reserved                                                                                       |

### 3.6.2. Register Base Address Strapping

| Signal Name | Signal Description                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MD[5:0]     | At power-up, these pins strap a portion of the register base address for ChromaCast's register file, which corresponds to address bits [13:8] of the micro-controller bus. The setting 01h is not allowed due to a conflict with the CLUT BASE default. |  |  |  |  |  |  |

|             | Bit <u>5 4 3 2 1 0 Operation</u>                                                                                                                                                                                                                        |  |  |  |  |  |  |

|             | 0 0 0 0 0 Fixed address at 8000h                                                                                                                                                                                                                        |  |  |  |  |  |  |

|             | 0 0 0 0 1 Relocate Address to 8100h                                                                                                                                                                                                                     |  |  |  |  |  |  |

|             |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|             |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|             | 1 1 1 1 1 Relocate Address to BF00h                                                                                                                                                                                                                     |  |  |  |  |  |  |

|             |                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

### **Advance Information**

82C205

Page 14 Revision 1.0

#### 4. Functional Description

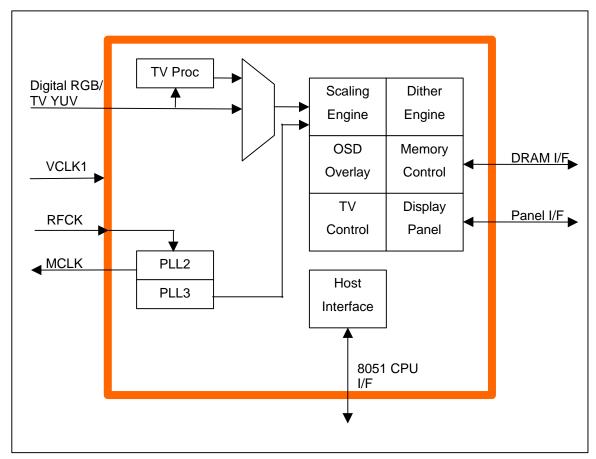

#### 4.1. Internal Block Diagram

Figure 2. ChromaCast Internal Block Diagram

#### 4.2. Micro-Controller Interface

The 82C205 interfaces to the popular 8051-compatible micro-controller with a shared 16-bit address and data bus (8-bit). The 82C205 provides the micro-controller with one interrupt source, which can be used by the programmer to monitor the status of the 82C205.

The micro-controller can access the registers of the 82C205, the Color Look-Up Table (CLUT), and the DRAM frame buffer. Since the internal address of the frame buffer is 22 bits wide, the 82C205 uses a bank switching technique in order to allow the micro-controller access to the entire memory address space.

#### 4.3. Input Source

The 82C205 supports 24-bit digital input. This 24-bit digital input port can be connected to a TV decoder, external ADC and PanelLink™ receiver. The 82C205 can also generate its own internal test patterns and syncs that can be used for system integration tests.

912-1000-024 Page 15

#### 4.4. Automatic Resolution Detection

The 82C205 monitors the horizontal and vertical syncs from the VGA and performs automatic polarity detection, as well as determination of the horizontal sync frequency and the incoming image resolution. Changes in the horizontal sync frequency and the input image resolution can be configured to prompt an interrupt when these changes occur. The micro-controller can then read the system status and then re-program the 82C205 appropriately.

A fully programmable capture CRTC can be adjusted by the programmer to align with incoming data, based upon the status information that the 82C205 provides.

#### 4.5. TV Mode

The 82C205 chip can be used to turn the LCD monitor into a TV monitor. If the system design for the monitor includes a TV input and NTSC/PAL decoder, then the 82C205 can enable the flat panel to display television signals. Both 16- and 8-bit interfaces to TV decoders are supported, which offers the designer the flexibility of using a less expensive decoder. The 82C205 requires an ODD/EVEN flag as its vertical sync, and the HREF signal as its horizontal sync.

#### 4.6. Full Scale and Centering Options

Scaling is always an important issue for multi-sync monitors, so the 82C205 uses high quality filters to perform image scaling, both horizontally and vertically. Even low resolution images, such as the output from a TV decoder, can be displayed at the full panel resolution. A "centering" option also allows for a smaller resolution image to be displayed on a larger panel with its original resolution surrounded by a black border.

#### 4.7. Contrast/Brightness Control

Contrast and brightness are adjusted digitally on the 82C205, with built in clamping to prevent overflow and underflow. The contrast and brightness controls exist for each color component separately (R-G-B), so color weighting can also be performed by adjusting the contrast of each component to give a component a certain weight relative to the other color components.

$R_o$  =  $R_i$  \* Contrast<sub>R</sub> + Brightness<sub>R</sub>  $G_o$  =  $G_i$  \* Contrast<sub>G</sub> + Brightness<sub>G</sub>  $B_o$  =  $B_i$  \* Contrast<sub>B</sub> + Brightness<sub>B</sub>

#### 4.8. On Screen Display

The 82C205 supports 8 color OSD. Using the attribute control of the 82C205, the programmer is able to build onscreen menus with transparency, translucency, video inversion, and blinking special effects.

The OSD region on the display is defined as a rectangular region. The rectangular region's size and location on the display are controlled by programmable registers, so the OSD can be of any size, and be located at any coordinate on the display.

The micro-controller writes the bitmap data for the rectangular OSD region to a DRAM buffer. The OSD data in the DRAM buffer contains a 4-bit index into a Color Look Up Table (CLUT) register which is internal to the 82C205 and is also programmable by the micro-controller.

The CLUT contains 16 entries each using 6 bits to describe a 3-bit RGB color value, a 2-bit attribute value to control the overlay graphics, and a 1-bit alpha blend value to control the global alpha value or translucency of the of the overlay graphics. Figure 3 illustrates the organization of the CLUT.

| Bit[5] | Bit[4] | Bit[3] | Bits[2:1] | Bit[0] |

|--------|--------|--------|-----------|--------|

| Red    | Green  | Blue   | Overlay   | α      |

Figure 3. CLUT contents

A global alpha is defined for the entire table, and each entry is tagged with an alpha-blend flag. Inverted video, transparent and blinking attributes are also supported in this mode.

Using the alpha blend value, the OSD graphics can be composited with the video stream controlled by a blend factor in order to create a translucent effect. Pixels in the defined rectangular OSD region that the programmer wishes to be "blank" graphics, i.e. the underlying video is clearly visible, can attach the "transparent" attribute to the OSD pixel. The formula used to control alpha blending is as follows:

Output = Video \*

$$(1-\alpha)$$

+ OSD \*  $(\alpha)$

Attributes further expand the OSD effects, with an invert attribute (which inverts the video data) and a blink attribute, which performs a hardware controlled blink using a programmable blink rate.

#### 4.9. Dithering

Some flat panels do not provide a 24-bit "true color" interface, so the challenge is to achieve the effect of true color when the panel itself supports less than a full color display. OPTi uses an advanced dithering technique which delivers a true color effect on all display types.

#### 4.10. Versatile Panel Support

The 82C205 is configurable to support a wide range of active matrix displays with resolutions of 640 x 480, 800 x 600, 1024 x 768, and 1280 x 1024 pixels. TFT displays with 9-, 12-, 18-, and 24-bits per pixel are supported. 82C205 also supports multiple pixels per clock and provides a 36-bit interface for panel support.

The synchronization signals to the flat panel are controlled by a fully programmable display CRTC. Positive and negative polarity syncs are supported. In addition to the horizontal and vertical syncs, and the pixel clock for the panel, a data ready (DE) signal is also provided for TFT displays

#### 4.11. Clock Generation

82C205 contains two internal PLLs that are used to generate the clocks necessary for operation. In addition to these two clocks, which control the video processing unit and the memory subsystem, the 14.318 Mhz reference clock is also used internally. This 14.319Mhz same as the system clock for the micro-controller interface.

- PLL2 (MCK) uses the 14.318 MHz reference clock to generate the clock for the memory controller. This clock frequency should match the speed of the DRAM. For SDRAM, a 100 MHz clock is recommended.

- PLL3 (VCLK2) uses the 14.318 MHz reference clock to generate the display clock for the video processing unit. This is also the clock that will be used to drive the panel and its frequency is closely linked to the panel specifications.

#### **Advance Information**

82C205

#### 4.12. DRAM Interface

82C205 contains an integrated memory controller that supports 64-bit SDRAM. There is also a bypass mode available for some TFT panels that can be used to eliminate the need for a frame buffer, but at the cost of reduced functionality, such as loss of the TV support option.

Page 18 Revision 1.0

### 5. Register Descriptions

### 5.1. Revision Register

| 7         | 6             | 5                 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|---------------|-------------------|---|---|---|---|---|--|--|--|

| Index 00h |               | Chip Revision (R) |   |   |   |   |   |  |  |  |

|           | Chip Revision |                   |   |   |   |   |   |  |  |  |

### 5.2. System Control Register

| 7         | 6                        | 5                   | 4                   | 3                                       | 2                   | 1                        | 0                        |  |  |  |

|-----------|--------------------------|---------------------|---------------------|-----------------------------------------|---------------------|--------------------------|--------------------------|--|--|--|

| Index 01h |                          |                     | System Er           | able (R/W)                              |                     |                          | Default = 00h            |  |  |  |

| Reserved  | Reserved                 | Reserved            | Reserved            | Add one clock<br>for CPU<br>read/write: | CPU DRAM<br>Access: | Video Display<br>Control | Video Capture<br>Control |  |  |  |

|           |                          |                     |                     |                                         | 0: Enable           | 0: Disable               | 0: Disable               |  |  |  |

|           |                          |                     |                     | 0: Enable                               | 1: Disable          | 1: Enable                | 1: Enable                |  |  |  |

|           |                          |                     |                     | 1: Disable                              |                     |                          |                          |  |  |  |

| Index 02h | 02h Software Reset (R/W) |                     |                     |                                         |                     |                          |                          |  |  |  |

|           | These                    | e software resets a | allow the CPU flexi | bility for debug and                    | d power down fund   | ctions.                  |                          |  |  |  |

|           |                          | The default value   | e is zero and softw | are reset is unnec                      | essary at startup   |                          |                          |  |  |  |

| Reserved  | Reserved                 | Capture             | Display Reset:      | Reserved                                | Memory              | Reserved                 | Timer Reset:             |  |  |  |

| Reset:    | Reset:                   | 0: Normal           |                     | Controller                              |                     | 0: Normal                |                          |  |  |  |

|           |                          | 0: Normal           | 1: Reset            |                                         | Reset:              |                          | 1: Reset the             |  |  |  |

|           |                          | 1: Reset            |                     |                                         | 0: Normal           |                          | timer                    |  |  |  |

|           |                          |                     |                     |                                         | 1: Reset            |                          |                          |  |  |  |

### 5.3. Memory Control Registers

| 7         | 6                                                      | 5                                                             | 4                  | 3                  | 2                | 1      | 0             |  |

|-----------|--------------------------------------------------------|---------------------------------------------------------------|--------------------|--------------------|------------------|--------|---------------|--|

| Index 04h |                                                        | Capt                                                          | ure Start Addres   | s - Field 1 (R/W)  |                  |        | Default = 00h |  |

|           |                                                        | Starting add                                                  | ress for Video Cap | oture Field 1 Lov  | / Byte           |        |               |  |

| Index 05h |                                                        |                                                               |                    |                    |                  |        | Default = 00h |  |

|           |                                                        | Starting addre                                                | ess for Video Capt | ure Field 1 Midd   | le Byte          |        |               |  |

| Index 06h |                                                        |                                                               |                    |                    |                  |        | Default = 00h |  |

| Reserved  | Reserved                                               | Reserved Starting address for Video Capture Field 1 High Byte |                    |                    |                  |        |               |  |

| Index 07h |                                                        | Capt                                                          | ure Start Addres   | s - Field 2 (R/W)  |                  |        | Default = 00h |  |

|           |                                                        | Starting add                                                  | ress for Video Cap | oture Field 2 Lov  | / Byte           |        |               |  |

| Index 08h |                                                        |                                                               |                    |                    |                  |        | Default = 00h |  |

|           | Starting address for Video Capture Field 2 Middle Byte |                                                               |                    |                    |                  |        |               |  |

| Index 09h |                                                        |                                                               |                    |                    |                  |        | Default = 00h |  |

| Reserved  | Reserved                                               |                                                               | Starting add       | ress for Video Cap | ture Field 2 Hig | h Byte |               |  |

912-1000-024 Page 19

| 7                                    | 6                                                     | 5                  | 4                    | 3                   | 2                  | 1   | 0                |  |  |  |

|--------------------------------------|-------------------------------------------------------|--------------------|----------------------|---------------------|--------------------|-----|------------------|--|--|--|

| Index 0Ah -0Ch                       |                                                       |                    | Reserve              | ed                  |                    |     | Default = 00h    |  |  |  |

| Index 0Dh                            |                                                       |                    | OSD Start Addr       | ess (R/W)           |                    |     | Default = 00h    |  |  |  |

|                                      |                                                       | Starting           | address of OSD In    | dex Buffer Low By   | te                 |     |                  |  |  |  |

| Index 0Eh                            |                                                       |                    |                      |                     |                    |     | Default = 00h    |  |  |  |

|                                      |                                                       | Starting a         | ddress of OSD Ind    | ex Buffer Middle E  | syte               |     |                  |  |  |  |

| Index 0Fh                            |                                                       |                    |                      |                     |                    |     | Default = 00h    |  |  |  |

| Reserved                             | Reserved                                              |                    | Starting a           | address of OSD In   | dex Buffer High By | /te |                  |  |  |  |

| Index 10h                            | Index 10h Display Panel Start Address – Field 1 (R/W) |                    |                      |                     |                    |     |                  |  |  |  |

|                                      |                                                       |                    | arting address for   |                     |                    |     |                  |  |  |  |

|                                      |                                                       | This is the start  | ing address for fie  |                     | GA data.           |     |                  |  |  |  |

|                                      |                                                       |                    | Low Byt              | e                   |                    |     | Default = 00h    |  |  |  |

| Index 11h                            |                                                       |                    |                      |                     |                    |     |                  |  |  |  |

|                                      |                                                       |                    | Middle By            | /te                 |                    |     | D - (   4   00 - |  |  |  |

| Index 12h Reserved                   | Reserved                                              |                    |                      | Lliah Du            |                    |     | Default = 00h    |  |  |  |

| Index 13h                            | Reserved                                              | Dienley            | Danal Start Addr     | High By             |                    |     | Default = 00h    |  |  |  |

| index 13ff                           |                                                       |                    | Panel Start Addr     |                     | v)                 |     | Delault = 0011   |  |  |  |

|                                      |                                                       |                    | starting address for |                     | data.              |     |                  |  |  |  |

|                                      |                                                       |                    | Low Byt              |                     |                    |     |                  |  |  |  |

| Index 14h                            |                                                       |                    | ·                    |                     |                    |     | Default = 00h    |  |  |  |

|                                      |                                                       |                    | Middle By            | /te                 |                    |     |                  |  |  |  |

| Index 15h                            |                                                       |                    |                      |                     |                    |     | Default = 00h    |  |  |  |

| Reserved                             | Reserved                                              |                    |                      | High Byt            | e                  |     |                  |  |  |  |

| Index 16h                            |                                                       |                    | Video Pitch          | (R/W)               |                    |     | Default = 00h    |  |  |  |

|                                      |                                                       |                    | Pitch of the Fran    | ne Buffer.          |                    |     |                  |  |  |  |

|                                      |                                                       |                    | Low Byt              | е                   |                    |     |                  |  |  |  |

| Index 17h                            |                                                       |                    |                      |                     |                    |     | Default = 00h    |  |  |  |

| Reserved                             | Reserved                                              | Reserved           |                      |                     | High Byte          |     |                  |  |  |  |

| Index 18h - 19h                      |                                                       |                    | Reserve              | ed                  |                    |     | Default = 00h    |  |  |  |

| Index 1Ah                            |                                                       |                    | OSD Pitch            | (R/W)               |                    |     | Default = 00h    |  |  |  |

|                                      |                                                       |                    | Pitch of the OSD I   | ndex Buffer         |                    |     |                  |  |  |  |

| Low Byte                             |                                                       |                    |                      |                     |                    |     |                  |  |  |  |

| Index 1Bh                            |                                                       |                    | <u> </u>             |                     |                    |     | Default = 00h    |  |  |  |

| Reserved                             | Reserved                                              | Reserved           |                      |                     | High Byte          |     |                  |  |  |  |

| Index 1Ch                            |                                                       |                    | Memory Ban           |                     |                    |     | Default = 00h    |  |  |  |

| Bank Address for DRAM access by CPU. |                                                       |                    |                      |                     |                    |     |                  |  |  |  |

|                                      |                                                       | The CPU address is |                      |                     | ory address is:    |     |                  |  |  |  |

|                                      |                                                       | Honor cost         | bank[7:0], cpu_a     |                     | hanke              |     |                  |  |  |  |

|                                      |                                                       | nence, each        | oank is 16Kbytes,    | willi 200 available | Datiks.            |     |                  |  |  |  |

Page 20 Revision 1.0

| 7               | 6           | 5                                                                                                                          | 4                 | 3                   | 2                     | 1                 | 0                                               |

|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|-----------------------|-------------------|-------------------------------------------------|

| Index 1Dh       |             |                                                                                                                            | Sequencer Con     | trol (R/W)          | •                     | •                 | Default = 20h                                   |

| Reserved        | Reserved    | Arbiter Client<br>Acknowledge<br>Overlap:                                                                                  | Reserved          | Reserved            | Reserved              | Reserved          | Reserved                                        |

|                 |             | This bit should be set to 1 (default) for optimal memory performance. It allows for greater throughput for internal client |                   |                     |                       |                   |                                                 |

|                 |             | requests.                                                                                                                  |                   |                     |                       |                   |                                                 |

| Index 1Eh       |             |                                                                                                                            | Refresh Rate Co   | ntrol (R/W)         |                       |                   | Default = FFI                                   |

|                 | Numbe       | er of reference clock cy                                                                                                   | cles between refr | esh requests (f =   | 14.318Mhz, T = 70     | ns).              |                                                 |

|                 | The duratio | n between refresh rec                                                                                                      |                   |                     | m refresh interval fo | or a row.         |                                                 |

|                 |             |                                                                                                                            | Low By            | te                  |                       |                   |                                                 |

| Index 1Fh       |             |                                                                                                                            |                   |                     |                       |                   | Default = FF                                    |

|                 |             |                                                                                                                            | High By           | te                  |                       |                   |                                                 |

| Index 20h - 21h |             |                                                                                                                            | Reserve           | ed                  |                       |                   | Default = 00                                    |

| Index 22h       |             |                                                                                                                            | SDRAM Contro      | ol 0 (R/W)          |                       |                   | Default = 00                                    |

| Reserved        | Reserved    | Reserved                                                                                                                   | Reserved          | CAS<br>Latency = 3: | SDRAM Burst           | SDRAM Burst       | Length:                                         |

|                 |             |                                                                                                                            |                   | 0: Disable          | Type: 0: Sequential   | 00: Burst I       | ŭ                                               |

|                 |             |                                                                                                                            |                   | 1: Enable           | 1: Interleave         | 01: Burst I       | ŭ                                               |

|                 |             |                                                                                                                            |                   | 1. Lilabic          | 1. Interieuve         | 10: Burst I       | J                                               |

|                 |             |                                                                                                                            |                   |                     |                       | 11: Burst I       |                                                 |

| Index 23h       |             |                                                                                                                            | Reserve           |                     |                       |                   | Default = 00                                    |

| Index 24h       | ı           | T                                                                                                                          | CLUT Base Add     |                     |                       |                   | Default = 01                                    |

| Reserved        | Reserved    |                                                                                                                            |                   | lor Look Up Table   |                       |                   |                                                 |

|                 |             | This                                                                                                                       | 6-bit value corre |                     | 8] of the micro-cor   | ntroller address. |                                                 |

|                 |             |                                                                                                                            | (DEOF             | Default :           |                       | `                 |                                                 |

|                 |             |                                                                                                                            |                   |                     | be strapped to '1'.   | )                 |                                                 |

| Index 25h       |             |                                                                                                                            | TV Weave Mo       |                     |                       | T .               | Default = 00                                    |

| Reserved        | Reserved    | Reserved                                                                                                                   | Reserved          | Reserved            | Reserved              | Reserved          | TV Weave<br>Mode<br>Capture<br>Pitch<br>Adjust: |

|                 |             |                                                                                                                            |                   |                     |                       |                   | 0: Enable                                       |

|                 |             |                                                                                                                            |                   |                     |                       |                   | 1: Disable<br>(See note                         |

|                 |             |                                                                                                                            |                   |                     |                       |                   | below.)                                         |

|                 |             | ure Pitch to twice the Vimage in an interlea                                                                               |                   |                     |                       | eave mode. TV     | Weave mode                                      |

|                 |             |                                                                                                                            | CDI I Mamaru Bas  | al Duffer (D)       |                       |                   | D ( 1/ 00                                       |

| Index 26h       |             | •                                                                                                                          | CPU Memory Rea    | ia Butter (K)       |                       |                   | Default = 00                                    |

| 7         | 6                                                             | 5                                        | 4                   | 3                 | 2                  | 1 | 0             |  |  |  |

|-----------|---------------------------------------------------------------|------------------------------------------|---------------------|-------------------|--------------------|---|---------------|--|--|--|

| Index 27h |                                                               | Arbiter State (R)                        |                     |                   |                    |   |               |  |  |  |

|           | This register can be used to detect a lock-up of the arbiter. |                                          |                     |                   |                    |   |               |  |  |  |

|           | For debug purposes only.                                      |                                          |                     |                   |                    |   |               |  |  |  |

| Reserved  | Reserved                                                      | Reserved                                 |                     | Ar                | biter State Status |   |               |  |  |  |

| Index 28h |                                                               |                                          | Sequencer S         | tate (R)          |                    | ı | Default = 00h |  |  |  |

|           |                                                               | This register can be                     | used to detect a lo | ck-up of the memo | ory sequencer.     |   |               |  |  |  |

|           | For debug purposes only.                                      |                                          |                     |                   |                    |   |               |  |  |  |

| Reserved  | Reserved                                                      | Reserved Reserved Sequencer State Status |                     |                   |                    |   |               |  |  |  |

### 5.4. OSD Registers

| 7         | 6                                                           | 5                                                                                                            | 4                     | 3                    | 2                                                                                            | 1                                            | 0              |

|-----------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------|

| Index 29h |                                                             |                                                                                                              | OSD Configu           | ıration (R/W)        |                                                                                              |                                              | Default = 00h  |

| Reserved  | Reserved                                                    | Reserved                                                                                                     | Reserved              | Reserved             | OSD Blink Background Select: 0: Blink to Video Background 1: Blink to CLUT Index0 Background | OSD function: 0: Disable (default) 1: Enable | Reserved       |

| Index 2Ah |                                                             | 0                                                                                                            | SD Window Hori        | zontal Offset (R/V   | V)                                                                                           |                                              | Default = 00h  |

| Horiz     | contal Offset for the                                       | al Offset for the rectangular OSD region referenced from the far left of the display and in units of display |                       |                      |                                                                                              |                                              | xels.          |

|           |                                                             |                                                                                                              | Low                   | Byte                 |                                                                                              |                                              |                |

| Index 2Bh |                                                             | 0                                                                                                            | SD Window Horiz       | zontal Offset (R/V   | V)                                                                                           |                                              | Default = 00h  |

| Reserved  | Reserved                                                    | Reserved                                                                                                     | Reserved              | Reserved             |                                                                                              | High Byte                                    |                |

| Index 2Ch |                                                             |                                                                                                              | OSD Horizon           | tal Size (R/W)       |                                                                                              |                                              | Default = 00h  |