# Intelligent Network Controller for Embedded System **S1S60000**Technical Manual

# NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material of ute to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from anther government agency. ©SEIKO EPSON CORPORATION 2002, All rights reserved. All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

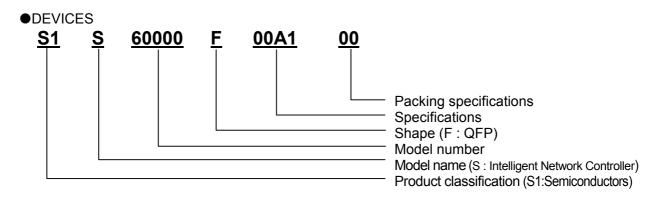

### The information of the product number change

Starting April 1, 2001 the product number has been changed as listed below. Please use the new product number when you place an order. For further information, please contact Epson sales representative.

### Configuration of product number

### **CONTENTS**

| 1. | . DESCRIPTION |                                               |    |  |  |  |  |  |  |  |

|----|---------------|-----------------------------------------------|----|--|--|--|--|--|--|--|

|    | 1.1           | Features                                      | 1  |  |  |  |  |  |  |  |

|    | 1.2           | Key Specifications                            | 1  |  |  |  |  |  |  |  |

|    | 1.3           | Block Diagram                                 | 2  |  |  |  |  |  |  |  |

|    | 1.4           | Pin Description                               | 3  |  |  |  |  |  |  |  |

|    |               | 1.4.1 Pin Layout                              | 3  |  |  |  |  |  |  |  |

|    |               | 1.4.2 Pin Functions                           | 4  |  |  |  |  |  |  |  |

|    |               | 1.4.2.1 Pin in Power Supply System            | 4  |  |  |  |  |  |  |  |

|    |               | 1.4.2.2 Host Interface Signals                | 4  |  |  |  |  |  |  |  |

|    |               | 1.4.2.3 MII Interface Signals                 | 5  |  |  |  |  |  |  |  |

|    |               | 1.4.2.4 External Device Control Signals       | 6  |  |  |  |  |  |  |  |

|    |               | 1.4.2.5 General Purpose Input and Output Pins | 7  |  |  |  |  |  |  |  |

|    |               | 1.4.2.6 Clock Generator Pins                  | 7  |  |  |  |  |  |  |  |

|    |               | 1.4.2.7 Other Pins                            | 9  |  |  |  |  |  |  |  |

| 2. | HAF           | RDWARE SPECIFICATIONS                         | 10 |  |  |  |  |  |  |  |

|    | 2.1           |                                               |    |  |  |  |  |  |  |  |

|    |               | 2.1.1 ROM and Boot Address                    |    |  |  |  |  |  |  |  |

|    |               | 2.1.2 RAM                                     |    |  |  |  |  |  |  |  |

|    | 2.2           | Peripheral Circuits                           |    |  |  |  |  |  |  |  |

|    | 2.3           | •                                             |    |  |  |  |  |  |  |  |

|    |               | 2.3.1 Hardware Control Mode                   |    |  |  |  |  |  |  |  |

|    |               | 2.3.2 Serial Emulation Mode                   |    |  |  |  |  |  |  |  |

|    | 2.4           | Power Supply                                  | 12 |  |  |  |  |  |  |  |

|    |               | 2.4.1 Operating Voltage                       |    |  |  |  |  |  |  |  |

|    | 2.5           | Power on Reset                                | 12 |  |  |  |  |  |  |  |

|    | 2.6           | OSC3 Clock                                    | 13 |  |  |  |  |  |  |  |

| 3. | NFT           | TWORK INTERFACE                               | 14 |  |  |  |  |  |  |  |

| ٥. | 3.1           | MII Interface                                 |    |  |  |  |  |  |  |  |

|    | 3.2           |                                               |    |  |  |  |  |  |  |  |

|    |               |                                               |    |  |  |  |  |  |  |  |

|    |               | Communication Mode                            |    |  |  |  |  |  |  |  |

|    |               |                                               |    |  |  |  |  |  |  |  |

| 4. |               | ST INTERFACE                                  |    |  |  |  |  |  |  |  |

|    |               | Control Signals                               |    |  |  |  |  |  |  |  |

|    | 4.2           | Host Interface Port                           |    |  |  |  |  |  |  |  |

|    |               | 4.2.2 Status Port                             |    |  |  |  |  |  |  |  |

|    |               | 4.2.3 Data Port                               |    |  |  |  |  |  |  |  |

|    |               |                                               |    |  |  |  |  |  |  |  |

|    | 4.3           | 4.2.4 Flag PortHost Interface Type            |    |  |  |  |  |  |  |  |

|    | 4.3           | • •                                           |    |  |  |  |  |  |  |  |

|    | 4.4           | • •                                           |    |  |  |  |  |  |  |  |

|    |               | · ·                                           |    |  |  |  |  |  |  |  |

| 5. |               | RDWARE CONTROL                                |    |  |  |  |  |  |  |  |

|    | 5.1           | Control Approach                              |    |  |  |  |  |  |  |  |

|    |               | 5.1.1 Control from Network                    | 28 |  |  |  |  |  |  |  |

|    |     | 5.1.2    | Control from Host Interface                   | 31 |

|----|-----|----------|-----------------------------------------------|----|

|    |     | 5.1.3    | Control from External I <sup>2</sup> C Master | 31 |

|    |     | 5.1.4    | Control from Serial Interface                 | 31 |

|    | 5.2 | Built-in | Registers                                     | 34 |

|    |     | 5.2.1    | REVID                                         | 35 |

|    |     | 5.2.2    | MAC0,MAC1,MAC2                                | 35 |

|    |     | 5.2.3    | GENCR                                         | 36 |

|    |     | 5.2.4    | HIFCR                                         | 37 |

|    |     | 5.2.5    | I2CSADR                                       | 37 |

|    |     | 5.2.6    | 12CCONF                                       | 38 |

|    |     | 5.2.7    | GPALT                                         | 39 |

|    |     | 5.2.8    | GPCFG                                         | 40 |

|    |     | 5.2.9    | GPDAT                                         | 40 |

|    |     | 5.2.10   | GPMSK                                         | 40 |

|    |     | 5.2.11   | EPMSK                                         | 41 |

|    |     | 5.2.12   | I2CMSK                                        | 41 |

|    |     | 5.2.13   | PMWAIT                                        | 41 |

|    |     | 5.2.14   | PHYMODE                                       | 42 |

|    |     | 5.2.15   | ANEGR                                         | 43 |

|    |     | 5.2.16   | IPADRH,IPADRL                                 | 44 |

|    |     | 5.2.17   | SNMSKH,SNMSKL                                 | 44 |

|    |     | 5.2.18   | DGWH,DGWL                                     | 44 |

|    |     | 5.2.19   | DADRnH,DADRnL                                 | 44 |

|    |     | 5.2.20   | PORT                                          | 44 |

|    |     | 5.2.21   | DPORT                                         | 44 |

|    |     | 5.2.22   | SERMODE                                       | 45 |

|    |     | 5.2.23   | TM OUT                                        | 45 |

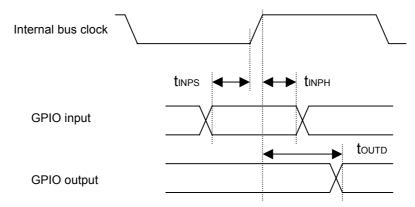

|    | 5.3 | GPIO     |                                               | 46 |

|    | 5.4 | I2C      |                                               | 47 |

|    |     | 5.4.1    | Master Function                               | 47 |

|    |     | 5.4.2    | Slave Function                                | 49 |

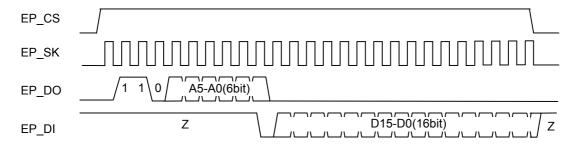

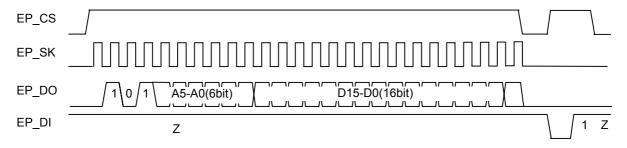

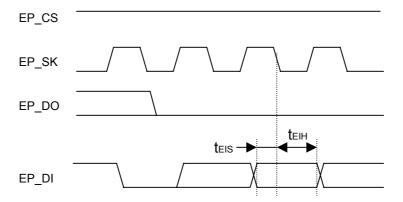

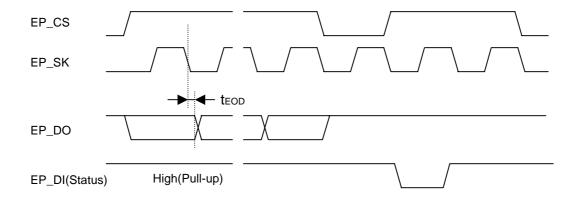

|    | 5.5 | EEPRO    | DM                                            | 52 |

|    |     | 5.5.1    | EEPROM Specification                          | 52 |

|    |     | 5.5.2    | Data Stored                                   |    |

|    |     | 5.5.3    | Transmission/Receiving Format                 |    |

|    |     | 5.5.4    | Automatic Read                                |    |

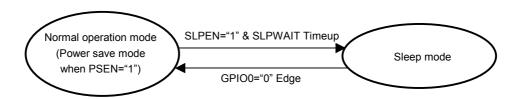

| 6. | POV | VER MA   | NAGEMENT CONTROL                              |    |

| 7. |     |          | ONS ON IMPLEMENTATION                         |    |

| 8. | ELE |          | CHARACTERISTICS                               |    |

|    | 8.1 | Absolut  | te Maximum Rating                             | 56 |

|    | 8.2 | Recom    | mended Operating Conditions                   | 56 |

|    | 8.3 | DC Cha   | aracteristics                                 | 57 |

|    | 8.4 | Current  | t consumption                                 | 57 |

|    | 8.5 |          | aracteristics                                 |    |

|    |     | 8.5.1    | Description of Symbols                        | 57 |

|    |     |          | AC Characteristics Measuring Condition        |    |

|    |     |          | AC Characteristics Table                      |    |

|    |     |          |                                               |    |

|    |      | 8.5.4 | AC Characteristics Timi | ning Chart | 59 |

|----|------|-------|-------------------------|------------|----|

|    | 8.6  |       |                         |            |    |

|    |      |       |                         |            |    |

| 9. | PAC  | KAGE  | <b>:</b>                |            | 64 |

| ΑP | PENI | DIX A | REFERENCE CIRCUIT       | ·          | 65 |

| AΡ | PENI | DIX B | LIST OF PIN CHARACT     | TERISTICS  | 68 |

**EPSON** iii

### 1. DESCRIPTION

S1S60000 is an intelligent network controller equipped with the built-in protocol processing function. Simplified commands and data from the host MPU enables S1S60000 to establish TCP/IP communication thanks to its capability of internally processing protocols for TCP/IP connection including ARP, ICMP, IP, TCP and UDP. MII (Media Independent Interface) is employed for interfacing the physical layer. Just adding PHY chip designed for MII allows you to realize 10BASE-T/100BASE-TX equipment operable on networks. S1S60000 is one of the network controllers best suited for converting your 8/16 bits MPU-featured equipment to ones workable on network without resorting to a high performance OS or protocol stacks provided by software vendors. It enables to establish direct connection with various types of CPUs without using additional logic circuits.

There is no trouble in using it on equipment not provided with a general-purpose bus or external bus such as PCI and ISA.

### 1.1 Features

- Internally processes protocols for up to L4 layer of OSI model.

- Realizes network connection with simple command operations.

- Eliminates license costs thanks to the unique protocol stack.

- General purpose I/O pins and I<sup>2</sup>C bus allows simpler hardware control without resorting to a host MPU.

- Allows adding or changing the protocols used through rewriting of the Flash ROM.

### 1.2 Key Specifications

• Protocol supported ARP, ICMP, IP, TCP, UDP, HTTP, DHCP, TFTP and SNMP.

• Interface with physical layer Media Independent Interface (Complied with Clause 22 of IEEE802.3)

10Base-T/Full duplex, 10Base-T/Half duplex and 100Base-TX/Half duplex

(100Base-TX/Half duplex is not supported)

• Effective transfer rate Approximately 2Mbps maximum.

• Host interface 8/16 bits parallel

• Directly connectable Includes SH-3/4, EPSON S1C33, MC68000, MC68030, Philips

type PR31500/PR31700, Toshiba TX3912, NEC VR4121, PC Card (PCMCIA) and

ISA.

• Endian Switching between little and big is possible.

• Host command system EPSON Standard Code for Network

• General purpose I/O 16 maximum (Directly controllable from the network. 8 out of 16 are shared

with the serial interface.)

•EEPROM I/F

• I<sup>2</sup>C bus

3-wire and 16-bit I/F compatible with 93C46/56/66 (partially usable by user)

Master function (Multi-master and 10bit slave supported. Fast/Normal

mode.)and slave function contained.

Core CPU

Built-in Flash ROM

Power supply

EPSON S1C33240 50MHz

128KB (1KB×128 blocks)

+3.3V, (TBD)mA(Max.)

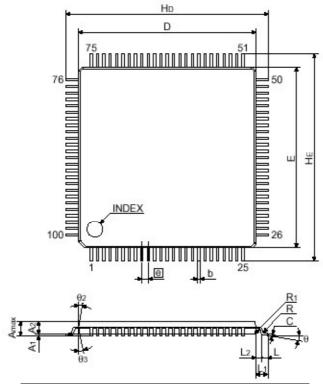

• Package QFP15-100pin

S1S60K series (EPSON Network Controller for Embedded System)is the general name for the network ICs equipped with the built-in protocol stack. S1S60000 is the first product of S1S60K series.

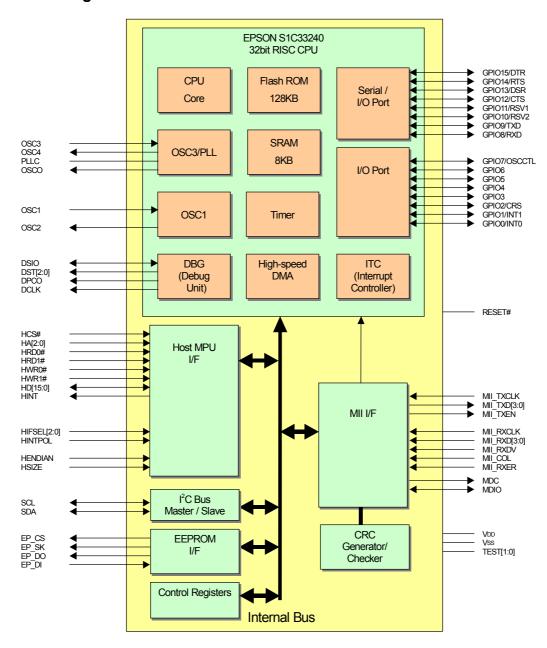

### 1.3 Block Diagram

Figure 1.1 S1S60000 Block Diagram

### 1.4 Pin Description

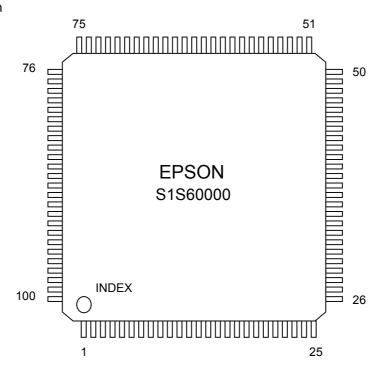

## **1.4.1 Pin Layout** QFP15-100pin

| No. | Pin name     | No. | Pin name  | No. | Pin name | No. | Pin name |

|-----|--------------|-----|-----------|-----|----------|-----|----------|

| 1   | GPIO15/DTR   | 26  | MII_COL   | 51  | HA2      | 76  | Reserve  |

| 2   | GPIO14/RTS   | 27  | MII_TXD3  | 52  | Vss      | 77  | Reserve  |

| 3   | GPIO13/DSR   | 28  | MII_TXD2  | 53  | HD0      | 78  | HIFSEL0  |

| 4   | GPIO12/CTS   | 29  | MII_TXD1  | 54  | HD1      | 79  | VDD      |

| 5   | GPIO11/RSV1  | 30  | MII_TXD0  | 55  | HD2      | 80  | PLLC     |

| 6   | GPIO10/MODE  | 31  | MII_TXEN  | 56  | HD3      | 81  | TEST0    |

| 7   | GPIO9/TXD    | 32  | VDD       | 57  | HD4      | 82  | HIFSEL1  |

| 8   | GPIO8/RXD    | 33  | MII_TXCLK | 58  | HD5      | 83  | HIFSEL2  |

| 9   | Vss          | 34  | MII_RXER  | 59  | HD6      | 84  | Reserve  |

| 10  | GPIO7/OSCCTL | 35  | MII_RXCLK | 60  | HD7      | 85  | HINTPOL  |

| 11  | GPIO6        | 36  | MII_RXDV  | 61  | VDD      | 86  | TEST1    |

| 12  | GPIO5        | 37  | MII_RXD0  | 62  | HD8      | 87  | OSC4     |

| 13  | GPIO4        | 38  | MII_RXD1  | 63  | HD9      | 88  | Vss      |

| 14  | GPIO3        | 39  | MII_RXD2  | 64  | HD10     | 89  | OSC3     |

| 15  | GPIO2/CRS    | 40  | MII_RXD3  | 65  | HD11     | 90  | VDD      |

| 16  | GPIO1        | 41  | MDC       | 66  | HD12     | 91  | RESET#   |

| 17  | GPIO0/INT0   | 42  | MDIO      | 67  | HD13     | 92  | HENDIAN  |

| 18  | VDD          | 43  | OSC2      | 68  | HD14     | 93  | HSIZE    |

| 19  | EP_CS        | 44  | VDD       | 69  | HD15     | 94  | OSCO     |

| 20  | EP_SK        | 45  | Vss       | 70  | Vss      | 95  | DSIO     |

| 21  | EP_DI        | 46  | OSC1      | 71  | HRD0#    | 96  | DST0     |

| 22  | EP_DO        | 47  | VDD       | 72  | HRD1#    | 97  | DST1     |

| 23  | SCL          | 48  | HCS#      | 73  | HWR0#    | 98  | DST2     |

| 24  | SDA          | 49  | HA0       | 74  | HWR1#    | 99  | DPCO     |

| 25  | Vss          | 50  | HA1       | 75  | HINT     | 100 | DCLK     |

Figure 1.2 Pin Layout

### 1.4.2 Pin Functions

Following describes pins used on S1S60000. Symbol "#" added to a signal name indicates it a negative logic. Notations such as "[15:0]" indicate that the subject signal comprises two or more signal lines. For details of respective pins, refer to Appendix B List of Pin Characteristics.

### 1.4.2.1 Pin in Power Supply System

Table 1.1 List of Pins used in Power Supply System

| Pin name | Pin No.              | I/O | Function                                          |

|----------|----------------------|-----|---------------------------------------------------|

| VDD      | 18,32,44,47,61,79,90 | _   | Built-in logic power supply (+)                   |

|          |                      |     | Power pins. Be sure to supply +3.3V to every pin. |

| Vss      | 9,25,45,52,70,88     | _   | Power supply (-) GND                              |

|          |                      |     | Grounding pins. Be sure to ground every pin.      |

### 1.4.2.2 Host Interface Signals

It is the interface used to connect the host CPU. Every input pin including I/O contains a pull-up resister enabling 5V input of HCS#, HA [2:0], HD [15:0], HRD0#, HRD1#, HWR0# and HWR1#. The output is 3.3V CMOS 3-state output.

Table 1.2 List of Host Interface Signals

| Pin name    | Pin No.              | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCS#        | 48                   | I   | Host Chip Select: It is the host interface access control signal. Access to the host interface is enabled as long as this signal remains low. This pin has a built-in pull-up resister enabling to accept 5V input.                                                                                                                                                                                                                                                                       |

| HA[2:0]     | 51,50,49             | I   | Host Address: It is the host interface port select signal. It selects the port to be accessed while HCS# = Low. Following shows the selectable ports.  00x: Command port (write)/Status port (read)  01x: Data port (read/write)  1xx: Flag port (read only)  These pins contain the pull-up resister enabling to accept 5V input.  * HA0 is used for switching between the upper and lower bytes when the 8-bit interface is selected. It is disabled when the 16-bit interface is used. |

| HD[15:0]    | 69 to62,<br>60 to 53 | I/O | Host Data: Data signal line of the host interface. When the 8-bit interface is selected, HDATA [7:0] alone is enabled and HDATA [15:8] is not driven. These pins contain the pull-up resister enabling to accept 5V input. Output is 3.3V CMOS output.                                                                                                                                                                                                                                    |

| HRD0#       | 71                   | I   | Host Read/Host Write:  R/W control signal of the host interface. Its function varies depending                                                                                                                                                                                                                                                                                                                                                                                            |

| HRD1#       | 72                   | I   | on status of HIFSEL [2:0]. For the detail, refer to "4. Host Interface".                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HWR0#       | 73                   | I   | These pins contain the pull-up resister enabling to accept 5V input.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HWR1#       | 74                   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

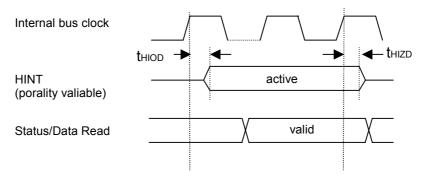

| HINT        | 75                   | Tri | Host Interrupt: Interrupt line from S1S60000 to the host interface. Causes of interrupts are identifiable from contents of the flag port. Polarity of the interrupt is changeable by changing state of HINTPOL line at the reset. Since this signal is 3.3V/3-state output, be sure to externally connect a pull-up resister when HINTPOL=0 and a pull down resister when HINTPOL=1.                                                                                                      |

| HIFSEL[2:0] | 83,82,78             | I   | Host Interface Select: It is the host interface type select signal. These pins contain the pull-up resister. For the detail, refer to "4. Host Interface".                                                                                                                                                                                                                                                                                                                                |

| Pin name | Pin No. | I/O | Function                                                                                                                                                                                                                                                                                                      |

|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HINTPOL  | 85      | I   | Host Interrupt Polarity Select: It is the polarity select pin for HRQI and HDVI when they are active. 1:High active, 0:Low active State of this pin is acquired to HIFCR at reset. This pin contains the pull-up resister.                                                                                    |

| HENDIAN  | 92      | I   | Host Interface Endian Select: It is the endian type select pin. Appropriately selecting the type for a given MPU allows switching the upper/lower data on the command or status port.  1:Big Endian, 0:Little Endian State of this pin is acquired to HIFCR at reset. This pin contains the pull-up resister. |

| HSIZE    | 93      | ı   | Host Bus Size Select: It is the interface size select pin. It is used to specify the data bus size when accessing the port. 1:8bit, 0:16bit State of this pin is acquired to HIFCR at reset. This pin contains the pull-up resister.                                                                          |

### 1.4.2.3 MII Interface Signals

Table 1.3 List of MII Interface Signals

| Pin name     | Pin No.  | I/O | Function                                                                                                                                                                                                                                 |

|--------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII_RXCLK    | 35       | I   | MII Receive Clock: Receiving clock entered from PHY chip. It is the reference clock of MII_RXD [3:0], MII_RXDV. Its frequency is 2.5MHz for 10Base-T and 25MHz for 100Base-TX.                                                           |

| MII_RXD[3:0] | 40 to 37 | I   | MII Receive Data: Receive data entered from PHY chip.                                                                                                                                                                                    |

| MII_RXDV     | 36       | I   | MII Receive Data Valid: Input signal from PHY chip. If it is high at the positive going edge of MII_RXCLK, MII_RXD [3:0] is valid.                                                                                                       |

| MII_TXCLK    | 33       | I   | MII Transmit Clock: Transmit clock entered from PHY chip. It is the reference clock of MII_TXD [3:0], MII_TXEN. Its frequency is 2.5MHz for 10Base-T and 25MHz for 100Base-TX.                                                           |

| MII_TXD[3:0] | 27 to 30 | 0   | MII Transmit Data:<br>Transmit data output to PHY chip.                                                                                                                                                                                  |

| MII_TXEN     | 31       | 0   | MII Transmit Enable: Output signal to PHY chip. If it is high at the positive going edge of MII_TXCLK, MII_TXD[3:0] is valid.                                                                                                            |

| MII_RXER     | 34       | I   | MII Receive Error: Input signal from PHY chip. This signal indicates that receive data contained an error. It is valid on 100Base-TX alone and ignored on 10Base-T.                                                                      |

| MII_COL      | 26       | I   | MII Collision Detect: It indicates that collision of signals occurred during half duplex communication.                                                                                                                                  |

| MDC          | 41       | 0   | MII Management Interface Clock: It is the clock used to set up function of PHY chip as well as control it and read its status. This signal is output from S1S60000. MDIO pin sends or receives data in synchronization with this signal. |

| Pin name  | Pin No. | I/O | Function                                                                |

|-----------|---------|-----|-------------------------------------------------------------------------|

| MDIO      | 42      | I/O | MII Management Interface Data I/O                                       |

|           |         |     | This data is used to set up function of PHY chip as well as control it  |

|           |         |     | and read its status. Data for the function setup and control of PHY     |

|           |         |     | chip is sent from this pin to PHY chip in synchronization with MDC.     |

|           |         |     | When reading status of PHY chip, data from PHY chip is read from        |

|           |         |     | this pin in synchronization with MDC.                                   |

|           |         |     | This pin must be connected to a pull-up resister externally.            |

| GPIO2/CRS | 15      | I   | MII Carrier Sense                                                       |

|           |         |     | When the alternate function of GPIO2 is selected, this pin functions as |

|           |         |     | CRS input pin to enter state of the carrier in half-duplex              |

|           |         |     | communication. It is not used when half-duplex communication is         |

|           |         |     | not employed.                                                           |

### 1.4.2.4 External Device Control Signals

Table 1.4 External Device Control Pins

| Pin name | Pin No. | I/O  | Function                                                                                                                      |

|----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------|

| EP_CS    | 19      | 0    | EEPROM Chip Select:                                                                                                           |

|          |         |      | It is the EEPROM chip select pin.                                                                                             |

| EP_SK    | 20      | 0    | EEPROM Serial Clock:                                                                                                          |

|          |         |      | It is the EEPROM clock pin.                                                                                                   |

| EP_DI    | 21      | I    | EEPROM Data In:                                                                                                               |

|          |         |      | It is the EEPROM data input pin.                                                                                              |

| EP_DO    | 22      | 0    | EEPROM Data Out:                                                                                                              |

|          |         |      | It is the EEPROM data output pin.                                                                                             |

| SCL      | 23      | OD/I | I <sup>2</sup> C Serial Clock:                                                                                                |

|          |         |      | I <sup>2</sup> C bus serial clock pin. When the master is selected, it is input                                               |

|          |         |      | signal and it becomes output signal when the slave is selected.                                                               |

|          |         |      | Since output of this pin is open drain, a pull-up resister must be                                                            |

|          |         |      | provided externally. Select an optimum pull-up resister value taking                                                          |

|          |         | 05"  | into consideration of load on the bus as well as noises.                                                                      |

| SDA      | 24      | OD/I |                                                                                                                               |

|          |         |      | I <sup>2</sup> C bus data input/output pin. It is a bi-directional signal used to                                             |

|          |         |      | input or output data and ACK.                                                                                                 |

|          |         |      | Since output of this pin is open drain, a pull-up resister must be                                                            |

|          |         |      | provided externally. Select an optimum pull-up resister value taking into consideration of load on the bus as well as noises. |

|          |         |      | into consideration or load on the bus as well as noises.                                                                      |

### 1.4.2.5 General Purpose Input and Output Pins

Table 1.5 List of General Purpose Input and Output Pins

| Pin name     | Pin No. | I/O | Function                                                                                      |

|--------------|---------|-----|-----------------------------------------------------------------------------------------------|

| GPIO0/INT0   | 17      | I/O |                                                                                               |

| GPIO1        | 16      | I/O | I/O General Purpose I/O [7:0]:                                                                |

| GPIO2/CRS    | 15      | I/O | General-purpose input/output pin. They accept 5V input. GPIO0 and 1 are used as the interrupt |

| GPIO3        | 14      | I/O | pin to send interrupt notice to a previously specified destination.                           |

| GPIO4        | 13      | I/O | GPIO2 is used as CRS input pin in half-duplex communication.                                  |

| GPIO5        | 12      | I/O | GPIO7 can be used as OSC control pin in the sleep mode. For the detail, refer to Chapter 5.3. |

| GPIO6        | 11      | I/O | After the hardware reset, all pins are used for input only.                                   |

| GPIO7/OSCCTL | 10      | I/O |                                                                                               |

| GPIO8/RXD    | 8       | I/O |                                                                                               |

| GPIO9/TXD    | 7       | I/O | I/O General Purpose I/O [15:8]:                                                               |

| GPIO10/MODE  | 6       | I/O | General-purpose input/output pin for 3.3 V CMOS level and                                     |

| GPIO11/RSV1  | 5       | I/O | Schimitt input. They can be used as start-stop synchronous                                    |

| GPIO12/CTS   | 4       | I/O | serial terminals by setting GPLLT register. For details, refer to                             |

| GPIO13/DSR   | 3       | I/O | Chapter 2.3.                                                                                  |

| GPIO14/RTS   | 2       | I/O | After the hardware reset, all pins are used for input only.                                   |

| GPIO15/DTR   | 1       | I/O |                                                                                               |

### 1.4.2.6 Clock Generator Pins

Table 1.6 List of Clock Generator Pins

| Pin name | Pin No. | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1     | 46      | -   | OSC1 clock pin                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC2     | 43      | 0   | When using the sleep mode in the power management, it is used to connect 32.768kHz crystal. S1S60000 in the sleep mode is operated with this clock. When the sleep mode is not used, connect OSC1 to Vss and open OSC2.                                                                                                                                                                                                |

| OSC3     | 89      | ı   | OSC3 clock pin (for oscillation of crystal/ceramics or input of                                                                                                                                                                                                                                                                                                                                                        |

| OSC4     | 87      | 0   | external clock) Operating clock oscillation pin for S1S60000. Crystal transducer of 10 to 25MHz is connected. When entering external clock, input clock at 10 to 25MHz to OSC3 and make CSC4 open.  * It is advised to use clock of 25MHz normally.                                                                                                                                                                    |

| osco     | 94      | 0   | OSC output pin It is used to generate buffered output of OSC3 input. Frequency of output from this pin is the same as that OSC3 input. Supplying clock to PHY chip from this pin helps reducing number of oscillators for PHY.  Note: When supplying clock from this pin, be sure to use a crystal oscillator that can meet the frequency accuracy required by PHY chip. Normally, 50ppm maximum accuracy is required. |

| PLLC     | 80      | _   | PLL capacitor connecting pin It is the capacitor connecting pin used to double the OSC3 frequency with the internal PLL.                                                                                                                                                                                                                                                                                               |

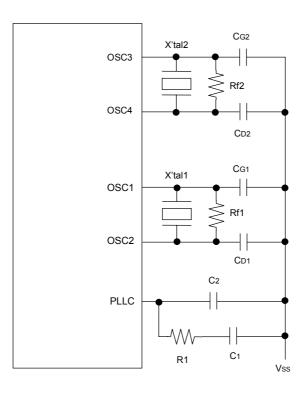

Figure 1.3 Clock Generator Connection Diagram

| X'tal1           | Crystal transducer  | 32.768kHz Ci (Max.) =34kΩ |

|------------------|---------------------|---------------------------|

| C <sub>G</sub> 1 | Gate capacitance    | 10pF                      |

| C <sub>D</sub> 1 | Drain capacitance   | 10pF                      |

| Rf1              | Feedback resistance | 10ΜΩ                      |

| X'tal2           | Crystal transducer  | 25MHz                     |

| CG2              | Gate capacitance    | 10pF                      |

| CD2              | Drain capacitance   | 10pF                      |

| Rf2              | Feedback resistance | 1ΜΩ                       |

| R1               | Resister            | 4.7kΩ                     |

| C1               | Capacitor           | 100pF                     |

| C2               | Capacitor           | 5pF                       |

### 1.4.2.7 Other Pins

Table 1.7 Other Pins

| Pin name    | Pin No.  | I/O | Function                                                                                                              |

|-------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------|

| DSIO        | 95       | I/O | These pins are used for communication with the debug tool ICD33.                                                      |

| DST[2:0]    | 98,97,96 | 0   | ICD33 is mainly use for rewriting flash memory on S1S60000.                                                           |

| DPCO        | 99       | 0   | It should not be connected to any equipment other than above.                                                         |

| DCLK        | 100      | 0   |                                                                                                                       |

| RESET#      | 91       | I   | Hardware Reset Input:<br>S1S60000 is reset as the low level is input. This pin contains the<br>pull-up resister.      |

| TEST1,TEST0 | 86,81    | I   | Test Input: Testing pins for this IC. They are made open when operated normally. They contain the pull-down resistor. |

| Reserve     | 77,76,84 |     | These pins are reserved for future expansion. No equipment should be connected to these pins.                         |

### 2. HARDWARE SPECIFICATIONS

### 2.1 Core CPU

Seiko Epson original 32 bits microcomputer S1C33240 or equivalent is employed for the core CPU. ADC, however, is not built in it.

CPU operating clock, always working identically with the internal bus, is initially set to twice the OSC3. Setting PSEN bit (11 bit) of GENCR register reduces it to 1/4 clock comparing when it operates normally. This arrangement helps reducing operating current.

### 2.1.1 ROM and Boot Address

S1S60000 contains a 128Kbytes flash ROM. After the reset, it is started from 0x0C00000, namely area 10 flash ROM area. Of these 128Kbytes, 127Kbytes are for the system firmware area, while the remaining 1Kbyte is for the user area. The user area ranges from 0xC1FC00 to 0xC1FFFF.

Rewriting in the system firmware is done from the debug serial pin and network by using a special tool and program. To rewrite in the user area, the debug serial pin or host interface can be used.

### 2.1.2 RAM

S1S60000 contains an 8Kbytes RAM. Device size of this built-in RAM is 32 bits enabling to read/write data of a byte, half-word or word in a single cycle. Since this RAM is exclusively used by S1S60000, user can't operate it

### 2.2 Peripheral Circuits

Among the peripheral blocks of the built-in core CPU S1C33240, S1S60000 uses the following built-in peripheral circuits. For details of respective peripheral circuits, refer to "S1C33 Family ASIC Macro Manual".

C33 core block

CPU 32-bit RISC type CPU S1C33000

BCU Bus control unit

ITC Interrupt controller

CLG Clock generator

DBG Functional block for debugging featured with ICD33 (In-Circuit Debugger for S1C33 Family)

• C33 peripheral circuits block

Pre-scaler Used to set the clock for peripheral circuits programmable

16 bits programmable timer

Serial interface

Input/output port

Elapsed timer

C33DMA block

HSDMA (high-speed DMA) 4-channel

The I/O memory map contained S1S60000 is essentially the same as that of S1C33240. For the detail, refer to "S1C33240 Technical Manual".

### 2.3 Serial Interface

GPIO [15:8] can be used as the serial interface when the GPALT register bit [15:8] is set.

### 2.3.1. Hardware Control Mode

GPIO10 can be used as the MODE signal line when the GPALT register bit [15:8] is set and GPIO [15:8] is used as a serial interface pin. While this signal is low, normal serial communication mode is set based on the GENCR register SERCONF bit (bit [10:8]) and SERMODE register settings. When this signal is high, the mode is switched to the hardware control mode via the serial interface. Note that the communication conditions in this mode are limited to the following:

Start-stop synchronous serial, 9,600 baud, 8-bit data, 1-stop bit, without parity and flow control.

For details on this mode, refer to Chapter 5.1.4.

**Note:** Avoid accessing the serial interface for at least 100ms after switching the mode.

### 2.3.2 Serial Emulation Mode

When GPALT register's bit [15:8] is set and GENCR register's SERCONF (bit [10:8])=010, the serial emulation mode is selected. Functions of respective pins are as shown in Table 2.1.

Table 2.1 Pin Functions when Start-Stop Synchronous Serial is selected

| Pin    | Pin | Name | In/Out | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO15 | 1   | DTR  | 0      | Data Terminal Ready Indicates that data receiving is enabled. It is a high active signal.                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO14 | 2   | RTS  | 0      | Request to Send Indicates that data transmission is enabled. It is a high active signal.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GPIO13 | 3   | DSR  | I      | Data Set Ready Indicates that transmission from outside is readied. It is a high active signal. If this signal is high and yet preparation for receiving is readied, S1S60000 causes DTR to be active.                                                                                                                                                                                                                                                                                       |

| GPIO12 | 4   | стѕ  | I      | Clear to Send Indicates that the state is readied for receiving data from outside. It is a high active signal. If this pin goes low, transmission is temporarily suspended until it returns to high. The time from the stop up to the resumption of transmission is uncertain since this operation is controlled according to the interrupt-based software control. The external device side must make sure that sufficient margin is available on the buffer before turning on the control. |

| GPIO11 | 5   | _    | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPIO10 | 6   | MODE | I      | Mode Select Used to switch over normal/hardware control modes. Be sure to set this pin to low in the normal mode.                                                                                                                                                                                                                                                                                                                                                                            |

| GPIO9  | 7   | TXD  | 0      | Transmit Data<br>Serial transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO8  | 8   | RXD  | I      | Receive Sata<br>Serial transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

TXD and RXD are start-stop synchronous serial pins to be transmitted/received by use of the serial I/F Ch.0 function of the built-in S1C33240. For details, refer to the serial I/F specifications in the technical manual for the S1C33240. Other control lines are controlled by the software. DSR and CTS signals are processed by internal interruptions.

In this mode, transmission data of the serial interface are transmitted to the preset destinations. This is useful when transmitting data from a device with a conventional RS232 interface to another device on the Ethernet.

### [ Establishing connection ]

When GPIO [15:8] is set to start-stop synchronous serial, the S1S60000 performs processing equivalent to that of open command of the host interface, automatically. In Active Open (client operation), connection is made to the IP address and port of the destination preset to the EEPROM. When connection is terminated by the destination, reconnection is performed automatically. In Passive Open (server operation), the server enters listening state by opening its transmission port preset by itself. Connection is established when it is requested externally.

### [ Transmission from Serial Interface to Network ]

Data received from RXD is output to the network when no data has been received for about 10 minutes after the last data was received during transfer time, or when the data volume received reaches 1 packet (536 bytes).

### [ Transmission from Network to Serial Interface ]

Data received from the network is transmitted to TXD after executing an error check and removing the header information.

### 2.4 Power Supply

### 2.4.1 Operating Voltage

S1S60000 operates with the voltage supplied across VDD and Vss. This operating voltage is as shown below.  $V_{DD} = 3.3 \pm 0.3 \text{V}(\text{Vss} = \text{GND})$

Note: S1S60000 has 7 VDD pins and 6 Vss pins. Be sure to connect every pin to the power supply so that any of them may not become open.

### 2.5 Power on Reset

Be sure to implement initial reset at powering on in order to ensure normal start of S1S60000. Schmitt input is applied RESET#.

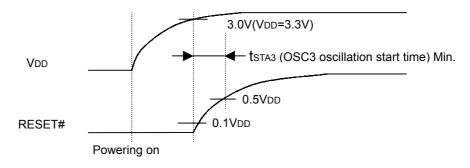

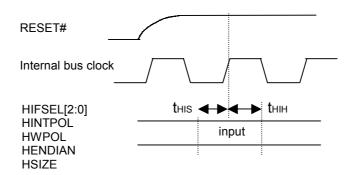

Operation of OSC3 oscillation circuit is started by the initial reset (RESET#=Low) and then CPU is started by OSC3 clock at the positive going edge of the reset signal. OSC3 oscillation circuit takes some time until its oscillation stabilizes(Vdd=3V, the time required for stabilized oscillation under normal operation condition: 10ms Max.). Thus, in order to ensure positive start of CPU, be sure to release the initial reset only after this time has been elapsed. Make sure that length of the initial reset pulse is longer than the above oscillation stabilizing time. Figure 2.1 shows the timing chart at the power on reset.

Figure 2.1 Power on Reset Timing

After powering on, maintain RESET# pin below 0.1 • VDD (Low level) until supply voltage reaches the oscillation start voltage (3.0V) or above. It is also required to maintain RESET# pin below 0.5 • VDD until oscillation of OSC3 oscillation circuit is stabilized.

**Note:** Oscillation start time of OSC3 oscillation circuit depends on the device substrate pattern used as well as the operating environment. So you must be sure to provide enough time before releasing the reset.

### Reset pulse

When S1S60000 is in operation, it is possible to implement the initial by applying low level pulse to RESET# pin. In this case, however, the pulse width used must be greater than the minimum reset pulse width listed in the "AC Characteristics".

When applying reset pulse while OSC3 oscillation circuit is not in operation, RESET# pin must be maintained at low level for a period longer than the oscillation stabilization time. It is the same requirement as that for the power on reset.

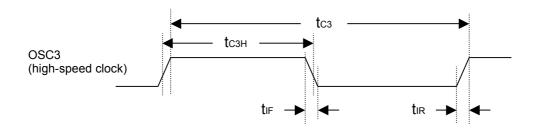

### 2.6 OSC3 Clock

Operating clock for S1S60000 is entered to OSC3 pin. For the internal bus and CPU operation, the clock entered from OSC3 is used after it has been doubled. Normally, 25MHz clock is used. The lowest frequency allowed to input is 10MHz.

While the power save mode is turned on, the internal bus clock and CPU operating clock is reduced to 1/4 of the normal operation (1/2 of that input from OSC3).

When operating S1S60000 on 100Base-TX, be sure to enter 25MHz to OSC3 and operate S1S60000 in the normal mode. Note that it cannot operate in the power saving mode.

### 3. NETWORK INTERFACE

### 3.1 MII Interface

S1S60000 employs MII (Media Independent Interface) for connection with the physical layer (PHY chip) enabling it to connect various network PHY chips designed for MII. For the detail of MII, refer to IEEE 802.3 Clause22. However, your attention is required on the following points.

### • CRS (Carrier Sense) signal

This signal is not used in full duplex communication. Connect CRS signal to GPIO2 pin only when half-duplex communication is to take place. Also, when setting PHY forcibly to half-duplex communication, half-duplex must be set on GENCR.

### • TX ER signal

This signal is used to propagate the error received with RX\_ER. This signal, however, is not used on S1S60000 since it does have a repeating function.

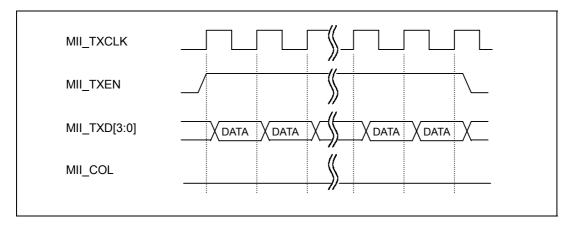

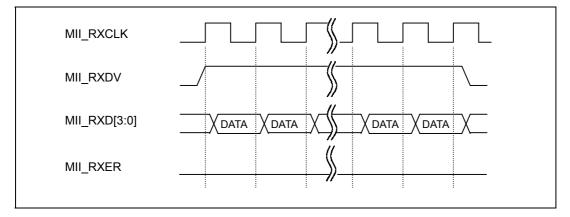

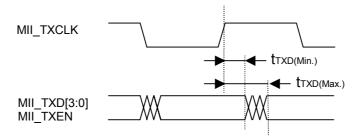

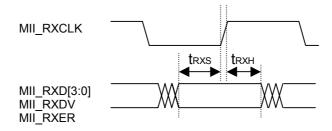

Figures 3.1 and 3.2 show MII transmit waveform and MII receive waveform, respectively.

In transmission, MII\_TXEN is set to high level and then level of MII\_TXD is changed after MII\_TXCLK has reached high level. In half-duplex communication, interrupt occurs in S1S60000 as MII\_COL goes high level thereby forcing MII\_TXEN to low level and suspending transmission. Then transmission is resumed after a predetermined time.

In receiving, after MII\_RXDV has reached high level, MII\_RXD is acquired at positive-going edge of MII\_RXCLK. If MII\_RXER goes high level while communicating with 100Base-TX, FCS error is set after receiving is complete and the received frames are disposed.

Figure 3.1 MII Transmit Waveform

Figure 3.2 MII Receive Waveform

### 3.2 Management Interface

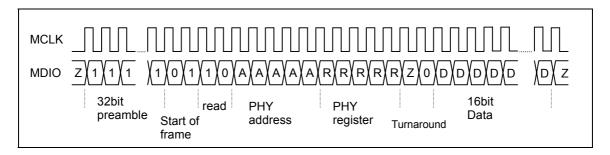

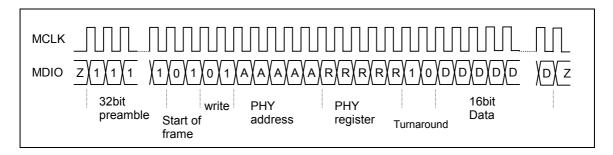

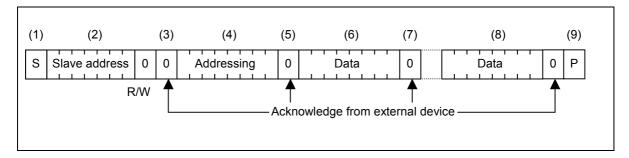

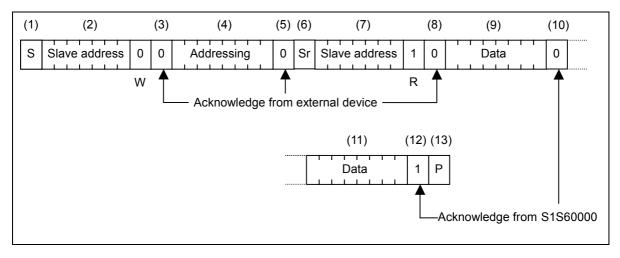

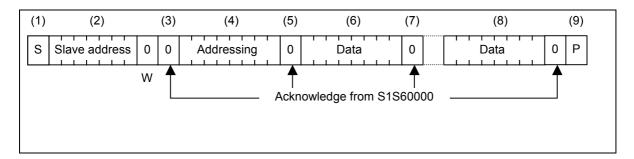

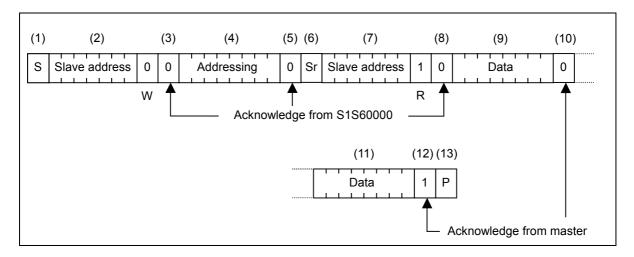

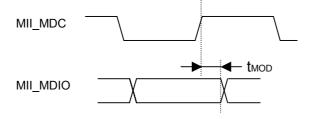

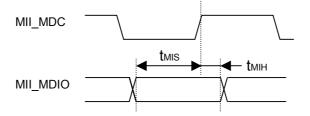

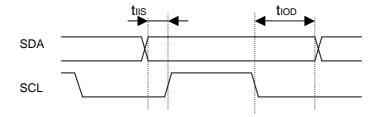

S1S60000 supports MII management interface. It can write or read registers in PHY through this interface. Figures 3.3 and 3.4 show the waveforms in the read and write operations, respectively.

Figure 3.3 MII Management Interface Read Operation

Figure 3.4 MII Management Interface Write Operation

### 3.3 Connecting PHY Chips

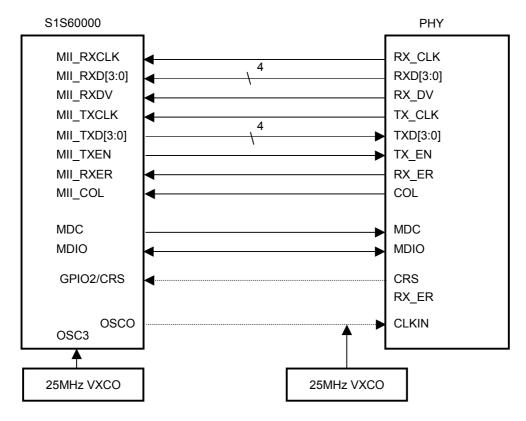

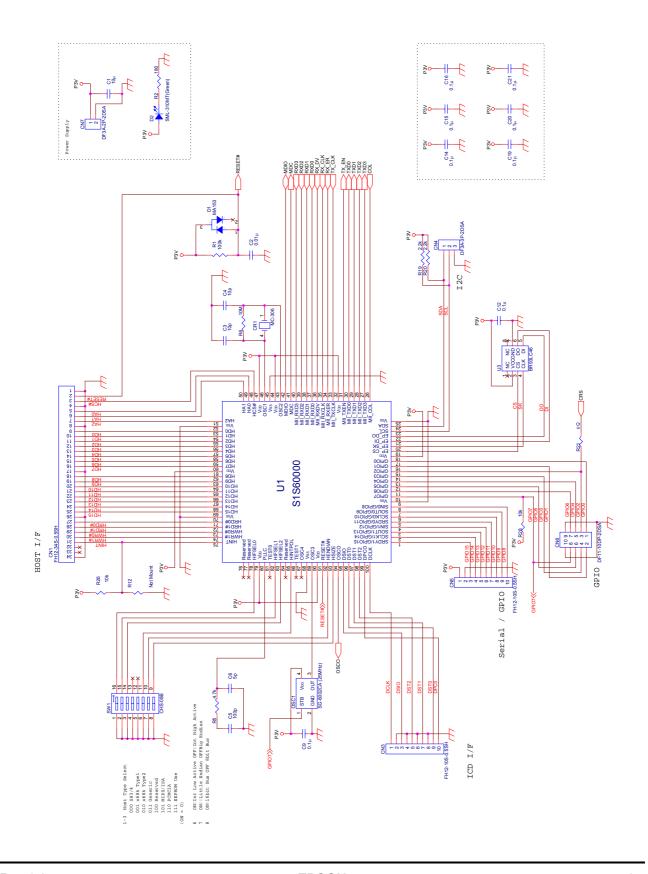

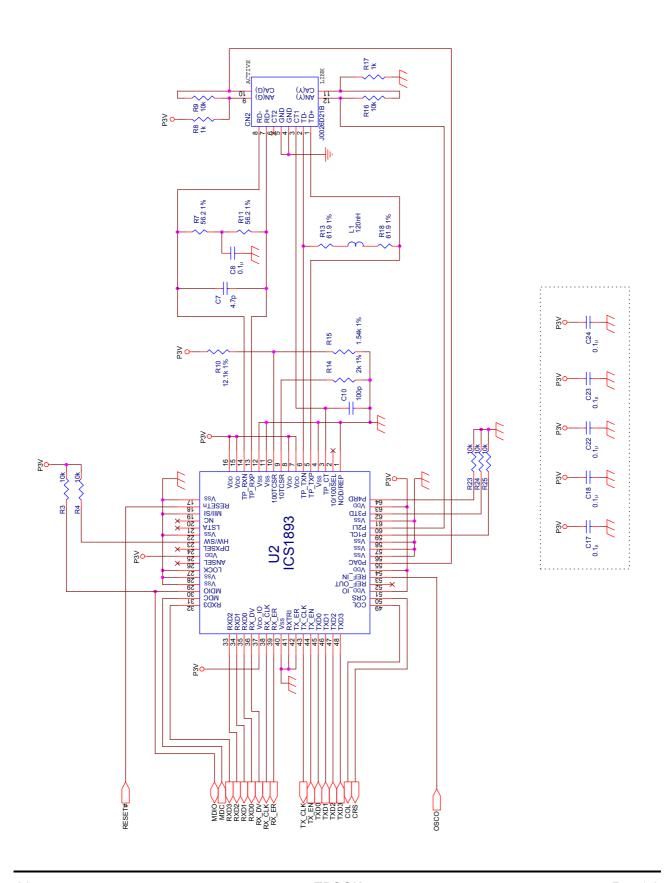

Figure 3.5 shows connection between S1S60000 and PHY chips.

You don't have to connect CRS for full duplex communication. TX ER signal is also not connected.

In the normal operation and the power save mode, OSC pin on S1S60000 outputs the signal being formed after buffering OSC3 input. Thus connecting a 25MHz crystal oscillator to OSC3 input and connecting OSCO to the clock of PHY allows you operate both S1S60000 and PHY with a single crystal oscillator.

**Note:** Before supplying clock form OSCO to PHY, make sure that it meets the clock accuracy required by PHY. Also make sure that length of the pattern connected is minimized and the clock waveform satisfies requirements of the PHY specification.

Followings are recommended for connection with S1S60000.

ICS ICS1893Y-10 TDK 78Q2120-64T

Figure 3.5 Connection between S1S60000 and PHY

### 3.4 Communication Mode

When using S1S60000, it is normally recommended to select 10Base-T/full duplex mode. S1S60000 does not support 100Base-TX/full duplex communication.

When selecting a communication mode through the auto-negotiation with the PHY chip, S1S60000 carries out the negotiation in the order of 10Base-T/full duplex, 100Base-TX/half-duplex and 10Base-T/half-duplex, and the mode for which the link is established the first is employed as the communication mode. This process takes approximately 6 seconds at maximum.

You can also turn on 100Base-TX/half-duplex or 10Base-T/half-duplex mode communication from setting of PHYMODE register. In this case, however, transfer performance can become lower than that available from 10Base-T/full duplex because of re-sending processing at occurrence of collisions as well as the restrictions imposed on the internal processing. Be advised not to use these modes except where so forced.

### Communication Mode Setup Flow

- (1) The auto-negotiation is started selecting 10Base-T/Full-Duplex as the target. If it ends successfully, 10Base-T/Full-Duplex is employed and the setup process is ended. Otherwise, the negotiation continues to the next step.

- (2) The auto-negotiation is executed selecting 100Base-TX/Half-Duplex as the target. If it ends successfully, 100Base-TX/ Half-Duplex is employed and the setup process is ended. Otherwise, the negotiation continues to the next step.

- (3) The auto-negotiation is executed selecting 10Base-T/Half-Duplex as the target. If it ends successfully, 10Base-T/ Half-Duplex is employed and the setup process is ended.

- (4) If all negotiations ended unsuccessfully, S1S60000 judges that the link has not been established.

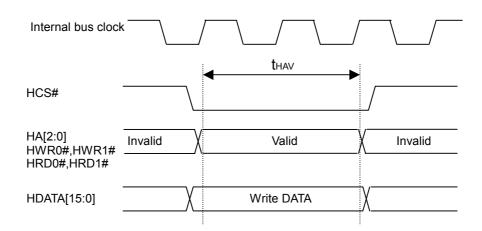

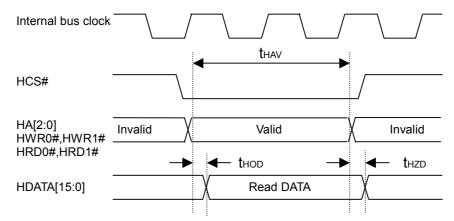

### 4. HOST INTERFACE

The host interface is an 8 bits or 16 bits parallel interface used to connect S1S60000 with external MPU. The host interface can connect up to five types of MPUs depending on its setting.

### 4.1 Control Signals

Table 4.1 shows the host interface signals. Every input pin including I/O pins contain a pull-up resister enabling then to accept 5V input is acceptable for HCS#, HA [2:0], HD [15:0], HRD0#, HRD1#, HWR0# and HWR1#. Output is 3.3V CMOS or 3-state output. When not using the host interface (when implementing GPIO control independently, for instance), be sure to leave the every host interface signal unconnected.

Pin name I/O **Function** HCS# It is the access enable signal. Access available as it goes low HA[2:0] ī Port select signal HD[15:0] I/O Input/output data bus HRD0# A R/W control signal. Its function depends on state of HIFSEL [2:0]. Its function depends on state of HIFSEL [2:0]. HRD1# ı A R/W control signal. A R/W control signal. HWR0# Its function depends on state of HIFSEL [2:0] HWR1# A R/W control signal. Its function depends on state of HIFSEL [2:0]. It is the interrupt signal. Polarity is settable. Host interface type select signal HINT Tri HIFSEL[2:0] HINTPOL Host interrupt line polarity select (enabled at the reset) 1:High active, 0:Low active HENDIAN Host interface endian select (enabled at the reset) 1:Big Endian, 0:Little Endian HSIZE Host interface size select (enabled at the reset) 1:8bit, 0:16bit

Table 4.1 Host Interface Signals

Tri: 3-state output

When HCS# is low, an access port is selected depending on the state of HA [2:0]. Following shows the port assignment.

### (1) When 16-bit interface is selected

| HA[2:0] | Access port                               |

|---------|-------------------------------------------|

| 00x     | Command port (Write) / Status port (Read) |

| 01x     | Data port                                 |

| 1xx     | Flag port                                 |

Note: The flag port outputs the same contents to the upper and lower 8 bits.

### (2) When 8-bit interface is selected

| HA[2:0] | Access port                                           |

|---------|-------------------------------------------------------|

| 000     | Lower command port (Write) / Lower status port (Read) |

| 001     | Upper command port (Write) /Upper status port (Read)  |

| 010     | Lower data port                                       |

| 011     | Upper data port                                       |

| 1xx     | Flag port                                             |

Note: When the 8-bit interface is used, data transfer of one time is completed as access is made to both the upper and lower ports. The order in accessing the upper and lower ports is optional. The flag port does not have the upper or lower port.

### 4.2 Host Interface Port

### 4.2.1 Command Port

This port is used to send a command from the host MPU to S1S60000. Since this port is 16-bit wide, two times of access (the upper and lower addresses) are required when the 8-bit interface is used. For detail of the commands, refer to the "S1S60K Series Host I/F Manual".

### 4.2.2 Status Port

This port is used to return a status from S1S60000 to the host MPU. Since this port is 16-bit wide, two times of access (the upper and lower addresses) are required when the 8-bit interface is used. For detail, refer to the "S1S60K Series Host I/F Manual".

### 4.2.3 Data Port

This port is used to exchange data between the host MPU and S1S60000. Since this port is 16-bit wide, two times of access (the upper and lower addresses) are required when the 8-bit interface is used. An option segment added to a command or status is also exchanged via this port. For detail of the options, refer to the "S1S60K Series Host I/F Manual".

### 4.2.4 Flag Port

This port is used to indicate how a host interface-related command, status or data is processed. One of the following two types is assigned according to setting of EXTINT (bit7).

When EXTINT=0, the state of bit [1:0] is the factor which activates the HINT signal. If any of the bits is 1, the HINT signal goes active (polarity of the signal is changeable). On the host side, the reading-out status or data clears the corresponding factors. Thus, HINT signal turns to inactive when all factors are cleared. When checking the data processing status on the S1S60000 from the host interface, the state of bit [3:2] must be referenced.

When EXTINT=1, the state of bit [3:0] is the factor which activates the HINT signal. If any of the bits is 1, the HINT signal goes active (polarity of the signal is changeable).

On the host side, factors can be cleared by writing 1 at the corresponding bit positions. The HINT signal becomes inactive when all factors are cleared.

This port is 8-bit wide. Thus, when the 16-bit interface is used or when two times of access (to the upper and lower addresses) are made from the 8-bit interface, the same data is read to the upper and lower bits.

bit EXTINT=0 EXTINT=1 **EXTINT** 0: Extended interrupt is not used (so far compatible) 1: Extended interrupt is used 6:5 Not used. Value is 0. **HSTREN** 0: Data port receiving circuit of S1S60000 is disabled Data port receiving circuit of S1S60000 is enabled 3 H2CDC Data read complete notice (Read) H2CDV Write data processing state (R/O) 0: Waiting for data read or data is absent 0: Data write available 1: Read of preceding data is complete (it is cleared as 1 is written) 1: Waiting for data read 2 H2CCV Command processing state H2CCC Command processing complete notice (Read) (R/O) 0: Command is not processed yet or command is 0: Command write available not present 1: Processing of preceding command is complete (it 1: Waiting processing of command is cleared as 1 is written) C2HDV Read-data preparation state (Read) C2HDV Read-data preparation state (R/O) 0: Data to be read is not present 0: Data to be read is not present 1: Data to be read is present (it is cleared as 1 is 1: Data to be read is present written) C2HSV Status preparation state (R/O) C2HSV Status preparation state (Read) 0: Status to be read is not present 0: Status to be read is not present 1: Status to be read is present 1: Status to be read is present (it is cleared as 1 is written)

Table 4.2 Flag Port Bit Assignment

Note: When the host interface is 16 bits wide, the same information is output to bit [15:8] and bit [7:0]. Writing is enabled to bit [7:0] alone.

### 4.3 Host Interface Type

Type of the host interface is selected depending on state of HIFSEL [2:0] at the hardware reset. Table 4.3 shows assignment of the host interface type.

Table 4.3 Host Interface Type

| HIFSEL[2:0] | Type   | Example of host CPUs (8/16bit bus)                                                  |

|-------------|--------|-------------------------------------------------------------------------------------|

| 000         | Type 0 | Hitachi SH-3/4, EPSON S1C33                                                         |

| 001         | Type 1 | MC68000/10                                                                          |

| 010         | Type 2 | MC68030/40                                                                          |

| 011         | Type 3 | Generic                                                                             |

| 100         | Type 4 | Reserved                                                                            |

| 101         | Type 5 | MIPS, ISA, NEC VR4121(16bit)                                                        |

| 110         | Type 6 | PCMCIA, Philips PR31500/PR31700, Toshiba TX3912                                     |

| 111         | EEPROM | A type is selected in the range of Type0 to Type6 depending on HIFCR data of EEPROM |

- Type0 This type of interface controls access by use of the independent write signals (byte basis) and a single read signal. Hitachi SH-3/4 and EPSON S1C33 belong to this type.

- Type1 It controls access by combining the upper/lower byte signal (such as UDS#/LDS#) and the read/write signal. Motorola's MC68000 belongs to this type. In this case, connect the upper byte select signal to HWR0#, the lower byte select signal to HWR1# and the read/write signal to HRD1#. And maintain RD0# unconnected.

- Type2 It controls access by combining the data transfer size indicate signal and the read/write signal. MC68030/40 belong to this type. In this case, connect SIZ0 signal to HWR0#, SIZ1 signal to HRD0# and the read/write signal to HRD1#. And maintain HWR1# unconnected.

- Type3 It is the general-purpose type. When a given host CPU does not fit into any type, it is used to connect such host CPU by use of an externally generated access signal. In this case, connect the lower byte write signal to HWR0#, the upper byte write signal to HWR1#, the lower byte read signal to HRD0# and the upper byte read signal to HRD1#.

- Type4 This type is reserved for future extension. Don't select it.

- Type5 It controls access by using the upper/lower byte select signal (composed of two or more signals) plus the independent read signal and the write signals. MIPS and ISA bus belong to this type. In this case, connect the write signal to HWR0#, the upper byte select signal to HWR1# and the read signal to HRD0#. Maintain RD1# unconnected.

- Type6 It controls access by use of the independent byte enable signal, independent read enable signal and write signal. PCMCIA interface belongs to this type. In this case, connect the write signal to HWR0#, the read signal to HRD0# and the lower byte enable signal to HRD1#.

- EEPROM It selects a type according to HIFCR data of the serial EEPROM. A type is selectable in the range of Type0 to Type6. When EEPROM data is "111" or when EEPROM is not connected, S1S60000 assumes that a host CPU is unconnected.

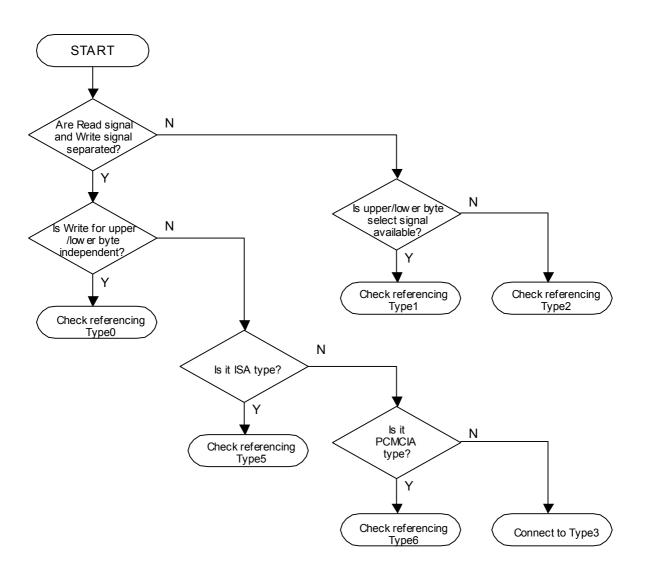

Figure 4.1 shows the CPU type selection flowchart. Identify type of the target CPU based on its signal line and then check whether an appropriate access is obtainable or not referencing the signal pattern of respective CPUs in Tables 4.5 to 4.10. When the selected signal pattern does not match the pattern of the target CPU, decode the signal externally so that it may fit to the CPU type having the same or similar pattern to that of Type3 (Generic). When a CPU's address and data buses are multiplexed, be sure separate them before connection by, for instance, using a latch provided externally.

Figure 4.1 Host I/F Type Selection Flowchart

Table 4.4 Signal Connection by CPU Type

| Туре  | Manufacturer | Model              | HCS# | HA[2:0]       | HD[15:0]              | HWR0#         | HWR1#         | HRD0#         | HRD1#         | RESET#            | Re-<br>mark          |

|-------|--------------|--------------------|------|---------------|-----------------------|---------------|---------------|---------------|---------------|-------------------|----------------------|

| Type0 | Hitachi      | SH-3               | (*1) | A[2:0]        | D[15:0]               | WE0#          | WE1#          | RD#           | _             | RESET#            |                      |

|       |              | SH-4               | (*1) | A[2:0]        | D[15:0]               | WE0#          | WE1#          | RD#           | _             | RESET#            |                      |

|       | EPSON        | S1C33              | (*1) | A[2:0]        | D[15:0]               | #WRL          | #WRH          | #RD           | _             | #RESET            |                      |

| Type1 | Motolora     | MC68000<br>MC68010 | (*1) | A[2:1],<br>NC | D[15:0]               | UDS#          | LDS#          | _             | R/W#          | RESET#            | 16bit<br>bus<br>only |

|       |              | MC68008            | (*1) | A[2:0]        | D[7:0]                | _             | DS#           | _             | R/W#          | RESET#            | 8bit<br>bus<br>only  |

|       |              | MC68HC<br>001      | (*1) | A[2:0]        | D[15:0]               | UDS#          | LDS#          |               | R/W#          | RESET#            |                      |

| Type2 | Motolora     | MC68030            | (*1) | A[2:0]        | D[31:16]              | SIZ0          | _             | SIZ1          | R/W#          | RESET#            |                      |

|       |              | MC68040            | (*1) | A[2:0]        | D[31:16]              | SIZ0          | _             | SIZ1          | R/W#          | RESET#            |                      |

| Type3 | _            | Generic            | (*1) | A[2:0]        |                       | WR0#          | WR1#          | RD0#          | RD1#          | RESET#            |                      |

| Type5 | _            | MIPS               | (*1) | SA[2:0]       | SD[15:0]              | MEMW#         | SBHE#         | MEMR#         | _             | inverted<br>RESET |                      |

|       | IBM          | ISA                | (*1) | SA[2:0]       | SD[15:0]              | MEMW#         | SBHE#         | MEMR#         | _             | inverted<br>RESET |                      |

|       | NEC          | VR4121             | (*1) | ADD<br>[2:0]  | DATA<br>[15:0]        | IOW#          | SHB#          | IOR#          | _             | RSTSW#            |                      |

| Type6 | Philips      | PR31500<br>PR31700 | GND  | A[2:0]        | D[23:16],<br>D[31:24] | /CARD<br>IOWR | /CARD<br>xCSL | /CARD<br>IORD | /CARD<br>xCSH | /PON              |                      |

|       | Toshiba      | TX3912             | GND  | A[2:0]        | D[23:16],<br>D[31:24] | CARD<br>IOWR* | CARD<br>xCSL* | CARD<br>IORD* | CARD<br>xCSH* | PON*              |                      |

|       | PCMCIA       | PC Card            | GND  | A[2:0]        | D[15:0]               | -WE           | -CE1          | -RD           | -CE2          | inverted<br>RESET |                      |

<sup>-:</sup> Not Connect

**Note:** The connections described in this table do not necessarily guarantee the operation. The connection required depends on the operating conditions (including the bus size, bus clock and signal timing). Be sure to reference the signal pattern by type before finalizing your connection.

<sup>\*1:</sup> Enter the decoded signal, as needed. Active Low.

Table 4.5 Signal Pattern of Type0

|       |        |             |           |       | S1S60 | 000 signa | l line |     |

|-------|--------|-------------|-----------|-------|-------|-----------|--------|-----|

| R/W   | Endian | Bus<br>size | Operation | HWR0# | HWR1# | HRD0#     | HRD1#  | HA0 |

| Write | Little | 16bit       | Word      | L     | L     | Н         | Н      | L   |

|       |        |             | Low       | L     | Н     | Н         | Н      | L   |

|       |        |             | High      | Н     | L     | Н         | Н      | Н   |

|       |        | 8bit        | Low       | L     | Н     | Н         | Н      | L   |

|       |        |             | High      | L     | Н     | Н         | Н      | Н   |

|       | Big    | 16bit       | Word      | L     | L     | Н         | Н      | L   |

|       |        |             | Low       | L     | Η     | Н         | Н      | L   |

|       |        |             | High      | Η     | L     | Н         | Н      | Н   |

|       |        | 8bit        | Low       | L     | Η     | Н         | Н      | L   |

|       |        |             | High      | L     | Н     | Н         | Н      | Н   |

| Read  | Little | 16bit       | Word      | Н     | Н     | L         | Н      | L   |

|       |        |             | Low       | Н     | Н     | L         | Н      | L   |

|       |        |             | High      | Н     | Н     | L         | Н      | Н   |

|       |        | 8bit        | Low       | Н     | Н     | L         | Н      | L   |

|       |        |             | High      | Н     | Н     | L         | Н      | Н   |

|       | Big    | 16bit       | Word      | Н     | Н     | L         | Н      | L   |

|       |        |             | Low       | Н     | Н     | L         | Н      | L   |

|       |        |             | High      | Η     | Η     | Ĺ         | Н      | Н   |

|       |        | 8bit        | Low       | Η     | Η     | Ĺ         | Н      | L   |

|       |        |             | High      | Н     | Н     | L         | Н      | Н   |

<sup>\*</sup> HRD1# is constantly kept at High by the internal pull-up resister in order to maintain it unconnected.

Table 4.6 Signal Pattern of Type1

|       |        |             |           |       | S1S60 | 000 signa | l line |     |

|-------|--------|-------------|-----------|-------|-------|-----------|--------|-----|

| R/W   | Endian | Bus<br>size | Operation | HWR0# | HWR1# | HRD0#     | HRD1#  | HA0 |

| Write | Little | 16bit       | Word      | L     | L     | Н         | L      | L   |

|       |        |             | Low       | L     | Н     | Н         | L      | L   |

|       |        |             | High      | Η     | L     | Τ         | L      | Н   |

|       |        | 8bit        | Low       | Η     | L     | Τ         | L      | L   |

|       |        |             | High      | Η     | L     | Τ         | L      | Н   |

|       | Big    | 16bit       | Word      | L     | L     | Τ         | L      | L   |

|       |        |             | Low       | L     | Η     | Τ         | L      | L   |

|       |        |             | High      | Η     | L     | Τ         | L      | Н   |

|       |        | 8bit        | Low       | Η     | L     | Τ         | L      | L   |

|       |        |             | High      | Η     | L     | Τ         | L      | Н   |

| Read  | Little | 16bit       | Word      | L     | L     | Τ         | Н      | L   |

|       |        |             | Low       | L     | Η     | Τ         | Н      | L   |

|       |        |             | High      | Η     | L     | Τ         | Н      | Н   |

|       |        | 8bit        | Low       | Η     | L     | Τ         | Н      | L   |

|       |        |             | High      | Η     | L     | Τ         | Н      | Н   |

|       | Big    | 16bit       | Word      | L     | L     | Н         | Н      | L   |

|       |        |             | Low       | L     | Н     | Н         | Н      | L   |

|       |        |             | High      | Н     | L     | Н         | Н      | Н   |

|       |        | 8bit        | Low       | Н     | Ĺ     | Н         | Н      | Ĺ   |

|       |        |             | High      | Н     | Ĺ     | Н         | H      | H1  |

<sup>\*</sup> HRD0# is constantly kept at High by the internal pull-up resister in order to maintain it unconnected.

Table 4.7 Signal Pattern of Type2

|       |        |             |           |       | S1S60 | 000 signa | l line |     |

|-------|--------|-------------|-----------|-------|-------|-----------|--------|-----|

| R/W   | Endian | Bus<br>size | Operation | HWR0# | HWR1# | HRD0#     | HRD1#  | HA0 |

| Write | Little | 16bit       | Word      | L     | Н     | Н         | L      | L   |

|       |        |             | Low       | Н     | Н     | L         | L      | L   |

|       |        |             | High      | Н     | Н     | L         | L      | Η   |

|       |        | 8bit        | Low       | Η     | Η     | L         | L      | L   |

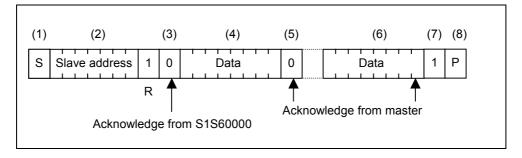

|       |        |             | High      | Η     | Η     | L         | L      | Н   |