# GATE ARRAY S1L35000 Series DESIGN GUIDE

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any from or by any means without the written permission of EPSON. EPSON reserves the right to make changes to this material without notice. EPSON does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this marerial will be free from any patent or copyright infringement of a third party. This material or portions there of may contain techology or the subject relating to strategic products under the control of the Forign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of international Trade and Industry or other approval from another government agency.

©SEIKO EPSON CORPORATION 2001, All rights reserved.

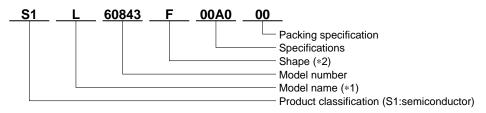

#### The information of the product number change

Starting April 1, 2001 the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

# Configuration of product number

#### DEVICES

#### \*1: Model name

| Κ | Standard Cell  |

|---|----------------|

| L | Gate Array     |

| Х | Embedded Array |

\*2: Shape

| В | Assembled on board, COB, |

|---|--------------------------|

|   | BGA                      |

| С | Plastic DIP              |

| D | Bare Chip                |

| F | Plastic QFP              |

| Н | Ceramic DIP              |

| L | Ceramic QFP              |

| Μ | Plastic SOP          |

|---|----------------------|

| R | TAB–QFP              |

| Т | Tape Carrier (TAB)   |

| 2 | TSOP (Standard Bent) |

| 3 | TSOP (Reverse Bent)  |

# Comparison table between new and previous number

| Previous number | New Number      |  |  |

|-----------------|-----------------|--|--|

| SLA35000 series | S1L35000 series |  |  |

| SLA3504         | S1L35043        |  |  |

| SLA3506         | S1L35063        |  |  |

| SLA3509         | S1L35093        |  |  |

| SLA3516         | S1L35163        |  |  |

|                 |                 |  |  |

# S1L35000 Series Table of Contents

| Chapter 1 Overview                                                                          |      |

|---------------------------------------------------------------------------------------------|------|

| 1.1 Features of the S1L35000 Series                                                         | 1    |

| 1.2 Master Structure of the S1L35000 Series                                                 |      |

| 1.3 Electrical Characteristics and Specifications of the S1L35000 Series                    | 2    |

| 1.4 Overview of Gate Array Development Flow                                                 | 6    |

| Chapter 2 Estimating Gate Density and Selecting the Master                                  | 8    |

| 2.1 Dividing up Logic between Chips                                                         |      |

| 2.2 Determining Gate Density                                                                |      |

| 2.3 Estimating the Number of Input/Output Terminals                                         |      |

| 2.4 Selecting the Master                                                                    |      |

| 2.5 Estimating the BCs That can be Used in Circuits Which Include RAM                       |      |

| Chapter 2 Coutions and Notes Regarding Circuit Design                                       | 10   |

| Chapter 3 Cautions and Notes Regarding Circuit Design<br>3.1 Inserting Input/Output Buffers |      |

| 3.2 The Use of Differentiating Circuits is Forbidden                                        |      |

| -                                                                                           |      |

| 3.3 Wired Logic is Forbidden                                                                |      |

| 3.4 Hazard Countermeasures                                                                  |      |

| 3.5 Fan-Out Constraints                                                                     |      |

| 3.6 Bus Circuits                                                                            |      |

| 3.7 Schematic Capture Guidelines                                                            |      |

| 3.8 Clock Tree Synthesis                                                                    |      |

| 3.9 Restrictions and Constraints on VHDL/Verilog-HDL Netlist                                |      |

| 3.9.1 Common Restrictions and Constraints                                                   |      |

| 3.9.2 Restrictions and Constraints for Verilog Netlist                                      |      |

| 3.9.3 Restrictions and Constraints on VHDL Netlist                                          | 18   |

| Chapter 4 Input/Out Buffer and Their Use                                                    | 19   |

| 4.1 Types of Input/Output Buffer in the S1L35000 Series                                     | . 19 |

| 4.1.1 Selecting I/O Buffer                                                                  |      |

| 4.2 I/O Buffer Configurations with a Single Power Supply                                    | .20  |

| 4.2.1 I/O Buffer Configurations with a Single 5.0V Power Supply                             | 20   |

| 4.2.1.1 Input Buffer Configurations with a Single 5.0V Power Supply                         |      |

| 4.2.1.2 Output Buffer Configurations with a Single 5.0V Power Supply                        |      |

| 4.2.1.3 Bi-directional Buffer Configurations with a Single 5.0V Power Supply                |      |

| 4.2.2 I/O Buffer Configurations with a Single 3.0/3.3 V Power Supply                        |      |

| 4.2.2.1 Input Buffer Configurations with a Single 3.0/3.3 V Power Supply                    |      |

| 4.2.2.2 Output Buffer Configurations with a Single 3.0/3.3V Power Supply                    |      |

| 4.2.2.3 Bi-directional Buffer Configurations with a Single 3.0/3.3 V Power Supply           |      |

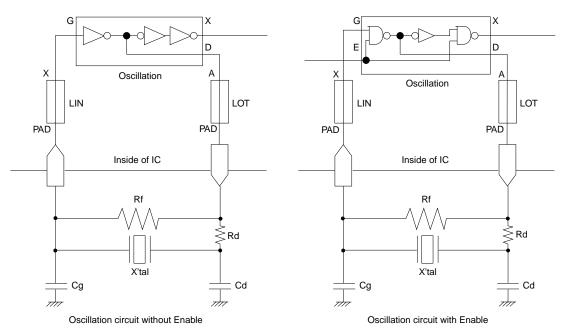

| 4.3 Oscillation Circuit                                                                     |      |

| 4.3.1 Oscillation Circuit Configurations                                                    |      |

| 4.3.2 Oscillator Circuit Considerations                                                     | 30   |

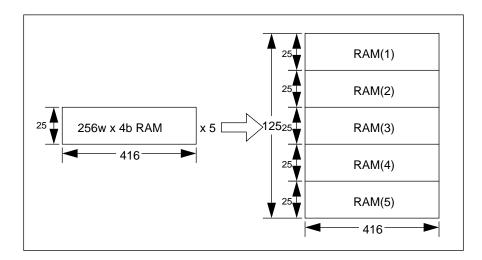

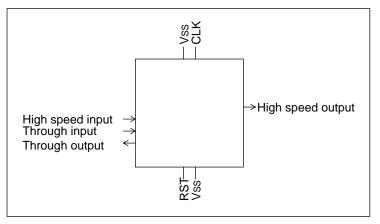

| Chapter 5 RAM                                                                               |      |

| 5.1 Features                                                                                |      |

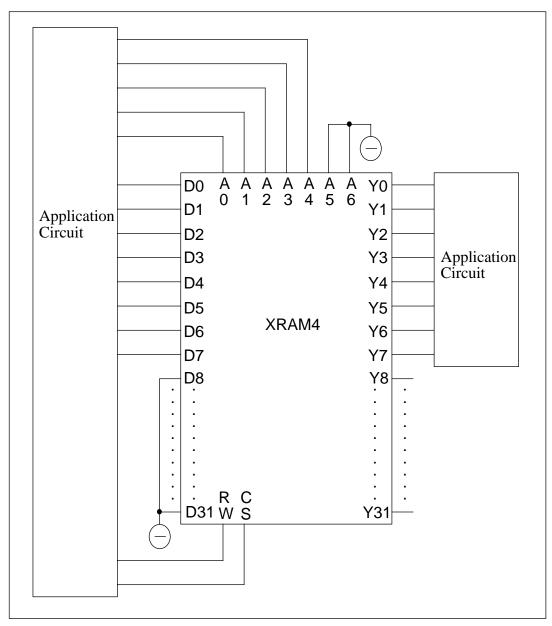

| 5.2 RAM Configuration and Simulation Model Selection                                        |      |

| 5.3 RAM Size                                                                                |      |

| 5.4 Investigating RAM Placement on Master Slice                                             |      |

| 5.5 Explanation of Functions                                                                |      |

| 5.6 Delay Parameters                                                                        | . 38 |

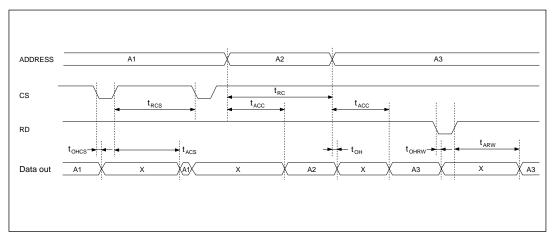

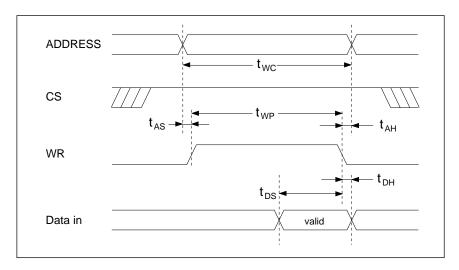

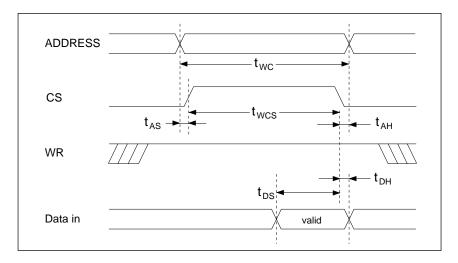

| 5.7 Timing Charts                                                                           |      |

| 5.8 RAM Test Method                                                                                       | .49  |

|-----------------------------------------------------------------------------------------------------------|------|

| 5.9 Estimating RAM Current Consumption                                                                    | .49  |

| 5.10 RAM Symbols and How They are Used                                                                    | .49  |

| Chapter C. Circuit Design Taking Testshility Into Assount                                                 | E 4  |

| Chapter 6 Circuit Design Taking Testability Into Account                                                  |      |

| 6.1 Considerations Regarding Circuit Initialization                                                       |      |

| <ul><li>6.2 Considerations Regarding Compressing the Test Patterns</li><li>6.3 RAM Test Circuit</li></ul> |      |

| 6.3.1 RAM Test Patterns                                                                                   |      |

| 6.4 Function Cell Test Circuits                                                                           |      |

| 6.4.1 Test Circuit Structures                                                                             |      |

| 6.4.2 Test Patterns                                                                                       |      |

| 6.4.3 Test Circuit Data                                                                                   |      |

| 6.5 Test Circuit Which Simplifies AC and DC Testing                                                       |      |

|                                                                                                           |      |

| Chapter 7 Propagation Delay and Timing                                                                    |      |

| 7.1 Simple Delay Models                                                                                   |      |

| 7.2 Load Due to Input Capacitance (Load A)                                                                |      |

| 7.3 Load Due to Interconnect Capacitance (Load B)                                                         |      |

| 7.4 Propagation Delay Calculations                                                                        |      |

| 7.5 Calculating Output Buffer Delay                                                                       |      |

| 7.6 Sequential Cell Setup/Hold Time                                                                       |      |

| 7.7 Chip Internal Skew                                                                                    | .75  |

| Chapter 8 Test Pattern Generation                                                                         | 76   |

| 8.1 Testability Considerations                                                                            | .76  |

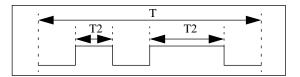

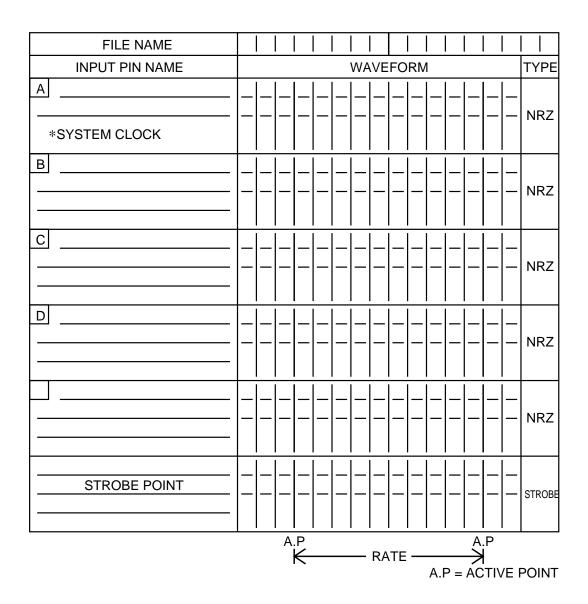

| 8.2 Waveform Types                                                                                        | .76  |

| 8.3 Constraints on the Types of Test Patterns                                                             | .77  |

| 8.3.1 Test Period                                                                                         | . 77 |

| 8.3.2 Input Delay                                                                                         | . 77 |

| 8.3.3 Pulse Width                                                                                         |      |

| 8.3.4 Input Waveform Format                                                                               | . 78 |

| 8.3.5 Strobe                                                                                              |      |

| 8.4 Notes Regarding DC Testing                                                                            |      |

| 8.5 Notes Regarding the Use of Oscillation Circuits                                                       |      |

| 8.6 Regarding AC Testing                                                                                  | .81  |

| 8.6.1 Constraints Regarding Measurement Events                                                            |      |

| 8.6.2 Constraints on the Measurement Locations for AC Testing                                             |      |

| 8.6.3 Constraints Regarding the Path Delay Which is Tested                                                |      |

| 8.6.4 Other Constraints                                                                                   |      |

| 8.7 Test Pattern Constraints for Bi-directional Terminals                                                 | .82  |

| Chapter 9 Estimating the Power Consumption                                                                | 83   |

| 9.1 Calculating the Power Consumption                                                                     | .83  |

| 9.2 Constraints on Power Consumption                                                                      | .86  |

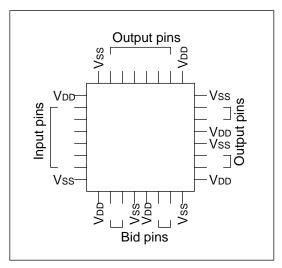

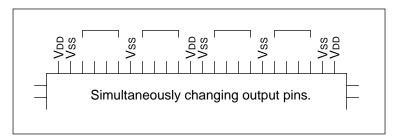

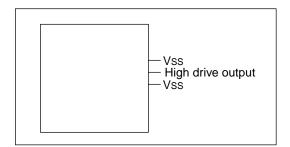

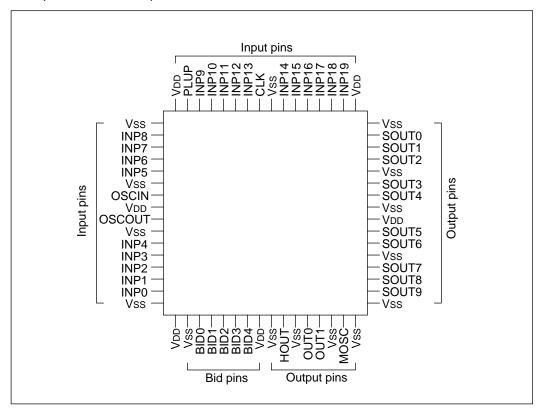

| Chapter 10 Pin Layout Considerations                                                                      | 87   |

| 10.1 Estimating the Number of Power Supply Terminals                                                      |      |

| 10.2 Number of Simultaneous Operations and Adding Power Supplies                                          |      |

| 10.3 Cautions and Notes Regarding the Layout of Terminals                                                 |      |

| 10.3.1 Fixed Power Supply Pins                                                                            |      |

| 10.3.2 Cautions and Notes Regarding the Pin Layout                                                        |      |

| 10.3.3 Examples of Recommended Pin Connections                                                            |      |

# Chapter 1 Overview

The S1L35000 Series is a family of ultra high-speed VLSI CMOS gate arrays utilizing a 0.6 micron "sea-of-gates" architecture.

# 1.1 Features of the S1L35000 Series

| <ul> <li>Integration</li> </ul>     | A Max. of 161,841 gates<br>(2 input NAND gate equivalent)                                                                                                                                                                                                                          |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Operating Speed</li> </ul> | Internal gates:0.30 ns (5.0 V Typ.), 0.4 ns (3.3 V Typ.)<br>(2-input power NAND, F/O = 2, AI = 2 mm)<br>Input buffer: 0.48 ns (5.0 V Typ.), 0.63 ns (3.3 V Typ.)<br>(F/O = 2, AI = 2 mm)<br>Output buffer: 2.08 ns (5.0 V Typ.), 2.86 ns (3.3 V Typ.)<br>( $C_L = 50 \text{ pF}$ ) |

| Process                             | CMOS 0.6 µm AI 3 interconnect layers                                                                                                                                                                                                                                               |

| <ul> <li>I/F Levels</li> </ul>      | Input/Output TTL/CMOS compatible                                                                                                                                                                                                                                                   |

| <ul> <li>Input Modes</li> </ul>     | TTL, CMOS, TTL Schmitt, CMOS Schmitt                                                                                                                                                                                                                                               |

|                                     | Pull-up and pull-down resistors can be equipped internally (2 types for each resistor value)                                                                                                                                                                                       |

| <ul> <li>Output Modes</li> </ul>    | Normal, 3-state, bi-directional                                                                                                                                                                                                                                                    |

| <ul> <li>Output Drive</li> </ul>    | I <sub>OL</sub> = 1, 4, 8, 12 mA, selectable (at 5.0 V)                                                                                                                                                                                                                            |

|                                     | I <sub>OL</sub> = 0.5, 2, 4, 6 mA, selectable (at 3.3V)                                                                                                                                                                                                                            |

| • RAM                               | Asynchronous 1-port, asynchronous 2-port                                                                                                                                                                                                                                           |

# 1.2 Master Structure of the S1L35000 Series

The S1L35000 Series comprises 4 types of masters, from which the customer is able to select the master most suitable.

| Master   | BC Total | Number<br>of Pads | Number<br>of Columns<br>(X) | Number<br>of Rows<br>(Y) | Cell use ratio<br>(U) *1 |

|----------|----------|-------------------|-----------------------------|--------------------------|--------------------------|

| S1L35043 | 41417    | 110               | 499                         | 83                       | 65%                      |

| S1L35063 | 64320    | 130               | 480                         | 134                      | 60%                      |

| S1L35093 | 95760    | 162               | 570                         | 168                      | 55%                      |

| S1L35163 | 161841   | 210               | 739                         | 219                      | 50%                      |

| Table 1-1 | Overview of the S1L35000 Series |

|-----------|---------------------------------|

|-----------|---------------------------------|

NOTE: \*1: This is the value when there are no cells, such as RAM cells. The cell use effciency is dependent not only on the scope of the circuits, but also on the number of signals, the number of branches per signal, etc.; thus, use the values in this table only as an estimate.

# 1.3 Electrical Characteristics and Specifications of the S1L35000 Series

Table 1-2 S1L35000 Absolute Max. Ratings  $(V_{ss} = 0 V)$

| Item                 | Symbol           | Limits                        | Unit |

|----------------------|------------------|-------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  | -0.3 to 6.0                   | V    |

| Input Voltage        | VI               | -0.3 to V <sub>DD</sub> + 0.5 | V    |

| Output Voltage       | V <sub>O</sub>   | -0.3 to V <sub>DD</sub> + 0.5 | V    |

| Output Current/Pin   | I <sub>OUT</sub> | ± 25                          | mA   |

| Storage Temperature  | T <sub>STG</sub> | -65 to 150                    | °C   |

# Table 1-3 Recommended Operating Conditions for the S1L35000 Series(For Single Power Supplies)

| Item                       | Symbol          | Min.            | Тур. | Max.            | Unit |

|----------------------------|-----------------|-----------------|------|-----------------|------|

|                            |                 | 2.70            | 3.00 | 3.30            |      |

| Power Supply Voltage       | V <sub>DD</sub> | 3.00            | 3.30 | 3.60            | v    |

| Tower Supply Voltage       | •00             | 4.75            | 5.00 | 5.25            | v    |

|                            |                 | 4.50            | 5.00 | 5.50            |      |

| Input Voltage              | VI              | V <sub>SS</sub> |      | V <sub>DD</sub> | V    |

|                            | Topr            | 0               | 25   | 70              | °C   |

| Operating Temperature      |                 | -40             | 25   | 85              | °C   |

| Normal Input Rising Time   | t <sub>ri</sub> |                 |      | 50              | ns   |

| Normal Input Falling Time  | t <sub>fa</sub> |                 |      | 50              | ns   |

| Schmitt Input Rising Time  | t <sub>ri</sub> |                 |      | 5               | ms   |

| Schmitt Input Falling Time | t <sub>fa</sub> |                 |      | 5               | ms   |

# Table 1-4 Electrical Characteristics of the S1L35000 Series (V<sub>DD</sub> = 5 V, V<sub>SS</sub> = 0 V, Ta = -40 to $85^{\circ}$ C)

| Item                                 | Item Symbol Conditions |                                                                                                               | Min.     | Тур.      | Max.       | Unit |

|--------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|----------|-----------|------------|------|

| Quiescent Current                    | I <sub>DDS</sub>       | Quiescent Conditions                                                                                          |          |           | 400        | μA   |

| Input Leakage Current                | ILI                    |                                                                                                               |          |           | 1          | μA   |

| Off State Leakage Current            | I <sub>OZ</sub>        |                                                                                                               |          |           | 1          | μA   |

| High Level Output Voltage            | V <sub>OH</sub>        | I <sub>OH</sub> = -1 mA (Type M), -4 mA (Type 1)<br>-8 mA (Type 2), -12 mA (Type 3)<br>V <sub>DD</sub> = Min. |          |           |            | V    |

| Low Level Output Voltage             | V <sub>OL</sub>        | I <sub>OL</sub> = 1 mA (Type M), 4 mA (Type 1),<br>8 mA (Type 2), 12 mA (Type 3)<br>V <sub>DD</sub> = Min.    |          |           | 0.4        | V    |

| High Level Input Voltage             | V <sub>IH1</sub>       | CMOS Level, V <sub>DD</sub> = Max.                                                                            | 3.5      |           |            | V    |

| Low Level Input Voltage              | V <sub>IL1</sub>       | CMOS Level, V <sub>DD</sub> = Min.                                                                            |          |           | 1.0        | V    |

| High Level Input Voltage             | V <sub>T1+</sub>       | CMOS Schmitt, V <sub>DD</sub> = 5.0 V                                                                         |          |           | 4.0        | V    |

| Low Level Input Voltage              | V <sub>T1-</sub>       | CMOS Schmitt, V <sub>DD</sub> = 5.0 V                                                                         |          |           |            | V    |

| Hysteresis Voltage                   | V <sub>H1</sub>        | CMOS Schmitt, V <sub>DD</sub> = 5.0 V                                                                         |          |           |            | V    |

| High Level Input Voltage             | V <sub>IH2</sub>       | TTL Level, V <sub>DD</sub> = Max.                                                                             |          |           |            | V    |

| Low Level Input Voltage              | V <sub>IL2</sub>       | TTL Level, V <sub>DD</sub> = Min.                                                                             |          |           | 0.8        | V    |

| High Level Input Voltage             | V <sub>T2+</sub>       | TTL Schmitt, V <sub>DD</sub> = 5.0 V                                                                          |          |           | 2.4        | V    |

| Low Level Input Voltage              | V <sub>T2-</sub>       | TTL Schmitt, V <sub>DD</sub> = 5.0 V                                                                          | 0.6      |           |            | V    |

| Hysteresis Voltage                   | V <sub>H2</sub>        | TTL Schmitt, V <sub>DD</sub> = 5.0 V                                                                          | 0.1      |           |            | V    |

| Pull-up Resistance                   | R <sub>PU</sub>        | V <sub>I</sub> = 0 V<br>Type 1<br>Type 2                                                                      | 25<br>50 | 50<br>100 | 100<br>200 | kΩ   |

| Pull-down Resistance                 | R <sub>PD</sub>        | V <sub>I</sub> = V <sub>DD</sub> Type 1<br>Type 2                                                             | 25<br>50 | 50<br>100 | 100<br>200 | kΩ   |

| Input Terminal Capacitance           | CI                     | $f = 1 MHz, V_{DD} = 0 V$                                                                                     |          |           | 12         | pF   |

| Output Terminal Capacitance          | Co                     | $f = 1 MHz, V_{DD} = 0 V$                                                                                     |          |           | 12         | pF   |

| Input/Output Terminal<br>Capacitance | C <sub>IO</sub>        | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                              |          |           | 12         | pF   |

# Table 1-5 Electrical Characteristics of the S1L35000 Series (V<sub>DD</sub> = 3 V $\pm$ 0.3 V, V<sub>SS</sub> = 0 V, Ta = -40 to 85 <sup>o</sup>C)

| Item                                 | Symbol           | Conditions                                                                                                         | Min. | Тур. | Max. | Unit |

|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Quiescent Current                    | I <sub>DDS</sub> | Quiescent Conditions                                                                                               |      |      | 260  | μA   |

| Input Leakage Current                | ILI              |                                                                                                                    | -1   |      | 1    | μA   |

| Off State Leakage Current            | I <sub>OZ</sub>  |                                                                                                                    | -1   |      | 1    | μA   |

| High Level Output Voltage            | V <sub>OH</sub>  | I <sub>OH</sub> = -0.5 mA (Type M), -1.8 mA (Type 1)<br>-3.5 mA (Type 2), -5 mA (Type 3)<br>V <sub>DD</sub> = Min. |      |      |      | V    |

| Low Level Output Voltage             | V <sub>OL</sub>  | I <sub>OL</sub> = 0.5 mA (Type M),1.8 mA (Type 1),<br>3.5 mA (Type 2), 5 mA (Type 3)<br>V <sub>DD</sub> = Min.     |      |      | 0.3  | V    |

| High Level Input Voltage             | V <sub>IH1</sub> | CMOS Level, V <sub>DD</sub> = Max.                                                                                 | 2.0  |      |      | V    |

| Low Level Input Voltage              | V <sub>IL1</sub> | CMOS Level, V <sub>DD</sub> = Min.                                                                                 |      |      | 0.8  | V    |

| High Level Input Voltage             | V <sub>T1+</sub> | CMOS Schmitt, V <sub>DD</sub> = 3.0 V                                                                              |      |      | 2.3  | V    |

| Low Level Input Voltage              | V <sub>T1-</sub> | CMOS Schmitt, V <sub>DD</sub> = 3.0 V                                                                              |      |      |      | V    |

| Hysteresis Voltage                   | V <sub>H1</sub>  | CMOS Schmitt, V <sub>DD</sub> = 3.0 V                                                                              |      |      |      | V    |

| Pull-up Resistance                   | R <sub>PU</sub>  | V <sub>I</sub> = 0 V                                                                                               | 50   | 100  | 200  | kΩ   |

|                                      |                  | Type 2                                                                                                             | 100  | 200  | 400  | 1122 |

| Pull-down Resistance                 | R <sub>PD</sub>  | $V_{O} = V_{DD}$ Type 1                                                                                            | 50   | 100  | 200  | kΩ   |

| Full-down Resistance                 | TYPD             | Type 2                                                                                                             | 100  | 200  | 400  | K22  |

| Input Terminal Capacitance           | Cl               | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                   |      |      | 12   | pF   |

| Output Terminal Capacitance          | Co               | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                   |      |      | 12   | pF   |

| Input/Output Terminal<br>Capacitance | C <sub>IO</sub>  | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                   |      |      | 12   | pF   |

# Table 1-6 Electrical Characteristics of the S1L35000 Series (V<sub>DD</sub> = $3.3 \text{ V} \pm 0.3 \text{ V}$ , V<sub>SS</sub> = 0 V, Ta = -40 to 85 <sup>o</sup>C)

| Item                                 | Symbol           | Conditions                                                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Quiescent Current                    | I <sub>DDS</sub> | Quiescent Conditions                                                                                            |      |      | 290  | μA   |

| Input Leakage Current                | ILI              |                                                                                                                 | -1   |      | 1    | μA   |

| Off State Leakage Current            | I <sub>OZ</sub>  |                                                                                                                 | -1   |      | 1    | μA   |

| High Level Output Voltage            | V <sub>OH</sub>  | I <sub>OH</sub> = -0.5 mA (Type M), -2 mA (Type 1),<br>-4 mA (Type 2), -6 mA (Type 3)<br>V <sub>DD</sub> = Min. |      |      |      | V    |

| Low Level Output Voltage             | V <sub>OL</sub>  | I <sub>OL</sub> = 0.5 mA (Type M),2 mA (Type 1),<br>4 mA (Type 2), 6 mA (Type 3)<br>V <sub>DD</sub> = Min.      |      |      | 0.3  | V    |

| High Level Input Voltage             | V <sub>IH1</sub> | CMOS Level, V <sub>DD</sub> = Max.                                                                              | 2.2  |      |      | V    |

| Low Level Input Voltage              | V <sub>IL1</sub> | CMOS Level, V <sub>DD</sub> = Min.                                                                              |      |      | 0.8  | V    |

| High Level Input Voltage             | V <sub>T1+</sub> | CMOS Schmitt, V <sub>DD</sub> = 3.3 V                                                                           |      |      | 2.4  | V    |

| Low Level Input Voltage              | V <sub>T1-</sub> | CMOS Schmitt, V <sub>DD</sub> = 3.3 V                                                                           |      |      |      | V    |

| Hysteresis Voltage                   | V <sub>H1</sub>  | CMOS Schmitt, V <sub>DD</sub> = 3.3 V                                                                           |      | -    |      | V    |

| Pull-up Resistance                   | R <sub>PU</sub>  | V <sub>1</sub> = 0 V                                                                                            | 45   | 90   | 180  | kΩ   |

|                                      | 1.10             | Туре 2                                                                                                          | 90   | 180  | 360  | 132  |

| Pull-down Resistance                 | R <sub>PD</sub>  | V <sub>I</sub> = V <sub>DD</sub> Type 1                                                                         | 45   | 90   | 180  | kΩ   |

|                                      |                  | Type 2                                                                                                          | 90   | 180  | 360  | K22  |

| Input Terminal Capacitance           | Cl               | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                |      |      | 12   | pF   |

| Output Terminal Capacitance          | Co               | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                |      |      | 12   | pF   |

| Input/Output Terminal<br>Capacitance | C <sub>IO</sub>  | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                |      |      | 12   | pF   |

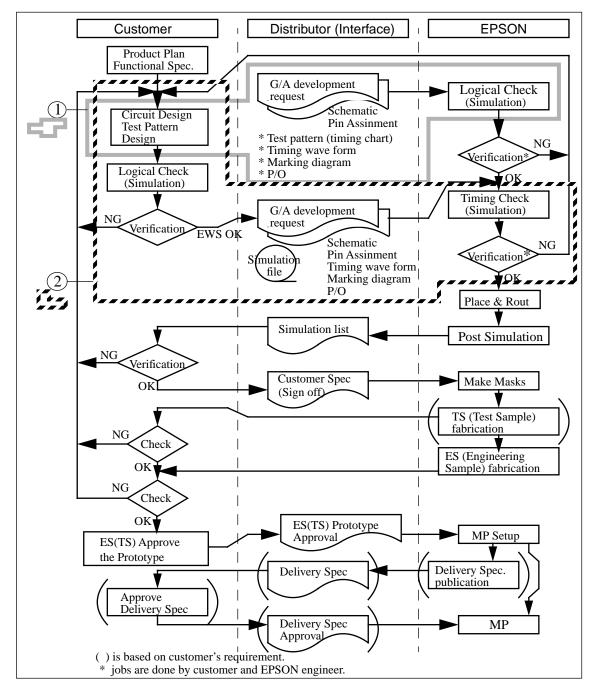

# 1.4 Overview of Gate Array Development Flow

Gate arrays are developed jointly by the customer and EPSON. System design, circuit design, and test pattern design is performed by the customer, based on various reference materials, including the cell libraries provided to the customer by EPSON.

Various modes of interface, listed below, are possible between the customer and EPSON during design, depending on the stage in gate array development wherein the customer interfaces with EPSON.

When interfacing with EPSON, the customer is to provide the necessary data and documents to EPSON.

The customer performs schematic capture, logic synthesis and simulation using EDA software and Auklet\* supported by EPSON. Place and route is performed by EPSON. Both the customer and EPSON are responsible for final sign-off simulations.

Note) \*: Auklet is the EPSON's ASIC desgin support system that can run on a personal computer- OS : MS-Windows 95/98, NT platform.

The simulation is currently supported by the following EDA software:

- Verilog-XL (\*1)

- VSS (\*2)

- ModelSim (\*3)

Note) \*1 : Verilog-XL is a registered trademark of Cadence Desgin Systems Corporation, USA.

- \*2 : VSS is a registered trademark of Synopsys Inc., USA.

- \*3 : ModelSim is a registered trademark of Model Technology Corp., USA.

For more information, refer to the Gate Array Technical Guide or contact to our sales office for technical support.

The process flow of the gate array development process is shown below:

NOTE: When the customer performs all tasks to the point of logical simulations and delay simulations on engineering workstations, etc., the route taken is (2). When EPSON performs the logical simulations, the route taken is (1).

# Chapter 2 Estimating Gate Density and Selecting the Master

Methods and guidelines are described below to assist in defining the logic which will be integrated into a gate array, estimating the array requirements, and determining the appropriate master for a given application.

# 2.1 Dividing up Logic between Chips

When extracting logic, which is to be integrated into gate arrays from the system being created by the user, the logic should be selected with the following criteria in mind.

• Integration Criteria

- (1) Quantity of logic to integrate

- (2) Quantity of input, output and bi-directional signals required

- (3) Package to be used

- (4) Power consumption

Generally, the larger the gate density, the more power is consumed, and the more input and output terminals required. Because of this, it may be better, from the perspective of total cost or from the perspective of power consumption, etc., to divide the circuit into multiple chips, rather than forcing them into a single chip.

# 2.2 Determining Gate Density

In the case of gate arrays, the scope of the array is defined as the sum of gates or basic cells (BCs) used. One gate or basic cell is typically defined as being equivalent to one two-input NAND gate (or four transistors). The "Gate Array S1L35000 Series MSI Cell Library" can be used as reference to facilitate gate count estimation.

# 2.3 Estimating the Number of Input/Output Terminals

Defining the number of I/O signals, test signals and power pins required for a given application has a bearing on the array member suitable for that application. The appropriate number of I/O pads must be available on the array member to satisfy the application signal requirements. Estimate the number of power supply pins using the method discussed in Chapter 10.

# 2.4 Selecting the Master

Select the appropriate master from the CMOS Device Catalog S1L35000 Series tables, based on the estimated number of BCs, the number of required input and output pins (including power supply pins) and the package to be used.

The actual number of BCs ( $BC_A$ ) which can be used for each device type is estimated using the following formula from the gross number of BCs ( $BC_G$ ) loaded on each master (shown in Table 1-1 of the previous chapter) and the cell utilization ratio (U).

$$BC_A = U \times BC_G$$

where U = 0.50 to 0.65

NOTE: When a RAM circuit is included, this estimate should be made after referring to the following section and after referring to Chapter 5.

# 2.5 Estimating the BCs That can be Used in Circuits Which Include RAM

RAM blocks, in comparison to MSI cells, are extremely large and have fixed shapes (defined vertical and horizontal dimensions). Because of this, some RAM blocks which may appear to fit on the chip because of calculations based on the number of BCs may, in actuality, not be placable on a given master. Thus, the first decision is that of whether or not the RAM configuration is available on a given master. Please refer to Chapter 5.

Once the masters which can accommodate the RAM have been selected, it becomes possible to estimate the number of BCs ( $BC_{AWR}$ ) of random logic (excluding RAM) available using the formula below.

$BC_{AWR} = 0.9 \times U \times (BC_G - BC_{RAM})$

- where  $BC_{AWR}$  is the number of BCs available for random logic  $BC_G$  is the gross BCs available on a mater (raw gates)  $BC_{RAM}$  is the BC use of RAM(s) (See Chapter 5 for BC calculation) U is the utilization ratio

- NOTE: Actual BCs available (BC<sub>AWR</sub>) is design dependent. Use the formula above for estimation purposes only. Please consult EPSON for design specific information.

# Chapter 3 Cautions and Notes Regarding Circuit Design

# 3.1 Inserting Input/Output Buffers

When designing your circuit using gate arrays, always be sure to use input/output buffers to exchange signals with external devices. Due to CMOS IC's extreme vulnerability to electrical static discharge (ESD), protection circuitry has been incorporated within the input/output buffers. In addition, due to limitations on chip layout, be sure to insert input or output buffers between external terminals and internal cells.

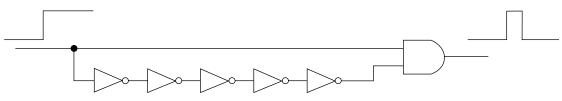

# 3.2 The Use of Differentiating Circuits is Forbidden

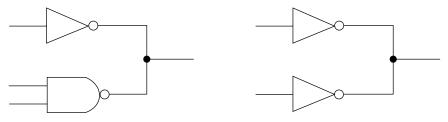

In LSIs, the propagation delay (tpd) of each gate varies depending on process variance during mass production and on the operating environment. Therefore, depending on the process dispersions and operating conditions, differentiating circuits using the relative time difference of tpd, like the one shown in Figure 3-1, may not be able to obtain a sufficient pulse width, causing the circuit to operate erratically.

When using a differentiating circuit, be sure to use one that utilizes flip-flops, and not the one shown in Figure 3-1.

Figure 3-1 Example of a Differentiating Circuit

# 3.3 Wired Logic is Forbidden

Because the S1L35000 uses CMOS transistors, wired logic as in bipolar transistors cannot be configured. Consequently, cell output terminals cannot be wired together, as shown in Figure 3-2. It is only in a bus-circuit configuration that output terminals can be connected together.

Figure 3-2 Example of Forbidden Wired Logic

# 3.4 Hazard Countermeasures

In circuits or decoder cells configured by combining gates such as NAND or NOR gates, an extremely short pulse may be generated due to the difference in delay times between gates. This short pulse is known as a "hazard" and, when fed into the clock or reset terminals of flip-flops, causes malfunction.

Therefore, circuits in which such a hazard is likely to occur must be configured so as to prevent the hazard from propagating. Alternately, for decoders, it may be necessary to use one that has an enable terminal.

# 3.5 Fan-Out Constraints

The tpd of a logic gate is determined by the load capacitance of its output terminal. An excessively large load capacitance may not only cause the tpd to become large, but may also cause malfunction. Therefore, the output terminals of each logic gate are subject to limitations on the number of loads that can be connected. These are known as "fan-out constraints."

The input-terminal capacitance of each logic gate, on the other hand, tends to differ for each logic-gate input. The input capacitance of each logic gate, as referenced to the input capacitance of an inverter (INI) = 1, is known as the "fan-in."

In the design of your circuit, confirm that the sum total of fan-ins connected to the output terminals of each logic gate will not exceed the fan-out constraints of those output terminals.

Furthermore, for logic gates operating at high speed such as high-speed clock lines (fmax = 40 MHz or more), confirm that the output-terminal capacitance of those gates is approximately half of the fan-out constraints.

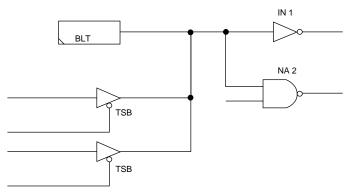

# 3.6 Bus Circuits

A bus circuit is configured with 3-state logic circuits, so that one of the outputs connected to the bus is driven active (while the other outputs are placed in the high-impedance state) by turning the bus control signals on or off. In this way, one transmission signal line on the bus is shared by dividing its use time.

Although bus circuits are very effective for logic design, note the following when using a bus circuit.

Notes Regarding the Use of Bus Circuits

- (1) Bus cells can only be used for bus circuits (for the S1L35000 series bus cells, see Table 3-1).

- (2) When using bus cells, add bus definition cells BLT to the bus when configuring your circuit.

- (3) Up to 32 bus cells can be connected to one length of bus.

- (4) Of the bus cells connected to one length of bus, only one output can be active (0 or 1) at one time, and all other bus-cell outputs must be placed in the high-impedance state (Z).

- (5) Even when all of the bus cells connected to one length of bus are in the high-impedance state (Z), data may be retained by a bus latch cell. However, leave the retained data floating, and do not use it as a logic signal.

- (6) In the creation of your test pattern, make sure the bus's initial state will be easily settled to provide improved testability. In addition, add one or more test terminals to make the bus easily controllable.

- (7) The bus control signals within the same event rate can be switched only once.

- (8) An excessive fan-out of the bus circuit may cause the propagation delay time to increase, making high-speed operation difficult.

The usable bus cells in the S1L35000 series are listed in Table 3-1.

|                                                      | Cell Name   |        |        |

|------------------------------------------------------|-------------|--------|--------|

| Cell Type                                            | 1 Bit       | 4 Bit  | 8 Bit  |

| Bus latches                                          | XBLT 1      | XBLT 4 | XBLT 8 |

| Bus drier                                            | XTSB, XTSBP | XT244H | XT244  |

| Inverting bus driver                                 | XTSV, XTSVP | XT240H | XT240  |

| Transparent latches with reset<br>and 3-state output | _           | ХТ373Н | XT373  |

| D-flip flops with rest and<br>3-state output         | _           | XT374H | XT374  |

| 1-bit RAM                                            | XRM1        | -      | _      |

Table 3-1 Table of S1L35000 Series Bus Cells

Figure 3-3 Typical Configuration of a Bus Cell Circuit

# 3.7 Schematic Capture Guidelines

Please adhere to the following conventions when designing an ASIC via manual schematic entry:

- Use logic cells found in Gate Array S1L35000 Series MSI Cell Library.

- Use orthogonal (not oblique) connections when wiring logic cells to one another.

- Primary uni-directional I/O and bi-directional I/O signal names must be 2 to 32 characters in length, and must begin with an alphabetic character.

# 3.8 Clock Tree Synthesis

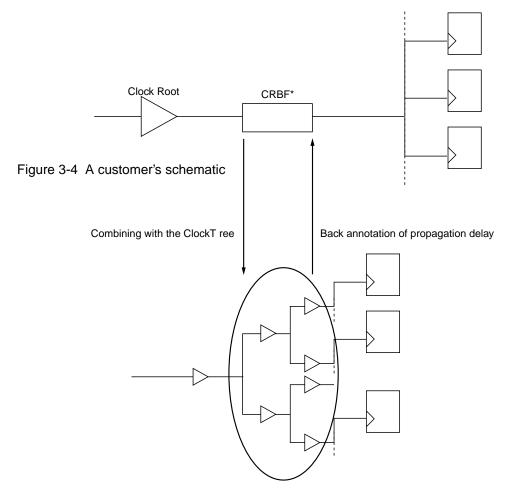

#### (1) Overview

Clock Tree Synthesis is a support that automatically inserts the ClockTree into the buffer group that optimizes the skew and delay time of "Clock Line". If a customer has a program to insert ClockTree to adjust the Fan-out of "ClockLine", clock skew may be large, so the P & R tool is started and the placing and routing for designing the gate array are executed voluntarily. Also, the propagation delay time may be longer than estimated because there are many cases it is difficult to maintain a good balance between the wire interconnecting load and the intrinsic cell delay. The Clock Tree Synthesis is used to solve this problem. Refer to the actual results to use the Clock Tree Synthesis as follows:

#### (2) How to Examine the Clock Tree Synthesis

When the clock tree is inserted automatically, the customer must insert the special buffer to the Clock Line for the following three purposes.

- Judging the place to insert the Clock Tree Synthesis.

- Estimating the delay time of the Clock Tree inserted and execute the simulation of virtual wire interconnecting level (pre-simulation).

- Back annotate the delay time of the inserted Clock Tree to accurately estimate the postsimulation.

Select the special buffer for the Clock Tree Synthesis in the table of special buffers mentioned later. Then insert the special buffer selected from the table into the Clock Line taking into consideration the restriction or notes mentioned later and the same placing as the normal cells. Otherwise, if the logic are designed by HDL, as the special buffer can not insert automatically the Clock Line, assign directly the HDL of the content using the script language. Note that another buffer is not combined in the clock Line inserted in the special buffer, and execute the following command:

set\_dont\_touch\_net net\_name

#### [The special buffer]

Select the special buffer from the table below corresponding to the estimated number of fan-outs.

| S1L9000F, S1L30000, S1L50000 Series |              |                             |  |

|-------------------------------------|--------------|-----------------------------|--|

| Cell Name                           | To Max. (ns) | Estimated number of fan-out |  |

| CRBF2                               | 2.00         | 0 to 500                    |  |

| CRBF3                               | 3.00         | 500 to 3000                 |  |

| CRBF4                               | 4.00         | 3000 to 10000               |  |

| CRBF5                               | 5.00         | Over 10000                  |  |

| CRBF6                               | 6.00         |                             |  |

| CRBF7                               | 7.00         |                             |  |

| CRBF8                               | 8.0          |                             |  |

| S1L35000 Series |              |                             |  |

|-----------------|--------------|-----------------------------|--|

| Cell Name       | To Max. (ns) | Estimated number of fan-out |  |

| XCRBF2          | 2.00         | 0 to 500                    |  |

| XCRBF3          | 3.00         | 500 to 3000                 |  |

| XCRBF4          | 4.00         | 3000 to 10000               |  |

| XCRBF5          | 5.00         | Over 10000                  |  |

| XCRBF6          | 6.00         |                             |  |

| XCRBF7          | 7.00         |                             |  |

| XCRBF8          | 8.0          |                             |  |

Note 1: The value "K" (load delay of fan-out) of these cells is set "0" at the pre-simulation.

Note 2: The number of fan-outs of these cells is set to the infinity.

Note 3: Please consider that the load delay for the number of fan-outs is not accurately and only estimated.

[Restriction and Notes]

- Target series: S1L9000F, S1L30000, S1L35000, S1L50000

- The special buffer can not be used for any purpose other than the Clock Tree Synthesis.

- The Clock Tree Synthesis can also be used for data line and other control signals. However, when the nets used in the synthesis are increased, the skew and propagation delay also became larger. Therefore, the number of nets to be used in the synthesis is less than 10 and the net which has a critical and large fan-out should be used.

- If a net which has a small fan-out is used for the Clock Tree Synthesis, the propagation delay and skew may be larger. The target net with fan-out should be used more than scores.

- As there are cases corresponding to the skew adjustment between multiple Clock lines, contact EPSON for handing in the detail schematic (the clock line configuration is described very clearly) to be checked.

- For the Clock group separated into multiple Clock Lines with the same Root of Clock by the gates, contact EPSON to obtain the materials of "Gated Clock Tree Synthesis Explanations".

[Necessary Information from a Customer]

Send the following information until the data is released, because the Clock Tree Synthesis is used efficiently.

| Instance name of CRBF* | Target skew value | Target propagation delay<br>(Min./Max.) |

|------------------------|-------------------|-----------------------------------------|

|                        |                   |                                         |

|                        |                   |                                         |

|                        |                   |                                         |

|                        |                   |                                         |

|                        |                   |                                         |

Note 1: The target values on the table are needed to estimate to use the Synthesis. The target values are not always satisfied.

Note 2: If there is no target values, write the comments for each item in the table. Example: As smaller as possible

#### [Imaging schematic]

The schematic created by a customer and the layout schematic after executing the Clock Tree Synthesis in EPSON are shown as follows:

Figure 3-5 Layout schematic after executing the Clock Tree Synthesis in EPSON

# 3.9 Restrictions and Constraints on VHDL/Verilog-HDL Netlist

The VHDL/Verilog-HDL net list to be interfaced to EPSON shall be a pure gate-level net list (not containing description of operation). The restrictions and constraints in developing EPSON ASIC using VHDL/Verilog HDL are as follows.

# 3.9.1 Common Restrictions and Constraints

- (1) Names of External Terminal (I/O Terminal)

- Use only upper-case letters.

- Number of characters: 2 to 32

- Usable characters : Alphanumeric characters and "\_." Use an alphabetical letter at the head.

- Examples of prohibited character strings :

2 INPUT : A digit is at the head.

\2INPUT : "\" is at the head.

InputA : Lower-case letters are included.

\_INPUTA : "\_" is at the head.

TNA[3:0] : A bus is used for the name of the external terminal.

INA[3] : A bus is used for the name of the external terminal.

- (2) Names of Internal Terminal (including bus net names)

- Upper-and lower-case letters can be used in combination, except the following. Combinations of the same words expressed in upper-and lower-case letters, such as "\_RESET\_" and "\_Reset\_."

- Number of characters : 2 to 32

- Usable characters :Alphanumeric characters, "\_," "\_[ ]\_" (Verilog bus blanket), and "\_()\_" (VHDL bus blanket) with an alphabetical letter at the head.

- (3) Bus description is prohibited at the most significant place of the module.

Examples: DATA [0:3], DATA [3], and DATA [2] are prohibited.DATA0, DATA1, and DATA2 are all allowed.

- (4) You can use I/O cells of the same library series, but cannot combine those of different series.

- (5) It is not possible to describe operations in behaviors or in the C language. Such descriptions existing in the net list are invalid.

- (6) Precision of the time scale of the library of each series is 1 ps.

# 3.9.2 Restrictions and Constraints for Verilog Netlist

- (7) Descriptions using the functions "assign" and "tran" are prohibited in the gate-level Verilog net list.

- (8) Descriptions of connection with cell pin names are recommended in the Verilog net list.

Example: Connection with pin names: IN2 inst\_1 (.A(inst\_2),.X(inst\_3)); Recommended Connection with net names: IN2 inst\_1(net1, net2):

- (9) You cannot use the Verilog command "force" as a description of flip-flop operation. (Example: force logic .singal = 0;)

- (10) The time scale description is added at the head of the gate-level net list generated by the Synopsys design compiler.

Set it at the value described in the EPSON Verilog library. See (6) for the time scale of each series.

Example: 'timescale 1ps/1ps

(11) EPSON prohibits combination of a bus single port name and a name that includes "\_\\_", such as the following, in the same module.

input A [0];

wire \A [0];

(12) The following letter strings are reserved for Verilog, which cannot be used as a user-defined name.

always, and, assign, begin, buf, bufif0, bufif1, case, design,default, defparam, disable, else, end, endcase, endfunction, endmodule, endtask, event, for, force, forever, fork, function, highz0, highz1, if, initial, inout, input, integer, join, large, medium, module, nand, negedge, nor, not, notif0, notif1, or, output, parameter, posedge, pull0, pull1, reg, release, repeat, scalared, small, specify, strong0, strong1, supply0, supply1, task, time, tri, tri0, tri1, trinand, trior, trireg, vectored, wait, wand, weak0, weak1, while, wire, wor, xor, xnor

#### 3.9.3 Restrictions and Constraints on VHDL Netlist

(13) In addition to the constraints in (1), the following letter strings are also prohibited.

INPUTA\_: "\_" is used at the end.INPUT\_\_A: "\_" is used twice or more in succession.read: Used in the system.write: Used in the system.

(14) The following letter strings are reserved for VHDL, which cannot be used as a user-defined name.

abs, access, after, alias, all, and, architecture, array, assert, attribute, begin, block, body, buffer, bus, case, component, configuration, constant, disconnect, downto, else, elsif, end, entity, exit, file, for, function, generate, generic, guarded, if, in, inout, is, label, library, linkage, loop, map, mod, nand, new, next, nor, not, null, of, on, open, or, others, out, package, port, procedure, process, range, record, register, rem, report, return, select, severity, signal, subtype, then, to, transport, type, units, until, use, variable, wait, when, while, with, xor

(15) To use EPSON utilities and tools, it is necessary to change the VHDL format into the Verilog format. Therefore, the letter strings reserved for Verilog in (12) are also prohibited.

# Chapter 4 Input/Out Buffer and Their Use

# 4.1 Types of Input/Output Buffer in the S1L35000 Series

Various I/O buffers types of the S1L35000 Series are available according to the input interface level, output drive capacity, use or no use of pull-up and pull-down resistors, and the pull-up and pull-down resistors. You can select the ones appropriate to your needs.

# 4.1.1 Selecting I/O Buffer

The S1L35000 series provides a wide range of input / output buffers. You can select buffer parameters, including input interface level, schmitt trigger input or not, output drive capabil-ity and a pull-up or pull-down resistance. This allows you to select the most suitable buffer for each application.b) Is a schmitt trigger input necessary? (Are hysteresis characteristics necessary?)

- (1) Selecting the Input Cell

- a) Is the required interface level a CMOS level or a TTL level?

- b) Is a schmitt trigger input necessary? (Are hysteresis characteristics necessary?)

- c) Is it necessary to add pull-up/pull-down resistors?

- (2) Selecting the Output Cell

- a) How much output current must be driven?( $I_{OL} / I_{OH}$ )

- b) Are noise countermeasures necessary?

- (3) Selecting Bi-directional Cells Select the bi-directional cells by examining both sets of criteria for selecting the input cells and selecting the output cells.

- I/O Interface Level

- 5.0V system single power supply Input level TTL level, CMOS level, TTL Schmitt, CMOS Schmitt Output level CMOS level

- 2) 3.0 V system single power supply Input level TTL Schmitt, CMOS Schmitt Output level CMOS level

- NOTE 1 :The 3.0 V/ 3.3 V system CMOS level is about the same value as the 5.0V system TTL level. When a single 3.0 / 3.3 V power supply is used, TTL level input cannot be used.

- Output Drive Capability See the electrical characteristics (Tables 1.4 to 1.6).

- Pull-up/Pull-down Resistance See the electrical characteristics (Tables 1.4 to 1.6).

Some I/O buffers of the S1L35000 series need to use a combination of I/O cells and internal interface cells.

The input buffer, output buffer, and bi-directional buffer configuration for single power supplies are expained in detail biginning with Section 4.2.

# 4.2 I/O Buffer Configurations with a Single Power Supply

When using a single power supply, the power supply voltage (V\_DD) may be either 5.0V, 3.3V or 3.0V.

Also, I/O buffer can be used either 5.0V, 3.3V or 3.0V. I/O buffer configurations with a single power supply either 3.0V or 5.0V are explained below.

#### 4.2.1 I/O Buffer Configurations with a Single 5.0V Power Supply

#### 4.2.1.1 Input Buffer Configurations with a Single 5.0V Power Supply

The input buffer function is structured of input cells only.

| Cell Name | Input Level  | Function | Pull-up/Pull-down Resistance                           |

|-----------|--------------|----------|--------------------------------------------------------|

| XIBT      | TTL          | Buffer   | None                                                   |

| XIBTP*    | TTL          | Buffer   | Pull-up resistance (50 k $\Omega$ , 100 k $\Omega$ )   |

| XIBTD*    | TTL          | Buffer   | Pull-down resistance (50 k $\Omega$ , 100 k $\Omega$ ) |

| XIBC      | CMOS         | Buffer   | None                                                   |

| XIBCP*    | CMOS         | Buffer   | Pull-up resistance (50 k $\Omega$ , 100 k $\Omega$ )   |

| XIBCD*    | CMOS         | Buffer   | Pull-down resistance (50 k $\Omega$ , 100 k $\Omega$ ) |

| XIBS      | TTL Schmitt  | Buffer   | None                                                   |

| XIBSP*    | TTL Schmitt  | Buffer   | Pull-up resistance (50 k $\Omega$ , 100 k $\Omega$ )   |

| XIBSD*    | TTL Schmitt  | Buffer   | Pull-down resistance (50 k $\Omega$ , 100 k $\Omega$ ) |

| XIBH      | CMOS Schmitt | Buffer   | None                                                   |

| XIBHP*    | CMOS Schmitt | Buffer   | Pull-up resistance (50 k $\Omega$ , 100 k $\Omega$ )   |

| XIBHD*    | CMOS Schmitt | Buffer   | Pull-down resistance (50 k $\Omega$ , 100 k $\Omega$ ) |

Table 4-1 Input Cell (combinations of I/O cells)

NOTE: When \* value is 1 or 2, pull-up/pull-down resistance values correspond to 1:50 k $\Omega$ ., 2:100 k $\Omega$  respectively.

#### 4.2.1.2 Output Buffer Configurations with a Single 5.0V Power Supply

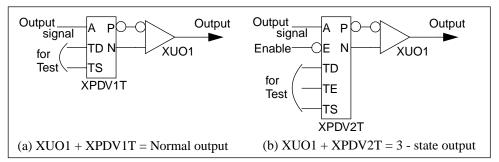

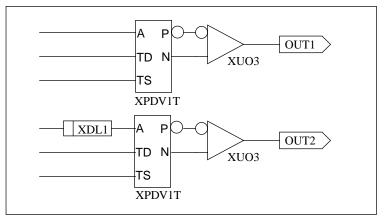

Please configure the output buffers using pre-drivers (such as XPDV1T, XPDV1AT, XPDV1BT, XPDV2T, XPDV2AT, XPDV2BT, etc.), and output cells (such as XUOM to XUO3). See Figure 4-1 for connectivity and reference Table 4-2 below regarding the pre-driver and output cell combinations.

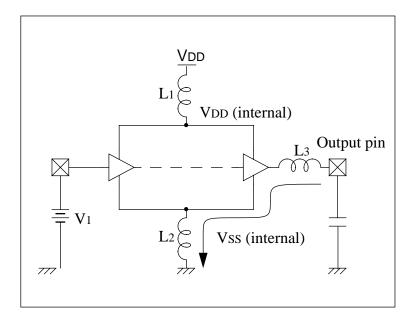

Figure 4-1 Examples of Pre-driver and Output Cell Configurations

| Function                              | I <sub>OL</sub> * / I <sub>OH</sub> ** | Cell Structure*** |

|---------------------------------------|----------------------------------------|-------------------|

| Normal output for low noise           | 1mA/-1mA                               | XUOM+XPDV1T       |

|                                       | 4mA/-4mA                               | XUO1+XPDV1T       |

|                                       | 8mA/-8mA                               | XUO2+XPDV1T       |

|                                       | 12mA/-12mA                             | XUO3+XPDV1T       |

| Normal output for high speed          | 1mA/-1mA                               | XUOM+XPDV1AT      |

|                                       | 4mA/-4mA                               | XUO1+XPDV1AT      |

|                                       | 8mA/-8mA                               | XUO2+XPDV1AT      |

|                                       | 12mA/-12mA                             | XUO3+XPDV1AT      |

| Normal output with slew rate control  | 1mA/-1mA                               | XUOM+XPDV1BT      |

|                                       | 4mA/-4mA                               | XUO1+XPDV1BT      |

|                                       | 8mA/-8mA                               | XUO2+XPDV1BT      |

|                                       | 12mA/-12mA                             | XUO3+XPDV1BT      |

| Normal output with slew rate control  | 12mA/-12mA                             | XUO3L+XPDV3T      |

| for falling edge only                 |                                        |                   |

| 3-state output for low noise          | 1mA/-1mA                               | XUOM+XPDV2T       |

|                                       | 4mA/-4mA                               | XUO1+XPDV2T       |

|                                       | 8mA/-8mA                               | XUO2+XPDV2T       |

|                                       | 12mA/-12mA                             | XUO3+XPDV2T       |

| 3-state output for high speed         | 1mA/-1mA                               | XUOM+XPDV2AT      |

|                                       | 4mA/-4mA                               | XUO1+XPDV2AT      |

|                                       | 8mA/-8mA                               | XUO2+XPDV2AT      |

|                                       | 12mA/-12mA                             | XUO3+XPDV2AT      |

| 3-state output with low slew rate     | 1mA/-1mA                               | XUOM+XPDV2BT      |

| control                               | 4mA/-4mA                               | XUO1+XPDV2BT      |

|                                       | 8mA/-8mA                               | XUO2+XPDV2BT      |

|                                       | 12mA/-12mA                             | XUO3+XPDV2BT      |

| 3-state output with slew rate control | 12mA/-12mA                             | XUO3L+XPDV4T      |

| for falling edge only                 |                                        |                   |

Table 4-2 Combinations of Pre-drivers and Output Cells

NOTES: \*  $V_{OL} = 0.4 \text{ V} (V_{DD} = 5.0 \text{ V})$

\*\*  $V_{OH} = V_{DD} - 0.4 V (V_{DD} = 5.0 V)$

\*\*\* In addition to the configurations in Table 4-2, the output buffers may be configured with pre-drivers which do not have test terminals. Customers desiring to use such structures should direct inquiries to EPSON.

As is shown in Table 4-2, the combination with XUO3L and XPDV3T can be output more than normal slew rate for falling edge only . Also, both XPDV1BT and XPDV2BT are output more than normal slew rate for falling and rising edges. Usually, they are used in combination with XUO3.

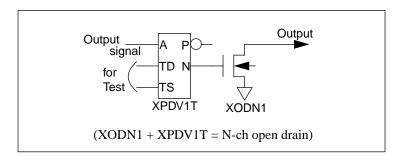

• XODN (Open Drain Output Cell) Usage

As is shown in Table 4-3, configure open drain output functionality using the XODNx output cell and pre-driver combinations with the N terminal connection only. Do not connect the P terminal of the pre-driver output. (See Figure 4-2)

Figure 4-2 Example of XODN Configuration

| Table 4-3 | Combinations of Pre-drivers and XODN Cell Usage |  |

|-----------|-------------------------------------------------|--|

|-----------|-------------------------------------------------|--|

| Function                     | I <sub>OL</sub> * | Cell Structure** |

|------------------------------|-------------------|------------------|

| Normal output for low noise  | 1mA               | XODNM+XPDV1T     |

|                              | 4mA               | XODN1+XPDV1T     |

|                              | 8mA               | XODN2+XPDV1T     |

|                              | 12mA              | XODN3+XPDV1T     |

| Normal output for high speed | 1mA               | XODNM+XPDV1AT    |

|                              | 4mA               | XODN1+XPDV1AT    |

|                              | 8mA               | XODN2+XPDV1AT    |

|                              | 12mA              | XODN3+XPDV1AT    |

| Normal output with slew rate | 12mA              | XODN3L+XPDV3T    |

| control                      |                   |                  |

NOTES: \*  $V_{OL}$  = 0.4 V ( $V_{DD}$  = 5 V)

\*\* In addition to the configurations on Table 4-3, the output buffers may be configured with pre-drivers which do not have test terminals. Customers desiring to use such structures should direct inquiries to EPSON.

#### 4.2.1.3 Bi-directional Buffer Configurations with a Single 5.0V Power Supply

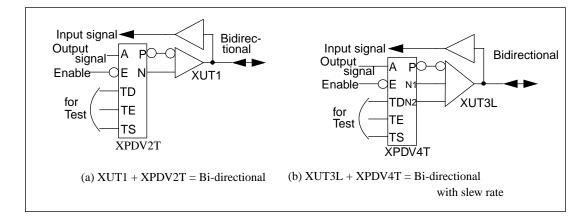

Bi-directional buffers are configured from combinations of pre-drivers (with enable terminals) and bi-directional cells. (See Figure 4-3.)

Figure 4-3 Examples of Pre-driver and Bi-directional Cell Configurations

| Input Level | Function                                                           | I <sub>OL</sub> */I <sub>OH</sub> **           | Cell Structure***                                            |

|-------------|--------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| TTL         | Bi-directional for low noise output                                | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUTM+XPDV2T<br>XUT1+XPDV2T<br>XUT2+XPDV2T<br>XUT3+XPDV2T     |

| TTL         | Bi-directional for high speed output                               | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUTM+XPDV2AT<br>XUT1+XPDV2AT<br>XUT2+XPDV2AT<br>XUT3+XPDV2AT |

| TTL         | Bi-directional with low slew rate control output                   | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUTM+XPDV2BT<br>XUT1+XPDV2BT<br>XUT2+XPDV2BT<br>XUT3+XPDV2BT |

| TTL         | Bi-directional with slew rate control output for falling edge only | 12mA/-12mA                                     | XUT3L+XPDV4T                                                 |

| CMOS        | Bi-directional for low noise output                                | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUCM+XPDV2T<br>XUC1+XPDV2T<br>XUC2+XPDV2T<br>XUC3+XPDV2T     |

| CMOS        | Bi-directional for high speed output                               | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUCM+XPDV2AT<br>XUC1+XPDV2AT<br>XUC2+XPDV2AT<br>XUC3+XPDV2AT |

| CMOS        | Bi-directional with low slew rate control output                   | 1mA/-1mA<br>4mA/-4mA<br>8mA/-8mA<br>12mA/-12mA | XUCM+XPDV2BT<br>XUC1+XPDV2BT<br>XUC2+XPDV2BT<br>XUC3+XPDV2BT |

| CMOS        | Bi-directional with slew rate control output for falling edge only | 12mA/-12mA                                     | XUC3L+XPDV4T                                                 |

| Table 4-4 Combinations of Pre- | rivers and Bi-directional Cells (1/2) |

|--------------------------------|---------------------------------------|

|--------------------------------|---------------------------------------|

| Input Level  | Function                              | I <sub>OL</sub> */I <sub>OH</sub> ** | Cell Structure |

|--------------|---------------------------------------|--------------------------------------|----------------|

| TTL Schmitt  | Bi-directional for low noise output   | 1mA/-1mA                             | XUSM+XPDV2T    |

|              |                                       | 4mA/-4mA                             | XUS1+XPDV2T    |

|              |                                       | 8mA/-8mA                             | XUS2+XPDV2T    |

|              |                                       | 12mA/-12mA                           | XUS3+XPDV2T    |

| TTL Schmitt  | Bi-directional for high speed output  | 1mA/-1mA                             | XUSM+XPDV2AT   |

|              |                                       | 4mA/-4mA                             | XUS1+XPDV2AT   |

|              |                                       | 8mA/-8mA                             | XUS2+XPDV2AT   |

|              |                                       | 12mA/-12mA                           | XUS3+XPDV2AT   |

| TTL Schmitt  | Bi-directional with low slew rate     | 1mA/-1mA                             | XUSM+XPDV2BT   |

|              | control output                        | 4mA/-4mA                             | XUS1+XPDV2BT   |

|              |                                       | 8mA/-8mA                             | XUS2+XPDV2BT   |

|              |                                       | 12mA/-12mA                           | XUS3+XPDV2BT   |

| TTL Schmitt  | Bi-directional with slew rate control | 12mA/-12mA                           | XUS3L+XPDV4T   |

|              | output for falling edge only          |                                      |                |

| CMOS Schmitt | Bi-directional for low noise output   | 1mA/-1mA                             | XUHM+XPDV2T    |

|              |                                       | 4mA/-4mA                             | XUH1+XPDV2T    |

|              |                                       | 8mA/-8mA                             | XUH2+XPDV2T    |

|              |                                       | 12mA/-12mA                           | XUH3+XPDV2T    |

| CMOS Schmitt | Bi-directional for high speed output  | 1mA/-1mA                             | XUHM+XPDV2AT   |

|              |                                       | 4mA/-4mA                             | XUH1+XPDV2AT   |

|              |                                       | 8mA/-8mA                             | XUH2+XPDV2AT   |

|              |                                       | 12mA/-12mA                           | XUH3+XPDV2AT   |

| CMOS Schmitt | Bi-directional with low slew rate     | 1mA/-1mA                             | XUHM+XPDV2BT   |

|              | control output                        | 4mA/-4mA                             | XUH1+XPDV2BT   |

|              |                                       | 8mA/-8mA                             | XUH2+XPDV2BT   |

|              |                                       | 12mA/-12mA                           | XUH3+XPDV2BT   |

| CMOS Schmitt | Bi-directional with slew rate control | 12mA/-12mA                           | XUH3L+XPDV4T   |

|              | output for falling edge only          |                                      |                |

#### Table 4-4 Combinations of Pre-drivers and Bi-directional Cells (2/2)

NOTES:  $* V_{OL} = 0.4 V (V_{DD} = 5.0 V)$

\*\*  $V_{OH} = V_{DD} - 0.4 V (V_{DD} = 5.0 V)$

\*\*\* In addition to the configurations in Table 4-4, bi-directional buffers may be configured with pre-drivers which do not have test terminals. Most bi-directional buffers have two types of pull-up resistance options and two types of pull-down resistance options. Customers desiring such should direct inquiries to EPSON.

# 4.2.2 I/O Buffer Configurations with a Single 3.0/3.3 V Power Supply

#### 4.2.2.1 Input Buffer Configurations with a Single 3.0/3.3 V Power Supply

| Cell Name | Input Level** | Function | Pull-up/Pull-down Resistance                           |

|-----------|---------------|----------|--------------------------------------------------------|

| XIBC      | CMOS          | Buffer   | None                                                   |

| XIBCP*    | CMOS          | Buffer   | Pull-up Resistance (90 kΩ, 180 kΩ)                     |

| XIBCD*    | CMOS          | Buffer   | Pull-down Resistance (90 k $\Omega$ , 180 k $\Omega$ ) |

| XIBH      | CMOS Schmitt  | Buffer   | None                                                   |

| XIBHP*    | CMOS Schmitt  | Buffer   | Pull-up Resistance (90 kΩ, 180 kΩ)                     |

| XIBHD*    | CMOS Schmitt  | Buffer   | Pull-down Resistance (90 k $\Omega$ , 180 k $\Omega$ ) |

#### Table 4-5 Input Cells

NOTES:When \* value is 1 or 2, pull-up/pull-down resistance values correspond to 1:90 kΩ., 2:180 kΩ respectively. \*\* In a 3.0 V/3.3 V single power supply TTL level input cannot be used.

#### XIDC (Input Cells)

The XIDC is a 5.0 V tolerant input buffer which can be used in a 3.0 V/3.3 V only ASIC application to satisfy mixed-voltage system requirements.

| Cell Name | Input Level | Function | Pull-up/Pull-down Resistance                           |

|-----------|-------------|----------|--------------------------------------------------------|

| XIDC      | TTL         | Buffer   | None                                                   |

| XIDCD*    | TTL         | Buffer   | Pull-down Resistance (90 k $\Omega$ , 180 k $\Omega$ ) |

| Table 4-6 Table of Input Level Shifter |

|----------------------------------------|

|----------------------------------------|

NOTE: When \* value is 1 or 2, pull-down resistance value correspond to 1:90 k $\Omega$  and 2:180 k $\Omega$  respectively.

#### 4.2.2.2 Output Buffer Configurations with a Single 3.0/3.3V Power Supply

When structuring the output buffer, use a combination of pre-drivers (such as XPDV1T, XPDV1AT, XPDV2T, XPDV2AT, etc.), which are structured of internal cells and output cells (such as XUOM to XUO3). See Table 4-7 below, regarding these combinations.

| Function                              | I <sub>OL</sub> */I <sub>OH</sub> ** | Cell Structure*** |

|---------------------------------------|--------------------------------------|-------------------|

| Normal output for low noise           | 0.5mA/-0.5mA                         | XUOM+XPDV1T       |

| · · · · · · · · · · · · · · · · · · · | 2mA/-2mA                             | XUO1+XPDV1T       |

|                                       | 4mA/-4mA                             | XUO2+XPDV1T       |

|                                       | 6mA/-6mA                             | XUO3+xPDV1T       |

| Normal output for high speed          | 0.5mA/-0.5mA                         | XUOM+XPDV1AT      |

|                                       | 2mA/-2mA                             | XUO1+XPDV1AT      |

|                                       | 4mA/-4mA                             | XUO2+XPDV1AT      |

|                                       | 6mA/-6mA                             | XUO3+XPDV1AT      |

| Normal output with low slew           | 0.5mA/-0.5mA                         | XUOM+XPDV1BT      |

| rate control                          | 2mA/-2mA                             | XUO1+XPDV1BT      |

|                                       | 4mA/-4mA                             | XUO2+XPDV1BT      |

|                                       | 6mA/-6mA                             | XUO3+XPDV1BT      |

| Normal output with slew rate          | 6mA/-6mA                             | XUO3L+XPDV3T      |

| control for fallling edge only        |                                      |                   |

| 3-state output for low noise          | 0.5mA/-0.5mA                         | XUOM+XPDV2T       |

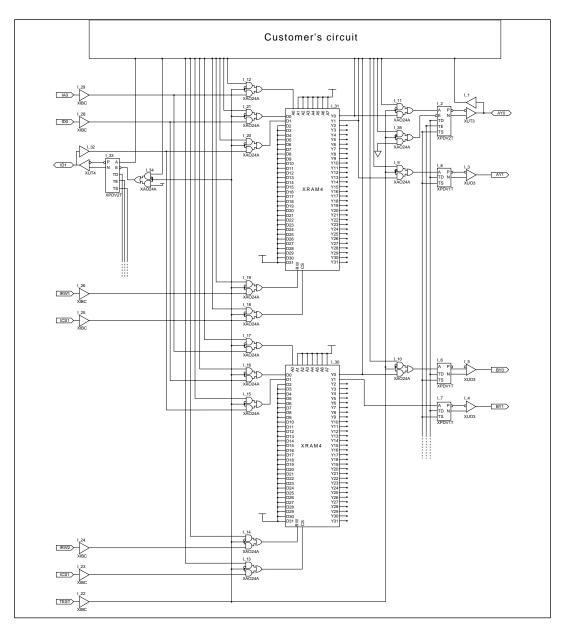

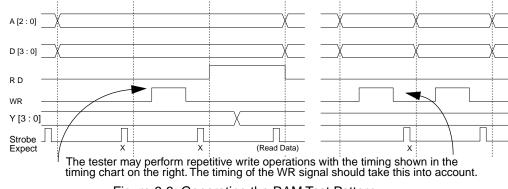

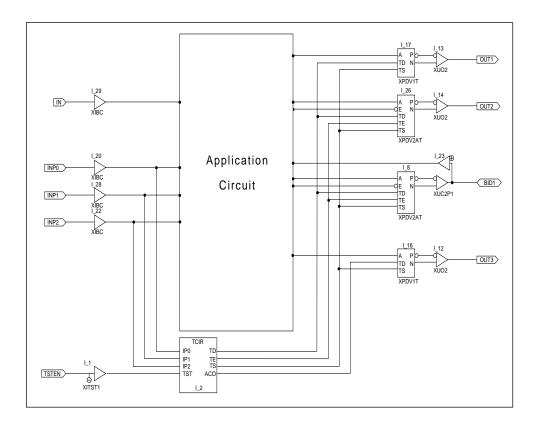

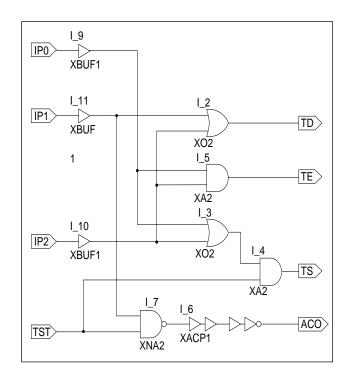

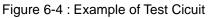

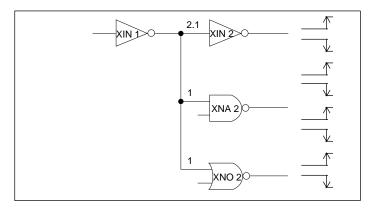

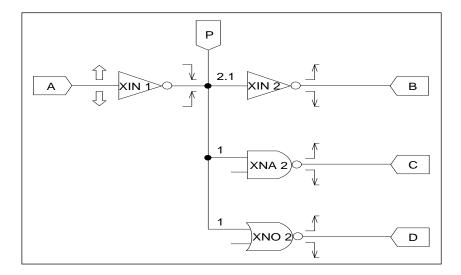

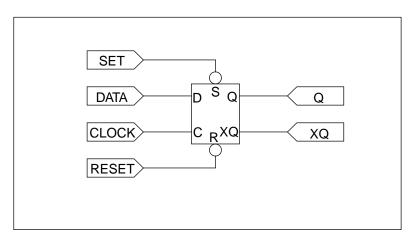

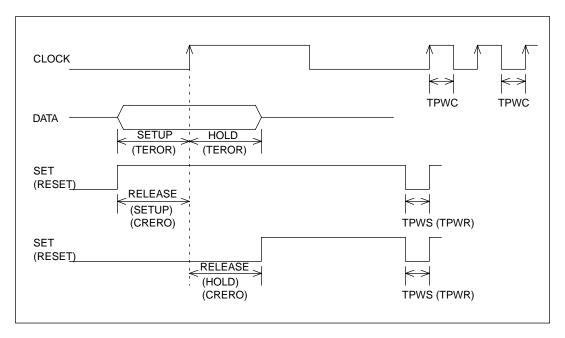

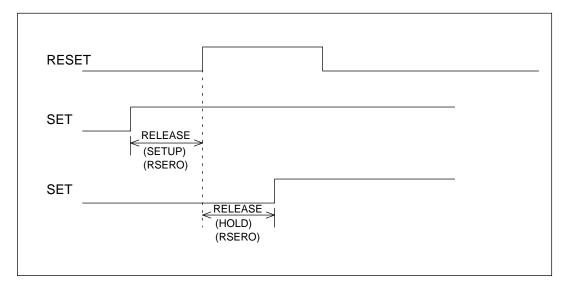

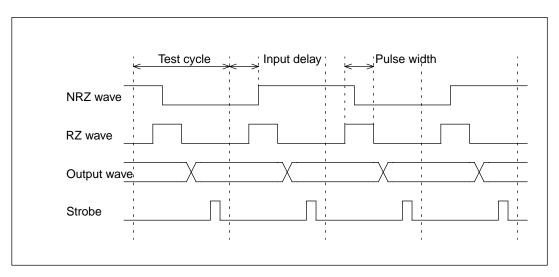

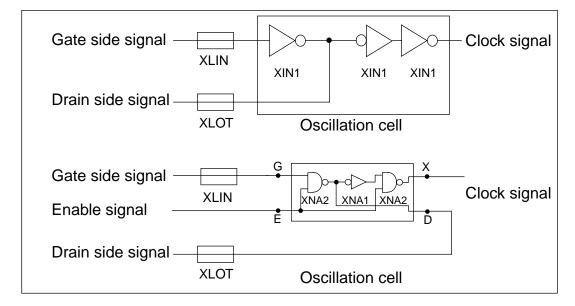

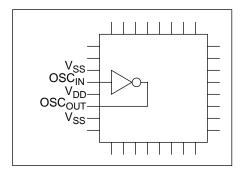

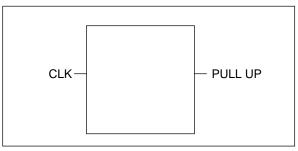

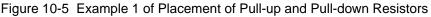

|                                       | 2mA/-2mA                             | XUO1+XPDV2T       |