# CMOS 8-BIT SINGLE CHIP MICROCOMPUTER **S1C88409** Technical Manual S1C88409 Technical Hardware

SEIKO EPSON CORPORATION

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

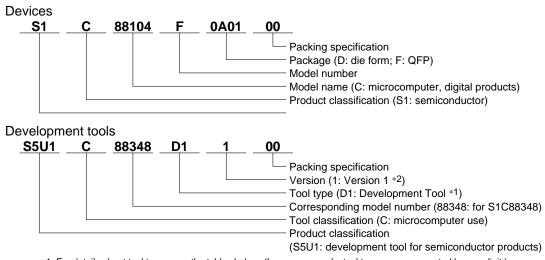

### The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

### Configuration of product number

\*1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

\*2: Actual versions are not written in the manuals.

### Comparison table between new and previous number

#### S1C88 Family processors

|              | •        |  |              |          |

|--------------|----------|--|--------------|----------|

| Previous No. | New No.  |  | Previous No. | New No.  |

| E0C88104     | S1C88104 |  | E0C88365     | S1C88365 |

| E0C88112     | S1C88112 |  | E0C88F360    | S1C8F360 |

| E0C88308     | S1C88308 |  | E0C88408     | S1C88408 |

| E0C88316     | S1C88316 |  | E0C88409     | S1C88409 |

| E0C88317     | S1C88317 |  | E0C88816     | S1C88816 |

| E0C88348     | S1C88348 |  | E0C88832     | S1C88832 |

| E0C88P348    | S1C8P348 |  | E0C88862     | S1C88862 |

| E0C88349     | S1C88349 |  | E0C88F816    | S1C8F816 |

### Comparison table between new and previous number of development tools

Development tools for the S1C88 Family

|              |              |   | ,            |              |  |

|--------------|--------------|---|--------------|--------------|--|

| Previous No. | New No.      |   | Previous No. | New No.      |  |

| 88ISAIF      | S5U1C88000H4 | Γ | DEV88816     | S5U1C88816D  |  |

| ADP88348     | S5U1C88348X  |   | DEV88832     | S5U1C88832D  |  |

| ADP88360     | S5U1C88360X  |   | DEV88862     | S5U1C88862D  |  |

| DEV88104     | S5U1C88104D  |   | DMT88348-DB  | S5U1C88348T  |  |

| DEV88112     | S5U1C88112D  |   | ICE88UR      | S5U1C88000H5 |  |

| DEV88308     | S5U1C88308D  |   | PRC88316     | S5U1C88316P  |  |

| DEV88316     | S5U1C88316D  |   | PRC88348     | S5U1C88348P  |  |

| DEV88317     | S5U1C88317D  |   | PRC88365     | S5U1C88365P  |  |

| DEV88348     | S5U1C88348D  |   | PRC88409     | S5U1C88409P  |  |

| DEV88365     | S5U1C88365D  |   | PRC88816     | S5U1C88816P  |  |

| DEV88408     | S5U1C88408D  |   | SAP88        | S5U1C88000S  |  |

| DEV88409     | S5U1C88409D  |   | URS88348     | S5U1C88348Y  |  |

#### Development tools for the S1C63/88 Family

| Previous No. | New No.      |

|--------------|--------------|

| ADS00002     | S5U1C88000X1 |

| GWH00002     | S5U1C88000W2 |

| URM00002     | S5U1C88000W1 |

### **CONTENTS**

| CHAPTER 1 | <b>O</b> U2 | TLINE                                                                       |    | 1  |

|-----------|-------------|-----------------------------------------------------------------------------|----|----|

|           | 1.1         | Features                                                                    | _  |    |

|           | 1.2         | Block Diagram                                                               |    |    |

|           | 1.3         | System Configuration<br>1.3.1 Single-chip system<br>1.3.2 Multi-chip system | 4  |    |

|           | 1.4         | Pin Layout Diagram                                                          | 5  |    |

|           | 1.5         | Mask Option                                                                 |    |    |

| CHAPTER 2 | Pov         | ver Supply                                                                  |    | 12 |

|           | 2.1         | Operating Voltage                                                           |    |    |

|           | 2.2         | Internal Power Supply Circuit                                               | 12 |    |

|           | 2.3         | Heavy Load Protection Mode                                                  |    |    |

| CHAPTER 3 | CP          | U AND MEMORY                                                                |    | 13 |

|           | 3.1         | <i>CPU</i>                                                                  |    |    |

|           | 3.2         | Internal Memory                                                             |    |    |

|           |             | 3.2.1 ROM                                                                   |    |    |

|           |             | 3.2.2 RAM (Data Memory, Display Memory)                                     |    |    |

|           |             | 3.2.3 I/O memory                                                            |    |    |

|           | 3.3         | Exception Processing Vectors                                                |    |    |

|           | 3.4         | CC (Customized Condition Flag)                                              |    |    |

|           | 3.5         | Chip Mode                                                                   |    |    |

|           |             | 3.5.1 MCU mode and MPU mode                                                 |    |    |

|           | 3.6         | External Bus                                                                |    |    |

|           | 2.0         | 3.6.1 Data bus                                                              |    |    |

|           |             | 3.6.2 Address bus                                                           | 18 |    |

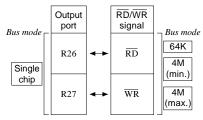

|           |             | 3.6.3 Read $(\overline{RD})/write$ $(\overline{WR})$ signals                |    |    |

|           |             | 3.6.4 Chip enable ( $\overline{CE}$ ) signal                                |    |    |

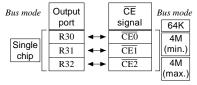

|           |             | 3.6.5 WAIT control                                                          | 20 |    |

| CHAPTER 4 | INI         | TIAL RESET                                                                  | 2  | 21 |

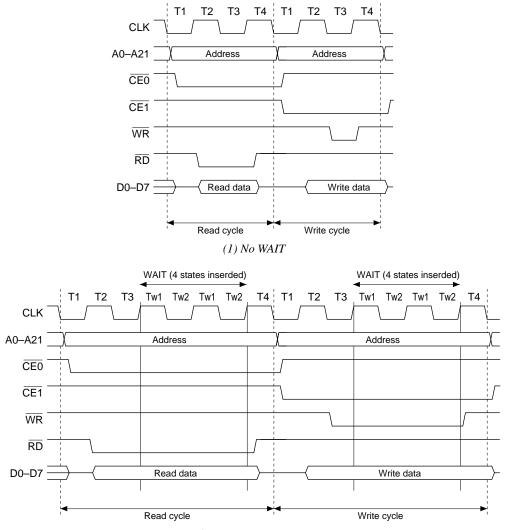

|           | 4.1         | Initial Reset Factors                                                       |    |    |

|           |             | 4.1.1 RESET terminal                                                        |    |    |

|           |             | 4.1.2 Simultaneous LOW level input at input port terminals K00–K03          |    |    |

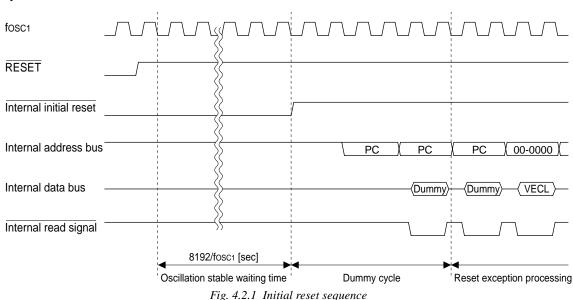

|           | 4.2         | Initial Reset Sequence                                                      |    |    |

|           | 4.3         | Initial Settings at Initial Reset                                           |    |    |

| CHAPTER 5 | Рек         | RIPHERAL CIRCUITS AND OPERATION                                             |    | 24 |

|           | 5.1         | I/O Memory Map                                                              |    |    |

|           | 5.2         | System Controller and Bus Control                                           |    |    |

|           |             | 5.2.1 Bus mode settings                                                     |    |    |

|           |             | 5.2.2 Address decoder (CE output) settings<br>5.2.3 WAIT state settings     |    |    |

|           |             | 5.2.5 WATI state settings                                                   |    |    |

|           |             | 5.2.5 Programming note                                                      |    |    |

#### CONTENTS

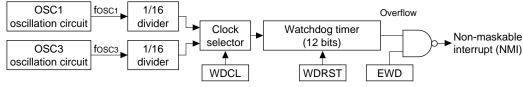

| 5.3          | Watchdog Timer                                              |          |

|--------------|-------------------------------------------------------------|----------|

|              | 5.3.1 Configuration of watchdog timer                       |          |

|              | 5.3.2 Control of watchdog timer 51                          |          |

|              | 5.3.3 Interrupt function                                    |          |

|              | 5.3.4 I/O memory of watchdog timer 52                       |          |

|              | 5.3.5 Programming notes                                     |          |

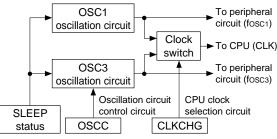

| 5.4          | Oscillation Circuit                                         | ļ        |

|              | 5.4.1 Configuration of oscillation circuit                  |          |

|              | 5.4.2 Mask option                                           |          |

|              | 5.4.3 OSC1 oscillation circuit                              |          |

|              | 5.4.4 OSC3 oscillation circuit 55                           |          |

|              | 5.4.5 Switching of CPU clock and operating voltage VD1      |          |

|              | 5.4.6 I/O memory of oscillation circuit 58                  |          |

|              | 5.4.7 Programming notes 59                                  |          |

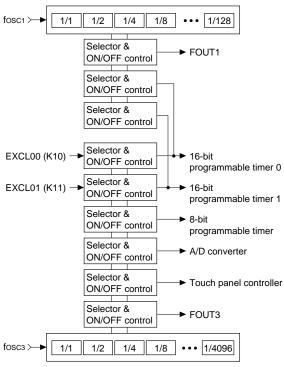

| 5.5          | Prescaler and Clock Control Circuit for Peripheral Circuits | )        |

|              | 5.5.1 Configuration of prescaler                            |          |

|              | 5.5.2 Setting of source clock                               |          |

|              | 5.5.3 Prescaler division ratio selection and output control |          |

|              | 5.5.4 Control of external clock for event counter           |          |

|              | 5.5.5 I/O memory of prescaler                               |          |

|              | 5.5.6 Programming note                                      |          |

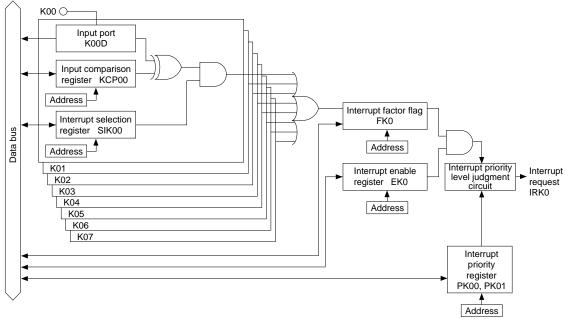

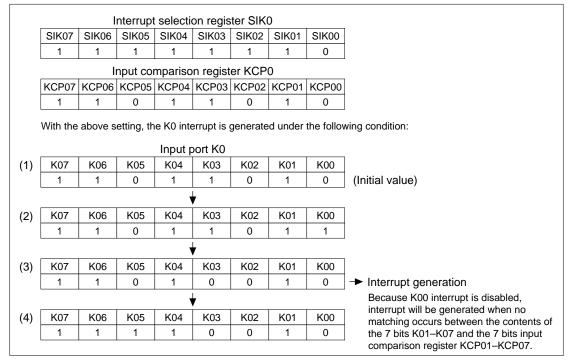

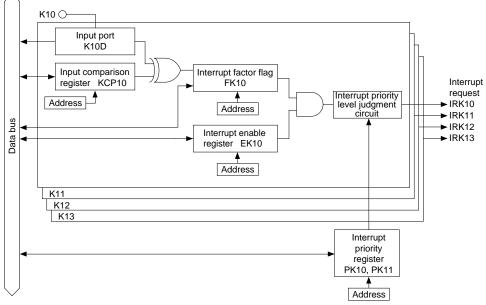

| 5.6          | Input Ports (K ports)                                       | 3        |

|              | 5.6.1 Configuration of input ports                          |          |

|              | 5.6.2 Mask option                                           |          |

|              | 5.6.3 Interrupt function                                    |          |

|              | 5.6.4 I/O memory of input ports                             |          |

|              | 5.6.5 Programming note                                      |          |

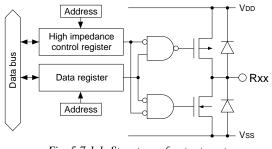

| 5.7          | Output Ports (R ports)                                      | 5        |

| 5.7          | 5.7.1 Configuration of output ports                         |          |

|              | 5.7.2 High impedance control                                |          |

|              | 5.7.3 DC output                                             |          |

|              | 5.7.4 Special output                                        |          |

|              | 5.7.5 I/O memory of output ports                            |          |

| 5.8          | <i>I/O Ports (P ports)</i>                                  | 2        |

| 5.0          | 5.8.1 Configuration of I/O ports                            | ,        |

|              | 5.8.1 Configuration of I/O ports and change of function     |          |

|              | 5.8.3 Mask option                                           |          |

|              | 5.8.4 I/O control registers and I/O mode                    |          |

|              | 5.8.5 I/O memory of I/O ports                               |          |

|              | 5.8.6 Programming note                                      |          |

| 5.9          | Clock Output                                                | 2        |

| 5.9          | 5.9.1 Configuration of clock output control circuit         | '        |

|              | 5.9.1 Configuration of clock output control circuit         |          |

|              | 5.9.2 Clock output control                                  |          |

|              | 5.9.4 Programming notes                                     |          |

| <b>5 1</b> 0 |                                                             | <b>.</b> |

| 5.10         | LCD Controller                                              | 5        |

|              | 5.10.1 Configuration of LCD controller                      |          |

|              | 5.10.2 Output signals                                       |          |

|              | 5.10.3 Display control                                      |          |

|              | 5.10.4 B&W and gray-scale mode setting                      |          |

|              | 5.10.5 Display memory                                       |          |

|              | 5.10.7 Vertical scroll function                             |          |

|              | 5.10.8 Virtual screen function                              |          |

|              | 5.10.9 Data transfer                                        |          |

|              | 5.10.9 Data transfer                                        |          |

|              |                                                             |          |

|               | 5.10.11 I/O memory of LCD controller               |     |

|---------------|----------------------------------------------------|-----|

|               | 5.10.12 Programming notes                          | 103 |

| 51            | 1 Clock Timer                                      | 104 |

| 5.11          |                                                    |     |

|               | 5.11.1 Configuration of clock timer                |     |

|               | 5.11.2 Interrupt function                          |     |

|               | 5.11.3 I/O memory of clock timer                   |     |

|               | 5.11.4 Programming notes                           | 108 |

| 51            | 2 16-bit Programmable Timer                        | 100 |

| 5.12          |                                                    |     |

|               | 5.12.1 Configuration of 16-bit programmable timer  |     |

|               | 5.12.2 Operation mode                              |     |

|               | 5.12.3 Setting of input clock                      |     |

|               | 5.12.4 Operation and control of timer              |     |

|               | 5.12.5 Interrupt function                          |     |

|               | 5.12.6 Setting of TOUT output                      | 114 |

|               | 5.12.7 I/O memory of 16-bit programmable timer     | 115 |

|               | 5.12.8 Programming notes                           |     |

| 5 1           |                                                    |     |

| 5.13          | 3 8-bit Programmable Timer                         |     |

|               | 5.13.1 Configuration of 8-bit programmable timer   |     |

|               | 5.13.2 Setting of input clock                      |     |

|               | 5.13.3 Operation and control of timer              | 124 |

|               | 5.13.4 Interrupt function                          |     |

|               | 5.13.5 Transfer rate setting for serial interface  | 125 |

|               | 5.13.6 I/O memory of 8-bit programmable timer      | 126 |

|               | 5.13.7 Programming notes                           |     |

| 5 1           |                                                    |     |

| 5.14          | 4 Serial Interface                                 |     |

|               | 5.14.1 Configuration of serial interface           |     |

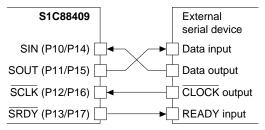

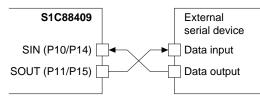

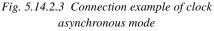

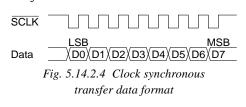

|               | 5.14.2 Transfer mode and input/output terminals    |     |

|               | 5.14.3 Mask option                                 | 133 |

|               | 5.14.4 Clock source                                | 133 |

|               | 5.14.5 Control procedure to transmit/receive       | 135 |

|               | 5.14.6 Receive error                               |     |

|               | 5.14.7 Interrupt function                          |     |

|               | 5.14.8 IR (Infrared-ray) interface                 |     |

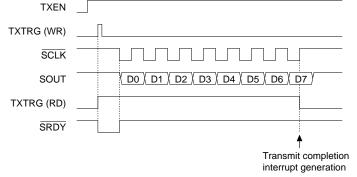

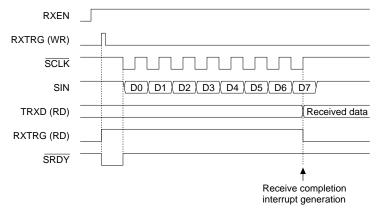

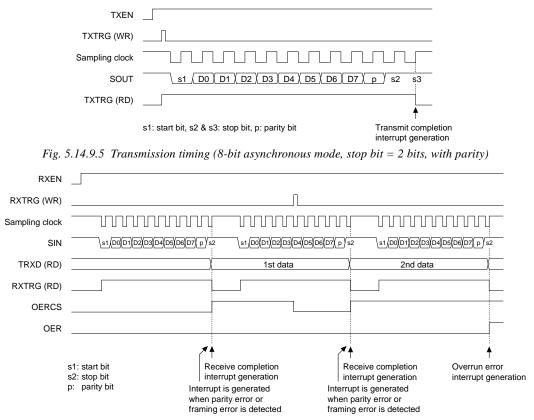

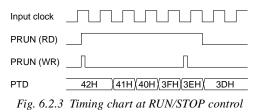

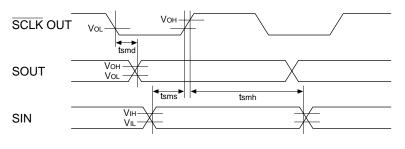

|               | 5.14.9 Timing charts                               |     |

|               | 5.14.10 I/O memory of serial interface             |     |

|               | 5.14.11 Programming notes                          |     |

|               |                                                    |     |

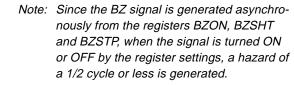

| 5.13          | 5 Sound Generator                                  |     |

|               | 5.15.1 Configuration of sound generator            | 150 |

|               | 5.15.2 Control of buzzer output                    | 150 |

|               | 5.15.3 Setting of buzzer frequency and sound level |     |

|               | 5.15.4 Digital envelope                            |     |

|               | 5.15.5 One-shot output                             |     |

|               | 5.15.6 I/O memory of sound generator               |     |

|               |                                                    |     |

|               | 5.15.7 Programming notes                           |     |

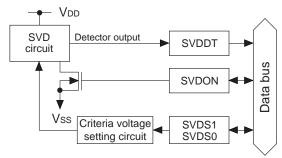

| 5.10          | 5 SVD (Supply Voltage Detection) Circuit           | 156 |

|               | 5.16.1 Configuration of SVD circuit                | 156 |

|               | 5.16.2 SVD operation                               |     |

|               | 5.16.3 I/O memory of SVD circuit                   |     |

|               | 5.16.4 Programming notes                           |     |

|               |                                                    |     |

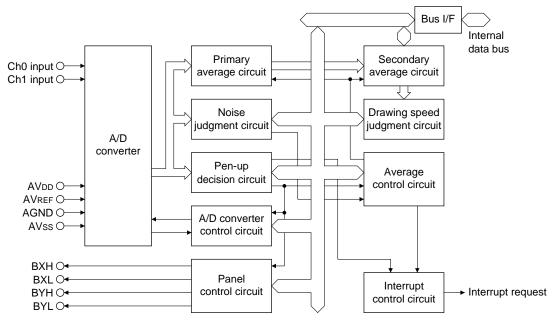

| 5. <i>1</i> 2 | 7 Touch Panel Controller                           |     |

|               | 5.17.1 Configuration of touch panel controller     |     |

|               | 5.17.2 Terminal configuration                      | 158 |

|               | 5.17.3 Operation of touch panel controller         |     |

|               | 5.17.4 Interrupt function                          |     |

|               | 5.17.5 Touch panel controller control flow         |     |

|               | 5.17.6 I/O memory of touch panel controller        |     |

|               | 5.17.7 Programming notes                           |     |

|               |                                                    |     |

|           | 5.18       | A/D Converter                                                              |     |

|-----------|------------|----------------------------------------------------------------------------|-----|

|           |            | 5.18.1 Characteristics and configuration of A/D converter                  | 176 |

|           |            | 5.18.2 Terminal configuration of A/D converter                             |     |

|           |            | 5.18.3 Mask option                                                         |     |

|           |            | 5.18.4 Control of A/D converter                                            |     |

|           |            | 5.18.5 Interrupt function<br>5.18.6 I/O memory of A/D converter            |     |

|           |            | 5.18.7 Programming notes                                                   |     |

|           | 5 10       |                                                                            |     |

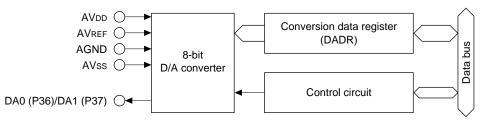

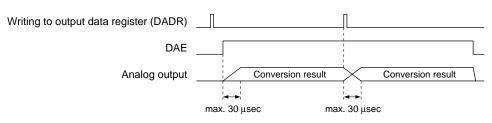

|           | 5.19       | D/A Converter<br>5.19.1 Characteristics and configuration of D/A converter |     |

|           |            | 5.19.1 Characteristics and conjugation of D/A converter                    |     |

|           |            | 5.19.3 Mask option                                                         |     |

|           |            | 5.19.4 Control of D/A converter                                            |     |

|           |            | 5.19.5 I/O memory of D/A converter                                         |     |

|           |            | 5.19.6 Programming note                                                    | 187 |

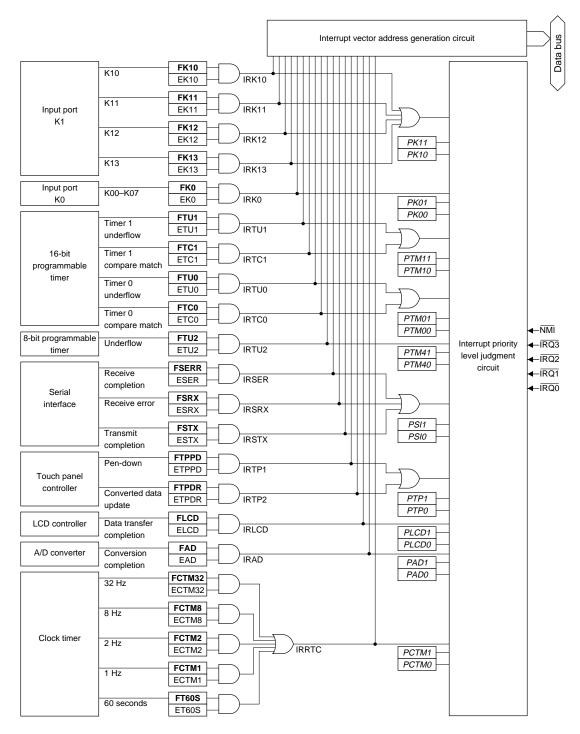

|           | 5.20       | Interrupt and Standby Mode                                                 |     |

|           |            | 5.20.1 Types of interrupts                                                 |     |

|           |            | 5.20.2 Standby mode                                                        |     |

|           |            | 5.20.3 Interrupt generation conditions                                     |     |

|           |            | 5.20.4 Interrupt factor flag                                               |     |

|           |            | 5.20.5 Interrupt enable register                                           |     |

|           |            | 5.20.6 Interrupt priority register and interrupt priority level            |     |

|           |            | 5.20.7 Exception processing vectors<br>5.20.8 I/O memory of interrupt      |     |

|           |            | 5.20.9 Programming notes                                                   |     |

|           |            | 0 0                                                                        |     |

| CHAPTER 6 | SUM        | IMARY OF NOTES                                                             | 19  |

|           | 6.1        | Notes for Low Current Consumption                                          |     |

|           | 6.2        | Summary of Notes by Function                                               |     |

|           | 6.3        | Precautions on Mounting                                                    |     |

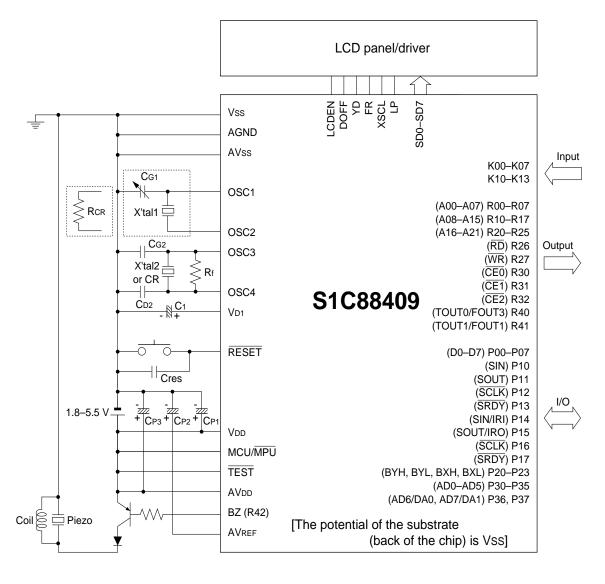

| CHAPTER 7 | BAS        | IC EXTERNAL WIRING DIAGRAM                                                 | 204 |

|           |            | CTRICAL CHARACTERISTICS                                                    |     |

|           | 8.1        | Absolute Maximum Rating                                                    |     |

|           |            | -                                                                          |     |

|           | 8.2        | Recommended Operating Conditions                                           |     |

|           | <i>8.3</i> | DC Characteristics                                                         |     |

|           | 8.4        | Analog Circuit Characteristics and Current Consumption                     |     |

|           | 8.5        | AC Characteristics                                                         |     |

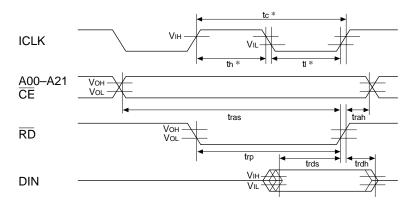

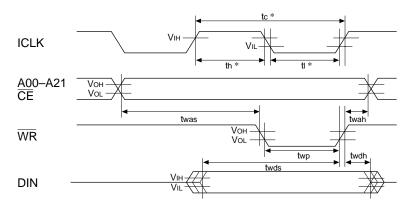

|           |            | 8.5.1 External memory access                                               | 208 |

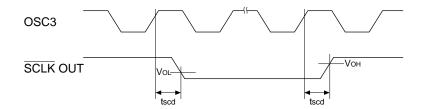

|           |            | 8.5.2 Serial interface                                                     |     |

|           |            | 8.5.3 Input clock                                                          |     |

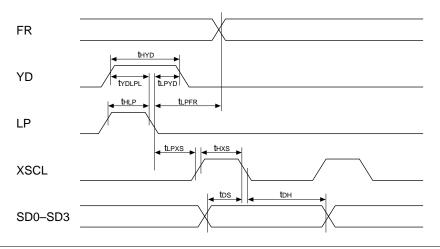

|           |            | 8.5.4 LCD controller                                                       |     |

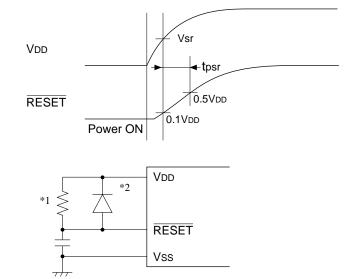

|           |            | 8.5.5 Power-on reset                                                       |     |

|           |            | 8.5.6 Switching operating mode                                             |     |

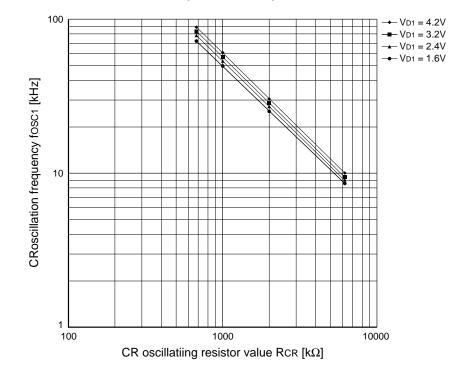

|           | 8.6        | Oscillation Characteristics                                                |     |

|           | 8.7        | A/D Converter Characteristics                                              |     |

|           | 8.8        | D/A Converter Characteristics                                              |     |

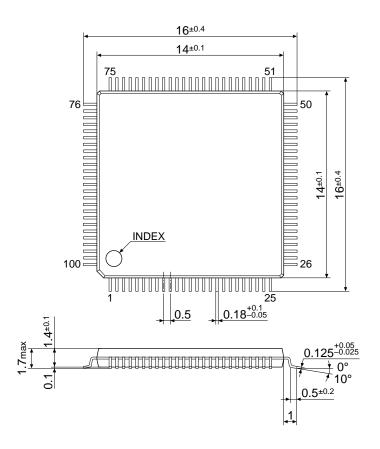

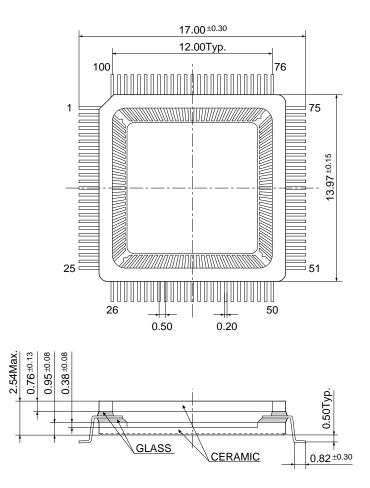

| CHAPTER 9 | PAC        | KAGE                                                                       | 216 |

|           |            | Plastic Package                                                            |     |

|           | 9.1<br>9.2 | Ceramic Package for Test Samples                                           |     |

|           | 11.7       | Coramic Packago for Tost Namplas                                           | 270 |

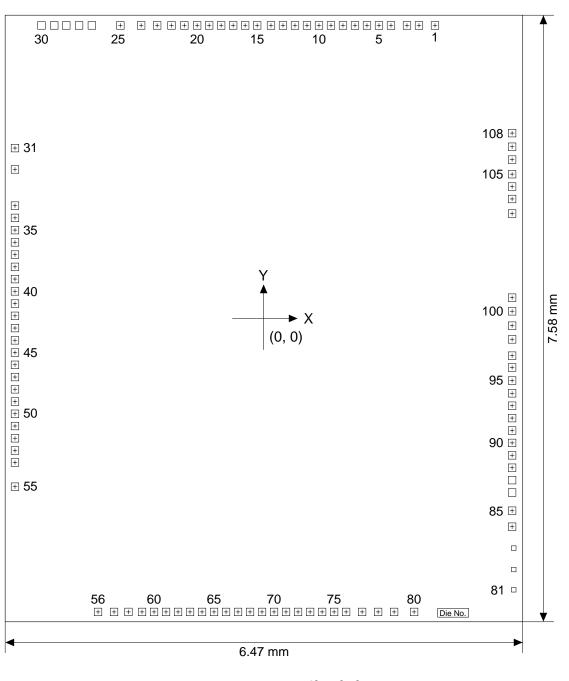

| CHAPTER 1 | CHAPTER 10 PAD LAYOUT 220 |                                                         |     |  |  |  |

|-----------|---------------------------|---------------------------------------------------------|-----|--|--|--|

|           | 10.1                      | Diagram of Pad Layout                                   |     |  |  |  |

|           | 10.2                      | Pad Coordinates                                         | 221 |  |  |  |

| Appendix  | Co                        | NTROLLING THE TOUCH PANEL CONTROLLER                    | 222 |  |  |  |

|           | A.1                       | I/O Map                                                 |     |  |  |  |

|           | A.2                       | Description                                             | 227 |  |  |  |

|           |                           | A.2.1 Circuit connection                                |     |  |  |  |

|           |                           | A.2.2 Mask option configuration                         | 227 |  |  |  |

|           |                           | A.2.3 Reducing power consumption and improving response |     |  |  |  |

|           |                           | A.2.4 Reading coordinate data from the TPC              |     |  |  |  |

|           |                           | A.2.5 Calculating the LCD dot position                  | 228 |  |  |  |

|           | A.3                       | Precautions                                             |     |  |  |  |

|           |                           | A.3.1 Interrupt processing                              |     |  |  |  |

|           |                           | A.3.2 Others                                            |     |  |  |  |

|           | A 4                       | Reference Flowchart                                     | 229 |  |  |  |

|           | 11.1                      | A.4.1 Initializing the TPC                              |     |  |  |  |

|           |                           | A.4.2 TPC data update interrupt processing              |     |  |  |  |

|           |                           | A.4.3 TP initial data configuration                     |     |  |  |  |

|           |                           | A.4.4 Coordinate data calculation                       |     |  |  |  |

|           | 4 5                       | Reference Program                                       | 232 |  |  |  |

|           | 11.5                      | A.5.1 Setting constants and macros (include file)       |     |  |  |  |

|           |                           | A.5.2 TPC initialization                                |     |  |  |  |

|           |                           | A.5.2 TPC data update interrupt processing              |     |  |  |  |

|           |                           | A.5.4 TP initial data setting                           |     |  |  |  |

|           |                           | A.5.5 Coordinate data calculation                       |     |  |  |  |

|           |                           |                                                         |     |  |  |  |

# CHAPTER 1

OUTLINE

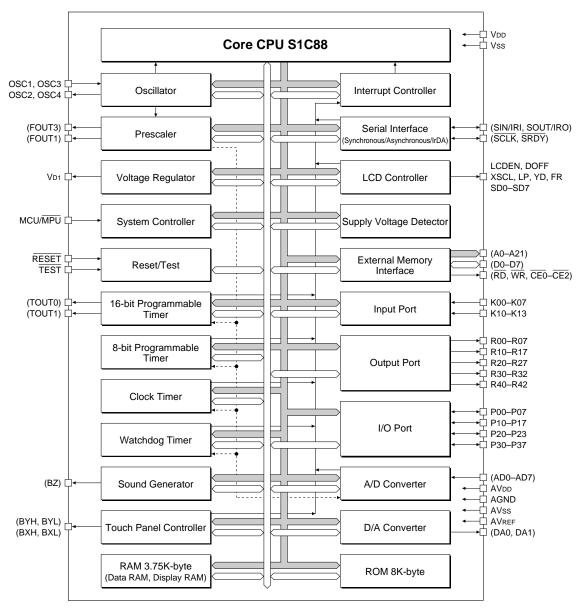

The S1C88409 is a single chip microcomputer which consists of a CMOS 8-bit core CPU S1C88 (MODEL3), 8KB ROM, 3.75KB RAM, dot-matrix LCD controller, 3 types of timers/counters, serial interface (IR input/output function is available), touch panel controller, A/D converter and D/A converter.

The S1C88409 operates faster even with low supply voltage, and is most suitable for various application equipment such as information terminals needing low power operation. Furthermore, the S1C88409 can control up to  $4M \times$ 3 bytes of memory with the 22-bit outside address bus and 3-bit chip enable signals, therefore it can also be applied to systems such as electronic dictionaries and organizers.

## 1.1 Features

|                |                             | Table 1.1.1 Features                                                                                             |  |  |  |  |  |

|----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Core CPU       |                             | CMOS 8-bit core CPU S1C88 (MODEL3)                                                                               |  |  |  |  |  |

| OSC1 oscilla   |                             | Crystal oscillation circuit/CR oscillation circuit/external clock input 32.768 kHz (Typ.)                        |  |  |  |  |  |

| OSC3 oscilla   |                             | Crystal oscillation circuit/ceramic oscillation circuit/CR oscillation circuit/external clock input 8 MHz (Max.) |  |  |  |  |  |

| Instruction se | et                          | Basic instruction: 54 types, Total: 608 types (multiplication/division instructions are usable)                  |  |  |  |  |  |

|                |                             | Addressing mode: 12 types                                                                                        |  |  |  |  |  |

|                | on execution time           | 0.25 µsec/8 MHz (2 clocks)                                                                                       |  |  |  |  |  |

| Internal ROM   |                             | 8K bytes                                                                                                         |  |  |  |  |  |

| Internal RAM   | l capacity                  | 3.75K bytes (display memory is included; data/display memory size can be set by mask option)                     |  |  |  |  |  |

| Bus line       |                             | Address bus: 22 bits                                                                                             |  |  |  |  |  |

|                |                             | Data bus: 8 bits (usable as general output port or I/O port when it is not used as a bus signal)                 |  |  |  |  |  |

|                |                             | CE signal: 3 bits                                                                                                |  |  |  |  |  |

|                |                             | WR signal: 1 bit                                                                                                 |  |  |  |  |  |

|                |                             | RD signal: 1 bit                                                                                                 |  |  |  |  |  |

| Input port     |                             | 12 bits                                                                                                          |  |  |  |  |  |

|                |                             | 2 bits are usable for event counter input                                                                        |  |  |  |  |  |

| Output port    |                             | 30 bits                                                                                                          |  |  |  |  |  |

|                |                             | • They are used as address bus and bus control signals when external bus is set                                  |  |  |  |  |  |

| 1/0            |                             | Usable for clock output and buzzer output                                                                        |  |  |  |  |  |

| I/O port       |                             | 28 bits                                                                                                          |  |  |  |  |  |

|                |                             | • 8 bits are used as data bus when external bus is set                                                           |  |  |  |  |  |

|                |                             | Usable for serial interface input/output, A/D converter input, D/A converter output and     tench neural network |  |  |  |  |  |

| Coriol interf  |                             | touch panel output                                                                                               |  |  |  |  |  |

| Serial interfa | ce                          | 1 channel                                                                                                        |  |  |  |  |  |

|                |                             | Clock synchronous mode/asynchronous mode selectable                                                              |  |  |  |  |  |

| 1C hit progra  | na na a la tina a r         | Usable as IrDA interface     I channel                                                                           |  |  |  |  |  |

| ro-bit progra  | mmable timer                | • Usable for 16 bits $\times$ 1 channel or 8 bits $\times$ 2 channels                                            |  |  |  |  |  |

|                |                             | Usable for 16 bits × 1 channel or 8 bits × 2 channels     Usable as event counter                                |  |  |  |  |  |

| 9 hit program  | mable timer                 |                                                                                                                  |  |  |  |  |  |

| 8-bit program  | imable limer                | 1 channel                                                                                                        |  |  |  |  |  |

| Clock timer    |                             | Jsable as baud rate generator for serial interface                                                               |  |  |  |  |  |

| CIOCK LITTIET  |                             | 1 channel                                                                                                        |  |  |  |  |  |

|                |                             | <ul> <li>Generating 1 sec signal with 32 kHz oscillation</li> <li>60S counter available</li> </ul>               |  |  |  |  |  |

| LCD controlle  | or                          | Dot-matrix type                                                                                                  |  |  |  |  |  |

|                | 51                          | • B&W or 4 gray scale display                                                                                    |  |  |  |  |  |

|                |                             | • A 240 × 100 dot LCD panel can be driven with external drivers (S1D16305 or S1D16700,                           |  |  |  |  |  |

|                |                             | S1D16006 or S1D15700)                                                                                            |  |  |  |  |  |

|                |                             | Scroll function available                                                                                        |  |  |  |  |  |

| Touch panel    | controller                  | Supports pressure sensitive and resistive membrane type analog touch panels                                      |  |  |  |  |  |

| A/D converte   |                             | Resolution 10 bits (input: 8 channels)                                                                           |  |  |  |  |  |

| D/A converte   | -                           | Resolution 8 bits (output: 2 channels)                                                                           |  |  |  |  |  |

| Sound gener    |                             | Equipped with envelope and volume control functions                                                              |  |  |  |  |  |

| <b>v</b>       |                             | Possible to detect 3 voltage levels                                                                              |  |  |  |  |  |

| Watchdog tin   |                             | Possible to detect 5 voltage revers                                                                              |  |  |  |  |  |

| Interrupt      |                             | External: Input interrupt 2 systems (5 types)                                                                    |  |  |  |  |  |

| linenupi       |                             | Internal: 16-bit programmable timer interrupt 2 systems (5 types)                                                |  |  |  |  |  |

|                |                             | 8-bit programmable timer interrupt 1 system (1 type)                                                             |  |  |  |  |  |

|                |                             | Clock timer interrupt 1 system (5 types)                                                                         |  |  |  |  |  |

|                |                             | Watchdog timer interrupt 1 system (3 types)<br>1 system (1 type)                                                 |  |  |  |  |  |

|                |                             | Serial interface interrupt 1 system (1 type)                                                                     |  |  |  |  |  |

|                |                             | LCD controller interrupt 1 system (1 type)                                                                       |  |  |  |  |  |

|                |                             | Touch panel interrupt I system (1 type)                                                                          |  |  |  |  |  |

|                |                             | A/D converter interrupt 1 system (2 types)                                                                       |  |  |  |  |  |

| Supply voltag  | ne                          | 1.8 V to 5.5 V (operating frequency Max. 1.1 MHz)                                                                |  |  |  |  |  |

|                | JC .                        | 2.6 V to 5.5 V (operating frequency Max. 4.4 MHz)                                                                |  |  |  |  |  |

|                |                             | 3.5 V to 5.5 V (operating frequency Max. 4.6 MHz)                                                                |  |  |  |  |  |

|                |                             | 4.5 V to 5.5 V (operating frequency Max. 8.8 MHz)                                                                |  |  |  |  |  |

| Current        | SLEEP                       | $0.6 \mu\text{A Typ. (at 3.0 V) (Normal mode)}$                                                                  |  |  |  |  |  |

| consumption    |                             | $3.0 \mu\text{A Typ. (at 3.0 V) (Normal mode)}$                                                                  |  |  |  |  |  |

| - sonsumption  | Run $(32 \text{ kHz})$      | $15 \mu\text{A Typ. (at 3.0 V) (Normal mode)}$                                                                   |  |  |  |  |  |

|                | Run (32 KHZ)<br>Run (4 MHZ) | 2 mA Typ. (at 3.0 V) (Normal mode)                                                                               |  |  |  |  |  |

|                | Run (8 MHz)                 | 9 mA Typ. (at 5.0 V) (Normal mode)<br>9 mA Typ. (at 5.0 V) (High speed mode)                                     |  |  |  |  |  |

| Supply form    |                             | QFP15-100pin or chip                                                                                             |  |  |  |  |  |

|                |                             |                                                                                                                  |  |  |  |  |  |

Table 1.1.1 Features

## 1.2 Block Diagram

Fig. 1.2.1 S1C88409 block diagram

\* The terminals that are shown in ( ) are shared with Pxx or Rxx terminals.

## 1.3 System Configuration

System configuration of the S1C88409 is classified in 2 types according to use.

- 1) Single-chip system

- 2) Multi-chip system

To construct these systems, the S1C88409 has been designed to switch the bus mode (configuration of the external bus) by software and/or mask option.

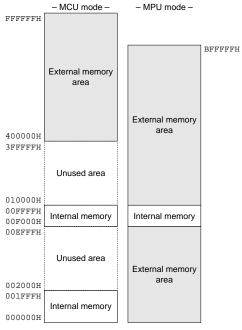

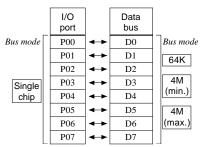

### 1.3.1 Single-chip system

The single-chip system has the smallest configuration that uses the S1C88409 as the CPU of the system and does not expand any memory and devices outside. It is suitable for various controller systems.

Since it does not use an external bus, the bus mode of the S1C88409 should be set to the MCU/ singlechip mode (see Section 3.5). (Initial setting) The memory that can be used is limited to the built-in area.

ROM ...8KB

RAM ....3.75KB (display memory is included)

The I/O ports shared with the external bus can be used entirely as general-purpose I/O ports.

Fig. 1.3.1.1 Configuration of single-chip system

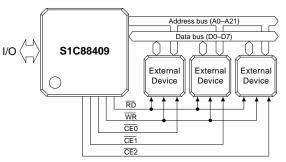

### 1.3.2 Multi-chip system

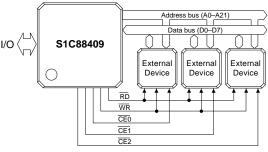

With the S1C88409 as the CPU, the multi-chip system has expanded memory as well as other expanded devices. It covers a wide range of applications. Memory and devices are connected to the external bus of the S1C88409 and are all controlled by the S1C88409.

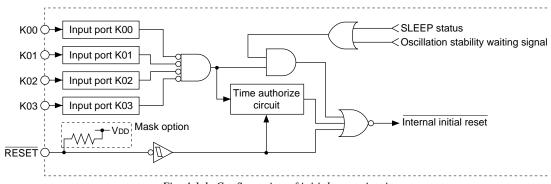

The bus mode of the S1C88409 can be set to the expanded mode (see Section 3.5) according to scale of the system.

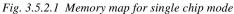

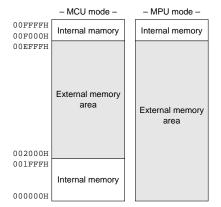

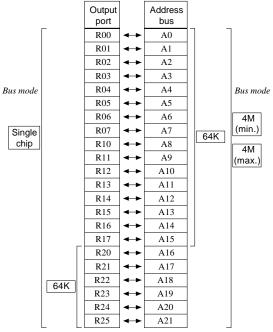

- MCU or MPU\*/Expanded 64K mode For systems with 64KB or less expanded memory

- MCU or MPU\*/Expanded 4M minimum mode For systems with 64KB to 12MB ( $4M \times 3$ ) expanded memory (However, program memory is 64KB or less)

- MCU or MPU\*/Expanded 4M maximum mode For systems with 64KB to 12MB (4M × 3) expanded memory (For systems that require 64KB or more program memory)

- \* The MCU mode is set when the internal ROM is used, and the MPU mode is set when the internal ROM is not used.

Refer to Section 3.6, "External Bus", for the bus configuration.

Fig. 1.3.2.1 Configuration of multi-chip system

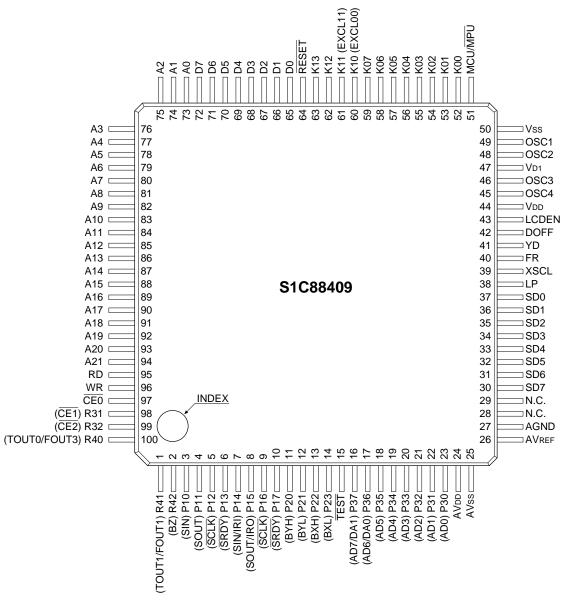

### 1.4 Pin Layout Diagram

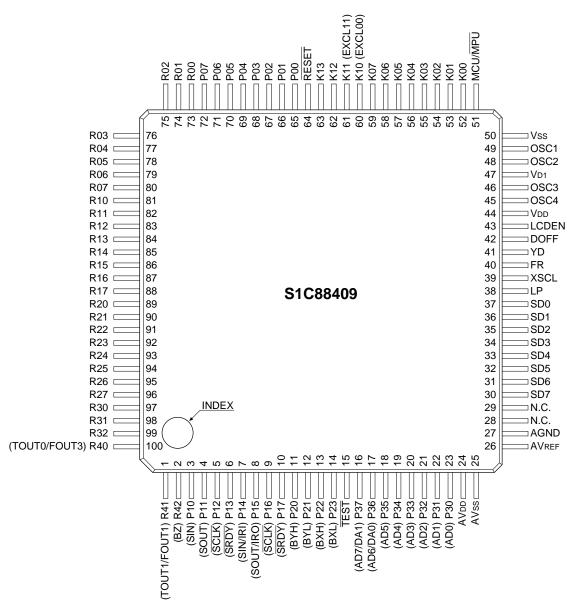

#### • Pin layout for single chip mode (initial setting)

Fig. 1.4.1 S1C88409 pin layout (single chip mode)

|                    | Table   |            | IC88409 pin description (single chip mode)                                                                                         |

|--------------------|---------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| Pin name           | Pin No. | I/O        | Function                                                                                                                           |

| VDD                | 44      | -          | Power supply (+) pin                                                                                                               |

| Vss                | 50      | -          | Power supply (GND) pin                                                                                                             |

| VD1                | 47      | 0          | Voltage regulator output pin                                                                                                       |

| AVdd               | 24      | -          | Power supply (+) pin for analog circuit system                                                                                     |

| AGND               | 27      | _          | GND pin for analog circuit system                                                                                                  |

| AVss               | 25      | -          | Power supply (GND) pin for analog circuit system                                                                                   |

| AVREF              | 26      | Ι          | Reference voltage input pin for analog circuit system                                                                              |

| OSC1               | 49      | Ι          | OSC1 oscillation input pin (32 kHz crystal, CR oscillation, external clock input)                                                  |

| OSC2               | 48      | 0          | OSC1 oscillation output pin                                                                                                        |

| OSC3               | 46      | Ι          | OSC3 oscillation input pin (crystal/ceramic, CR oscillation, external clock input)                                                 |

| OSC4               | 45      | 0          | OSC3 oscillation output pin                                                                                                        |

| MCU/MPU            | 51      | Ι          | MCU/MPU mode stting pin*1                                                                                                          |

| K00~K07            | 52~59   | Ι          | Input port pin                                                                                                                     |

| K10 (EXCL00)       | 60      | Ι          | Input port pin or external clock input pin for event counter (Timer 0)                                                             |

| K11 (EXCL01)       | 61      | Ι          | Input port pin or external clock input pin for event counter (Timer 1)                                                             |

| K12~K13            | 62~63   | Ι          | Input port pin                                                                                                                     |

| R00~R07            | 73~80   | 0          | Output port pin                                                                                                                    |

| R10~R17            | 81~88   | 0          | Output port pin                                                                                                                    |

| R20~R27            | 89~96   | 0          | Output port pin                                                                                                                    |

| R30~R32            | 97~99   | 0          | Output port pin                                                                                                                    |

| R40 (TOUT0/FOUT3)  | 100     | 0          | Output port pin or TOUT0/FOUT3 clock output pin                                                                                    |

| R41 (TOUT1/FOUT1)  | 1       | 0          | Output port pin or TOUT1/FOUT1 clock output pin                                                                                    |

| R42 (BZ)           | 2       | 0          | Output port pin or buzzer signal output pin                                                                                        |

| P00~P07            | 65~72   | I/O        | I/O port pin                                                                                                                       |

| P10 (SIN)          | 3       | I/O        | I/O port pin or serial I/F data input pin                                                                                          |

| P11 (SOUT)         | 4       | I/O        | I/O port pin or serial I/F data output pin                                                                                         |

| P12 (SCLK)         | 5       | I/O        | I/O port pin or serial I/F clock input/output pin                                                                                  |

| P13 (SRDY)         | 6       | I/O        | I/O port pin or serial I/F ready signal output pin                                                                                 |

| P14 (SIN/IRI)      | 7       | I/O        | I/O port pin, serial I/F data input or IR receiver input pin                                                                       |

| P15 (SOUT/IRO)     | 8       | I/O        | I/O port pin, serial I/F data output or IR transmitter output pin                                                                  |

| P16 (SCLK)         | 9       | I/O        | I/O port pin or serial I/F clock input/output pin                                                                                  |

| P17 (SRDY)         | 10      | I/O        | I/O port pin or serial I/F ready signal output pin                                                                                 |

| P20 (BYH)          | 10      | I/O        | I/O port pin or touch panel controller BYH signal output pin                                                                       |

| P21 (BYL)          | 12      | I/O        | I/O port pin or touch panel controller BYL signal output pin                                                                       |

| P22 (BXH)          | 13      | I/O        | I/O port pin or touch panel controller BXH signal output pin                                                                       |

| P23 (BXL)          | 14      | I/O        | I/O port pin or touch panel controller BXL signal output pin                                                                       |

| P30~P35 (AD0~AD5)  | 23~18   | I/O        | I/O port pin or A/D converter analog signal input pin                                                                              |

| P36. P37           | 17,16   | I/O<br>I/O | I/O port pin, A/D converter analog signal input pin<br>I/O port pin, A/D converter analog signal input pin or D/A converter analog |

| (AD6/DA0, AD7/DA1) | 17,10   | 1/0        | signal output pin                                                                                                                  |

| LCDEN              | 43      | 0          | LCD controller enable signal output pin                                                                                            |

| DOFF               | 42      | 0          | LCD controller forced blank signal output pin                                                                                      |

| YD                 | 42      | 0          | LCD controller scan start pulse output pin                                                                                         |

| FR                 | 40      | 0          | LCD controller frame signal output pin                                                                                             |

| XSCL               | 39      | 0          | LCD controller shift clock output pin                                                                                              |

| LP                 | 39      | 0          | LCD controller latch pulse output pin                                                                                              |

| LP<br>SD0~SD7      | 37~30   |            |                                                                                                                                    |

| RESET              |         | 0<br>I     | LCD controller data output pin                                                                                                     |

| TEST               | 64      | I          | Initial reset input pin                                                                                                            |

| 1651               | 15      | 1          | Test input pin*2                                                                                                                   |

Table 1.4.1 S1C88409 pin description (single chip mode)

\*1 The MCU/ $\overline{\text{MPU}}$  terminal should be connected to VDD.

\*2  $\overline{\text{TEST}}$  is the terminal used for factory inspection of the IC. For normal operation, be sure to connect the  $\overline{\text{TEST}}$  terminal to VDD.

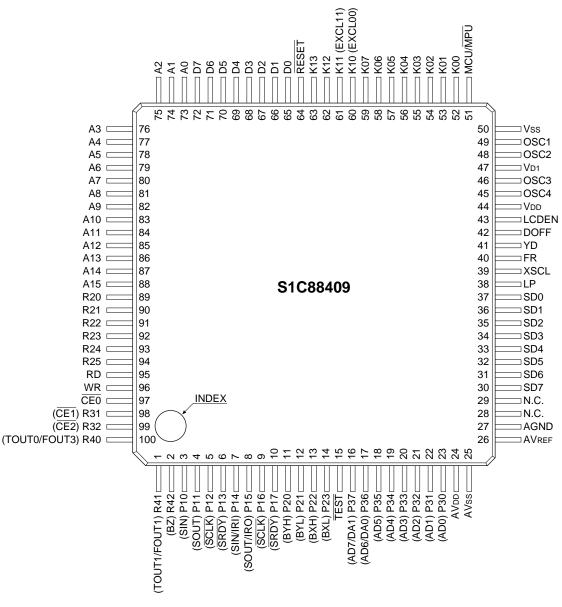

#### • Pin layout for expanded 64K mode (for multi-chip system)

Fig. 1.4.2 S1C88409 pin layout (expanded 64K mode)

|                               | Table 1 |            | C88409 pin description (expanded 64K mode)                                         |

|-------------------------------|---------|------------|------------------------------------------------------------------------------------|

| Pin name                      | Pin No. | I/O        | Function                                                                           |

| VDD                           | 44      | -          | Power supply (+) pin                                                               |

| Vss                           | 50      | -          | Power supply (GND) pin                                                             |

| VD1                           | 47      | 0          | Voltage regulator output pin                                                       |

| AVDD                          | 24      | _          | Power supply (+) pin for analog circuit system                                     |

| AGND                          | 27      | -          | GND pin for analog circuit system                                                  |

| AVss                          | 25      | -          | Power supply (GND) pin for analog circuit system                                   |

| AVREF                         | 26      | Ι          | Reference voltage input pin for analog circuit system                              |

| OSC1                          | 49      | Ι          | OSC1 oscillation input pin (32 kHz crystal, CR oscillation, external clock input)  |

| OSC2                          | 48      | 0          | OSC1 oscillation output pin                                                        |

| OSC3                          | 46      | Ι          | OSC3 oscillation input pin (crystal/ceramic, CR oscillation, external clock input) |

| OSC4                          | 45      | 0          | OSC3 oscillation output pin                                                        |

| MCU/MPU                       | 51      | Ι          | MCU/MPU mode stting pin                                                            |

| K00~K07                       | 52~59   | Ι          | Input port pin                                                                     |

| K10 (EXCL00)                  | 60      | Ι          | Input port pin or external clock input pin for event counter (Timer 0)             |

| K11 (EXCL01)                  | 61      | Ι          | Input port pin or external clock input pin for event counter (Timer 1)             |

| K12~K13                       | 62~63   | I          | Input port pin                                                                     |

| A00~A15                       | 73~88   | 0          | Address bus                                                                        |

| R20~R25                       | 89~94   | 0          | Output port pin                                                                    |

| RD                            | 95      | 0          | Read signal output pin                                                             |

| WR                            | 96      | 0          | Write signal output pin                                                            |

| TEO                           | 97      | 0          | Chip enable signal output pin                                                      |

| <u>CE1</u> (R31)              | 98      | 0          | Chip enable signal output pin or output port pin                                   |

| $\overline{\text{CE2}}$ (R32) | 99      | 0          | Chip enable signal output pin or output port pin                                   |

| R40 (TOUT0/FOUT3)             | 100     | 0          | Output port pin or TOUT0/FOUT3 clock output pin                                    |

| R41 (TOUT1/FOUT1)             | 1       | 0          | Output port pin or TOUT1/FOUT1 clock output pin                                    |

| R42 (BZ)                      | 2       | 0          | Output port pin or buzzer signal output pin                                        |

| D0~D7                         | 65~72   | I/O        | Data bus                                                                           |

| P10 (SIN)                     | 3       | I/O        | I/O port pin or serial I/F data input pin                                          |

| P11 (SOUT)                    | 4       | I/O        | I/O port pin or serial I/F data output pin                                         |

| P12 (SCLK)                    | 5       | I/O        | I/O port pin or serial I/F clock input/output pin                                  |

| P13 (SRDY)                    | 6       | I/O        | I/O port pin or serial I/F ready signal output pin                                 |

| P14 (SIN/IRI)                 | 7       | I/O        | I/O port pin, serial I/F data input or IR receiver input pin                       |

| P15 (SOUT/IRO)                | 8       | I/O        | I/O port pin, serial I/F data output or IR transmitter output pin                  |

| P16 (SCLK)                    | 9       | I/O<br>I/O | I/O port pin or serial I/F clock input/output pin                                  |

| P17 (SRDY)                    | 10      | I/O<br>I/O | I/O port pin or serial I/F ready signal output pin                                 |

| P20 (BYH)                     | 10      | I/O<br>I/O | I/O port pin or touch panel controller BYH signal output pin                       |

| P21 (BYL)                     | 12      | I/O<br>I/O | I/O port pin or touch panel controller BYL signal output pin                       |

| P22 (BXH)                     | 12      | I/O<br>I/O | I/O port pin or touch panel controller BYE signal output pin                       |

| P23 (BXL)                     | 13      | I/O<br>I/O | I/O port pin or touch panel controller BXL signal output pin                       |

| P30~P35 (AD0~AD5)             | 23~18   | I/O<br>I/O | I/O port pin or A/D converter analog signal input pin                              |

| P36, P37                      | 17,16   | I/O<br>I/O | I/O port pin, A/D converter analog signal input pin or D/A converter analog        |

| (AD6/DA0, AD7/DA1)            | 17,10   |            | signal output pin                                                                  |

| LCDEN                         | 43      | 0          | LCD controller enable signal output pin                                            |

| DOFF                          | 43      | 0          | LCD controller forced blank signal output pin                                      |

| YD                            | 42      | 0          | LCD controller scan start pulse output pin                                         |

| FR                            | 40      | 0          | LCD controller frame signal output pin                                             |

| XSCL                          | 39      | 0          | LCD controller shift clock output pin                                              |

| LP                            | 39      | 0          | LCD controller latch pulse output pin                                              |

| SD0~SD7                       | 37~30   | 0          | LCD controller data output pin                                                     |

| RESET                         | 64      | I          | Initial reset input pin                                                            |

| TEST                          | 15      | I          | Test input pin*1                                                                   |

| 11.51                         | 13      | 1          | rest input pill**                                                                  |

Table 1.4.2

S1C88409 pin description (expanded 64K mode)

\*1  $\overline{\text{TEST}}$  is the terminal used for factory inspection of the IC. For normal operation, be sure to connect the  $\overline{\text{TEST}}$  terminal to VDD.

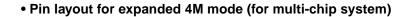

Fig. 1.4.3 S1C88409 pin layout (expanded 4M mode)

| Pin name                      | Pin No. | I/O        | Function                                                                           |

|-------------------------------|---------|------------|------------------------------------------------------------------------------------|

| VDD                           | 44      | _          | Power supply (+) pin                                                               |

| Vss                           | 50      | _          | Power supply (GND) pin                                                             |

| VD1                           | 47      | 0          | Voltage regulator output pin                                                       |

| AVDD                          | 24      | _          | Power supply (+) pin for analog circuit system                                     |

| AGND                          | 27      |            | GND pin for analog circuit system                                                  |

| AVss                          | 25      | _          | Power supply (GND) pin for analog circuit system                                   |

| AVREF                         | 25      | I          | Reference voltage input pin for analog circuit system                              |

| OSC1                          | 49      | I          |                                                                                    |

| OSC1<br>OSC2                  | -       |            | OSC1 oscillation input pin (32 kHz crystal, CR oscillation, external clock input)  |

|                               | 48      | 0          | OSC1 oscillation output pin                                                        |

| OSC3                          | 46      | I          | OSC3 oscillation input pin (crystal/ceramic, CR oscillation, external clock input) |

| OSC4                          | 45      | 0          | OSC3 oscillation output pin                                                        |

| MCU/MPU                       | 51      | Ι          | MCU/MPU mode stting pin                                                            |

| K00~K07                       | 52~59   | I          | Input port pin                                                                     |

| K10 (EXCL00)                  | 60      | Ι          | Input port pin or external clock input pin for event counter (Timer 0)             |

| K11 (EXCL01)                  | 61      | Ι          | Input port pin or external clock input pin for event counter (Timer 1)             |

| K12~K13                       | 62~63   | Ι          | Input port pin                                                                     |

| A00~A21                       | 73~94   | 0          | Address bus                                                                        |

| RD                            | 95      | 0          | Read signal output pin                                                             |

| WR                            | 96      | 0          | Write signal output pin                                                            |

| <b>CEO</b>                    | 97      | 0          | Chip enable signal output pin                                                      |

| <u>CE1</u> (R31)              | 98      | 0          | Chip enable signal output pin or output port pin                                   |

| $\overline{\text{CE2}}$ (R32) | 99      | 0          | Chip enable signal output pin or output port pin                                   |

| R40 (TOUT0/FOUT3)             | 100     | 0          | Output port pin or TOUT0/FOUT3 clock output pin                                    |

| R40 (TOUT1/FOUT1)             | 100     | 0          | Output port pin or TOUT1/FOUT1 clock output pin                                    |

| R41 (10011/10011)<br>R42 (BZ) | 2       | 0          | Output port pin of 100 11/100 11 clock output pin                                  |

| D0~D7                         | 65~72   | 1/O        | Data bus                                                                           |

| P10 (SIN)                     | 3       | I/O<br>I/O | I/O port pin or serial I/F data input pin                                          |

| · · /                         |         |            |                                                                                    |

| P11 (SOUT)                    | 4       | I/O        | I/O port pin or serial I/F data output pin                                         |

| P12 (SCLK)                    | 5       | I/O        | I/O port pin or serial I/F clock input/output pin                                  |

| P13 (SRDY)                    | 6       | I/O        | I/O port pin or serial I/F ready signal output pin                                 |

| P14 (SIN/IRI)                 | 7       | I/O        | I/O port pin, serial I/F data input or IR receiver input pin                       |

| P15 (SOUT/IRO)                | 8       | I/O        | I/O port pin, serial I/F data output or IR transmitter output pin                  |

| P16 (SCLK)                    | 9       | I/O        | I/O port pin or serial I/F clock input/output pin                                  |

| P17 (SRDY)                    | 10      | I/O        | I/O port pin or serial I/F ready signal output pin                                 |

| P20 (BYH)                     | 11      | I/O        | I/O port pin or touch panel controller BYH signal output pin                       |

| P21 (BYL)                     | 12      | I/O        | I/O port pin or touch panel controller BYL signal output pin                       |

| P22 (BXH)                     | 13      | I/O        | I/O port pin or touch panel controller BXH signal output pin                       |

| P23 (BXL)                     | 14      | I/O        | I/O port pin or touch panel controller BXL signal output pin                       |

| P30~P35 (AD0~AD5)             | 23~18   | I/O        | I/O port pin or A/D converter analog signal input pin                              |

| P36, P37                      | 17,16   | I/O        | I/O port pin, A/D converter analog signal input pin or D/A converter analog        |

| (AD6/DA0, AD7/DA1)            | ,<br>,  |            | signal output pin                                                                  |

| LCDEN                         | 43      | 0          | LCD controller enable signal output pin                                            |

| DOFF                          | 42      | 0          | LCD controller forced blank signal output pin                                      |

| YD                            | 41      | 0          | LCD controller scan start pulse output pin                                         |

| FR                            | 40      | 0          | LCD controller frame signal output pin                                             |

| XSCL                          | 39      | 0          | LCD controller shift clock output pin                                              |

| LP                            | 39      | 0          | LCD controller latch pulse output pin                                              |

| SD0~SD7                       | 37~30   | 0          | LCD controller data output pin                                                     |

| RESET                         |         |            |                                                                                    |

|                               | 64      | I          | Initial reset input pin                                                            |

| TEST                          | 15      | Ι          | Test input pin*1                                                                   |

Table 1.4.3 S1C88409 pin description (expanded 4M mode)

\*1  $\overline{\text{TEST}}$  is the terminal used for factory inspection of the IC. For normal operation, be sure to connect the  $\overline{\text{TEST}}$  terminal to VDD.

# 1.5 Mask Option

Mask options shown below are provided for the S1C88409. Several hardware specifications are prepared in each mask option, and one of them can be selected according to the application. The function option generator FOG88409, that has been prepared as the development software tool of the S1C88409, is used for this selection. Mask pattern of the IC is finally generated based on the data created by the FOG88409. Refer to the "S5U1C88409D Manual" for details on the FOG88409.

#### <Functions selectable with S1C88409 mask options>

#### (1) Bus mode

The bus mode that is set at initial reset can be selected. It is necessary to select it when using the S1C88409 in the MPU mode. Refer to Section 5.2, "System Controller and Bus Control", for details.

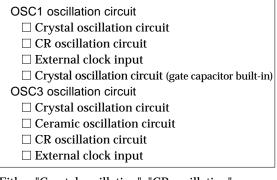

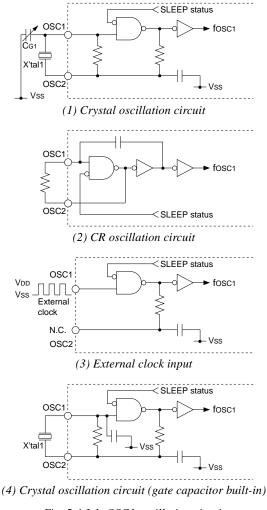

### (2) OSC1 oscillation circuit

The specification of the OSC1 oscillation circuit can be selected from among four types: "Crystal oscillation", "CR oscillation", "Crystal oscillation (gate capacitor built-in)" and "External clock input". Refer to Section 5.4.3, "OSC1 oscillation circuit", for details.

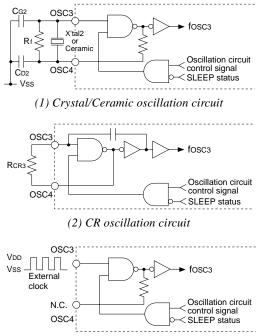

### (3) OSC3 oscillation circuit

The specification of the OSC3 oscillation circuit can be selected from among four types: "Crystal oscillation", "Ceramic oscillation", "CR oscillation" and "External clock input". Refer to Section 5.4.4, "OSC3 oscillation circuit", for details.

### (4) MCU/MPU terminal pull-up resistor

This mask option can select whether the pull-up resistor for the  $MCU/\overline{MPU}$  terminal is used or not.

### (5) RESET terminal pull-up resistor

This mask option can select whether the pullup resistor for the  $\overrightarrow{\text{RESET}}$  terminal is used or not.

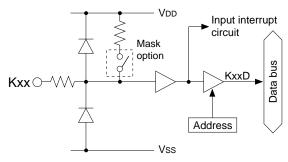

### (6) Input port pull-up resistor

This mask option can select whether the pullup resistor for the input port terminal is used or not. It is possible to select for each bit of the input ports. Refer to Section 5.6.2, "Mask option", for details.

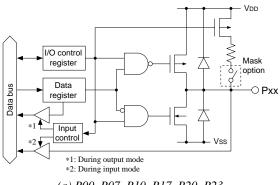

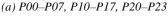

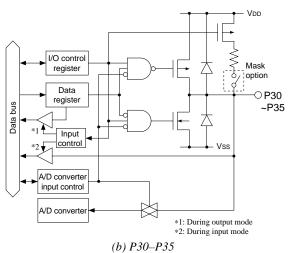

#### (7) I/O port pull-up resistor

This mask option can select whether the pullup resistor for the I/O port terminal (it works during input mode) is used or not. It is possible to select for each bit of the input ports. Refer to Section 5.8.3, "Mask option", for details.

### (8) Data RAM, Display RAM capacity

The S1C88409 has built-in 3.75KB RAM. The data memory/display memory size can be selected from seven types (256/3584, 512/3328, 768/3072, 1024/2816, 1280/2560, 1536/2304, 1792/2048 bytes) according to the LCD panel to be used. Refer to Section 3.2.2, "RAM (Data Memory, Display Memory)", for details.

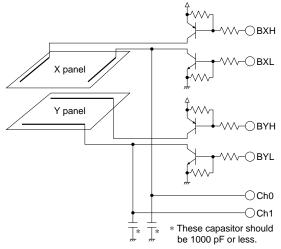

### (9) Touch panel control terminal

The control signal output terminals of the touch panel controller are shared with the I/O port terminals P20 to P23. The P20–P23 terminals can be set for either the touch panel controller or the I/O port. Refer to Section 5.17.2, "Terminal configuration", for details.

### (10) Touch panel controller input terminal

Two terminals can be selected from the I/O port terminals P30–P35 for inputting the X and Y coordinate detection signals of the touch panel to the A/D converter. Refer to Section 5.17.2, "Terminal configuration", for details.

# CHAPTER 2 POWER SUPPLY

This section explains the operating voltage and the configuration of the internal power supply circuit of the S1C88409.

### 2.1 Operating Voltage

Table 2.1.1 shows the operating voltage of the S1C88409.

Using a low voltage for VDD according to operating speed needs can reduce power consumption.

| Table 2.1.1 | Correspondence between operating voltage |

|-------------|------------------------------------------|

|             | and operating frequency                  |

| Operatable voltage range (VDD) | Max. clock frequency (OSC3) |

|--------------------------------|-----------------------------|

| 1.8 V to 5.5 V                 | 1.1 MHz                     |

| 2.6 V to 5.5 V                 | 4.4 MHz                     |

| 3.5 V to 5.5 V                 | 6.6 MHz                     |

| 4.5 V to 5.5 V                 | 8.8 MHz                     |

Note: I/O signal levels (high and low) that are described in this manual show the following voltage level if not otherwise noted.

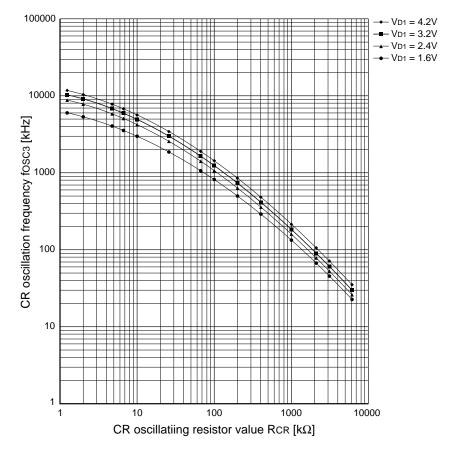

> High level = VDD Low level = Vss

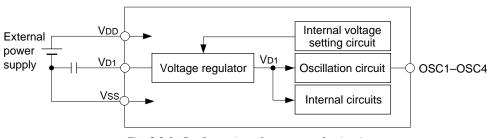

# 2.2 Internal Power Supply Circuit

The S1C88409 has the built-in power supply circuit shown in Figure 2.2.1. The power supply circuit generates the voltage VD1 for the internal circuits by supplying a voltage within the range mentioned above between the VDD (+) and Vss (GND) terminals.

VD1 voltage can be selected from among four types: 4.2 V (Max. 8.8 MHz), 3.2 V (Max. 6.6 MHz), 2.4 V (Max. 4.4 MHz) and 1.6 V (Max. 1.1 MHz). It should be selected by a program to switch according to the supply voltage and oscillation frequency.

Refer to Section 5.4, "Oscillation Circuit" for switching VD1.

Note: Be sure not to use the V<sub>D1</sub> terminal output for driving external circuits.

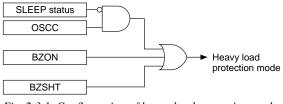

## 2.3 Heavy Load Protection Mode

The S1C88409 has a heavy load protection function for stable operation even when the supply voltage fluctuates by driving a heavy load. The heavy load protection mode becomes valid when the peripheral circuits are in the following status:

- The OSC3 oscillation circuit is switched ON (OSCC = "1" and not in SLEEP)

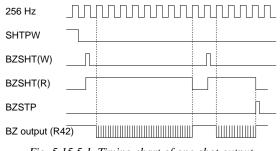

- (2) The buzzer output is switched ON (BZON = "1" or BZSHT = "1")

Fig. 2.3.1 Configuration of heavy load protection mode control circuit

For details of the OSC3 oscillation circuit and buzzer output, refer to Section 5.4, "Oscillation Circuit" and Section 5.15, "Sound Generator", respectively.

Fig. 2.2.1 Configuration of power supply circuit

**EPSON**

# CHAPTER 3 CPU AND MEMORY

This section explains the CPU, operating mode and bus configuration.

# 3.1 CPU

The S1C88409 employs the 8-bit core CPU S1C88 as the CPU, so that register configuration, instructions and so on are virtually identical to those in other family processors using the S1C88.

Refer to the "S1C88 Core CPU Manual" for details of the S1C88.

The S1C88 CPU model used is Model 3 and has up to  $4M \times 3$  address space that can be used for extended memory.

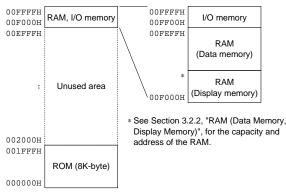

## 3.2 Internal Memory

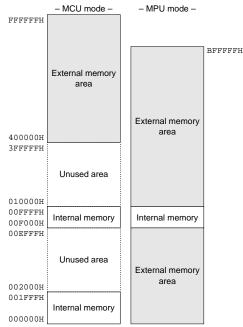

The S1C88409 has built-in ROM and RAM as shown in Figure 3.2.1.

Small-scale applications can be realized with only this chip. The internal memory can be used together with the external memory.

Furthermore, the internal ROM can be disconnected from the bus so that the space is released to external memory.

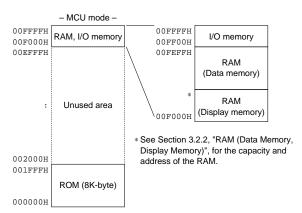

Fig. 3.2.1 Internal memory map

### 3.2.1 ROM

The internal ROM has a capacity of 8KB. Depending on the setting of the MCU/ $\overline{\text{MPU}}$  terminal, the internal ROM area can be released to external memory. (See Section 3.5, "Chip Mode".)

### 3.2.2 RAM (Data Memory, Display Memory)

The internal RAM has a capacity of 3.75KB. The data memory size and display memory size can be selected as shown in Table 3.2.2.1 by mask option.

| Table 3.2.2.1 | RAM | size | setting | by | mask | option |

|---------------|-----|------|---------|----|------|--------|

|---------------|-----|------|---------|----|------|--------|

|   |                 | 0 7 1           |

|---|-----------------|-----------------|

|   | Data memory     | Display memory  |

| 1 | 1792 bytes      | 2048 bytes      |

|   | 00F800H-00FEFFH | 00F000H-00F7FFH |

| 2 | 1536 bytes      | 2304 bytes      |

|   | 00F900H-00FEFFH | 00F000H-00F8FFH |

| 3 | 1280 bytes      | 2560 bytes      |

|   | 00FA00H-00FEFFH | 00F000H-00F9FFH |

| 4 | 1024 bytes      | 2816 bytes      |

|   | 00FB00H-00FEFFH | 00F000H-00FAFFH |

| 5 | 768 bytes       | 3072 bytes      |

|   | 00FC00H-00FEFFH | 00F000H-00FBFFH |

| 6 | 512 bytes       | 3328 bytes      |

|   | 00FD00H-00FEFFH | 00F000H-00FCFFH |

| 7 | 256 bytes       | 3584 bytes      |

|   | 00FE00H-00FEFFH | 00F000H-00FDFFH |

The internal RAM area is not released to external memory even when the external memory which overlaps the internal RAM area is expanded. Access to this area affects the internal RAM.

Note: The display memory area configured by mask option may be used as data memory. However, the stack area cannot be assigned there.

Refer to Section 5.10, "LCD Controller", for details of the display memory.

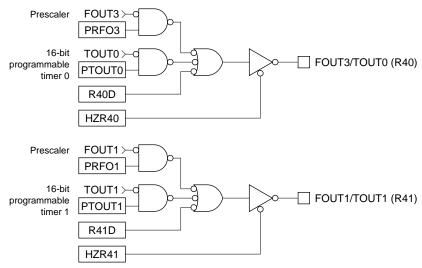

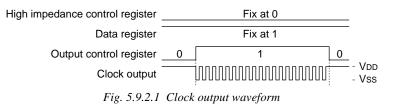

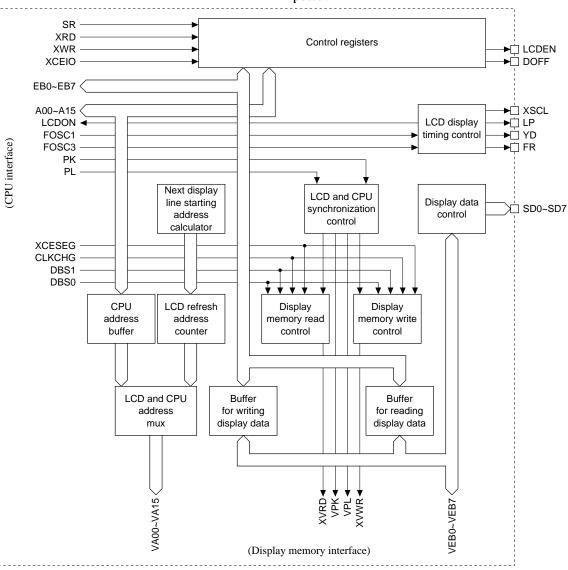

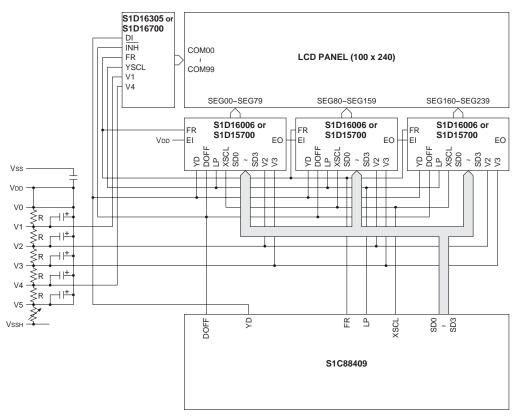

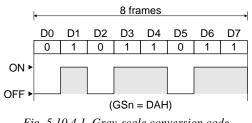

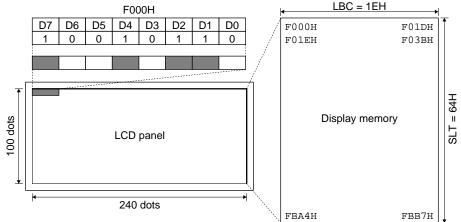

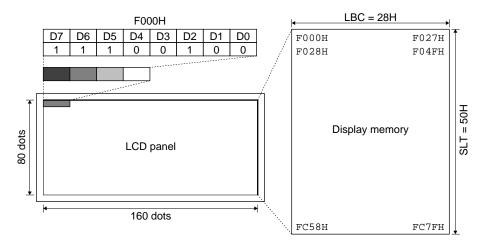

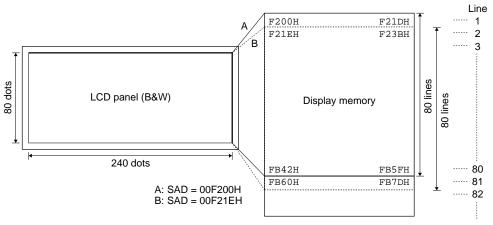

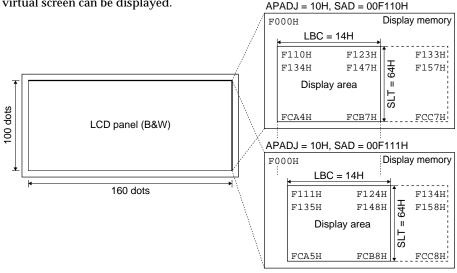

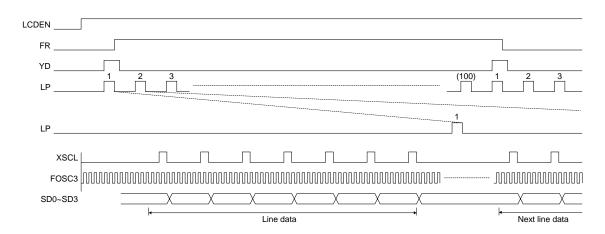

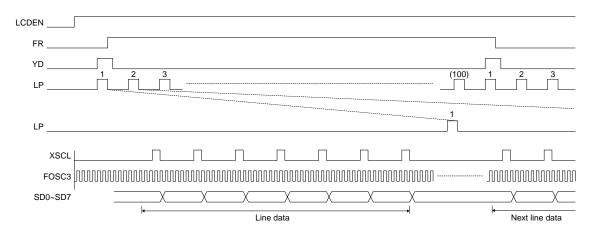

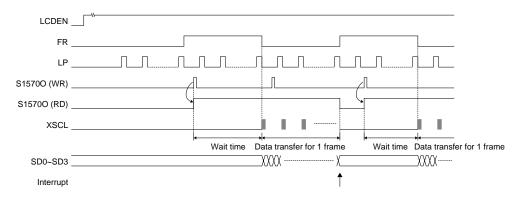

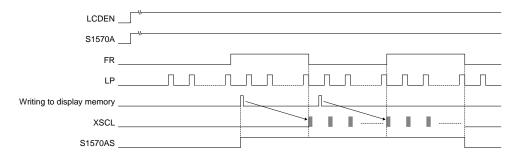

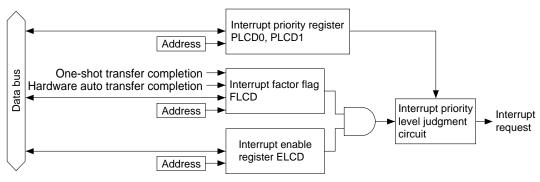

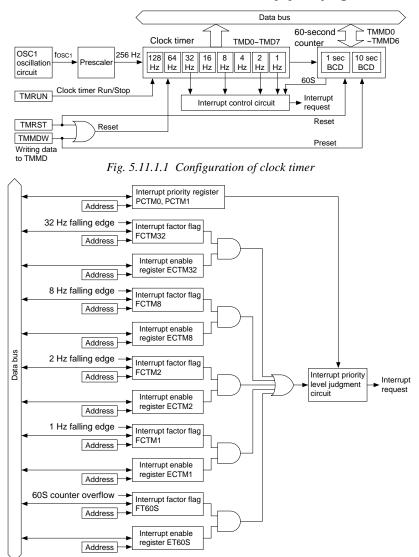

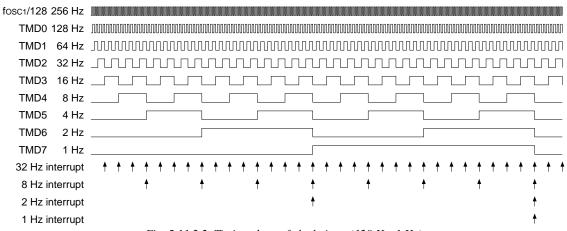

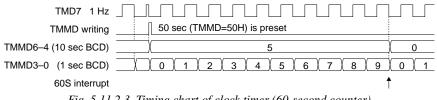

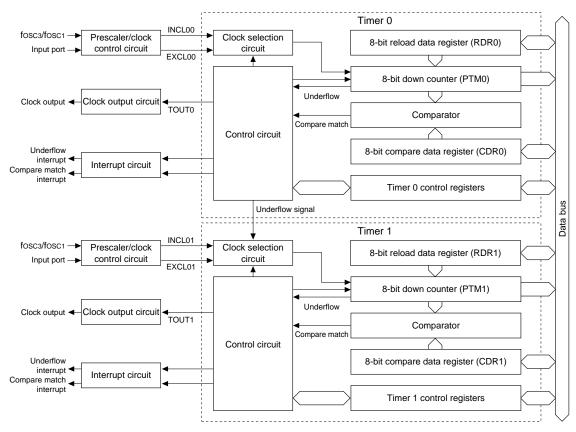

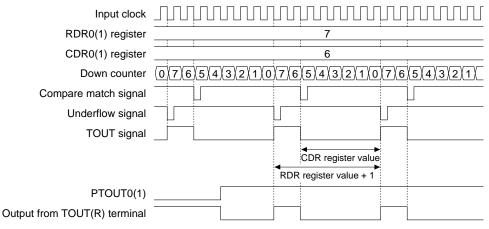

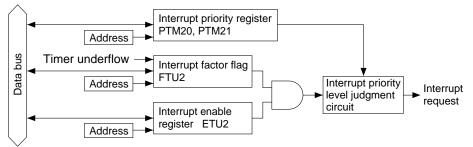

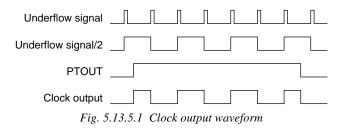

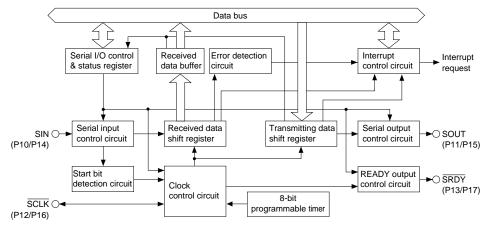

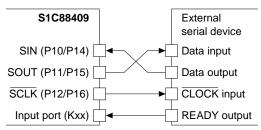

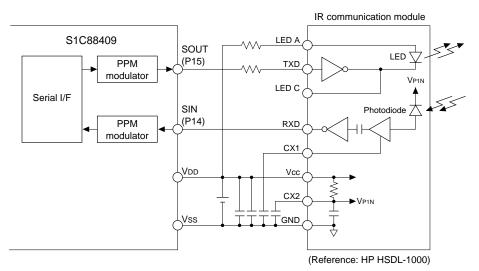

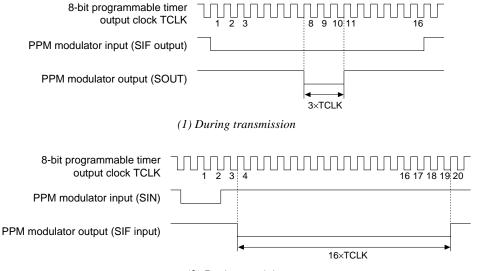

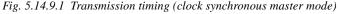

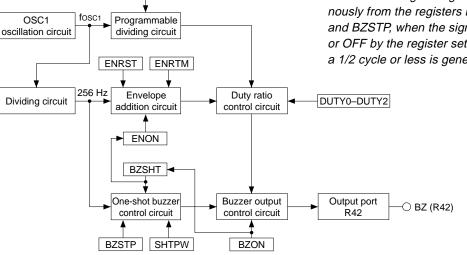

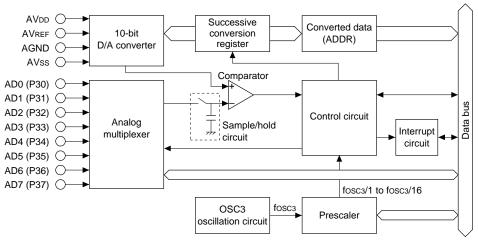

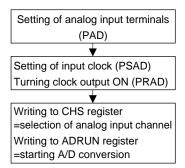

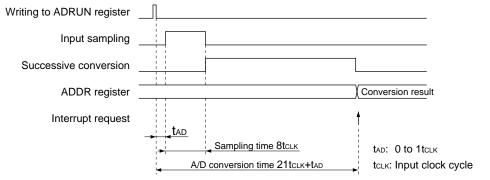

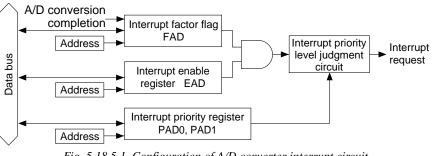

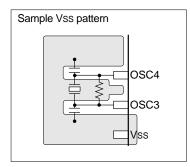

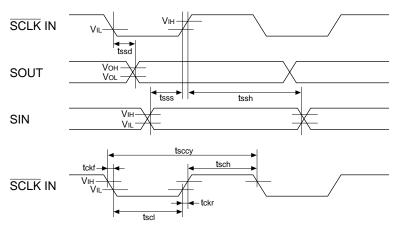

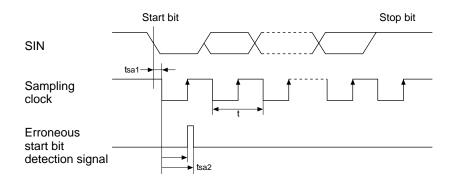

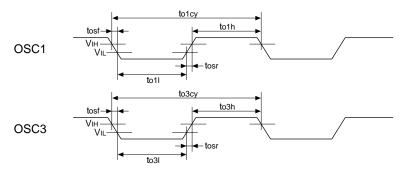

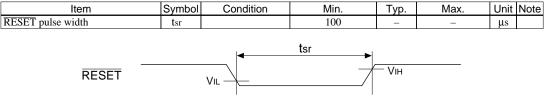

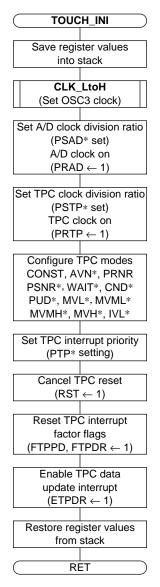

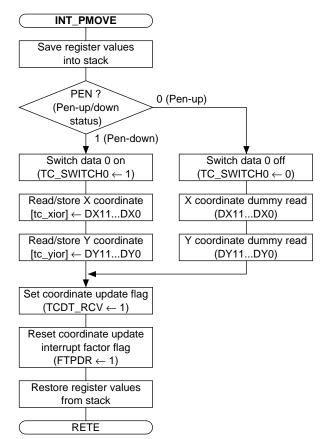

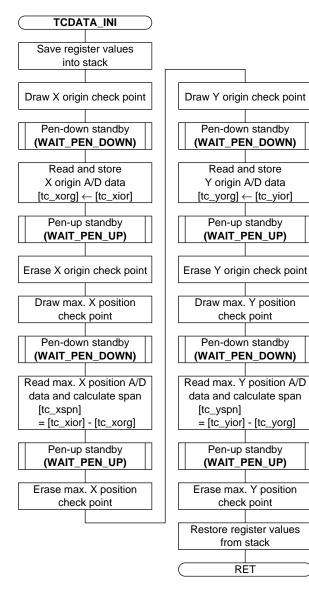

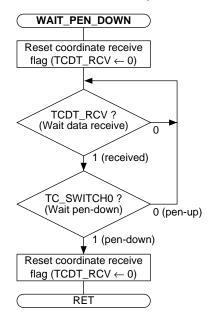

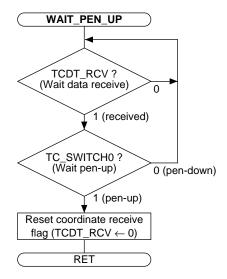

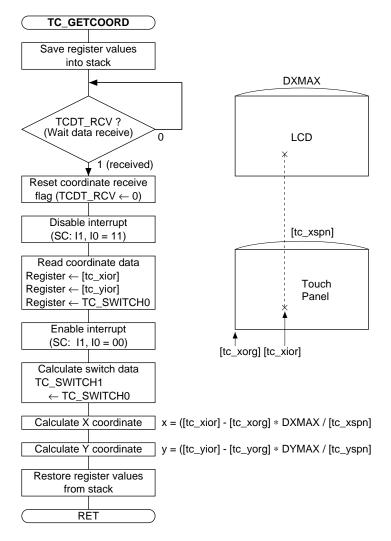

### 3.2.3 I/O memory