SMD Multilayer Varistor Array with Ni barrier Termination

CA06P4S17TLCG B72724A2170S162

Preliminary data sheet (parameters may be changed if necessary)

## **Designation System:**

- CA = <u>C</u>hip <u>A</u>rray

- 06 = Dimensions of the device  $\underline{06}x12$  (Length x width in 1/100 inch)

- P = Design (<u>P</u>arallel internal structure)

- 4 = Number of elements

- S = <u>S</u>pecial tolerance of the varistor voltage

- 17 = Max. operating voltage

- $T = \underline{T}$ hree-layer-termination

- LC = <u>L</u>ow <u>C</u>apacitance

- G = Taped version (blister tape, 7" reel, 3000 pieces/reel)

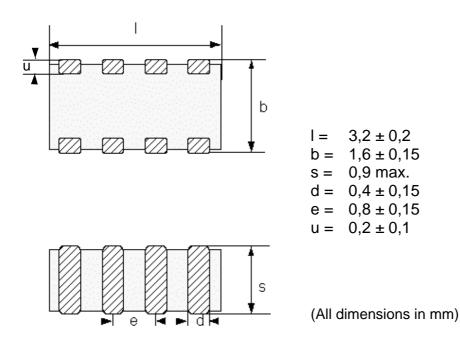

## Figure:

As far as patents or other rights of third parties are concerned, liability is only assumed for components per se, not for applications, processes and circuits implemented within components or assemblies. The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

| ISSUE DATE | 08.10.04 | ISSUE | а | PUBLISHER | KB VS PE | PAGE | 1/6 |

|------------|----------|-------|---|-----------|----------|------|-----|

|------------|----------|-------|---|-----------|----------|------|-----|

## SMD Multilayer Varistor Array with Ni barrier Termination

## CA06P4S17TLCG B72724A2170S162

Preliminary data sheet

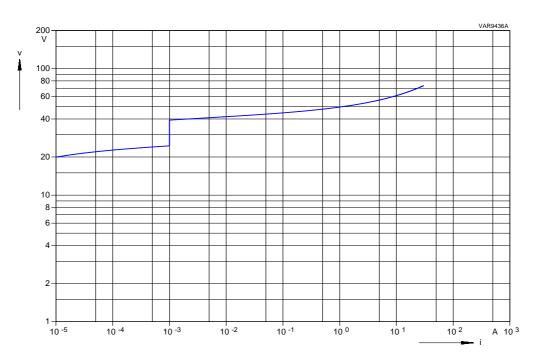

(parameters may be changed if necessary) **V-I-Characteristic:**

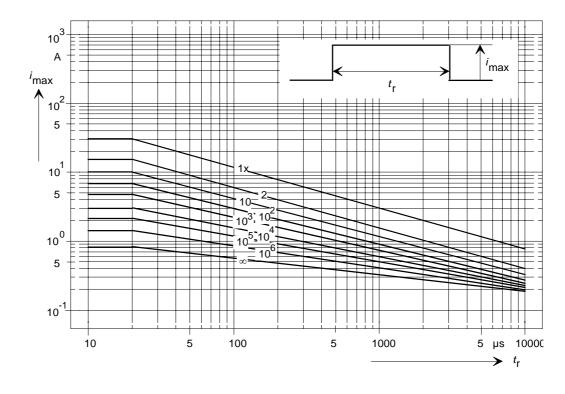

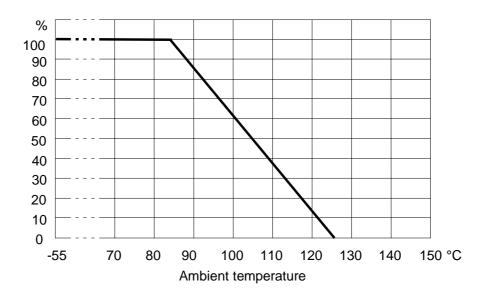

# **Derating field:**

| ISSUE DATE 08.10.04 | ISSUE | а | PUBLISHER | KB VS PE | PAGE | 2/6 |

|---------------------|-------|---|-----------|----------|------|-----|

|---------------------|-------|---|-----------|----------|------|-----|

| Metal Oxide Varistor                            |                                         | CA06P4S17TLCG   |

|-------------------------------------------------|-----------------------------------------|-----------------|

| SMD Multilayer Varistor Array with Ni barrier 1 | ermination                              | B72724A2170S162 |

| Preliminary data sheet                          |                                         |                 |

| (parameters may be changed if necessary)        |                                         |                 |

|                                                 |                                         |                 |

| Electrical Data                                 |                                         |                 |

|                                                 |                                         |                 |

| Max. operating voltage                          |                                         |                 |

| RMS voltage                                     | V <sub>eff</sub> = 17 V                 |                 |

| DC voltage                                      | V <sub>DC</sub> = 22 V                  |                 |

| Varistor voltage (@ 1 mA)                       | V <sub>V</sub> = 25 - 40 V              |                 |

| Max. clamping voltage (@ 1 A)                   | V <sub>C</sub> = 50 V                   |                 |

| Max. average power dissipation                  | $P_{max} = 3 \text{ mW}$                |                 |

| Max. surge current (8/20 µs)                    | $\hat{I}_{max} = 1 \times 30 \text{ A}$ |                 |

| Max. energy absorption (2 ms)                   | E <sub>max</sub> = 1 x 0.075            | J               |

| Capacitance (@ 1MHz, 0.5 V)                     | < 75 pF                                 |                 |

| Response time                                   | < 0.5 ns                                |                 |

| Operating temperature                           | -40 +85 °C                              |                 |

| Storage temperature (mounted parts)             | -40 +125 °C                             |                 |

SMD Multilayer Varistor Array with Ni barrier Termination

CA06P4S17TLCG B72724A2170S162

**Preliminary data sheet** (parameters may be changed if necessary)

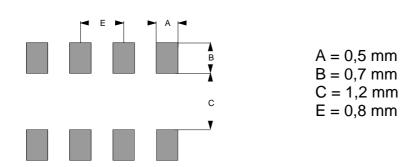

# **Recommended Geometry of Solder Pads**

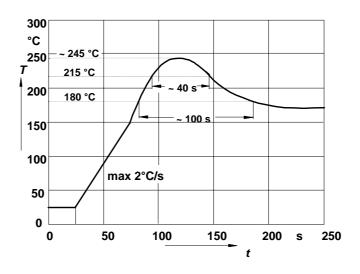

# **Recommended Soldering Temperature Profiles**

The components should be soldered within 12 months after delivery from EPCOS. The parts are to be left in the original packing in order to avoid any soldering problems caused by oxidized terminals.

Storage temperature: -25 to 45°C.

Relative humidity: <75% annual average, <95% on max. 30 days in a year.

The usage of mild, non activated fluxes for soldering is recommended, as well as proper cleaning of the PCB.

| ISSUE DATE |

|------------|

|------------|

SMD Multilayer Varistor Array with Ni barrier Termination

CA06P4S17TLCG B72724A2170S162

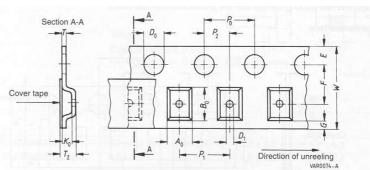

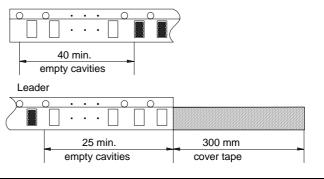

Preliminary data sheet (parameters may be changed if necessary) Taping and Packaging:

Taping: Tape and reel packing according to IEC 60286-3

Tape material: Blister

### **Dimensions and tolerances:**

| Definition                                 | Symbol         | Dimension | Tolerance           |

|--------------------------------------------|----------------|-----------|---------------------|

|                                            |                | [mm]      | [mm]                |

| Compartment width                          | A <sub>0</sub> | 1.9       | ± 0.2               |

| Compartment length                         | B <sub>0</sub> | 3.5       | ± 0.2               |

| Compartment height                         | K <sub>0</sub> | 1.3       | max.                |

| Sprocket hole diameter                     | D <sub>0</sub> | 1.5       | +0.1 /-0            |

| Compartment hole diameter                  | D <sub>1</sub> | 1.0       | min.                |

| Sprocket hole pitch                        | P <sub>0</sub> | 4.0       | ± 0.1 <sup>1)</sup> |

| Distance center hole to center compartment | P <sub>2</sub> | 2.0       | ± 0.05              |

| Pitch of the component compartments        | P <sub>1</sub> | 4.0       | ± 0.1               |

| Tape width                                 | W              | 8.0       | ± 0.3               |

| Distance edge to center of hole            | E              | 1.75      | ± 0.1               |

| Distance center hole to center compartment | F              | 3.5       | ± 0.05              |

| Distance compartment to edge               | G              | 0.75      | min.                |

| Overall thickness                          | T <sub>2</sub> | 2.5       | max.                |

| Thickness tape                             | Т              | 0.3       | max.                |

$^{1)} \le \pm 0.2$  mm over any 10 pitches Package: 8 mm tape:

| ISSUE DATE | 08.10.04 | ISSUE | а | PUBLISHER | KB VS PE | PAGE | 5/6 |

|------------|----------|-------|---|-----------|----------|------|-----|

|------------|----------|-------|---|-----------|----------|------|-----|

SMD Multilayer Varistor Array with Ni barrier Termination

CA06P4S17TLCG B72724A2170S162

Preliminary data sheet

(parameters may be changed if necessary)

#### Packing material: Plastic

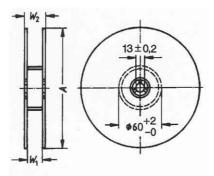

#### **Reel Dimensions:**

| Definition           | Symbol         | Dimension | Tolerance |

|----------------------|----------------|-----------|-----------|

|                      |                | [mm]      | [mm]      |

| Reel diameter        | A              | 180       | -3        |

| Reel width (inside)  | W <sub>1</sub> | 8.4       | +1.5 /-0  |

| Reel width (outside) | $W_2$          | 14.4      | max.      |

Packing unit: 3000 pcs / reel

© EPCOS AG 2004. Reproduction, publication and dissemination of this data sheet, enclosures hereto and the information contained therein without EPCOS' prior express consent is prohibited.

Purchase orders are subject to the General Conditions for the Supply of Products and Services of the Electrical and Electronics Industry recommended by the ZVEI (German Electrical and Electronic Manufacturers' Association), unless otherwise agreed.