# **EM6635**

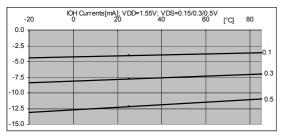

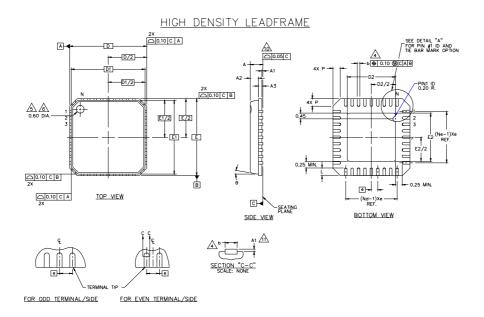

# Low Power Microcontroller with RC and 32kHz oscillators and 9 high drive outputs

#### **Features**

- □ 32'768Hz crystal oscillator

- □ 500kHz RC Oscillator (no external component)

- External clock (metal option)

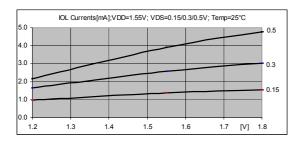

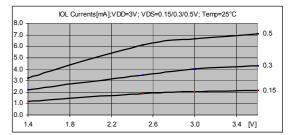

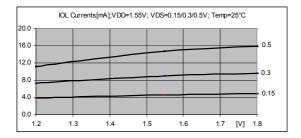

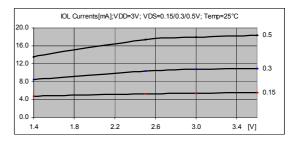

- 9 High drive outputs: up to 20mA

- Melody generator with 255 programmable frequencies

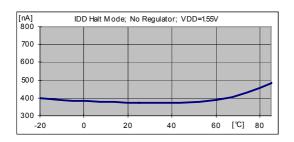

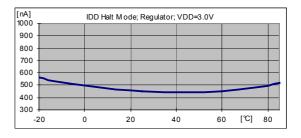

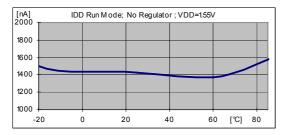

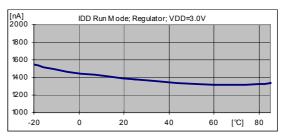

- □ True Low Power: 1.5uA active mode

0.4uA halt mode @ 1.55V, 32kHz, 25°C

- □ Low Supply Voltage 1.2V to 3.6V

- Max. 14 Inputs with selectable debouncers; Port P1, P2, P6, P70, P71

- Max. 15 outputs (9 I/O High drive outputs); Port P3, P4, P6, P70, P71, P72

- Mask ROM 4096 x 16bits

- □ RAM 256 x 4bits

- □ 2 clocks per instruction cycle

- 72 basic instructions

- 2 outputs; Reset OUT, Buzzer OUT

- ☐ 2 timers 8bits

- □ 2 x 4 bits BCD counters

- Event counter 3bits

- Prescaler down to 1Hz (crystal =32kHz), readable by CPU in 2 ranges

- □ Serial Port as selectable configuration of Port 5

- □ 18 Interrupts: 12 internal, 6 external

- □ Voltage Level Detector, 3 levels software selectable

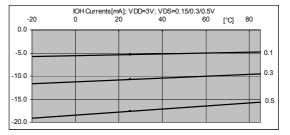

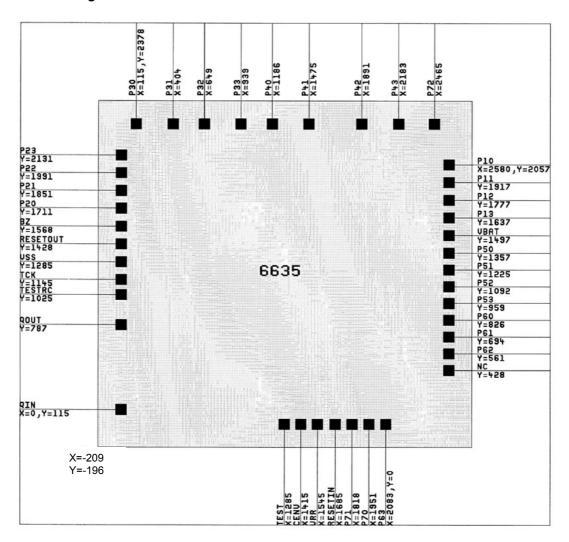

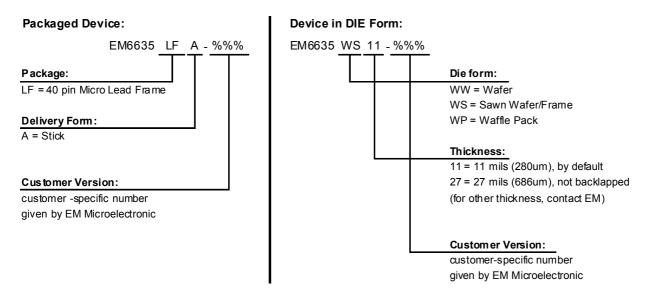

- Die form and MLF2, 40 pin (Micro Lead Frame) package

#### Description

The EM6635 is a low voltage, low power microcontroller containing 9 integrated high-drive outputs able to provide up to 20mA. It is ideal for use in applications in which one must drive devices such as motor drivers, small stepping motors, LEDs, triacs, external EEPROM or other ICs in the system.

EM6635 has both a 32kHz crystal oscillator and a 500kHz RC oscillator without external component, as well as an external clock to be driven up to 4MHz.

The CPU operating clock can be switched from crystal to RC oscillator for high-speed operation.

It has a frequency/melody generator with 255 programmable frequencies for quality buzzer.

The EM6635 contains the equivalent of 8kB mask ROM and the RAM has a capacity of 256x4 bits.

It also has a power-on reset, watchdog timer, 2 timers 8bits, 2 BCD counters, 3bits event counter, 4 wire serial port 8bits and several clock functions.

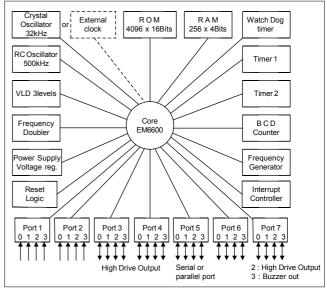

Figure 1. Architecture

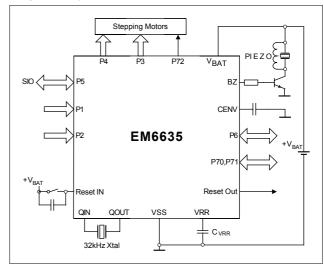

Figure 2. Typical application

#### **Applications**

- Watch & clock

- □ Timer / sports timing devices

- □ Security / industrial

- □ Toys

- □ Sensor interface

# EM6635 at a glance

#### □ Power Supply

- Low voltage low power architecture

- including internal voltage regulator

- 1.2 to 3.6 V battery voltage

- 1.5µA in active mode (Xtal, 25°C)

- 0.4 µA in HALT mode (Xtal, 25°C)

- 32'768Hz Crystal Oscillator

- 500kHz RC oscillator (no external component)

- External clock (metal option)

#### □ RAM

- 4 pages of 64 x 4bits, page 0 is direct addressable

#### □ ROM

- 4096 x 16bits, metal mask programmable

#### □ CPU

- 4-bits RISC architecture

- 2 clock cycles per instruction (CPI=2)

- 72 basic instructions

- operating frequency selectable by SW

#### Main Operating Modes and Resets

- Active mode, CPU is running

- Halt mode, CPU in halt, peripheral are running

- Initial reset on power on (POR)

- Watchdog reset (logic)

- Reset terminal with Schmitt Trigger

- Reset with input combination on Port P1 & Port P2 (register selectable)

#### □ Prescaler

- 15 stage system clock divider from 32kHz down to 1Hz

- 4 Interrupt requests; 128Hz, 64Hz, 32Hz and 1Hz or 64Hz, 16Hz, 8Hz and 1Hz

- Prescaler state readable to CPU from 128Hz to 16Hz and from 8Hz to 1Hz

- Prescaler reset (32Hz to 1Hz)

#### □ 8bit Serial Interface at Port 5

- 4 wire (serial clock In/Out, serial output, serial status In/Out (RDY), serial input)

- Master mode: 32kHz, 16kHz or 4kHz serial clock

- Slave mode: external clock from P33

- Selectable word length: 8 7 6 5 bit

- Selectable synchronized or direct output

- Selectable positive or negative active clock edge by direct or inverted serial clock SCK

- Special ready output mode when port is in master mode

- RDY can be set by SW

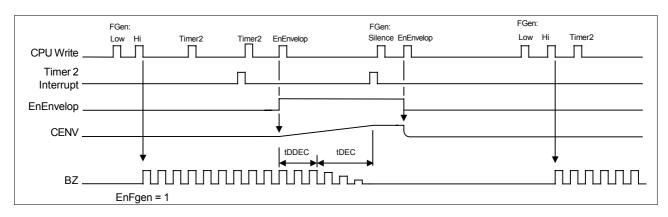

#### □ Frequency Generator with 255 output frequencies

- 8bit programmable frequency divider

- 50% duty cycle output signal

- Clock frequency is 65536Hz (doubled 32768Hz)

- SW activated

# □ Watchdog Timer

- Creates watchdog reset after time-out

- Can be disabled by SW and mask option

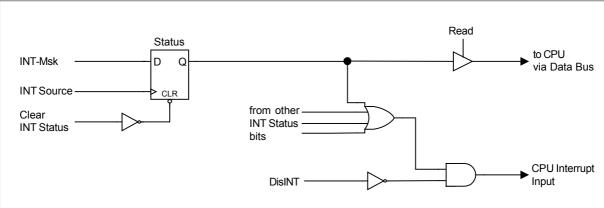

#### □ Interrupt Controller

- 12 internal, 6 external interrupt request sources

- Individually maskable, individually resettable

- Global interrupts disable, with auto-enable at HALT mode

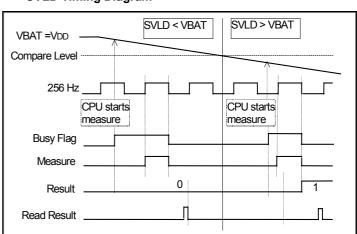

#### Voltage Level Detector (SVLD)

- 3 software selectable levels

- Busy flag during measure

- Active only on request during measurement to reduce power consumption

#### □ Timer 1

- 8bits timer with 3 modes: Zero Stop, Synchron Mode and Auto Reload Mode

- Timer clock selectable 4kHz-2kHz-1kHz-512Hz by SW

- Zero Stop: Timer starts counting down when loaded from CPU with data (> 0). When at zero, an interrupt is generated.

- Synchron Mode: After loading by CPU, timer starts synchronized by the positive edge of the prescaler 64Hz signal. An interrupt is generated when timer reaches zero. During timer count down, Port P3 and P4 are outputting their data, otherwise P3 and P4 are at high level (acc. to selected port configuration).

- Auto Reload Mode: (see text at Timer 2)

#### □ Timer 2

- 8bits timer with 2 modes: Zero Stop and Auto Reload

- Zero Stop as timer1

- Auto Reload mode: Timer starts when a non-zero data is loaded by CPU and counts down to zero. Then the loaded data (internally stored) is automatically reload to the timer counter and the sequence starts again. Each time when zero is reached, an interrupt is generated.

- Timer clock selectable 256Hz-64Hz-16Hz-4Hz by SW

#### ☐ CHRONO 2x4bits BCD counters

- Start, stop, reset by SW

- 1/100th second resolution

- CARRY flag can be read by SW when the counter changes from 99 to 0

#### ■ Event Counter 3bits

- Associated to input port P10, P11; readable to CPU

- Counter counts up to 7 and stays there

- Counter reset by CPU-write

#### ■ Buzzer Output

- Piezo driver via external NPN transistor

- Activated together with frequency generator

#### □ Input Ports P1, P2

- Direct or debounced input read selectable by SW for each port

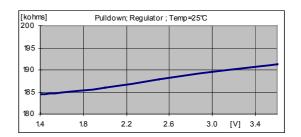

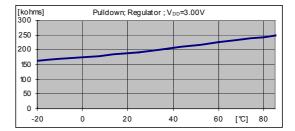

- Clocked pulldown or no pulldown by mask option

- P1: Edge detector at P10, P11 (both edges) to generate pulse for event counter

- Interrupt by P12: both edges, by P13: both edges

- Interrupt by positive edge (debounced) of any P2 input

- Reset by debounced input combination: P13, P22, P23 = high, enabled by SW

#### Input / Output Ports P3, P4, P5, P6, P7

- High current drive capability at P3, P4 and P72

- P3, P4: Common direction select P30-P32, P40-P42; P33 and P43 are individually selectable

- P5: individual direction select, debouncer when input

- As input: direct read of terminal data, as output: register data

- P3,P4,P72: selectable 9,8,7,6,5,4 or 3 high drive output in combination with special synchron mode of timer 1

- P5: pull down / pull up according to mask option

- P6: As input: Direct or debounced input read selectable by SW

- Interrupt by positive edge (debounced) of any P6 input

- Common direction select P60-P61, P62-P63

- P70, P71: As input: Direct or debounced input read selectable by SW for each port

- Interrupt by positive edge (debounced) of P70, P71 input

- Common direction select P70, P71

# 1. Pin Description

| Package<br>MLF2 | Function     | Symbol                  | Туре | Description                                                              |  |  |

|-----------------|--------------|-------------------------|------|--------------------------------------------------------------------------|--|--|

| 1               | Ports        | P23                     |      | Input port with selectable debouncer                                     |  |  |

| 2               |              | P22                     | ı    | Input port with selectable debouncer                                     |  |  |

| 3               |              | P21                     |      | Input port with selectable debouncer                                     |  |  |

| 4               |              | P20                     |      | Input port with selectable debouncer                                     |  |  |

| 5               | System       | BZ                      | 0    | Buzzer output                                                            |  |  |

| 6               | -            | RESET OUT               | 0    | Reset output                                                             |  |  |

| 7               | Power Supply | $V_{SS}$                |      | negative supply, substrate                                               |  |  |

| 8               | Test         | TCK                     |      | EM test access, must be without any connection                           |  |  |

| 9               |              | TESTRC                  |      | EM test access, must be without any connection                           |  |  |

| 10              | Oscillator   | QOUT                    |      | 32 kHz quartz connection, input <b>or</b> External clock (metal option)  |  |  |

| 11              |              | QIN                     |      | 32 kHz quartz connection, output                                         |  |  |

| 12              |              |                         |      | Not connected                                                            |  |  |

| 13              | Test         | TEST                    |      | EM test access, must be without any connection                           |  |  |

| 14              | System       | CENV                    |      | Capacitor connection for envelop control tw. V <sub>SS</sub>             |  |  |

| 15              | Power Supply | $V_{RR}$                |      | Regulated supply voltage, capacitor connection tw. V <sub>SS</sub>       |  |  |

| 16              | System       | RESET IN                | ı    | active high reset input                                                  |  |  |

| 17              | Ports        | P71                     | I/O  | Input/output; low current drive                                          |  |  |

| 18              |              | P70                     | I/O  | Input/output; low current drive                                          |  |  |

| 19              |              | P63                     | I/O  | Input/output; low current drive                                          |  |  |

| 20              |              | P62                     | I/O  | Input/output; low current drive                                          |  |  |

| 21              |              | P61                     | I/O  | Input/output; low current drive                                          |  |  |

| 22              |              | P60                     | I/O  | Input/output; low current drive                                          |  |  |

| 23              |              | P53                     | I/O  | Input/output: configurable as serial clock I/O: SCK                      |  |  |

| 24              |              | P52                     | I/O  | Input/output: configurable as serial output: SOUT                        |  |  |

| 25              |              | P51                     | I/O  | Input/output: configurable as serial status I/O: RDY                     |  |  |

| 26              |              | P50                     | I/O  | Input/output: configurable as serial input: SIN                          |  |  |

| 27              | Power Supply | VBAT (V <sub>DD</sub> ) |      | Positive supply, capacitor tw. V <sub>SS</sub> (C depends on VBAT noise) |  |  |

| 28              | Ports        | P13                     |      | Input port with selectable debouncer and edge detector                   |  |  |

| 29              |              | P12                     | I    | Input port with selectable debouncer and edge detector                   |  |  |

| 30              |              | P11                     | I    | Input port with selectable debouncer and edge detector                   |  |  |

| 31              |              | P10                     | ı    | Input port with selectable debouncer and edge detector                   |  |  |

| 32              |              | P72                     | I/O  | Input/output; high current drive                                         |  |  |

| 33              |              | P43                     | I/O  | Input/output; high current drive                                         |  |  |

| 34              |              | P42                     | I/O  |                                                                          |  |  |

| 35              |              | P41                     | I/O  |                                                                          |  |  |

| 36              |              | P40                     | I/O  | 1 ' 0                                                                    |  |  |

| 37              |              | P33                     | I/O  | Input/output; high current drive, P33 configurable as Fout               |  |  |

| 38              |              | P32                     | I/O  | Input/output; high current drive                                         |  |  |

| 39              |              | P31                     | I/O  | Input/output; high current drive                                         |  |  |

| 40              |              | P30                     | I/O  | Input/output; high current drive                                         |  |  |

|                 |              | NC/P63                  |      | Not connected                                                            |  |  |

#### 2. Peripheral Memory Allocation

| Address HEX | Peripheral Function            |  |  |  |

|-------------|--------------------------------|--|--|--|

| 0 - 3F      | Data RAM page 0, 1, 2, 3       |  |  |  |

| 40 - 46     | HW Control, Configuration      |  |  |  |

| 47 – 4C     | Input/output Ports             |  |  |  |

| 4D - 4F     | Free                           |  |  |  |

| 50 - 55     | Input/output Ports             |  |  |  |

| 56 – 5E     | Timer1, Timer2, BCD counter    |  |  |  |

| 5F          | Free                           |  |  |  |

| 60 – 6B     | Event Counter, Freq. Generator |  |  |  |

|             | Interrupt Controller           |  |  |  |

| 6C          | Supply voltage level detector  |  |  |  |

| 6D          | RC-Oscillator                  |  |  |  |

| 6E          | CPU Index Reg. Low             |  |  |  |

| 6F          | CPU Index Reg. Hi              |  |  |  |

| 70 - 74     | Serial Interface               |  |  |  |

| 75, 76      | EM Test                        |  |  |  |

| 77          | RAM Page Register              |  |  |  |

| 78          | Reserved                       |  |  |  |

| 79 – 7D     | Free                           |  |  |  |

| 7E          | EM Test                        |  |  |  |

| 7F          | EM Test                        |  |  |  |

#### Special Access Modes for HW-Control 1 and -2:

There are two HW-Control registers (HW-Ctl-1, HW-Ctl-2) with different access modes. Each of these two registers can be accessed by two different addresses. The access by address H40 for HW-Ctl-1 (H42 for HW-Ctl-2) is the normal access method as every other register in the EM6635: The corresponding data bus value is written into the register bit.

Using address H41 (HW-Ctl-1) or address H43 (HW-Ctl-2) allows a bitwise access to the register. The CPU has not to care about the states of the register bits which must not be modified.

With a high level at bits 0 to 2, the corresponding bits in the register are selected, while a low level unselects the register bits. The level of bit 3 defines the action on the selected bits: a high level will set and a low level will clear the selected register bits. Read access is done in the normal way.

If bits 0, 1, 2 are not selected (at Low level), the register at bit 3 is set if bit 3 is high or reset if it is low.

This concerns SelTBCapHi at HW-Ctl-2, address H43.

#### 2.1 RAM Address Modes

The EM6635 has 4 pages of 64x4bits RAM's built-in. The page number is coded on 2 bits, there are 4 pages.

The page number is stored on RAM index register at address H77.

The RAM is directly addressable on addresses decimal (0 to 63), and it is paged adressable.

To write or read the RAM page1, 2, 3 the user has first to set the offset value in the RAM Index register.

| RAM        | RAM index PageSel[1] PageSel[0] |   |  |  |  |  |

|------------|---------------------------------|---|--|--|--|--|

| PageSel[1] | Page                            |   |  |  |  |  |

| 0          | 0                               | 0 |  |  |  |  |

| 0          | 1                               | 1 |  |  |  |  |

| 1          | 0                               | 2 |  |  |  |  |

| 1          | 1                               | 3 |  |  |  |  |

#### Ram Architecture

| Add<br>Page | 64x4 direct<br>RAM | addressable | Add<br>Page | 64x4 indirect | t addressable | Add<br>Page | 64x4 indirect | t addressable | Add<br>Page | 64x4 indirect<br>RAM | addressable |

|-------------|--------------------|-------------|-------------|---------------|---------------|-------------|---------------|---------------|-------------|----------------------|-------------|

|             | RAM_0              | 4 bit R/W   |             | RAM_0         | 4 bit R/W     |             | RAM_0         | 4 bit R/W     |             | RAM_0                | 4 bit R/W   |

|             | RAM_1              | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | RAM_2              | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | RAM_3              | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | •                  | •           |             |               |               |             |               |               |             | •                    | •           |

| 0           | •                  | •           | 4           | •             | •             | 2           | •             | •             | 3           | •                    | •           |

| "           | •                  | •           | 1           |               | •             |             | •             | •             | 3           | •                    | •           |

|             | •                  | •           |             | •             | •             |             | •             | •             |             | •                    | •           |

|             | RAM_60             | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | RAM_61             | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | RAM_62             | 4 bit R/W   |             |               |               |             |               |               |             |                      |             |

|             | RAM_63             | 4 bit R/W   |             | RAM_63        | 4 bit R/W     |             | RAM_63        | 4 bit R/W     |             | RAM_63               | 4 bit R/W   |

#### **CPU Access Format:**

| Register  | Add Hex | Add Dec |   | bit3 | bit2 | bit1       | bit0       |

|-----------|---------|---------|---|------|------|------------|------------|

| RAM index | 77      | 119     | W | Х    | Х    | PageSel[1] | PageSel[0] |

|           |         |         | R | 0    | 0    | PageSel[1] | PageSel[0] |

#### 3. Operating Modes

The EM6635 has two low power operating modes, the active and the halt mode. The oscillator is always active in both modes, whereas the RC-Oscillator is controlled by the CPU.

#### 3.1 Active Mode:

The CPU is running. Instructions are read from the internal ROM and executed by the CPU.

After a system reset, the EM6635 is in active mode at ROM-address H000.

The active mode is stopped by executing the HALT instruction.

#### 3.2 HALT Mode:

After a HALT instruction, the EM6635 is in HALT mode. The CPU is stopped. The 32kHz-oscillator, the prescaler are running, whereas the timers, the watchdog timer, the BCD counters and the frequency generator are only working, if activated before.

The RC-oscillator is stopped.

All registers, RAM and output buffers retain their states prior to **HALT** mode.

The **HALT** mode is left by an interrupt occurrence or by a system reset.

The HALT command enables the global interrupt, i.e. DisINT=0.

Note: HALT mode is activated and XTAL Oscillator is not running. Only a system reset allows to go back in Active mode.

#### 4. Power Supply

The EM6635 is supplied by a single external power supply between V<sub>DD</sub> (VBAT) and V<sub>SS</sub> (Ground).

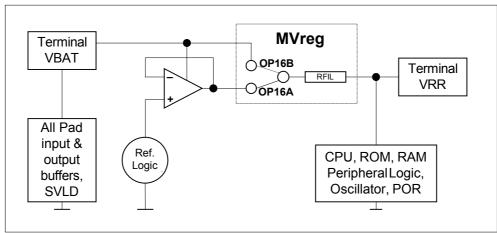

A built-in voltage regulator generates  $V_{RR}$  providing regulated voltage for the oscillator and the internal logic. The output drivers are supplied directly from the external supply  $V_{DD}$ . The internal power configuration is shown below in figure 3.

To supply the internal core logic it is possible to use either the internal voltage regulator ( $V_{RR} < V_{DD}$ ) or VBAT directly ( $V_{RR} = V_{DD}$ ). The selection is done by mask option. By default the voltage regulator is used. Refer to chapter 17 for the mask options.

The internal voltage regulator is chosen for high voltage systems. It saves power by reducing the internal core logic's power supply to an optimum value. However, due to the inherent voltage drop over the regulator the minimal  $V_{DD}$  is restricted to 1.4V.

A direct VBAT connection can be selected for systems running on a 1.5V battery. The internal RFIL 1kOhm resistor together with the external capacitor on  $V_{RR}$  is filtering the  $V_{DD}$  supply to the internal logic (as a low pass filter to protect the logic against parasitic over- and under-voltages, e.g. created by piezo shocks).

In this case the minimum  $V_{DD}$  can be as low as 1.2V. The output buffers are directly supplied from the external power supply.

**Note:** State of I/O pads may not be defined until  $V_{RR}$  reaches typ. 0.8V and Power-On-Reset supplied by  $V_{RR}$  clears them to inputs.

Fig.3: Power Supply Principle

#### 5. Reset

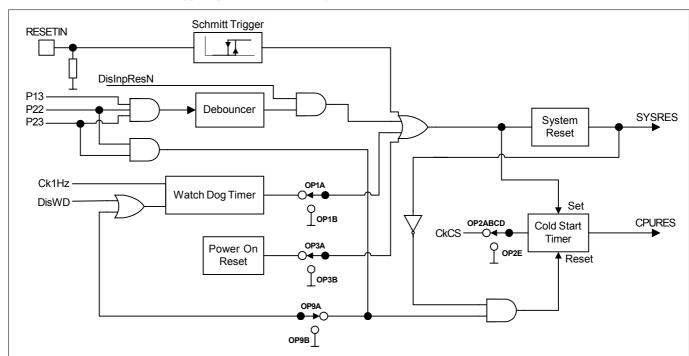

The EM6635 has 4 reset sources:

- the Power On Reset

- external reset input

- reset by input combination

- watchdog timer reset

If one of these reset sources becomes active, a system reset is generated. All registers are set to their corresponding initial values and the program counter of the CPU is set to H000.

If the EM6635 is in HALT mode, it is reset to active mode.

An internal Cold Start delay is triggered from the system reset, which holds the CPU in reset state until its time out. This ensures that the crystal oscillator can settle to stable oscillation.

The Cold Start delay time can be selected by mask option OP-2.

The Cold Start can be disabled by input P22 AND P23 = 1, if this input combination is applied longer than the duration of SYSRES signal (SYSRES terminates after the oscillator start time plus 10 valid clock time periods.) If this condition becomes active after the SYSRES has changed to low, but during an active Cold Start, the Cold Start will be stopped immediately. During the CPURES (corresponds to the Cold Start, after system starts on Xtal oscillator), pull down transistors are active at all port inputs.

Note that all 4 reset sources are triggering the Cold Start delay.

Fig.4: Reset Structure

#### 5.1 Power On Reset

The Power on Reset can be activated by mask option OP-3A.

When the positive power supply VBAT is applied, the internal logic supply voltage VRR rises to the VBAT value with a time constant given by the filter resistor RFIL and the external capacitor CVRR. The POR cell is active until VRR becomes higher than the trigger voltage VPOR of the POR cell. The output signal of the POR cell triggers the system reset.

The EM6635 has two oscillation circuits (refer to chapter 6 for the oscillators). With the metal option OP-20A, the oscillation circuit starts the operating clocks from RC oscillator. With the metal option OP-20B, the oscillation circuit starts the operating clocks from XTAL oscillator.

With the metal option OP-20C, the input P50 selects the RC oscillator or XTAL oscillator during SYSRES. A high level at P50 terminal activates the RC oscillator, a low level activates XTAL oscillator.

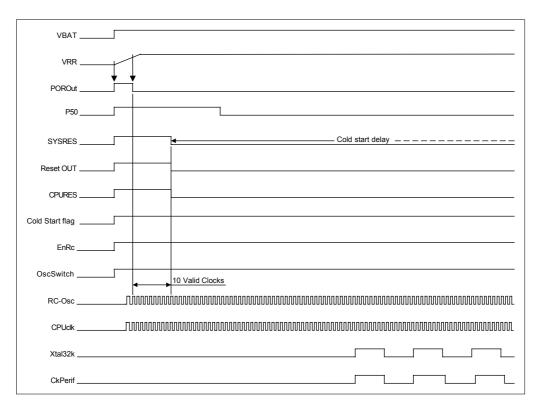

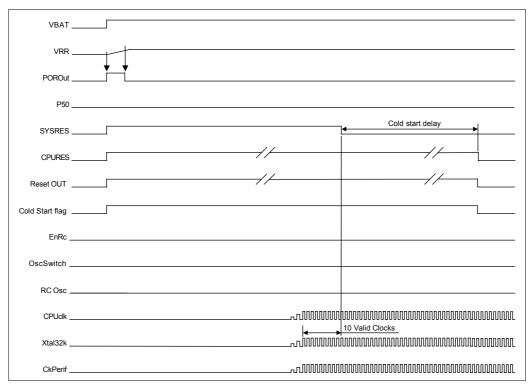

Fig.5: Power On Reset Timing and Clock Generation after System starts on the RC Oscillator

Fig.6: Power On Reset Timing and Clock Generation after System starts on Xtal Oscillator

#### 5.2 External Reset Input

A high level on the reset input "RESET" creates a system reset as long as it is applied. The reset input has an internal pull down resistor RRES, and includes a Schmitt Trigger circuit. The reset input creates the system reset in the same way as the POR signal, both are triggering the Cold Start delay for oscillator stabilisation.

# 5.3 Input Reset

If input reset is enabled by bit 3 of Config-2 register (at "0" level, address H45, in "DisInpRes"), a high level at input port P13 together with high levels at port P22 and P23 is creating a system reset after a debouncing time of 1.95ms (1 period of 512Hz). This reset is maintained as long as this input condition is applied.

# 5.4 Watchdog Timer Reset

The watchdog timer is a 2bits timer counting on rising edges of Ck1Hz. It generates a system reset if it is not cleared by the CPU periodically (writing "1" to HW-Ctl-1, bit 0, address H41).

This resets the watchdog timer to zero and timer operation restarts by counting up. Writing "0" has no effect.

The watchdog timer counts also in halt mode, therefore the standby duration must not exceed the watchdog time out tWD = 3-4sec to avoid a system reset.

Note: a prescaler reset is shortening the watchdog time out.

It is recommended to reset the watchdog timer periodically with the 1Hz interrupt.

The watchdog timer function is inhibited, if the input ports P22 and P23 are at high level, if this is enabled by mask option OP-9A

The watchdog timer can be disabled by Config-1 register, bit 2 at high level (H44), or by mask option OP-1B.

#### **CPU Access Format:**

| Register   | Add Hex | Add Dec |   | bit3       | bit2    | bit1     | bit0       |

|------------|---------|---------|---|------------|---------|----------|------------|

| HW-Ctl-1   | 41      | 65      | W |            |         | (DisINT) | ResetWD    |

| bit access |         |         | R | 0          | 0       | (DisINT) | 0          |

| Config-1   | 44      | 68      | W | (Mot3Mode) | DisWD   | (EnFOut) | (SellINT8) |

| _          |         |         | R | (Mot3Mode) | DisWD   | (EnFOut) | (SellINT8) |

| Config-2   | 45      | 69      | W | DisInpRes  | P5DebOn | P2DebOn  | P1DebOn    |

|            |         |         | R | DisInpRes  | P5DebOn | P2DebOn  | P1DebOn    |

#### 5.5 Reset Output

The Reset output outputs the CPU-reset signal. This signal is triggered by a system reset and its duration is the oscillator start time plus the cold start delay time.

The output buffer has the same electrical parameters as the port P5 output buffers.

#### 6. Oscillators

By metal option the 32kHz quartz oscillator can be replaced by external clock coming from QOUT terminal. When external clock is used Xtal oscillator can not work.

#### 6.1 32kHz Oscillator

The 32768Hz quartz oscillator of the EM6635 is working and supplies the timing functions with precise clock frequencies. The necessary oscillator capacitors are integrated within the EM6635, therefore the only external element needed is the 32kHz quartz.

The external impedance between QOUT and QIN terminal must be higher than 10MOhm.

As this type of oscillator has a relatively slow start-up behavior, precautions are necessary to make sure, that always corrects 32Khz clock signals are provided at the system start. The flag ColdStart in "RCOSC" to high level (bit2, address H6D) indicates an active Quartz Oscillator ColdStart delay when circuit starts to run under RC oscillator and ColdStart is not finished yet.

The 32kHz signal can be used to clock the µProcessor. This selection is done by setting OscSwitch in "RCOSC" to low level (bit 0, address H6D). The default selection at system start is the RC oscillator (metal option OP-20 A) or the Quartz oscillator (metal option OP-20 B).

#### 6.2 RC Oscillator

The EM6635 has an internal RC oscillator, which delivers a fast clock for the μProcessor. This RC oscillator can be switched On or Off by the CPU with EnRC in "RCOSC" (bit 1, address H6D). A high level activates the RC oscillator. After a system start, the RC oscillator is active (metal option OP-20 A is selected).

The  $\mu$ Processor can be configured to run with the 32kHz clock of the Quartz Oscillator. In this case, the RC oscillator can be set inactive. This selection is done by setting OscSwitch in "RCOSC" to low level.

#### **CPU Access Format:**

| Register | Add Hex | Add Dec |   | bit3 | bit2      | bit1 | bit0      |

|----------|---------|---------|---|------|-----------|------|-----------|

| RCOSC    | 6D      | 109     | W | Х    | Х         | EnRC | OscSwitch |

|          |         |         | R | 0    | ColdStart | EnRC | OscSwitch |

Note1: "RCOSC" register value is depending on supply voltage and metal option. With the metal option: OP-20B, Init=0100 and OP-20A, Init=0111. When 3.00V range is operating, register value can be set to 0111. When very low voltage e.g.1.2V is operating, register value must be set to 0000.

#### **6.3 External Clock Input**

RC and/or external clock where external clock replaces the Xtal frequency and supplies the main prescaler. These inputs must be specified according to mask option OP-19 and OP-20. See chapter 17. QOUT terminal becomes the external clock.

#### 6.4 Clock Switching Notes

When switching the  $\overline{CPU}$  from Quartz Oscillator to RC Oscillator, it's start-up time of max. 1ms must be respected. First EnRC must be set to 1 and after 1ms also OscSwitch can be set to 1. In order to synchronise the internal logic a Xtal clock of 32kHz is taken into account, then the RC Oscillator delivers fast clocks to the  $\mu$ Processor.

The internal voltage regulator at VRR terminal increases of 280mV typically. The stabilisation is depending of external loads (CVRR minimum = 100nF).

When switching off the RC Oscillator, first OscSwitch must be set to 0 and earliest in the following instruction EnRC can be cleared to 0. The internal voltage regulator decreases to its initial value.

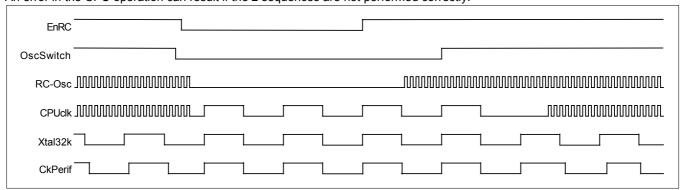

An error in the CPU operation can result if the 2 sequences are not performed correctly.

Fig.7: Clock Switching from RC-Oscillator to 32kHz and back

#### 7. Prescaler

The prescaler is a 15 stages divider chain, which delivers clock signals for the peripheral circuits such as timer, frequency generator, debouncer, etc. The input is the 32768Hz system clock from Quartz Oscillator or external clock.

**Note:** if external clock is applied it should be also 32768Hz to keep timing specified in this specification, in other case all timing change relative to external clock compared to 32768Hz.

The system reset initialises the prescaler to all 0, except the 1s stage, which is set to 1.

The prescaler generates four interrupt requests: INT-TB1, INT-TB2, INT-TB3, INT-TB4.

The source is selected by Sel/INT8.

| Interrupt | Sel/I      | NT8  |  |  |

|-----------|------------|------|--|--|

| apt       | 0          | 1    |  |  |

| TB1       | 1Hz        | 1Hz  |  |  |

| TB2       | 64Hz       | 8Hz  |  |  |

| TB3       | 32Hz       | 16Hz |  |  |

| TB4       | 128Hz 64Hz |      |  |  |

Both interrupts appear at the positive edge of the corresponding signal.

The first INT\_TB1 occurs 1 sec after the end of the system reset.

The prescaler can be reset partially from 32Hz to 1Hz by writing "1" to "ResetCK" of HW-Ctl-2 (bit 0 at address H43). A read access to that bit gives always "0".

Note: this prescaler reset shortens the watchdog time out tWD.

The prescaler creates a clock signal for the clocked pull down at inputs, e.g. at port P1. This is a 512Hz signal with an active time of 31µs if OP-6A is chosen or 64µs at OP-6B.

#### 7.1 Time Base Capture

The state of the prescaler stages 128Hz to 16Hz and 8Hz to 1Hz can be read by the CPU by a read access to address H55 (a write has no effect). The range selection is done by bit 3 of HW-Ctl-2, address H42 or H43. A "1" at this "SelTBCapHi" selects the range from 128Hz to 16Hz for read.

This time base capture capability is mostly designed for 4 bits application. The corresponding data are directly read from the prescaler. If two consecutive capture accesses are made to read the two ranges, the resulting data representation (8 bits) may not be coherent, due to a possible prescaler update event occuring to the 128 Hz stage plus its correlated carry to the following stages.

#### 8. EM6635 Input / Output Ports

#### 8.1 Input Port P1

The port P1 is a 4bits input port used to read the terminal logic levels P10 to P13 into the CPU.

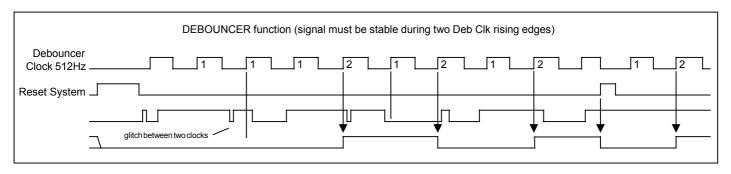

The port is equipped with 4 debouncers, which can be enabled by signal "P1DebOn", commonly for all 4 bits. With debouncers active, any input level must be present glitch free for at least the debounce time tDEB=1.95ms, to be transferred to the debouncer output, which can be read by the CPU.

When "P1DebOn" is at "0" level, the port P1 inputs are directly passed to the debouncer outputs.

Fig.8: Debouncer function

The port P1 has several special functions assigned to its inputs:

#### 8.1.1 Edge Detector

The port input P10 and P11 have edge detectors connected to the corresponding debouncer outputs. Both edge detectors create output signals of 488us at positive and negative edges. Each edge detector pulse from P10 or P11 input creates a pulse "M", which is the clock input for the event counter. Every change at P10 or P11 creates an "M" pulse. Also, an interrupt "M" is generated by this signal

The P13 input is logically combined as "AND" with P22 and P23 input, then input into a debouncer, whose output creates an Input Reset if enabled.

#### 8.1.2 Input Interrupt

The port P12 input (after debouncer) is connected to an edge detector, active at positive and negative edges. Its 488us output signal creates an interrupt P12 in register INT-Stat-2 (bit 0, address H66).

The port P13 input (after debouncer) is connected to an edge detector, active at positive and negative edges. Its 488us output signal creates an interrupt P13 in register INT-Stat-2 (bit 1, address H66).

#### 8.1.3 Input Pull Down

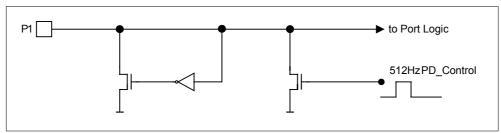

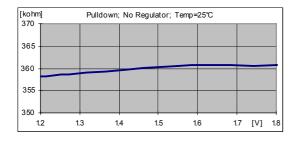

Each P1 input has associated pulldown transistors. These NMOS transistors are activated with a 512Hz signal with the duration of 31us (OP-6A) or 62us (OP-6B). A "0" input level is additionally hold by the circuitry shown in fig.8:

Fig.9: Port P1, P2 Input Pull Down

The pull down elements at port 1 can globally be disactivated by mask option OP-7B.

Note: Extra pull down transistors are active at this port during the CPURES signal.

#### **CPU Access Format:**

| Register | Add Hex | Add Dec |   | bit3        | bit2      | bit1      | bit0    |

|----------|---------|---------|---|-------------|-----------|-----------|---------|

| Config2  | 45      | 69      | W | (DisInpRes) | (P5DebOn) | (P2DebOn) | P1DebOn |

| -        |         |         | R | (DisInpRes) | (P5DebOn) | (P2DebOn) | P1DebOn |

| Port P1  | 47      | 71      | R | P13         | P12       | P11       | P10     |

#### 8.2 Input Port 2

The port P2 is a 4bits input port used to read the terminal logic levels P20 to P23 into the CPU.

The port is equipped with 4 debouncers, which can be enabled by signal "P2DebOn" commonly for all 4 inputs. With debouncers active, any input level must be present glitchfree for at least the debouncer time tDEB =1.95ms, to be transferred to the debouncer output, which can be read by the CPU.

When "P2DebOn" is at "0" level, the port P2 input is directly passed to the debouncer outputs.

#### Port 2 Interrupt:

Each debouncer output of port 2 is connected to the input of a positive edge dedector. The 4 edge detector outputs are logically combined as OR to create the P2 interrupt signal INT-P2 (bit 1, address H68).

In this way, any valid positive transition at P2 input can create an interrupt if not masked.

The P22 and P23 inputs are combined logically as "AND" with P13 input and applied to a debouncer. The debounced signal can create an Input Reset if not disabled by "DisInpRes".

Each P2 input has associated pull down transistors. These NMOS transistors are activated with a 512 Hz signal with the duration of 31µs (OP-6A) or 62µs (OP-6B). A "0" input level is additionally hold by the circuitry shown in Fig. 8. The pull down elements at port P2 can globally be disactivated by mask option OP-14B.

Note: Extra pull down transistors are active at this port during the CPURES signal.

| Register | Add Hex | Add Dec |   | bit3      | bit2      | bit1    | bit0      |

|----------|---------|---------|---|-----------|-----------|---------|-----------|

| Config2  | 45      | 69      | W | DisInpRes | (P5DebOn) | P2DebOn | (P1DebOn) |

|          |         |         | R | DisInpRes | (P5DebOn) | P2DebOn | (P1DebOn) |

| Port 2   | 48      | 72      | R | P23       | P22       | P21     | P20       |

#### 8.3 Input/Output Port P3

The port P3 is a 4bit input/output port with high current drive capability, e.g. for watch motor driver.

The port direction is controlled by the "PIO43 Ctl" register at address H52. The bit "P3-Dir" (bit 0, address H52) defines the direction of P30 to P32 commonly, whereas "P33-Dir" (bit 2, address H52) defines the individual direction of P33. A "1" level of the direction bit configures the corresponding port to be output, a "0" level defines it as input.

If the port P3 is configured as output, a write access to the P3 data register (address H50) stores the data into the internal port data register and the data appear at the corresponding port terminals. The port data register is only written when the port bit is output.

If a port P3 bit is read when the port is output, the data comes from the port output register. When the port is input, the data is read from the port terminal (output buffer in high impedance). The data LSB is at bit 0, the MSB at bit 3.

After system reset, the direction is input, the output data register contains "0000".

At port P3, no pull up or pull down element is available during normal operation.

Note: Extra pull down transistors are active at this port during the CPURES signal.

#### 8.3.1 Frequency Output

With mask option OP-18, the function of the output P33 can be modified directly or under CPU control. If OP-18A is chosen, the CPU can select with "ENFOut" set to "1", that the port P33 is set to output, but disconnected from its data register. Instead, it is configured as frequency output.

The output frequency is defined by the serial clock selection bits "SelSIOClk0, "1" in SIO-Ctl1(bit 3, address H72), independent of the "EnSIO" state, which enables the serial interface, configurated at port P5.

If the frequency output is set to 32 kHz, the output signal is the system clock from the quartz oscillator. In this case, the duty cycle is subject to higher tolerances than in case of the other possible output frequencies. If option OP-18B is chosen, the output P33 is always output for Fout, independently of the setting "ENFOut".

| SelSIOCIk1 | SelSIOCIk0 | Frequency at Fout = P33                        |

|------------|------------|------------------------------------------------|

| 0          | 0          | according to OP-8: 1kHz - 512Hz - 128Hz - 32Hz |

| 0          | 1          | 32kHz                                          |

| 1          | 0          | 16kHz                                          |

| 1          | 1          | 4kHz                                           |

# 8.3.2 Synchron Mode (Special Motor Mode)

If timer 1 is set to Synchron Mode by "SynMode" = "1", the port P3 operates in a special way, optimised to facilitate driving of watch motors.

The port must be set to output by the "PIO43-Ctl" register bits "P3-Dir" and/or "P33-Dir". An eventually "EnFOut" configuration has priority over Synchron Mode setting for port P33.

The Synchron Mode can work with the P30 to P32 bits alone or together with P33, if this port is also set to output and not frequency output.

#### Function:

As long as timer1 is not actively counting (its "TimerOn" signal is "0"), all the selected port P3 outputs are in "1" state. During active timer 1 counting, the selected P3 outputs correspond to the content of the port P3 output data register. The port state returns to all "1" after timer 1 has finished.

In this way, a predefined pattern loaded in the data output register appears synchronously with the timer 1 action for the programmed time at the P3 output, driving e.g. a stepper motor. (See also timer 1 description, Synchron Mode).

| Register  | Add Hex | Add Dec |   | bit3       | bit2    | bit1     | bit0   |

|-----------|---------|---------|---|------------|---------|----------|--------|

| Port P3   | 50      | 80      | W | P33 (Fout) | P32     | P31      | P30    |

|           |         |         | R | P33 (Fout) | P32     | P31      | P30    |

| PIO43 Ctl | 52      | 82      | W | (P43-Dir)  | P33-Dir | (P4-Dir) | P3-Dir |

|           |         |         | R | (P43-Dir)  | P33-Dir | (P4-Dir) | P3-Dir |

#### 8.4 Input / Output Port P4

The port P4 is similar to port P3: it is also a 4bits input/output port with high current drive capability, e.g. for watch motor driver.

The port direction is controlled by the "PIO43 Ctl" register at address H52. The bit "P4-Dir" (bit 1 of address H52) defines the direction of P40 to P42 commonly, whereas "P43-Dir" (bit 3 of address H52) defines the individual direction of P43. A "1" level of the direction bit configures the corresponding port to be output, a "0" level defines it as input.

If the port P4 is configured as output, a write access to the P4 data register (address H51) stores the data into the internal port data register and the data appear at the corresponding port terminals.

The port data register is only written when the port bit is output.

If a port P4 bit is read when the port is output, the data comes from the port output register. When the port is input, the data is read from the port terminal (output buffer in high impedance). The data LSB is at bit 0, the MSB at bit 3.

After system reset, the direction is input, the output data register contains "0000".

At port P4, no pull up or pull down element is available during normal operation.

Note: Extra pull down transistors are active at this port during the CPURES signal.

# 8.4.1 Synchron Mode

As port P3, port P4 can be configured in Synchron Mode. But additionally to the setting of timer 1 in "SynMode", the bit "Mot3Mode" in "Config1" register (bit 3, address H44) must be set to "0".

In this configuration, the selected number of port outputs can apply the loaded data pattern during timer 1 action to the output terminals, as explained in port P3 description.

The maximum number of outputs is 9 (included P72), other possible configurations are 8, 7, 6, or 4, 3 using P3 only. If "Mot3Mode" is set to "1", only port P3 is configured from "SynMode" of timer 1 as Synchron Mode output and P4 is normal input/output.

| Register  | Add Hex | Add Dec |   | bit3     | bit2      | bit1     | bit0     |

|-----------|---------|---------|---|----------|-----------|----------|----------|

| Config-1  | 44      | 68      | W | Mot3Mode | (DisWD)   | (EnFOut) | SelINT8  |

|           |         |         | R | Mot3Mode | (DisWD)   | (EnFOut) | SelINT8  |

| Port P4   | 51      | 81      | W | P43      | P42       | P41      | P40      |

|           |         |         | R | P43      | P42       | P41      | P40      |

| PIO43 Ctl | 52      | 82      | W | P43-Dir  | (P33-Dir) | P4-Dir   | (P3-Dir) |

|           |         |         | R | P43-Dir  | (P33-Dir) | P4-Dir   | (P3-Dir) |

#### 8.5 Input / Output Port P5

The port P5 is a 4bits input/output port with normal current drive capability outputs. It can be configured as a serial interface.

#### 8.5.1 Parallel Mode

The direction of each port bit can be defined individually by the "PIO5 Ctl" register (address H54). A bit of this register set to "1" defines the corresponding port terminal as output.

If the port P5 is configured as output, a write access to the P5 data register (address H53) stores the data into the internal port data register and the data appear at the corresponding port terminals.

The port data register is only written when the port bit is output.

If a port P5 bit is read when the port is output, the data comes from the port output register. When the port is input, the data is read from the port terminal (output buffer in high impedance). The data LSB is at bit 0, the MSB at bit 3. After system reset, the direction is input, the output data register contains "0000".

Note: Extra pull down transistors are active at this port during the CPURES signal.

As input, the port P5 is equipped with 4 debouncers, which can be enabled by signal "P5DebOn" (bit 2, address H45) commonly for all 4 bits. With debouncers active, the input level must be present glitch free for at least the debouncer time  $t_{DEB}$ =1.95ms, to be transferred to the debouncer output, which can be read by the CPU.

When "P5DebOn" is at "0" level, the port P5 inputs are directly passed to the debouncer outputs.

#### **CPU Access Format:**

| Register | Add Hex | Add Dec |   | bit3    | bit2    | bit1    | bit0    |

|----------|---------|---------|---|---------|---------|---------|---------|

| Port P5  | 53      | 83      | W | P53     | P52     | P51     | P50     |

|          |         |         | R | P53     | P52     | P51     | P50     |

| PIO5 Ctl | 54      | 84      | W | P53-Dir | P52-Dir | P51-Dir | P50-Dir |

|          |         |         | R | P53-Dir | P52-Dir | P51-Dir | P50-Dir |

#### 8.5.2 Serial Interface Mode

The port P5 is configured as 4 wire serial port, if "EnSIO" (bit 1, address H73) is set to "1".

In this serial mode, the port P5 bits have following functions:

P53: serial clock input/output: SCK

P52: serial output: SOUT

P51: serial status input/output: RDY

P50: serial input: SIN

It is possible, to select by SW the serial clock frequency, the serial word length, the active clock edge, the output mode and RDY function. Pull down or pull up resistors can be activated by mask option OP-10.

#### **General Description**

For data input, a 5 to 8bit shift register converts the serial input data from the SIN terminal to a parallel format, which can be read by the CPU. The low nibble is accessible at address H70: "SIO Low-Data" (LSB at bit0) and the high nibble is at "SIO Hi-Data" at address H71.

For data output, the CPU loads data into the shift register in two steps (SIO Low-Data and SIO Hi-Data), which is then output serially to SOUT terminal.

It is possible to simultaneously shift data out to SOUT and to shift data in from SIN.

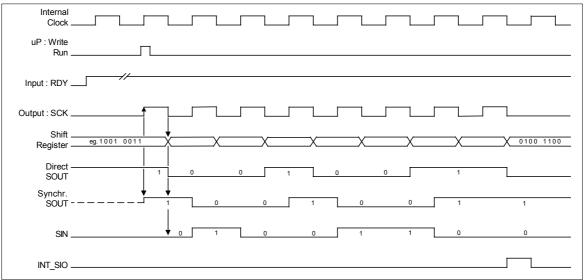

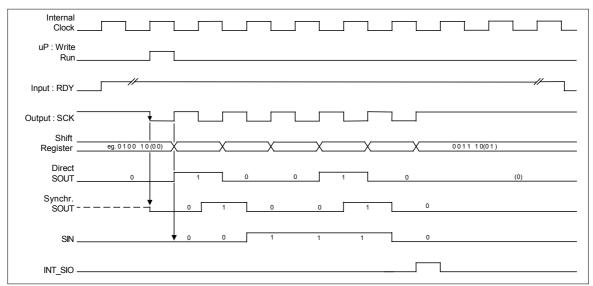

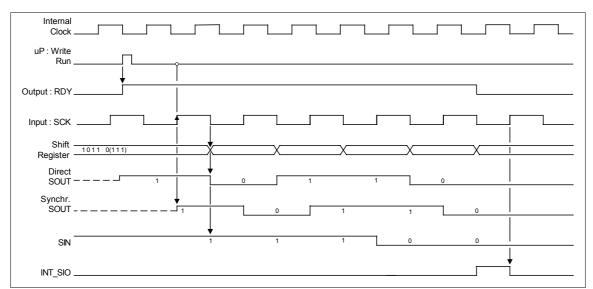

In the master mode, the serial clock is generated internally, corresponding to the selection done by "SIO-Ctl1" (address H72) and output to SCK.

In slave mode, an external clock is input to SCK.

The active clock edge is selected in "SIO Ctl2" by "NegEdg" bit 2, address H73.

The shift direction is always MSB-first.

The RDY signal controls the serial transmission or indicates to an external circuit, if the serial interface is ready for a new transmission. RDY is input in master mode and output in slave mode, if not otherwise configured by "SIO Ctl3" register. As output, RDY can also be set to "1" by the CPU.

After data nibbles are loaded in " SIO Low-Data " and " SIO Hi-Data " registers, the CPU can start a serial transmission by setting the "RUN" bit3 at "SIO-Ctl2" (address H73) to "1". (By writing "0" to "RUN", a current transmission is stopped without interrupt.)

In slave mode, the RDY output becomes "1" until the transmission is completed. In master mode, the RDY is input. The serial interface waits until the RDY input becomes "1" and starts then the transmission. (All RDY level indications are given for direct input/output selection done in "SIO Ctl3" by SelRDYPol1, -0)

The CPU can read the "RUN" status (bit3 at SIO Ctl2), which is cleared to "0" by the serial port logic when the transmission has finished.

As master, the serial port logic generates the number of serial clocks SCK according to the selected word length (in SIO Ctl1: SelWL1, 0, address H72).

After the last serial clock SCK, an interrupt INT\_SIO is generated (bit 0, address H68).

When slave, the external clocks applied to SCK are counted. When the defined number is reached, the transmission is stopped and interrupt INT-SIO is generated.

With "NegEdg" = "0" ("SIO Ctl2", bit2, address H73) the active SCK clock edge is positive, the shift register shifts at the negative edge. If "SelSynOut" is set to "1" (synchronised output mode), the output synchronisation is done with the positive clock edge. If "SelSynOut" is "0", the output SOUT is in direct output mode and changes with the negative clock edge as the shift register.

When "NegEdg" is set to "1", all above mentioned clock edges are inverted.

The SIO Low-Data and SIO High-Data register can only be read, if EnSIO is set to Hi.

Fig.10A: Serial Interface Operation Timing in Master Mode, 8bit, positive clock

Fig. 10B: Serial Interface Timing in Master Mode, 6 bit, negative clock

Fig. 10C: Serial Interface Timing in Slave Mode, 5 bit, positive clock

The register "SIO Ctl1" defines the serial clock frequency with "SelSIOClk1, 0" at bit 3, 2 and the serial word length with "SelWL1, 0" at bit 1, 0.

| SelSIOCIk1 | SelSIOCIk0 | SCK Frequency               | RDY    | Fout        |

|------------|------------|-----------------------------|--------|-------------|

| 0          | 0          | ext. clock: Slave Mode      | Output | acc. Option |

| 0          | 1          | 32kHz internal: Master Mode | Input  | CK32K       |

| 1          | 0          | 16kHz internal: Master Mode | Input  | CK16K       |

| 1          | 1          | 4kHz internal: Master Mode  | Input  | CK4K        |

| SelWL1 | SelWL0 | Serial Word Length |

|--------|--------|--------------------|

| 0      | 0      | 8 bit              |

| 0      | 1      | 7 bit              |

| 1      | 0      | 6 bit              |

| 1      | 1      | 5 bit              |

The mode of port P5 and output mode of serial mode are defined by "SIO Ctl2", "EnSIO" and "SelSynOut" according to following table:

| EnSIO | SelSynOut | Port 5 Mode                      |

|-------|-----------|----------------------------------|

| 0     | Х         | Parallel Input/output            |

| 1     | 0         | Serial Port, direct Output       |

| 1     | 1         | Serial Port, synchronized Output |

With "SIO Ctl3", the mode of the RDY signal can be defined in multiple ways. The polarity of RDY output and input is selected with "SelRDYPol1, -0" (bit 1, 0 of address H74) according to following table:

| SelRDYPol1 | SelRDYPol0 | RDY Polarity          |                    |

|------------|------------|-----------------------|--------------------|

| 0          | 0          | RDY is direct input   | or direct output   |

| 0          | 1          | RDY is inverted input | or direct output   |

| 1          | 0          | RDY is direct input   | or inverted output |

| 1          | 1          | RDY is inverted input | or inverted output |

The bit "RDYisOutput" (bit2 of SIO Ctl3) forces the RDY-terminal to be output, regardless of master- or slave mode, when set to "1" level.

The "RDYactive" (bit3 of SIO Ctl3) allows the CPU to set RDY-output directly to "1". The RDY output is then a logical OR function of this bit and the value delivered from the serial logic control. RDY must be set to output by RDYisOutput = Hi. If port P33 is configured as frequency output by "EnFOut" = "1", its frequency is the same as the serial clock in master mode and has the same polarity, if "NegEdg"is at "0".

#### 8.5.3 Pull Down / Up Resistors at Port P5

For each port P5 terminal, a pull down or a pull up resistor can be activated by mask option OP-10 to OP-13.

Activated resistors are only connected if the port terminal is input.

Activation is valid for parallel and serial mode of the port P5.

Each mask option offers 3 choices: A: no resistor B: pull up resistor C: pull down resistor

The options can be individually defined for each terminal.

#### **CPU Access Format:**

| Register     | Add Hex | Add Dec |   | bit3              | bit2        | bit1       | bit0             |

|--------------|---------|---------|---|-------------------|-------------|------------|------------------|

| SIO Low-Data | 70      | 112     | W | MSB Low Nibble <- |             |            | > LSB Low Nibble |

|              |         |         | R | MSB Low Nibble <- |             |            | > LSB Low Nibble |

| SIO Hi-Data  | 71      | 113     | W |                   |             |            |                  |

|              |         |         | R | MSB Hi Nibble <-  |             |            | > LSB Hi Nibble  |

| SIO Ctl1     | 72      | 114     | W | SelSIOClk1        | SelSIOClk0  | SelWL1     | SelWL0           |

|              |         |         | R | SelSIOClk1        | SelSIOClk0  | SelWL1     | SelWL0           |

| SIO Ctl2     | 73      | 115     | W | RUN               | NegEdg      | EnSIO      | SelSynOut        |

|              |         |         | R | RUN               | NegEdg      | EnSIO      | SelSynOut        |

| SIO Ctl3     | 74      | 116     | W | RDYactive         | RDYisOutput | SelRDYPol1 | SelRDYPol0       |

|              |         |         | R | RDYactive         | RDYisOutput | SelRDYPol1 | SelRDYPol0       |

#### 8.6 Input / Output Port P6

With the metal option OP-22B, the port P6 is a 4bits input/output port with normal current drive capability outputs.

The port direction is controlled by the "PIO67 Ctl" register at address H4C. The bit "P601-Dir" (bit 0, address H4C) defines the direction of P60, P61 and the bit "P623-Dir" (bit 1, address H4C) defines the direction of P62, P63. A "1" level of the direction bit configures the corresponding port to be output, a "0" level defines it as input.

If the port P6 is configured as output, a write access to the P6 data register (address H4A) stores the data into the internal port data register and the data appear at the corresponding port terminals. The port data register is only written when the port bit is output.

If a port P6 bit is read when the port is output, the data comes from the port output register. When the port is input, the data is read from the port terminal (output buffer in high impedance). The data LSB is at bit 0, the MSB at bit 3. After system reset, the direction is input, the output data register contains "0000".

As input, the port P6 is equipped with 4 debouncers, which can be enabled by signal "P6DebOn" (bit 0, address H46) commonly for all 4 bits. With debouncers active, the input level must be present glitch free for at least the debouncer time  $t_{\text{DEB}} = 1.95 \text{ms}$ , to be transferred to the debouncer output, which can be read by the CPU.

When "P6DebOn" is at "0" level, the port P6 inputs are directly passed to the debouncer outputs.

The port P6 input (after debouncer) is connected to an edge detector, active at positive edges. The 4 edge detector outputs are logically combined as OR to create the P6 interrupt signal INT-Stat-4 (bit 1, address H6A). In this way, any valid positive transition at P6 input can create an interrupt if not masked.

Note: Extra pull down transistors are active at this port during the CPURES signal.

For each port P6 terminal, a pull down or a pull up resistor can be activated by mask option OP-24 to OP-27. Activated resistors are only connected if the port terminal is input.

Each mask option offers 3 choices: A: no resistor B: pull up resistor C: pull down resistor

The options can be individually defined for each terminal.

| Register  | Add Hex | Add Dec |   | bit3      | bit2     | bit1      | bit0     |

|-----------|---------|---------|---|-----------|----------|-----------|----------|

| Config3   | 46      | 70      | W | Х         | Х        | (P7DebOn) | P6DebOn  |

|           |         |         | R | 0         | 0        | (P7DebOn) | P6DebOn  |

| Port 6    | 4A      | 75      | R | P63       | P62      | P61       | P60      |

| PIO67 Ctl | 4C      | 76      | W | (P72-Dir) | (P7-Dir) | P623-Dir  | P601-Dir |

|           |         |         | R | (P72-Dir) | (P7-Dir) | P623-Dir  | P601-Dir |

#### 8.7 Input / Output Port P7

With the metal option OP-23B, the port P7 is a 2bits input/output port P70, P71 with normal current drive capability outputs. P72 input/output is high current drive capability for watch motor driver (metal option OP-21A), 5mA led driver (metal option OP-21B, OP-21C) or only high current drive capability (metal option OP-21D).

As port P3 or P4, P72 can be configured in Synchron Mode. But additionally to the setting of timer 1 in "SynMode", the bit "Mot3Mode" in "Config1" register (bit 3, address H44) must be set to "0". For more details refer to chapter 8.3 and 8.4

The port direction is controlled by the "PIO67 Ctl" register at address H4C. The bit "P701-Dir" (bit 2, address H4C) defines the direction of P70 to P71 commonly. A "1" level of the direction bit configures the corresponding port to be output, a "0" level defines it as input.

The bit "P72-Dir" (bit 3, address H4C) defines the direction of P72.

If P70, P71and P72 are configured as output, a write access to the P7 data register (address H4B) stores the data into the internal port data register and the data appear at the corresponding port terminals. The port data register is only written when the port bit is output.

If P70, P71 and P72 bits are read when the port is output, the data comes from the port output register. When the port is input, the data is read from the port terminal (output buffer in high impedance). The data LSB is at bit 0, the MSB at bit 2. After system reset, the direction is input, the output data register contains "0000".

As input, P70 and P71 are equipped with 2 debouncers, which can be enabled by signal "P7DebOn" (bit 1, address H46) commonly for 2 bits. With debouncers active, the input level must be present glitch free for at least the debouncer time  $t_{DEB}$  = 1.95ms, to be transferred to the debouncer output, which can be read by the CPU.

When "P7DebOn" is at "0" level, P70 and P71 inputs are directly passed to the debouncer outputs.

P70, P71 inputs (after debouncer) are connected to an edge detector, active at positive edges. The 2 edge detector outputs are logically combined as OR to create the P7 interrupt signal INT-Stat-4 (bit 2, address H6A). In this way, any valid positive transition at P70 or P71 input can create an interrupt if not masked.

Note: Extra pull down transistors are active at this port during the CPURES signal.

For P70, P71 terminal, a pull down or a pull up resistor can be activated by mask option OP-28 and OP-29. Activated resistors are only connected if the port terminal is input.

Each mask option offers 3 choices: A: no resistor B: pull up resistor C: pull down resistor

The options can be individually defined for each terminal.

At P72, no pull up or pull down element is available during normal operation.

#### **CPU Access Format:**

| Register  | Add Hex | Add Dec |   | bit3    | bit2     | bit1       | bit0       |

|-----------|---------|---------|---|---------|----------|------------|------------|

| Config3   | 46      | 70      | W | Х       | Х        | P7DebOn    | (P6DebOn)  |

| -         |         |         | R | 0       | 0        | P7DebOn    | (P6DebOn)  |

| Port 7    | 4B      | 75      | R | 0       | P72      | P71        | P70        |

| PIO67 Ctl | 4C      | 76      | W | P72-Dir | P701-Dir | (P623-Dir) | (P601-Dir) |

|           |         |         | R | P72-Dir | P701-Dir | (P623-Dir) | (P601-Dir) |

Note: If the terminal P72 is not connected or not used, it must be an output.

A "1" level of the direction bit "P72-Dir" (bit 3, address H4C) configures as output.

In other case an over consumption will occur.

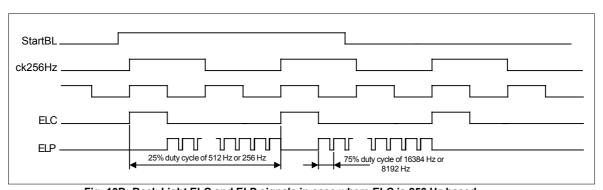

#### 8.7.1 Back Light function on P70 and P71

A special function of generating ELC and ELP clock can be attributed to P70 and P71 when selected and declared as outputs. Control bits for this function are in register Backlit.

#### **CPU Access Format:**

| Register | Add Hex | Add Dec |   | bit3  | bit2    | bit1     | bit0     |

|----------|---------|---------|---|-------|---------|----------|----------|

| Backlit  | 78      | 120     | W | Blout | StartBL | ELPcksel | ELCcksel |

|          |         |         | R | BLout | startBL | ELPcksel | ELCcksel |

ELC is a signal of 256 Hz or 512 Hz with 25 % duty cycle. Selection is done by bit ELCcksel.

**ELP** is a signal of 8.192 kHz or 16.384 kHz with 75% duty cycle which is inserted between ELC signal when ELC is low. Frequency selection is done by ELPcksel.

Function is initiated by writing **StartBL** control bit to 1 and **Blout** must be set to 1 to dedicate P70 when declared as output to ELC output and P71 to ELP output. Start of a sequence is synchronized by 512 or 1024 Hz signal from prescaler and repeats until StartBL bit is cleared to 0 while Blout is still set to 1. For proper sequence end first StartBL must be cleared to 0 and only when sequence finish – final ELC positive pulse following the end of StartBL, Blout can be cleared to 0 or port changed to input.

**Note:** when StartBL is cleared to end the sequence with the next positive ELC pulse, ELPcksel and ELCcksel selection bits must not be cleared but must keep the same value as when StartBL was set. If not the rest of the sequence will have default timing 256Hz for ELC and 8192Hz for ELP signal !!

By default this function is not selected and P70, P71 are general I/O pins as described in chapter 8.7.

| ELPcksel | ELCcksel | ELP freq [Hz] | ELC freq [Hz] |

|----------|----------|---------------|---------------|

| 0        | 0        | 8192          | 256           |

| 0        | 1        | 8192          | 512           |

| 1        | 0        | 16384         | 256           |

| 1        | 1        | 16384         | 512           |

Table showing ELP and ELC frequency selection

| Blout | P701-Dir | P70                   | P71                   |

|-------|----------|-----------------------|-----------------------|

| 0     | 0        | General Input         | General input         |

| 0     | 1        | General Output        | General Output        |

| 1     | 0        | General Input         | General Input         |

| 1     | 1        | Back light ELC Output | Back light ELP Output |

Table showing P70, P71 function depending on Blout and P701-Dir control bits

Fig. 10D: Back Light ELC and ELP signals in case where ELC is 256 Hz based.

In above picture it is shown that the sequence is started by setting StartBL to 1, together with ELPcksel and ELCcksel clock selection. Than it is synchronized to first rising edge of doubled frequency clock coming from the prescaler, that it starts with ELC 25% duty cycle signal and stops with one ELC positive pulse following the StartBL cleared to 0. Between ELC positive pulses (when ELC is low) is inserted ELP with 75% duty cycle of selected 16384 or 8192 Hz.

#### 9. Timer 1

The timer 1 can operate in three modes: the Zero Stop, the Synchron Mode and the Auto Reload Mode. The clock frequency can be selected by "SelT1F2" and "SelT1F1" control bits in "Timer1 Ctl" at address H56:

| SeIT1F2 | SelT1F1 | Timer 1 Clock Frequency |

|---------|---------|-------------------------|

| 0       | 0       | 512 Hz                  |

| 0       | 1       | 1024 Hz                 |

| 1       | 0       | 2048 Hz                 |

| 1       | 1       | 4096 Hz                 |

During active counting down, in all modes, the CPU can change the timer clock frequency. The new frequency is immediately applied, so the remaining timer counts until zero will be generated according to the new frequency selection. Inaccuracy is added, because the transitory counter cycle is generated with parts from two different clock periods. Additionally, a parasitic clock transition may be generated depending on the actual prescaler clock signal levels. The CPU writes divider data in two steps, first the higher 4bits into "Timer1 Hi-Data" (address H57) and then the lower 4bits into "Timer1 Low-Data" (address H58). This corresponds to an 8bit-timer.

The CPU can also write divider data in one step, only the lower 4 bits into "Timer1 Low-Data" (address H58). This corresponds to a 4bit-timer.

The timer contains an 8bits or a 4bits down counter, which can be loaded by the CPU via an autoreload register with "Timer1 Hi-Data" at address H57 (MSB at bit 3) and "Timer1 Low-Data" at address H58 (LSB at bit 0). The timer generates a "Timer1" interrupt (bit2, address H64) when it arrives at the all-zero-state of its counter. When a zero is loaded as data into the timer, and the timer is actively counting down, it is stopped, but no interrupt will occur.

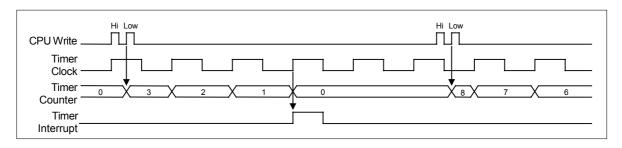

#### 9.1 Zero Stop Mode

If "SynMode" and "ARMode" are at "0", the timer1 is in Zero Stop Mode.

As soon as the CPU has written a non-zero value into "Timer1Hi-Data" and "Timer1 Low-Data", the timer1 starts counting down from this value with the selected clock frequency. When arrived at zero, the interrupt "Timer1" is generated. The timer remains at the zero state until it is loaded again with data.

The timer period from CPU write access to "Timer1" interrupt is:

Load Value\*Timer Clock Period - (0...1) Timer Clock Period

After a system reset, the timer is in Zero Stop Mode and in zero state.

If the timer 1 is reloaded by the CPU in Zero Stop mode, while it is counting, the actual counter state will be overwritten and a new counting down cycle starts with the new value loaded. No interrupt will be generated.

Fig.11: Timer 1 Timing in Zero Stop Mode

# 9.2 Synchron Mode

The timer 1 works in this special mode, when the "SynMode", bit3 of "Timer1 Ctl" is set to "1".

When the CPU has loaded non-zero data into the timer, the counter is not starting immediately. It waits to be triggered by the positive edge of the prescaler 64Hz signal. From this event on, it is counting down to zero and stops there. When arrived at zero, the interrupt "Timer1" is generated.

During its counting down action, the timer generates a "TimerOn" signal, which is used in port P3, P4 and P72 (metal option OP21-A) to enable data output (see description of ports P3, P4 and P7).

The timer period from positive edge of 64 Hz signal to timer1 interrupt is:

Load Value\*Timer Clock Period - 1/2 Timer Clock Period

Fig.12: Timer 1 Timing in Synchron Mode

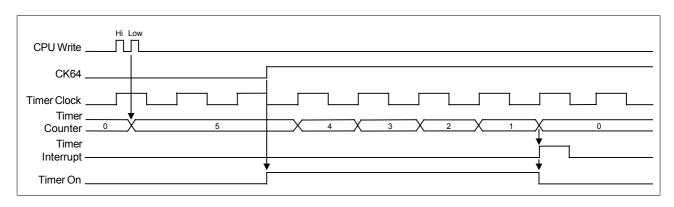

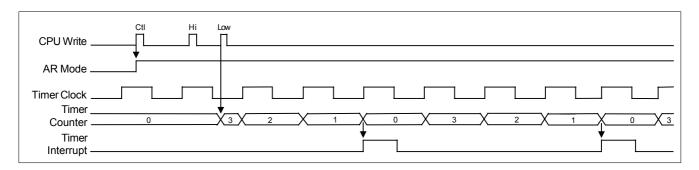

# 9.3 Auto Reload Mode

The timer 1 works in Auto Reload Mode, if the "ARMode", bit 2 of "Timer1 Ctl", address H56 is set to "1". The timer starts counting down, when a non-zero data is loaded into its 2 reload registers (address H57, "Timer1 Hi-Data" and address H58, "Timer1 Low-Data"). When the counter has arrived at zero state, a "Timer1" interrupt is generated. The counter is then automatically reloaded with the data stored in the reload register (previously written there by the CPU), and starts again to count down.

This sequence is repeated until the Auto Reload Mode is stopped by setting the "ARMode" bit to "0".

If the CPU reloads the timer while counting in Auto Reload mode, the actual sequence will be terminated normally. At the start of the next cycle, the new value is loaded into the counter and all following cycles are executed according to the new value loaded.

After setting "ARMode" to "0", the timer counts down to zero, generating an interrupt and stays then at zero. The Auto Reload Mode is only held by writing "0000" into the "Timer1 HI-Data" and the "Timer1Low-Data" reload registers. The timer1 period in the Auto Reload Mode is (1+Load Value) \* Clock Period, from interrupt to interrupt. The duration from CPU writes access to 1. Timer1 interrupt is LoadValue\*Timer Clock Period - (0...1) Timer Clock Period If an all-zero data is written into the reload register, no interrupt will be generated and the timer1 remains at this state until a non zero data is written into the reload register. Then, the described sequence starts again.

The "ARMode" and the "SynMode" can be combined: the two control bits "ARMode" and the "SynMode" (bits 2 and 3 of address H56) are set to "1". The timer 1 starts then synchronised by the 64Hz signal in Auto Reload Mode and ports P3, P4 and P72 (metal option OP21-A) are outputting data as described in 8.3, 8.4 and 8.7.

| Register        | Add Hex | Add Dec |   | bit3    | bit2         | bit1    | bit0    |

|-----------------|---------|---------|---|---------|--------------|---------|---------|

| Timer1 Ctl      | 56      | 86      | W | SynMode | ARMode       | SelT1F2 | SelT1F1 |

|                 |         |         | R | SynMode | ARMode       | SelT1F2 | SelT1F1 |

| Timer1 HI-Data  | 57      | 87      | W | MSB     | (hi nibble)  |         |         |

|                 |         |         | R | MSB     |              |         |         |

| Timer1 Low-Data | 58      | 88      | W |         | (low nibble) |         | LSB     |

|                 |         |         | R |         |              |         | LSB     |

#### 10. Timer 2

The timer 2 can operate in two modes: The Zero Stop Mode as explained in timer1 description and the Auto Reload Mode. The clock frequency can be selected by "SelT2F2" and "SelT2F1" control bits in "Timer2 Ctl" at address H59:

| SelT2F2 | SelT2F1 | Timer 2 Clock Frequency |

|---------|---------|-------------------------|

| 0       | 0       | 4 Hz                    |

| 0       | 1       | 16 Hz                   |

| 1       | 0       | 64 Hz                   |

| 1       | 1       | 256 Hz                  |

The timer 2 has the same general structure as timer 1, see description there.

#### 10.1 Zero Stop Mode

The operation in this mode is the same as for timer 1, only the CPU access address is H5A for "Timer2 Hi-Data", H5B for "Timer2 Low-Data" and H59 for "Timer2 Ctl".

#### 10.2 Auto Reload Mode

This mode of timer2 is enabled, if the "ARMode", bit2 of "Timer2 Ctl", address H59 is set to "1".

The timer starts counting down, when a non-zero data is loaded into its 2 reload registers (address H5A, "Timer2 Hi-Data" and address H5B, "Timer2 Low-Data"). When the counter has arrived at zero state, a "Timer2" interrupt is generated (bit 3, address H64).

The counter is then automatically reload with the data stored in the reload register (previously written there by the CPU), and starts again to count down.

This sequence is repeated until the Auto Reload Mode is stopped by setting the "ARMode" bit to "0". The Auto Reload Mode is only hold by writing "0000" into the "Timer2 Hi-Data" and "Timer2 Low-Data" reload registers.

The timer 2 period in the Auto Reload Mode is the same as defined for timer1 in Auto Reload Mode, see there. If an all-zero data is written into the 2 reload registers, no interrupt will be generated and the timer 2 remains at this state until a non-zero data is written into the 2 reload registers. Then, the described sequence starts again.

Fig.13: Timer 2 Timing in Auto Reload Mode

| Register        | Add Hex | Add Dec |   | bit3 | bit2         | bit1    | bit0    |

|-----------------|---------|---------|---|------|--------------|---------|---------|

| Timer2 Ctl      | 59      | 89      | W | Х    | ARMode       | SelT2F2 | SelT2F1 |

|                 |         |         | R | 0    | ARMode       | SelT2F2 | SelT2F1 |

| Timer2 Hi-Data  | 5A      | 90      | W | MSB  | (hi nibble)  |         |         |

|                 |         |         | R | MSB  |              |         |         |

| Timer2 Low-Data | 5B      | 91      | W |      | (low nibble) |         | LSB     |

|                 |         |         | R |      | ·            |         | LSB     |

#### 11. BCD counter/CHRONO

The EM6635 has an 8bits BCD counter or Chrono Block.

It contains a 100Hz generator, clocked from Prescaler, and a cascade of 2 BCD counters, which generate BCD-data for 1/100s and 1/10s digits.

The Chrono Block generates an interrupt BCD in register INT-Stat-4 (bit0, address H6A). The source of the interrupt is the 1/10s BCD counter overflow (transition from state "9" to "0") or the corresponding transition of 1/100s BCD counter. The mask bit BCD in register INT-Stat-4 can be reset by the CPU. A corresponding mask bit at high will enable the corresponding interrupt, a low level disables this interrupt (bit0, address H6B).

The CPU can start the chrono function by setting BCDRun in "BCDCtl" to high level (bit0, address H5C). This enables the 100Hz chrono clock and the BCD counters.

The CPU can stop the chrono counter by resetting this BCDRun to low level. By this, the clock of the counters is stopped, but the state of the counters is maintained, e.g. to be read later.

The CPU can reset the BCD counters by writing high to BCDRes in "BCD Ctl" (bit1, address H5C), independently of the actual mode of the BCD counters (counting or stopped).

The BCDRes is automatically reset after it has cleared the counters; a read access gives always a low level.

The CPU can read the state of the BCD counters in register BCD 1/100 while the counters are counting or when stopped. The 4bits of "BCD 1/100" register represent the 1/100s digit data and the 4 bits of "BCD 1/10" register represent the 1/10s digit data in BCD format.

The MSB's of this data are at bit3 of "BCD 1/100" register (address H5D), respectively at bit3 of "BCD 1/10" (address H5E).

The CPU can select an event each 100ms by setting this BCDEvent to high level in "BCD Ctl" (bit2, address H5C) or each second BCDEvent to low level.

The Chrono Block generates a carry flag when the counter changes from 99 to 00. The CPU can read the flag in register "BCD Ctl" (bit3, address H6B). State "1" indicates an increment of 1s. State "0" indicates no increment. When "1" is written, the BCDCarry is cleared. When "0" is written, no change occurs.

#### **CPU Access Format:**

| Register  | Add Hex | Add Dec |   | bit3       | bit2     | bit1   | bit0   |  |

|-----------|---------|---------|---|------------|----------|--------|--------|--|

| BCD Ctl   | 5C      | 92      | W | BCDCarry   | BCDEvent | BCDRes | BCDRun |  |

|           |         |         | R | BCDCarry   | BCDEvent | 0      | BCDRun |  |

| BCD 1/100 | 5D      | 93      | - |            |          |        |        |  |

|           |         |         | R | MSB <> LSB |          |        |        |  |

| BCD 1/10  | 5E      | 94      | - |            |          |        |        |  |

|           |         |         | R | MSB <      | BCD 1/   | 10     | > LSB  |  |

#### 12. Event Counter

The EM6635 has a 3bits event counter, capable to count the "M" pulses, which are generated by input port P1 (see description of port P1). The counting direction is upwards. When the event counter arrives at "111" (= decimal 7), it stops counting and remains at this state.

The state of the event counter can be read by the CPU at any time by reading "Event Counter" at address H60, bits 2, 1 and 0; The bit3 is always read as "0".

A write access to this address H60 clears the event counter to "000", independent of the data value written.

After a system reset, the event counter is in state "000".

| Register      | Add Hex | Add Dec |        | bit3 | bit2                      | bit1 | bit0 |