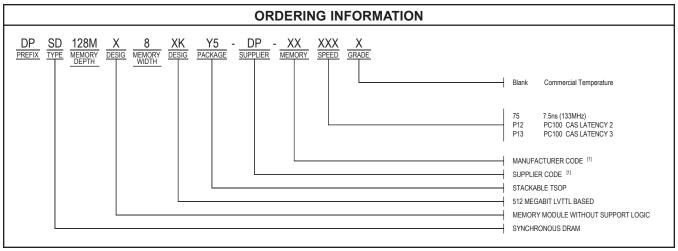

## 1 Gigabit Synchronous DRAM DPSD128MX8XKY5

## **DESCRIPTION:**

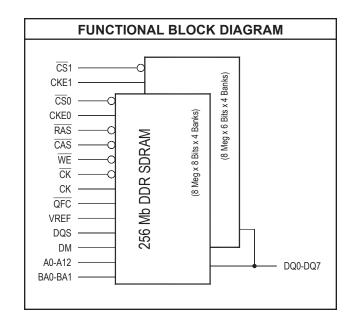

The Memory Stack<sup>M</sup> series is a family of interchangeable memory modules. The 1 Gigabit SDRAM is a member of this family which utilizes the space saving LP-Stack<sup>M</sup> TSOP stacking technology. The modules are constructed with two 64 Meg x 8 SDRAMs.

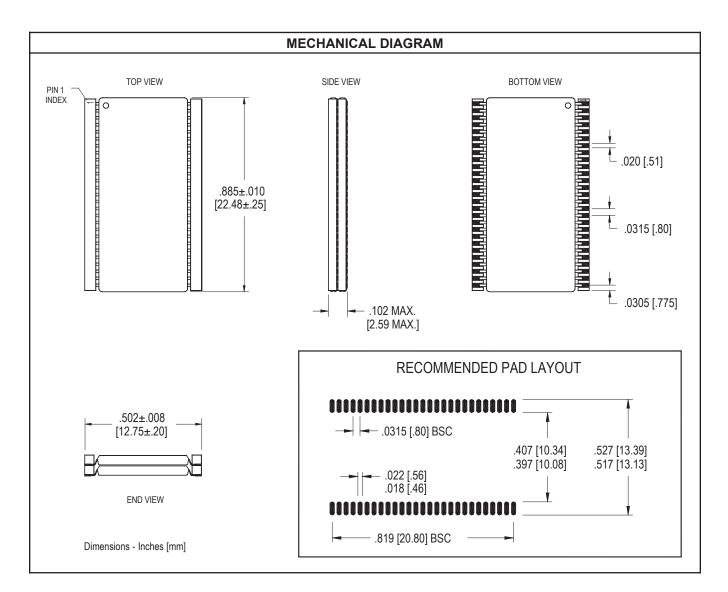

This 1 Gigabit LP-Stack<sup>™</sup> module, DPSD128MX8XKY5, has been designed to fit the same footprint as the 64 Meg x 8 SDRAM TSOP monolithics and 512 Megabit based family of LP-Stack.<sup>™</sup> modules. This allows system upgrade without electrical or mechanical redesign, providing an immediate and low cost memory solution.

## FEATURES:

- Configuration: 128 Meg x 8 bit (2 Banks x 16M x 4 Bit x 8 Banks)

- JEDEC Approved Footprint and Pinout

- · IPC-A-610 Manufacturing Standards

- Assemble per DPAC Application Note 53A001-00

- Package: 54-Pin LP-Stack™

The Following Features are not affected by LP Stack<sup>™</sup> and are provided as reference only. Refer to memory OEM Device specification for details:

- Clock Frequency is determined by OEM memory device used.

- 3.3 Volt DQ Supply

- LVTTL Compatible I/O

- Four Bank Operation

- Programmable Burst Type, Burst Length, and CAS Latency

**PIN NAMES**

- Refresh: 8192 Cycles / 64ms

- · Refresh Types: Auto and Self

| PINOUT DIAGRAM                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCC 1<br>DQ0 2<br>VCCQ 3<br>N.C. 4<br>DQ1 5<br>VSSQ 6<br>N.C. 7<br>DQ2 8<br>VCCQ 9<br>N.C. 10<br>DQ3 111<br>VSSQ 12<br>N.C. 13<br>VCC 14<br>CS1 15<br>WE 16<br>CAS 17<br>RAS 18<br>CS0 19<br>BA1 21<br>A10 22<br>A0 23<br>A1 24<br>A2 25<br>A3 26<br>VCC 27 | 54 VSS   53 DQ7   52 VSSQ   51 N.C.   50 DQ6   49 VCCQ   48 N.C.   47 DQ5   46 VSSQ   45 N.C.   44 DQ4   43 VCCQ   42 N.C.   41 VSS   40 N.C.   39 DQM   38 CLK   37 CKE   36 A11   34 A9   33 A8   32 A7   31 A6   30 A5   29 A4   28 VSS |  |

| A0-A12                            | Row Address:             | RA0-RA12          |

|-----------------------------------|--------------------------|-------------------|

|                                   | Column Address:          | CA0-CA9, A11, A12 |

| BA0, BA1                          | Bank Select Address      |                   |

| DQ0-DQ7                           | Data In/Data Out         |                   |

| CAS                               | Column Address Strobe    |                   |

| RAS                               | Row Address Strobe       |                   |

| WE                                | Data Write Enable        |                   |

| DQM                               | Data Input/Output Mask   |                   |

| CKE                               | Clock Enables            |                   |

| CLK                               | System Clock             |                   |

| $\overline{CS}0 - \overline{CS}1$ | Chip Selects             |                   |

| VDD/VSS                           | Power Supply/Ground      |                   |

| VDDQ/VSSQ                         | Data Output Power/Ground |                   |

| N.C.                              | No Connect               |                   |

30A248-00 REV. B 12/02 This document contains information on a product that is currently released to production at DPAC Technologies DPAC reserves the right to change products or specifications herein without prior notice.

DPAC Technologies Products & Services for the Integration Age 7321 Lincoln Way, Garden Grove, CA 92841 **Tel** 714 898 0007 **Fax** 714 897 1772 www.dpactech.com Nasdaq: DPAC

©2002 DPAC Technologies, all rights reserved. DPAC Technologies<sup>114</sup>, Memory Stack<sup>114</sup>, System Stack<sup>114</sup>, LP-Stack<sup>114</sup>, CS-Stack<sup>114</sup> are trademarks of DPAC Technologies Corp.