## 1 Gigabit CMOS DDR SDRAM DPDD128MX8XSBY5

## **DESCRIPTION:**

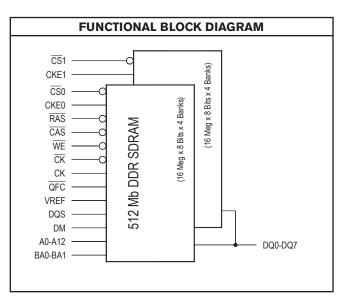

The Memory Stack™ series is a family of interchangeable memory modules. The 1 Gigabit Double Data Rate Synchronous DRAM module is a member of this family which utilizes the space saving LP-Stack™ TSOP stacking technology. The devices are constructed with two 64 Meg x 8 DDR SDRAMs.

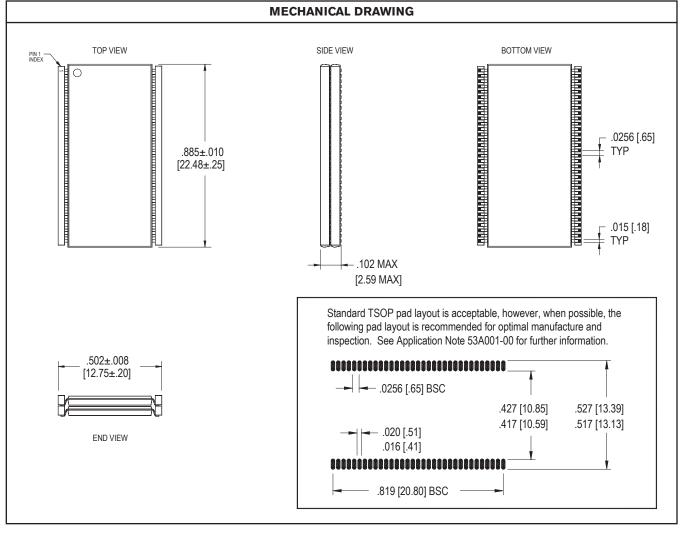

This 512 Megabit based LP-Stack™ module, DPDD128MX8XSBY5, has been designed to fit in the same footprint as the 64 Meg x 8 DDR SDRAM TSOP monolithic. This allows system upgrade without electrical or mechanical redesign, providing an immediate and low cost memory solution.

## **FEATURES:**

- · Configuration:

- 128 Meg x 8 (2 Banks of 16 Meg x 8 Bits x 4 Banks)

- · JEDEC Approved Footprint and Pinout

- · IPC-A-610 Manufacturing Standards

- · Package: 66-Pin Leadless TSOP Stack

The Following Features are not affected by LP-Stack™ and are provided as reference only. Refer to memory OEM device specification for details:

- Clock Frequency is determined by OEM memory device used.

- 2.5 Volt DQ Supply

- JEDEC Standard SSTL\_2 Interface for all Inputs/Outputs

- · Four Bank Operation

- Programmable Burst Length and Read Latency

- · Refresh: 8192 Cycles/64ms

- · Refresh Types: Auto and Self

|            | PIN NAMES                                              |

|------------|--------------------------------------------------------|

| A0-A12     | Row Address: A0-A12<br>Column Address: A0-A9, A11, A12 |

| BA0,BA1    | Bank Select Address                                    |

| A10/AP     | Auto Precharge                                         |

| DQ0-DQ7    | Data In/Data Out                                       |

| CAS        | Column Address Strobe                                  |

| CS0,CS1    | Chip Selects                                           |

| RAS        | Row Address Strobe                                     |

| WE         | Data Write Enable                                      |

| CK, CK     | Differential Clock Inputs                              |

| CKE0, CKE1 | Clock Enables                                          |

| DQS        | Data Strobe                                            |

| DM         | Data Masks                                             |

| QFC        | DQ FET Switch Control                                  |

| VDD        | Power Supply (+2.5V)                                   |

| Vss        | Ground                                                 |

| VDDQ       | DQ Power Supply (+2.5V)                                |

| Vssq       | DQ Ground                                              |

| VREF       | Reference Voltage for inputs                           |

| N.C.       | No Connect                                             |

| NU*        | Not used, Electrical Connect is Present                |

| VDD 1 |

|-------|

| A2 31 |

<sup>\*</sup> This pin is a No Connect for Some Manufacturers.

## NOTE:

- 1. AC Parameters of base memory are unchanged from device manufacturers' specifications.

- 2. DC Parameters may be affected by stacking. Please refer to Application Note 53A004-00 for further information.