# **DENSE-PAC** MICROSYSTEMS

# 64 Megabit FLASH EEPROM

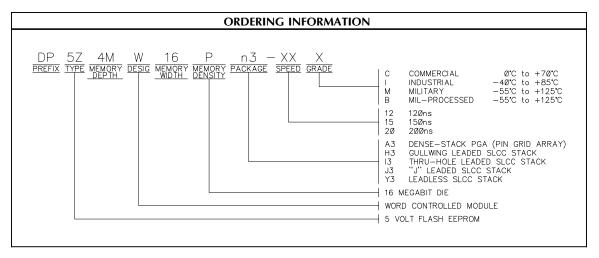

DP5Z4MW16Pn3

## PRELIMINARY

#### **DESCRIPTION:**

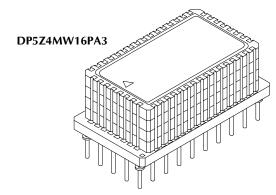

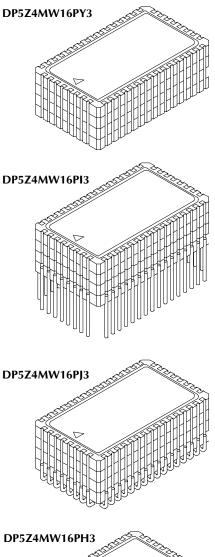

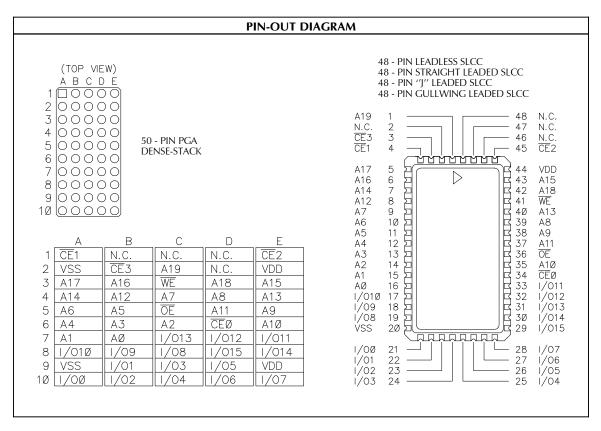

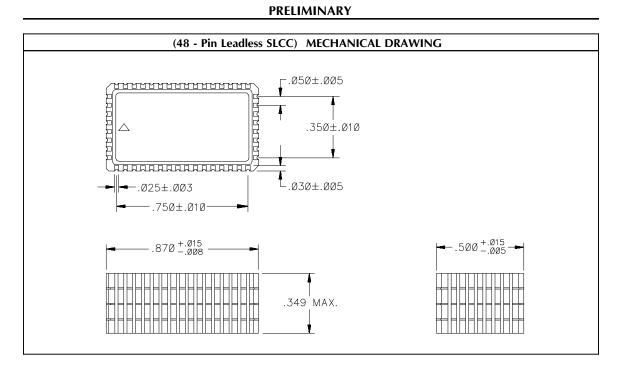

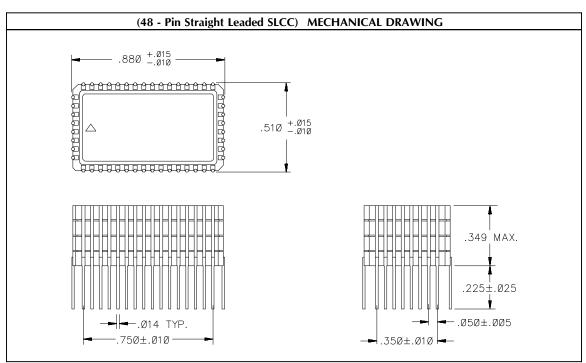

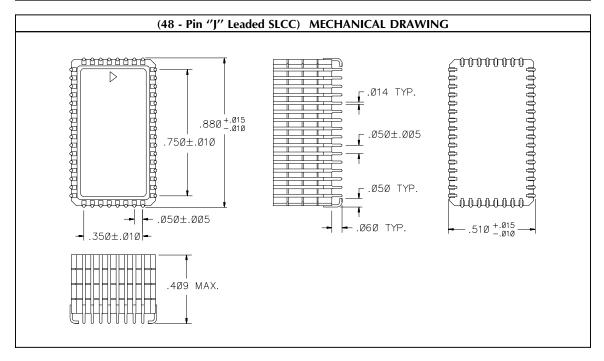

The DP5Z4MW16Pn3 "SLCC" devices are a revolutionary new memory subsystem using Dense-Pac Microsystems' ceramic Stackable Leadless Chip Carriers (SLCC). Available unleaded, straight leaded, "J" leaded, gullwing leaded packages, or mounted on a 50-pin PGA co-fired ceramic substrate. The Device packs 64-Megabits of FLASH EEPROM in an area as small as 0.463 in<sup>2</sup>, while maintaining a total height as low as 0.349 inches.

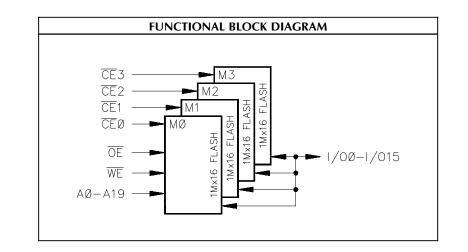

The DP5Z4MW16Pn3 contains four individual 1 Meg x 16 FLASH EEPROM memory devices. Each SLCC is hermetically sealed making the module suitable for commercial, industrial and military applications.

By using SLCCs, the "Stack" family of modules offer a higher board density of memory than available with conventional through-hole, surface mount or hybrid techniques.

### FEATURES:

- Organization: 4Meg x 16

- Fast Access Times: 120, 150, 200ns (max.)

- Single 5.0 Volt

- High-Density Symmetrically Blocked Architecture

Sixteen 64 K Word Blocks Per Device

- Extended Cycling Capability

100K Write/Erase Cycles

- Automated Erase and Program Cycles

- Command User Interface

- Status Register

- SRAM-Compatible Write Interface

- Hardware Data Protection Feature

- Erase / Write Lockout during Power Transitions

- Packages Available:

DP5Z4MW16PY3 48 - Pi DP5Z4MW16PI3 48 - Pi DP5Z4MW16PI3 48 - Pi DP5Z4MW16PH3 48 - Pi DP5Z4MW16PJ3 48 - Pi DP5Z4MW16PA3 50 - Pi

48 - Pin SLCC

48 - Pin Straight Leaded SLCC

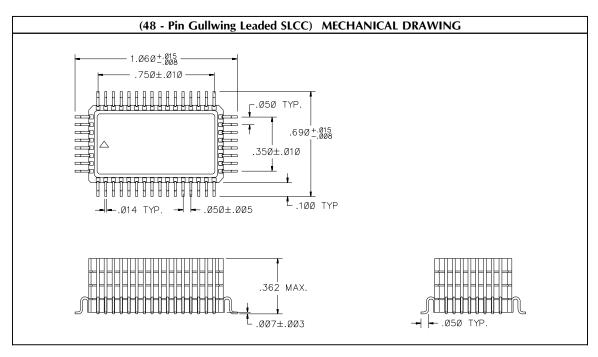

48 - Pin Gullwing Leaded SLCC

48 - Pin "J" Leaded SLCC

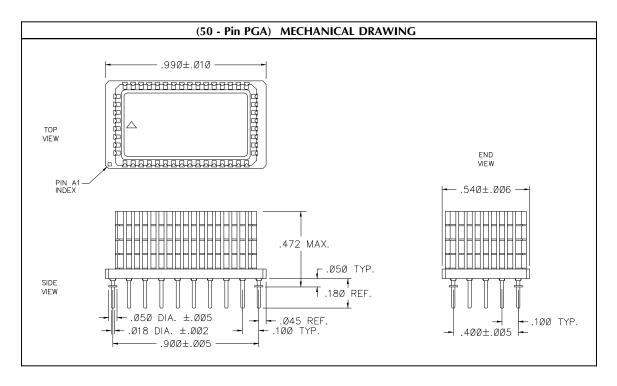

50 - Pin PGA Dense-SLCC

This document contains information on a product presently under development at Dense-Pac Microsystems, Inc. Dense-Pac reserves the right to change products or specifications herein without prior notice.

Dense-Pac Microsystems, Inc.

### Dense-Pac Microsystems, Inc.

# DP5Z4MW16Pn3

### PRELIMINARY

|                 | PIN NAMES                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 - A19        | ADDRESS INPUTS: for memory address. Addresses are internally latched during a write cycle.                                                                                                                                                                                                                                                                                                                                                         |

| I/O0 - I/O15    | DATA INPUT/OUTPUT: Input data and command during Command Data Interface Register (CIR) write cycles. Outputs array, status and identifier data in the appropriate read mode. Floated when the chip is de-selected or the outputs are disabled.                                                                                                                                                                                                     |

| CE              | CHIP ENABLE INPUT: Activate the device's control logic, Input buffers, decoders and sense amplifiers. With $\overline{CE}$ high, the device is de-selected and power consumption reduces to Standby level upon completion of a ny current program or erase operation. $\overline{CE}$ must be low to select the device. Device selection occurs with the falling edge of $\overline{CE}$ . The rising edge of $\overline{CE}$ disables the device. |

| WE              | WRITE ENABLE: Controls writes to the Command Interface Register (CIR). WE is active low.                                                                                                                                                                                                                                                                                                                                                           |

| OE              | OUTPUT ENABLE: Gates the device's data through the output buffers during a read cycle. OE is active low.                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | DEVICE POWER SUPPLY (+5.0 Volts ±10%)                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss             | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| N.C.            | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### **BUS OPERATION**

Flash memory reads, erases and writes in-system via the local CPU. All bus cycles to or from the fl ash memory conform to standard microprocessor bus cycles.

|                                         | Table 1: Bus Operation |     |     |     |     |     |            |  |  |

|-----------------------------------------|------------------------|-----|-----|-----|-----|-----|------------|--|--|

| Mode                                    | CE                     | OE  | WE  | A0  | A1  | A9  | I/O0-I/O15 |  |  |

| Read <sup>1</sup>                       | VIL                    | VIL | VIH | Х   | Х   | Х   | Dout       |  |  |

| Output Disable <sup>1</sup>             | VIL                    | VIH | VIH | Х   | Х   | Х   | HIGH-Z     |  |  |

| Standby <sup>1</sup>                    | VIH                    | Х   | Х   | Х   | Х   | Х   | HIGH-Z     |  |  |

| Deep Power-Down <sup>1</sup>            | Х                      | Х   | Х   | Х   | Х   | Х   | HIGH-Z     |  |  |

| Manufacturer Identifier <sup>1, 3</sup> | VIL                    | VIL | VIH | VIL | VIL | VID | 00C2H      |  |  |

| Device Identifier <sup>3</sup>          | VIL                    | VIL | Vih | Vih | VIL | Vid | 00F1H      |  |  |

| Write <sup>1, 2</sup>                   | VIL                    | Vih | VIL | Х   | Х   | Х   | Din        |  |  |

#### NOTES:

1. X can be  $V_{\mathsf{IL}}$  or  $V_{\mathsf{IH}}$  for address or control pins.

2. Command for deferent Erase operations, Data program operations or Selector Protect operations can only be successfully completed through proper command sequence.

3.  $V_{ID} = 11.5V - 12.5V.$

## WRITE OPERATION

Commands are written to the COMMAND INTERFACE REGISTER (CIR) using standard microprocessor write timing. The CIR serves as the interface between the microprocessor and the internal chip operation. The CIR can decipher Read Array, Read Silicon ID, Erase and Program command. In the event of a read command, the CIR simply points the read path at either the array or the Silicon ID, depending on the specific read command given. for a program or erase cycle, the CIR informs the write state machine that a program or erase has been requested. During a program cycle, the write state machine control the program sequences and the CIR will only respond to status reads. During a sector/chip erase cycle, the CIR will respond to status reads and erase suspend. After the writhe state machine has completed its task, it will allow the CIR to respond to its full command set. The CIR stays at read status register mode until the microprocessor issues another valid command sequence.

Device operations are selected by writing commands into the CIR. Table 3 below defines 16 Megabit Flash family command.

### PRELIMINARY

# **DEVICE OPERATION**

## SILICON ID READ

The Silicon ID Read mode allows the reading out of a binary code from the device and will identify its manufacturer and type. this is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional over the entire temperature range of the device.

To activate the mode, the programming equipment must force V ID (11.5V ~ 12.5V) on address pin A9. Two identifier bytes may then be sequenced from the device outputs by toggling address A0 from V<sub>IL</sub> to V<sub>IH</sub>. All addresses are don't cares except A0 and A1.

The manufacturer and device codes may also be read via the command register, for instance when the device is erased or programmed in a system without access to high voltage on the A9 pin. The command sequence is illustrated in Table 2.

To terminate the operation, it is necessary to write the read/reset command sequence into the CIR.

#### **READ RESET COMMAND**

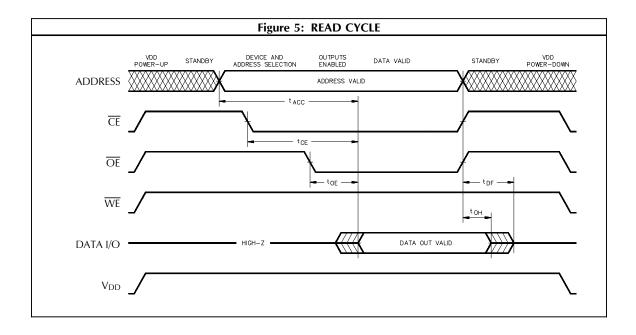

The read or reset operation is initiated by writing the read/reset command sequence into the command register. Microprocessor read cycles retrieve array data from the memory. The device remains enabled fro reads until the CIR contents are altered by a valid command sequence.

The device will automatically power-up in the read/reset state. In this case, a command sequence is not required to read data. This default value ensures that no spurious alteration of the memory content occurs during the power transition. Refer to the AC Read Characteristics and Waveforms for the specific timing parameters.

|                       |               |                    |      | Table 2           | : Con | nmand            | Defin | ition   |                       |                  |      |                  |      |

|-----------------------|---------------|--------------------|------|-------------------|-------|------------------|-------|---------|-----------------------|------------------|------|------------------|------|

| Command<br>Sequence   | Bus<br>Cycles | First I<br>Write ( |      | Second<br>Write ( |       | Third<br>Write ( |       | Read    | h Bus<br>Write<br>cle | Fifth<br>Write ( |      | Sixth<br>Write ( |      |

| •                     | Req'd         | Address            | Data | Address           | Data  | Address          | Data  | Address | Data                  | Address          | Data | Address          | Data |

| Read/Reset            | 4             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | FOH   | RA      | RD                    | -                | -    | -                | -    |

| Silicon ID Read       | 4             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | 90H   | 00H/01H | C2H/F1H               | -                | -    | -                | -    |

| Page/Byte Program     | 4             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | A0H   | PA      | PD                    | -                | -    | -                | -    |

| Chip Erase            | 6             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | 80H   | 5555H   | AAH                   | 2AAAH            | 55H  | 5555H            | 10H  |

| Sector Erase          | 6             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | 80H   | 5555H   | AAH                   | 2AAAH            | 55H  | SA               | 30H  |

| Erase Suspend         | 3             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | BOH   | -       | -                     | -                | -    | -                | -    |

| Erase Resume          | 3             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | D0H   | -       | -                     | -                | -    | -                | -    |

| Read Status Register  | 4             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | 70H   | Х       | SRD                   | -                | -    | -                | -    |

| Clear Status Register | 3             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | 50H   | -       | -                     | -                | -    | -                | -    |

| Sleep                 | 3             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | C0H   | -       | -                     | -                | -    | -                | -    |

| Abort                 | 3             | 5555H              | AAH  | 2AAAH             | 55H   | 5555H            | EOH   | -       | -                     | -                | -    | -                | -    |

#### NOTES:

Address bit A15 - A19 = X = Don't Care for all address commands except for Programming Address (PA) and Sector Address (SA). 5555H and 2AAAH address command codes stand for Hex number starting from A0 to A14.

Bus operations are defined in Table 2.

RA = Address of the memory location to be read. PA = Address of the memory location to be read. PA = Address of the sector to be programmed. Addresses are latched on the falling edge of the WE pulse. SA = Address of the sector to be erased. The combination of A16 - A19 will be uniquely select any sector.

RD = Data read from location RA during read operation. PD = Data to be programmed at location PA. Data is latched on the rising edge of WE. SRD = Data read from Status Register.

Table 3: Silicon ID Code Code Type A19 A18 A17 A16 A1 A0 I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0 (HEX) Manufacturer's 0 0 0 0 0 Х Х Х Х  $V_{IL}$ 00C2H 1 1 1  $V_{IL}$ Code Device Code Х Х Х  $V_{IL}$ 00FIH 0 0 0 Х  $V_{\text{IH}}$ 1 1 1 1 1

## PRELIMINARY

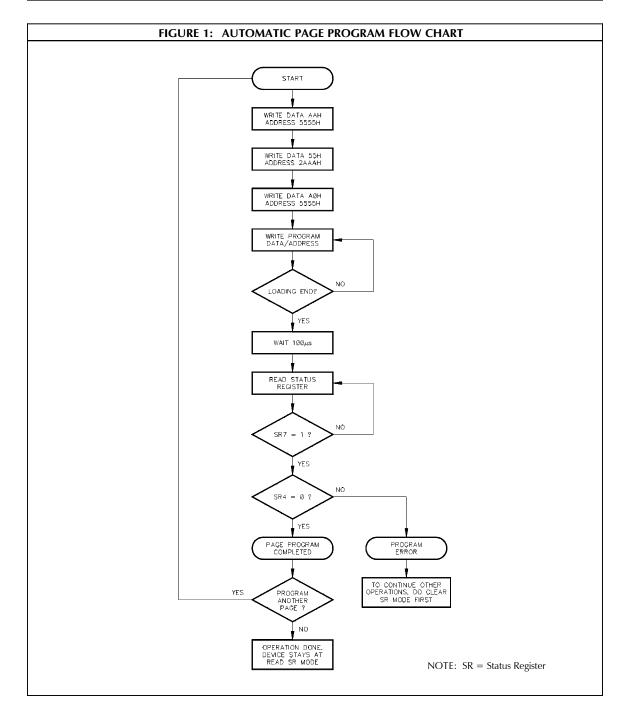

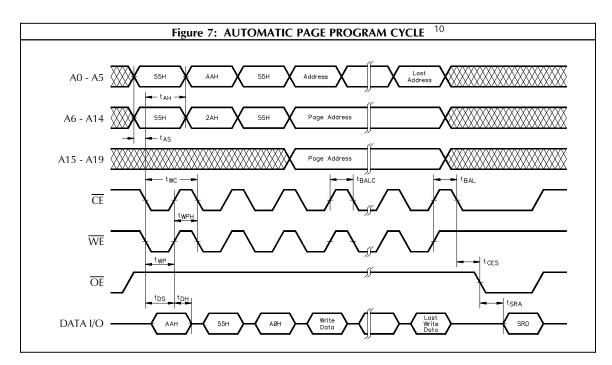

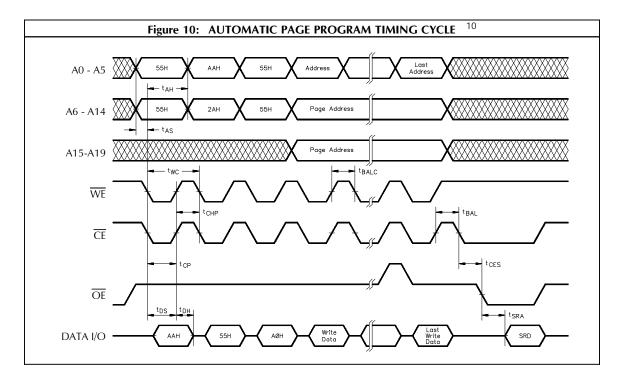

#### PAGE PROGRAM

To initiate Page Program mode, a three-cycle command sequence is required. There are two "unlock" write cycles. These are followed by writing the page program command - AOH.

After three-cycle command sequence is given, a word load is performed by applying a low pulse on the  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$  input with  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  low (respectively) and  $\overline{\text{OE}}$  high. The address is latched on the falling edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs last. The data is latched by the first rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ . Maximum of 64 words of data may be loaded into each page by the same procedures as outlined in the page program section below.

#### WORD LOAD

Word loads are used to enter the 64 words of a page to be programmed. A word load is performed by applying a low pulse on the  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$  input  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  low respectively) and  $\overline{\text{OE}}$  high. The address is latched on the falling edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs last. The data is latched by the first rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ .

#### PROGRAM

Any page to be programmed should have the page in the erase state first, i.e. performing sector erase is suggested before page programming can be performed.

The device is programmed on a page basis. If a word of data within a page is to be changed, data for the entire page can be loaded into the device. Any word that is not loaded during the programming of its page will be still in the erase state (i.e. FFH). Once the words of a page are loaded into the device, they are simultaneously programmed during the internal programming period. After the first data word has been loaded into the device, successive words are entered in the same manner. Each new word to be programmed must have its high to low transition on  $\overline{WE}$  (or  $\overline{CE}$ ) within 30µs of the low to high transition of  $\overline{WE}$  (or  $\overline{CE}$ ) of the preceding word. A6 to A19 specify the page address, i.e. the device is page-aligned on 64 words boundary The page address must be valid during each high to low transition of WE or CE. A0 to A5 specify the word address within the page. The word may be loaded in any order; sequential loading is not required. If a high to low transition of  $\overline{CE}$  or  $\overline{WE}$  is not detected within 100 µs of the last low to high transition, the load period will end and the internal programming period will start. The auto page program terminates when status on I/O7 is "1" at which time the device stays at read status register mode until the CIR contents are altered by a valid command sequence. (Refer to Table 2 & 5 and Figure 1, 6 & 7)

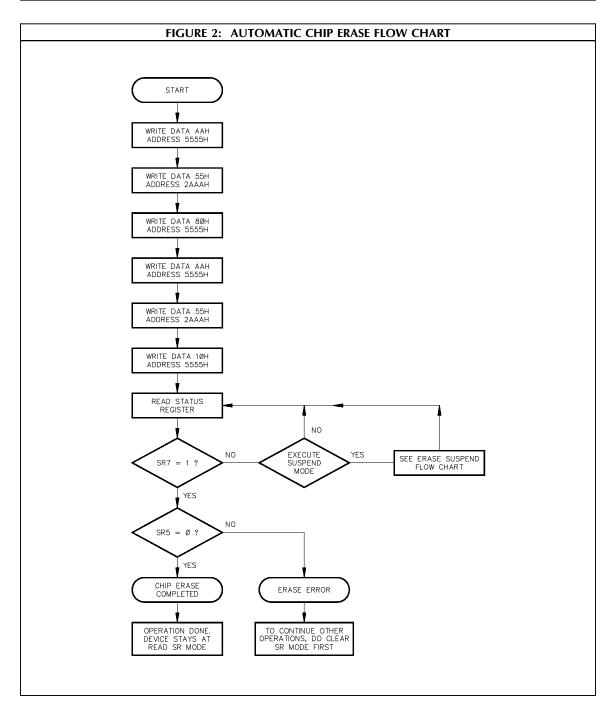

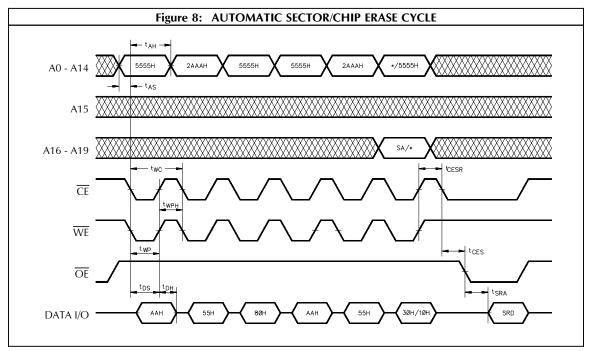

#### CHIP ERASE

Chip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command - 80H. Two more "unlock" write cycles are then followed by the chip erase command - 10H.

Chip erase does not require the user to program the device prior to erase.

The automatic erase begins on the rising edge of the last  $\overline{\text{WE}}$  pulse in the command sequence and terminates when the status on I/O7 is "1" at which time the device stays at read status register mode until the CIR contents are altered by a valid command sequence. (Refer to Tables 2 & 5 and Figures 2, 6 & 8)

|      | Table 4: Sector Address* |     |     |     |                        |  |  |

|------|--------------------------|-----|-----|-----|------------------------|--|--|

|      | A19                      | A18 | A17 | A16 | Address Range [A0-A15] |  |  |

| SA0  | 0                        | 0   | 0   | 0   | 00000H—0FFFFH          |  |  |

| SA1  | 0                        | 0   | 0   | 1   | 10000H—1FFFFH          |  |  |

| SA2  | 0                        | 0   | 1   | 0   | 20000H—2FFFFH          |  |  |

| SA3  | 0                        | 0   | 1   | 1   | 30000H—3FFFFH          |  |  |

| SA4  | 0                        | 1   | 0   | 0   | 40000H—4FFFFH          |  |  |

|      |                          |     |     |     |                        |  |  |

| SA15 | 1                        | 1   | 1   | 1   | F0000H—FFFFFH          |  |  |

\* Per 1 Meg x 16 device.

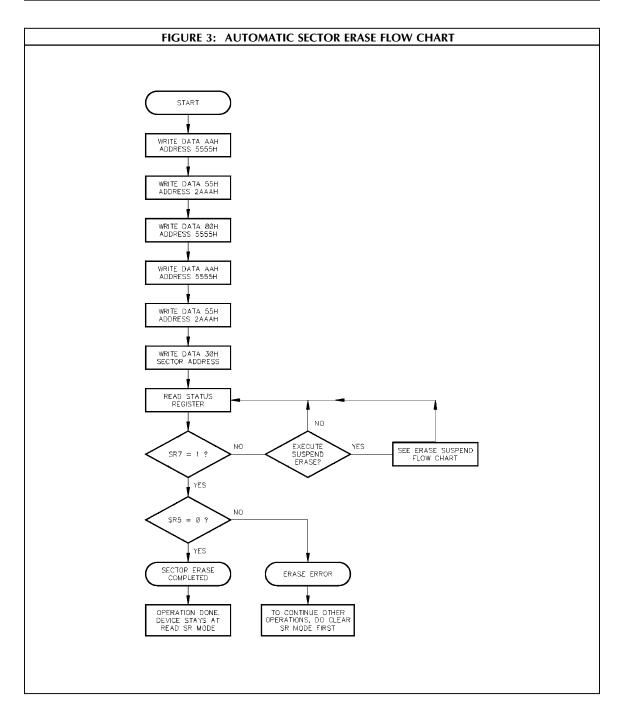

#### SECTOR ERASE

Sector erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the set-up command - 80H. Two more "unlock" write cycles are then followed by the sector erase command - 30H. The sector address is latched on the falling edge of  $\overrightarrow{WE}$ , while the command (data) is latched on the rising edge of  $\overrightarrow{WE}$ .

Sector erase does not require the user to program the device prior to erase. The system is not required to provide any controls or timings during these operations.

The automatic sector erase begins on the rising edge of the last  $\overline{\text{WE}}$  pulse in the command sequence and terminates when the status on I/O7 is "1" at which time the device stays at read status register mode. The device remains enabled for read status register mode until the CIR contents are altered by a valid command sequence. (Refer to Tables 2, & 5 and Figures 3, 4, 6 & 8)

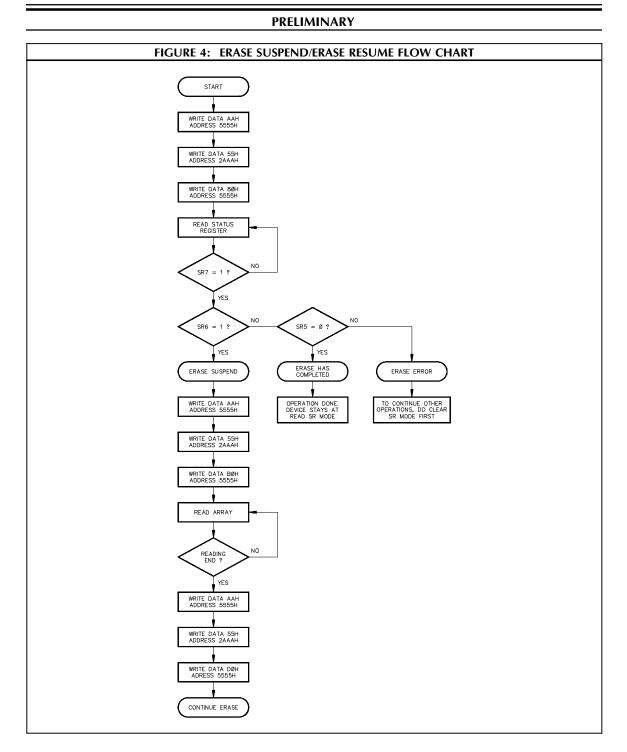

#### **ERASE SUSPEND**

This command only has meaning while the WSM is executing SECTOR or CHIP erase operations, and therefore will only be responded to during SECTOR or CHIP erase operation. After this command has been executed, the CIR will initiate the WSM to suspend erase operations, and then return to Read Status Register mode. The WSM will set the I/O6 bit to a "1". Once the WSM has reached the Suspend state, the WSM will set I/O7 bit to a "1". At this time, WSM allows CIR to respond to the Read Array, Read Status Register, Abort and Erase Resume commands only. In this mode, the CIR will not respond to any other commands. the WSM will continue to run, idling in the SUSPEND state, regardless of the state of all input control pins.

#### **ERASE RESUME**

This command will cause the CIR to clear the suspend state and set the I/O6 to a "0", but only in an Erase Suspend command was previously used. Erase Resume will not have any effect in all other conditions.

#### **READ STATUS REGISTER COMMAND**

The module contains a Status Register which may be read to determine when a program or erase operation is complete, and whether that operation completed successfully. The status register may be read at any time by writing the Read Status command to the CIR. After writing this command, all subsequent read operations output data from the status register, until another valid command is written to the CIR. A Read Array command must be written to the CIR to return to the Read Array mode.

Dense-Pac Microsystems, Inc.

### PRELIMINARY

The status register bits are output on I/O2 - I/O7 (Table 5), I/O0-I/O1 and I/O8-I/O15 is set to 0H.

It should be noted that the status register are latched on the falling edge of  $\overline{OE}$  or  $\overline{CE}$  whichever occurs last in the read cycle. This prevents possible bus errors which might occur if the contents of the status register change while reading the status register. CE or OE must be toggled with each subsequent status read, or the completion of a program or erase operation will not be evident.

The Status Register is the interface between the microprocessor and the Write State Machine (WSM). When the WSM is active, this register will indicate the status of the WSM, and will also hold the bits indicating whether or not the WSM was successful in performing the desired operation. The WSM sets status bits four through seven and clears bits six and seven, but cannot clear status bits four and five. If Erase fail or Program fail status bit is detected, the Status Register is not cleared until the Clear Status Register command is written. The device automatically outputs Status Register data when read after Chip Erase, Sector Erase, Page Program or Read Status Command write cycle. the default state of the Status Register after power-up and return from deep power-down mode is (I/O7, I/O6, I/O5, I/O4) = 1000B. I/O3 0 or 1 depends on sector-protect status, can not be changed by Clear Status Register Command or Write State Machine. I/O2 : 0 or 1 depends on Sleep status, During Sleep mode or Abort mode I/O2 is set to "1"; I/O2 is reset to "0" by Read Array command.

#### **CLEAR STATUS REGISTER**

The Erase fail status bit (I/O5) and Program fail status bit (I/O4) are set by the write state machine, and can only be reset by the system software. These bits can indicate various failure conditions (see

Table 5). By allowing the system software to control the resetting of these bits, several operations may be performed (such as cumulatively programming several pages or erasing multiple blocks in sequence). The Status register may then be read to determine if an error occurred during that programming or erasing series. This adds flexibility to the way the device may be programmed or erased. Additionally, once the program (erase) fail bit happens, the program (erase) operation can not be performed further. The program (erase) fail bit must be reset by system software before further page program or sector (chip) erase are attempted. To clear the status register, the Clear Status Register command is written to the CIR. Then, any other command may be issued to the CIR. Note again that before a read cycle can be initiated, a Read command must be written to the CIR to specify whether the read data is to come from the Array, Status Register or Silicon ID.

#### SLEEP MODE

The device features two software controlled low-power modes: Sleep and Abort modes. Sleep mode is allowable during any current operations except that once Suspend command is issued, Sleep command is ignored. Abort mode is executed only during page Programming and Chip/Sector Erase mode.

To activate Sleep mode, a three-bus cycle operation is required. COH command (refer to Table 2) puts the device in the Sleep mode. Once in the Sleep mode and CMOS input level applied, the power of the device is reduced to deep power-down current levels. The only threshold condition, input leakage, and output leakage.

The Sleep command allows the device to COMPLETE current operations before going into Sleep mode. Once current operation is done, device stays at read status register mode. The status

|                | Table 5: Status Register              |      |      |                         |   |     |          |  |  |  |

|----------------|---------------------------------------|------|------|-------------------------|---|-----|----------|--|--|--|

|                | STATUS                                | I/O7 | I/O6 | I/O6 I/O5 I/O4 I/O3 I/O |   |     |          |  |  |  |

|                | PROGRAM <sup>a, b, f</sup>            | 0    | 0    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

| IN PROGRESS    | ERASE <sup>a, c, f</sup>              | 0    | 0    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

| IN I KOGKESS   | SUSPEND (NOT COMPLETE) a, d, f        | 0    | 1    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

|                | SUSPEND (COMPLETE) <sup>a, d, f</sup> | 1    | 1    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

|                | PROGRAM <sup>a, b, f</sup>            | 1    | 0    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

| COMPLETE       | ERASE <sup>a, c, f</sup>              | 1    | 0    | 0                       | 0 | 0/1 | 0/1      |  |  |  |

| EALL           | PROGRAM <sup>a, e, f</sup>            | 1    | 0    | 0                       | 1 | 0/1 | 0/1      |  |  |  |

| FAIL           | ERASE <sup>a, e, f</sup>              | 1    | 0    | 1                       | 0 | 0/1 | 0/1      |  |  |  |

| AFTER CLEARING | STATUS REGISTER <sup>f</sup>          | 1    | 0    | 0                       | 0 | 0/1 | Note 'g' |  |  |  |

#### NOTES:

- a. I/O7: Write State Machine Status

- 1 = Ready, 0 = Busy I/O6: Erase Suspend Status 1 =Suspend, 0 = No Suspend

- I/O5: Erase Fail Status 1 = Fail in Erase, 0 = Successful Erase I/O4: Program Fail Status

- 1 = Fail in Program, 0 = Successful Program I/O3: Sector-Protect Status (Not Used)

- I/O2: Sleep Status

1 = Device in Sleep Status

I/O1 I/O0 = Reserved for further enhancements.

- These bits are reserved for future use; mask them out when polling the Status Register.

- b. Program Status is for the status during Page Programming or Sector Unprotect mode.

- c. Erase Status is for the status during Sector/Chip Erase or Sector Protection mode.

- d. Suspend Status is for both Sector and Chip Erase mode.

- e. Fail Status bit (I/O4 or I/O5) is provided during Page Program or Sector/Chip Erase modes respectively.

- f. I/O2 = 0 or 1 depends on whether device is in the Sleep mode or not.

- g. Once in the Sleep mode, I/O2 is set to "1", and is reset by read array command only

### PRELIMINARY

registers are not reset during sleep command. Program or Erase fail bit may have been set if during program/erase mode the device retry exceeds maximum count.

During Sleep mode, the status registers, Silicon ID codes remain valid and can still be read. The device Sleep Status bit - I/O2 will indicate that the device in the sleep mode.

Write and Read Array command wakes up the device out of Sleep mode,  $\ I/O2$  is reset to "0" and device returns to standby current level.

#### ABORT MODE

To activate Abort mode, a three-bus cycle operation is required. The E0H command (refer to Table 3) only stops page program or Sector/Chip erase operations currently in progress and puts the device in Sleep mode. But unlike the Sleep command, the program or erase operation will not be completed. Since the data in some page/sectors is no longer valid due to an incomplete program or erase operation, the program fail (I/O4) or erase fail (I/O5) bit will be set.

After the abort command is executed and with CMOS input levels applied, the device current is reduced to the same level as in deep power-down or sleep modes. Device stays at read register mode.

During Abort mode, the status register, Silicon ID codes remain valid and can still be read. The device Sleep Status bit - I/O2 will indicate that the device in the sleep mode.

### DATA PROTECTION

The device is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exit during power transitions. During power-up the device automatically resets the internal state machine in the read array mode. Also, with its control register architecture, alterations of the memory contents only occurs after successful completion of specific multi-bus cycles command sequences.

the device also incorporates several features to prevent inadvertent write cycles resulting from  $V_{\rm DD}$  power-up and power-down transitions or system noise.

#### LOW VDD WRITE INHIBIT

To avoid initiation of a write cycle during V <sub>DD</sub> power-up and power-down, a write cycle is locked out for V <sub>DD</sub> less than V<sub>OKL</sub> (=3.2V, typically 3.5V). If V <sub>DD</sub> < V<sub>LKO</sub>, the command register is disabled and all internal program/erase circuits are disabled. Under this condition the device will reset to the read mode. Subsequent writes will be ignored until the V <sub>DD</sub> level is greater than V<sub>LKO</sub>. It is logically correct to prevent unintentional write when V<sub>DD</sub> is above V<sub>LKO</sub>.

#### WRITE PULSE "GLITCH" PROTECTION

Noise pulses of less than 10ns (typical) on  $\overline{CE}$  or  $\overline{WE}$  will not initiate a write cycle.

#### LOGICAL INHIBIT

Writing is inhibited by holding any one of  $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IH}$  or  $\overline{WE} = V_{IH}$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be a logical zero while  $\overline{OE}$  is a logical one.

| ERA                    | ERASE AND PROGRAMMING PERFORMANCE |        |      |        |  |  |  |  |  |

|------------------------|-----------------------------------|--------|------|--------|--|--|--|--|--|

| PARAMETER              |                                   | LIMITS |      |        |  |  |  |  |  |

| TARAMETER              | MIN.                              | TYP.   | MAX. | UNITS  |  |  |  |  |  |

| Chip/Sector Erase Time |                                   | 150    | 2000 | ms     |  |  |  |  |  |

| Page Programming Time  |                                   | 3      | 60   | ms     |  |  |  |  |  |

| Chip Program Time *    |                                   | 48     | 150  | sec    |  |  |  |  |  |

| Erase/Program Cycles   | 10,000                            |        |      | Cycles |  |  |  |  |  |

| Byte Program Time      |                                   | 24     |      | μs     |  |  |  |  |  |

\* Per 1Mx16 device. Module program time is 4x.

| LATCH UP CHARACTI                                                                             | RISTICS |                      |       |

|-----------------------------------------------------------------------------------------------|---------|----------------------|-------|

| PARAMETER                                                                                     | MIN.    | AMX.                 | UNITS |

| Input Voltage with Respect to V ss on all pins except I/O pins                                | -1.0    | 13.5                 | V     |

| Input Voltage with Respect to V ss on all I/O pins                                            | -1.0    | V <sub>DD</sub> +1.0 | V     |

| Current                                                                                       | -100    | +100                 | mA    |

| Includes all pins except V <sub>DD</sub> . Test conditions: $V_{DD} = 5.0V$ , one pin at a ti | me      |                      |       |

## Dense-Pac Microsystems, Inc.

| R               | RECOMMENDED OPERATING RANGE <sup>1</sup> |       |      |               |      |      |  |  |  |  |  |

|-----------------|------------------------------------------|-------|------|---------------|------|------|--|--|--|--|--|

| Symbol          | Characteris                              | tic   | Min. | Тур.          | Max. | Unit |  |  |  |  |  |

| V <sub>DD</sub> | Supply Voltage                           | 4.5   | 5.0  | 5.5           | V    |      |  |  |  |  |  |

| VIL             | Input LOW Volt                           | -0.52 |      | 0.8           | V    |      |  |  |  |  |  |

| VIH             | Input HIGH Vol                           | 2.0   |      | $V_{DD}$ +0.5 | V    |      |  |  |  |  |  |

|                 |                                          | С     | 0    | +25           | +70  |      |  |  |  |  |  |

| TA              | Operating<br>Temperature                 | I     | -40  | +25           | +85  | °C   |  |  |  |  |  |

|                 | remperature                              | M/B   |      |               | +125 |      |  |  |  |  |  |

| VID             | A9 I.D. Input/O                          | utput | 11.5 |               | 12.5 | V    |  |  |  |  |  |

|                   | ABSOLUTE MAXIMUM RATINGS <sup>5</sup> |                           |      |  |  |  |  |  |  |

|-------------------|---------------------------------------|---------------------------|------|--|--|--|--|--|--|

| Symbol            | Parameter                             | Value                     | Unit |  |  |  |  |  |  |

| T <sub>STC</sub>  | Storage Temperature                   | -65 to +125               | °C   |  |  |  |  |  |  |

| T <sub>BIAS</sub> | Temperature Under Bias                | -55 to +125               | °C   |  |  |  |  |  |  |

| T <sub>OP</sub>   | Operating Temperature                 | -55 to +125               | °C   |  |  |  |  |  |  |

| lout              | Output Short<br>Circuit Current       | 100 4                     | mA   |  |  |  |  |  |  |

| VI/O              | Input/Output Voltage <sup>1</sup>     | -0.5 to +7.0 <sup>2</sup> | V    |  |  |  |  |  |  |

| V <sub>DD</sub>   | Supply Voltage <sup>1</sup>           | -0.5 to +7.0 $^{3}$       | V    |  |  |  |  |  |  |

| CA               | PACITANCE <sup>5</sup> : T <sub>A</sub> | NCE <sup>5</sup> : $T_A = 25^{\circ}C$ , F = 1.0MHz |      |                 |  |  |  |

|------------------|-----------------------------------------|-----------------------------------------------------|------|-----------------|--|--|--|

| Symbol           | Parameter                               | Max.                                                | Unit | Condition       |  |  |  |

| C <sub>ADR</sub> | Address Input                           | 45                                                  |      |                 |  |  |  |

| C <sub>CE</sub>  | Chip Enable                             | 20                                                  |      |                 |  |  |  |

| C <sub>WE</sub>  | Write Enable                            | 45                                                  | рF   | $V_{IN}^2 = 0V$ |  |  |  |

| COE              | Output Enable                           | 45                                                  |      |                 |  |  |  |

| C <sub>I/O</sub> | Data Input/Output                       | 60                                                  |      |                 |  |  |  |

| DC OUTPUT CHARACTERISTICS |                 |                          |      |      |      |  |  |

|---------------------------|-----------------|--------------------------|------|------|------|--|--|

| Symbol                    | Parameter       | Condition                | Min. | Max. | Unit |  |  |

| V <sub>OH</sub>           | HIGH<br>Voltage | I <sub>OH</sub> = -400μA | 2.4  |      | V    |  |  |

| VOL                       | LOW Voltage     | I <sub>OL</sub> =2.1mA   |      | 0.45 | V    |  |  |

|                  | DC                                                       | <b>OPERATING CHARACTERISTICS:</b> Over                                                                                                      | operating | ranges |                      |      |

|------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|----------------------|------|

| Symbol           | Characteristics                                          | Test Conditions                                                                                                                             |           | Limits |                      | Unit |

| Symbol           | Characteristics                                          | Test Conditions                                                                                                                             | Min.      | Тур.   | Max.                 | Unit |

| IIL              | Input Load Current <sup>6</sup>                          | $V_{DD} = V_{DD}$ max., $V_{IN} = V_{DD}$ or $V_{SS}$                                                                                       | -40       |        | +40                  | μA   |

| I <sub>OL</sub>  | Output Leakage<br>Current <sup>6</sup>                   | $V_{DD} = V_{DD}$ max., $V_{IN} = V_{DD}$ or $V_{SS}$                                                                                       | -40       |        | +40                  | μA   |

| I <sub>SB1</sub> | V <sub>DD</sub> Standby Current (CMOS) <sup>6</sup>      | $V_{DD} = V_{DD} \text{ max.}, \overline{CE} = V_{DD} \pm 0.2 V$                                                                            |           | 200    | 800                  | μA   |

| I <sub>SB2</sub> | V <sub>DD</sub> Standby Current (TTL) <sup>6</sup>       | $V_{DD} = V_{DD} \text{ max.}, \overline{CE} = V_{IH}$                                                                                      |           | 8      | 24                   | mA   |

| I <sub>CC1</sub> | V <sub>DD</sub> Read Current                             | $V_{DD} = V_{DD} \text{ max., } \overline{CE} = V_{IL},$<br>Inputs = V <sub>IL</sub> or V <sub>IH</sub> , f = 10MHz, I <sub>OUT</sub> = 0mA |           | 55     | 100                  | mA   |

| I <sub>CC2</sub> | V <sub>DD</sub> Read Current <sup>6</sup>                | $V_{DD} = V_{DD} max., \overline{CE} = V_{IL},$<br>Inputs = V <sub>IL</sub> or V <sub>IH</sub> , f = 5MHz, I <sub>OUT</sub> = 0mA           |           | 35     | 60                   | mA   |

| I <sub>CC3</sub> | V <sub>DD</sub> Erase Suspend<br>Current <sup>6, 8</sup> | Block Erase in Suspend, $\overline{CE} = V_{IH}$                                                                                            |           | 10     | 35                   | mA   |

| I <sub>CC4</sub> | V <sub>DD</sub> Program<br>Current <sup>6</sup>          | Program in Progress                                                                                                                         |           | 35     | 80                   | mA   |

| I <sub>CC5</sub> | V <sub>DD</sub> Erase Current <sup>6</sup>               | Erase in Progress                                                                                                                           |           | 35     | 80                   | mA   |

| V <sub>IL</sub>  | Input Low Voltage <sup>9</sup>                           |                                                                                                                                             | -3.0      |        | 0.8                  | V    |

| VIH              | Input High Voltage                                       |                                                                                                                                             | 2.4       |        | V <sub>DD</sub> +0.3 | V    |

| V <sub>OL</sub>  | Output Low Voltage                                       | $I_{OL} = 2.1 \text{mA}$                                                                                                                    |           |        | 0.45                 | V    |

| VOH              | Output High Voltage                                      | $I_{OH} = -400 \text{mA}$                                                                                                                   | 2.4       |        |                      | V    |

Dense-Pac Microsystems, Inc.

Dense-Pac Microsystems, Inc.

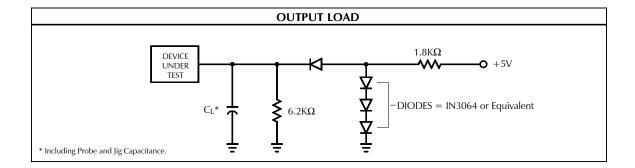

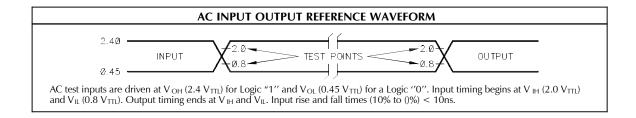

| AC TEST CONDITIONS                          |               |  |  |  |  |  |

|---------------------------------------------|---------------|--|--|--|--|--|

| Input Pulse Levels                          | 0.45V to 2.4V |  |  |  |  |  |

| Input Pulse Rise and Fall Times             | 10ns          |  |  |  |  |  |

| Input and Output<br>Timing Reference Levels | 0.8V, 2.0V    |  |  |  |  |  |

| OUTPUT LOAD |                                                               |                                          |  |  |  |  |

|-------------|---------------------------------------------------------------|------------------------------------------|--|--|--|--|

| Load        | Load CL Parameters Measured                                   |                                          |  |  |  |  |

| 1           | 100 pF                                                        | except $t_{DF}$ , $t_{LZ}$ and $t_{OLZ}$ |  |  |  |  |

| 2           | 2 30pF t <sub>DF</sub> , t <sub>LZ</sub> and t <sub>OLZ</sub> |                                          |  |  |  |  |

|     | AC Operating Conditions and Characteristics - Read Cycle: Over operating ranges |                               |       |      |       |      |       |      |      |

|-----|---------------------------------------------------------------------------------|-------------------------------|-------|------|-------|------|-------|------|------|

| No  | No. Symbol                                                                      | ymbol Parameter -             | 120ns |      | 150ns |      | 200ns |      | Unit |

| 10. |                                                                                 |                               | Min.  | Max. | Min.  | Max. | Min.  | Max. | Unit |

| 1   | t <sub>ACC</sub>                                                                | Address to Output Delay       |       | 120  |       | 120  |       | 150  | ns   |

| 2   | t <sub>CE</sub>                                                                 | Chip Enable Output Delay      |       | 120  |       | 120  |       | 150  | ns   |

| 3   | t <sub>OE</sub>                                                                 | Output Enable Output Delay    |       | 60   |       | 70   |       | 80   | ns   |

| 4   | t <sub>DF</sub>                                                                 | Output Enable to Output Delay | 0     | 55   | 0     | 55   | 0     | 70   | ns   |

| 5   | toH                                                                             | Address to Output Hold        | 0     |      | 0     |      | 0     |      | ns   |

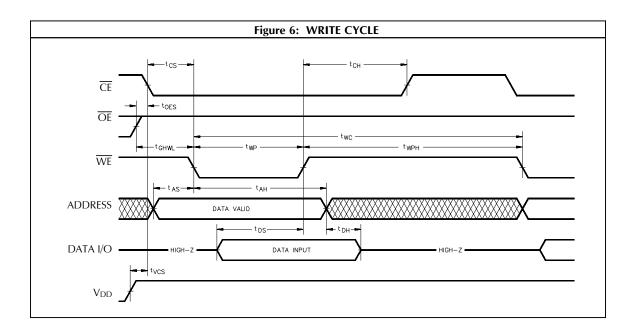

|      | AC Operating Conditions and Characteristics - Write/Erase/Program Cycle: Over operating ranges |                                  |       |      |       |      |       |      |      |

|------|------------------------------------------------------------------------------------------------|----------------------------------|-------|------|-------|------|-------|------|------|

| No   | Symbol                                                                                         | ol Parameter                     | 120ns |      | 150ns |      | 200ns |      | Unit |

| 110. | Symbol                                                                                         | Faranieter                       | Min.  | Max. | Min.  | Max. | Min.  | Max. | Unit |

| 6    | t <sub>WC</sub>                                                                                | Write Cycle Time                 | 120   |      | 150   |      | 200   |      | ns   |

| 7    | t <sub>AS</sub>                                                                                | Address Setup Time               | 0     |      | 0     |      | 0     |      | ns   |

| 8    | t <sub>AH</sub>                                                                                | Address Hold Time                | 50    |      | 60    |      | 70    |      | ns   |

| 9    | t <sub>DS</sub>                                                                                | Data Setup Time                  | 50    |      | 60    |      | 70    |      | ns   |

| 10   | t <sub>DH</sub>                                                                                | Data Hold Time                   | 10    |      | 10    |      | 10    |      | ns   |

| 11   | toes                                                                                           | Output Enable Setup Time         | 0     |      | 0     |      | 0     |      | ns   |

| 12   | t <sub>CES</sub>                                                                               | Chip Enable Setup Time           | 0     |      | 0     |      | 0     |      | ns   |

| 13   | t <sub>GHWL</sub>                                                                              | Read Recovery Time before Write  | 0     |      | 0     |      | 0     |      | ns   |

| 14   | t <sub>CS</sub>                                                                                | Chip Enable Setup Time           | 0     |      | 0     |      | 0     |      | ns   |

| 15   | t <sub>CH</sub>                                                                                | Chip Enable Hold Hold Time       | 0     |      | 0     |      | 0     |      | ns   |

| 16   | t <sub>WP</sub>                                                                                | Write Pulse Width                | 50    |      | 60    |      | 70    |      | ns   |

| 17   | t <sub>WPH</sub>                                                                               | Write Pulse Width HIGH           | 50    |      | 50    |      | 50    |      | ns   |

| 18   | t <sub>BALC</sub>                                                                              | Byte Address Load Cycle          | 0.3   | 30   | 0.3   | 30   | 0.3   | 30   | μs   |

| 19   | t <sub>BAL</sub>                                                                               | Byte Address Load Time           | 100   |      | 100   |      | 100   |      | μs   |

| 20   | t <sub>SRA</sub>                                                                               | Status Register Access Time      | 120   |      | 150   |      | 200   |      | ns   |

| 21   | t <sub>CESR</sub>                                                                              | Chip Enable Setup before SR Read | 100   |      | 100   |      | 100   |      | ns   |

| 22   | t <sub>VCS</sub>                                                                               | V <sub>DD</sub> Setup Time       | 2     |      | 2     |      | 2     |      | μs   |

NOTE: \* = Don't Care, SA = Sector Address, Refer to page 5 for detail Page Program Operation.

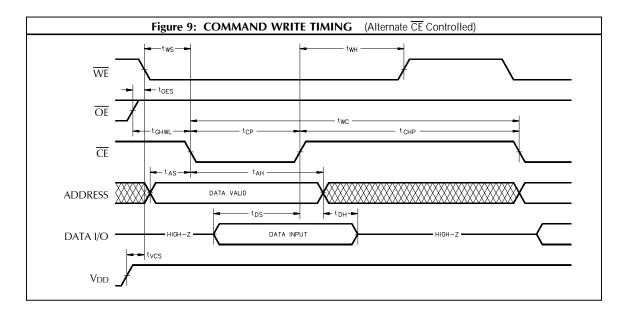

|     | AC Operating Conditions and Characteristics<br>Write/Erase/Program Operation Alternate CE Controlled Writes: Over operating ranges |                                 |      |       |      |       |      |       |      |

|-----|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|-------|------|-------|------|-------|------|

|     |                                                                                                                                    |                                 |      | 120ns |      | 150ns |      | 200ns |      |

| NO. | Symbol                                                                                                                             | Parameter                       | Min. | Max.  | Min. | Max.  | Min. | Max.  | Unit |

| 23  | t <sub>WC</sub>                                                                                                                    | Write Cycle time                | 120  |       | 150  |       | 200  |       | ns   |

| 24  | t <sub>AS</sub>                                                                                                                    | Address Setup Time              | 0    |       | 0    |       | 0    |       | ns   |

| 25  | t <sub>AH</sub>                                                                                                                    | Address Hold Time               | 50   |       | 60   |       | 70   |       | ns   |

| 26  | t <sub>DS</sub>                                                                                                                    | Data Setup Time                 | 50   |       | 60   |       | 70   |       | ns   |

| 27  | t <sub>DH</sub>                                                                                                                    | Data Hold Time                  | 10   |       | 10   |       | 10   |       | ns   |

| 28  | toes                                                                                                                               | Output Enable Setup Time        | 0    |       | 0    |       | 0    |       | ns   |

| 29  | t <sub>CES</sub>                                                                                                                   | Chip Enable Setup time          | 0    |       | 0    |       | 0    |       | ns   |

| 30  | t <sub>GHWL</sub>                                                                                                                  | Read Recovery Time before Write | 0    |       | 0    |       | 0    |       | ns   |

| 31  | t <sub>WS</sub>                                                                                                                    | Write Enable Setup              | 0    |       | 0    |       | 0    |       | ns   |

| 32  | twH                                                                                                                                | Write Enable Hold Time          | 0    |       | 0    |       | 0    |       | ns   |

| 33  | t <sub>CP</sub>                                                                                                                    | Chip Enable Pulse Width         | 50   |       | 60   |       | 70   |       | ns   |

| 34  | tсрн                                                                                                                               | Chip Enable Pulse Width High    | 50   |       | 50   |       | 50   |       | ns   |

| 35  | t <sub>VCS</sub>                                                                                                                   | V <sub>DD</sub> Setup time      | 2    |       | 2    |       | 2    |       | μs   |

## PRELIMINARY

30A161-24 REV. C

## PRELIMINARY

## NOTES:

- 1. All voltages are with respect to  $V_{SS}$ .

- 2. -2.0V min. for pulse width less than 20ns (V<sub>IL</sub> min. = -0.5V at DC level).

- 3. Maximum DC voltage on VPP or A9 may over shoot to +14.0V for periods less than 20ns.

- 4. Stresses greater than those under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 5. This parameter is guaranteed and not 100% tested.

- 6. All currents are in RMS unless otherwise noted. Typical values at  $V_{DD} = 5.0V$ ,  $t = 25^{\circ}C$ . These currents are valid for all product versions (package and speeds.).

- 7. I<sub>CC3</sub> is specified with the device de-selected. If the device is read while in erase suspend mode, current draw is the sum of I<sub>CC3</sub> and I<sub>CC1</sub>/I<sub>CC2</sub>.

- 8.  $V_{IL}$  min. = -1.0V for pulse width  $\leq$  50ns.

- 9.  $V_{IL}$  min. = -2.0V for pulse width  $\leq$  20ns.

- 10. Refer to page 5 for detail Page Program Operation.

| WAVEFORM KEY |                                |                                |                                 |  |  |  |  |  |

|--------------|--------------------------------|--------------------------------|---------------------------------|--|--|--|--|--|

|              |                                |                                |                                 |  |  |  |  |  |

| Data Valid   | Transition from<br>HIGH to LOW | Transition from<br>LOW to HIGH | Data Undefined<br>or Don't Care |  |  |  |  |  |

|              |                                |                                |                                 |  |  |  |  |  |

## Dense-Pac Microsystems, Inc.

## Dense-Pac Microsystems, Inc.

# DP5Z4MW16Pn3

## PRELIMINARY

# Dense-Pac Microsystems, Inc.

7321 Lincoln Way, Garden Grove, California 92841-1431

(714) 898-0007 ◆ (800) 642-4477 ◆ FAX: (714) 897-1772 ◆ http://www.dense-pac.com