# One-PLL General-Purpose Flash-Programmable and 2-Wire Serially Programmable Clock Generator

| Features                                    | Benefits                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrated phase-locked loop (PLL)          | Internal PLL to generate six outputs up to 200 MHz. Able to generate custom frequencies from an external crystal or a driven source.                                                                                                                                                                                                                                    |

| Commercial and industrial operation         | Performance guaranteed for applications that require an extended temper-<br>ature range.                                                                                                                                                                                                                                                                                |

| • Flash-programmable                        | Nonvolatile reprogrammable technology allows easy customization, quick<br>turnaround on design changes and product performance enhancements,<br>and better inventory control. Parts can be reprogrammed up to 100 times,<br>reducing inventory of custom parts and providing an easy method for<br>upgrading existing designs.                                          |

| • Field-programmable                        | The CY22150 can be programmed at the package level. In-house programming of samples and prototype quantities is available using the CY3672 FTG Development Kit. Production quantities are available through Cypress's value-added distribution partners or by using third party programmers from BP Microsystems <sup>™</sup> , HiLo Systems <sup>™</sup> , and others. |

| 2-wire serial programming interface         | The CY22150 provides an industry-standard interface for volatile, system-level customization of unique frequencies and options. Serial programming and reprogramming allows quick design changes and product enhancements, eliminates inventory of old design parts, and simplifies manufacturing.                                                                      |

| Low-skew, low-jitter, high-accuracy outputs | High performance suited for commercial, industrial, networking, telecomm and other general-purpose applications.                                                                                                                                                                                                                                                        |

| 3.3V operation with 2.5V output option      | Application compatibility in standard and low-power systems.                                                                                                                                                                                                                                                                                                            |

| 16-lead TSSOP                               | Industry-standard packaging saves on board space.                                                                                                                                                                                                                                                                                                                       |

٠

| Part Number | Outputs | Input Frequency Range                                           | Output Frequency Range                               | Specifications                                                        |

|-------------|---------|-----------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|

| CY22150FC   | 6       | 8 MHz–30 MHz (external crystal)<br>1 MHz–133 MHz (driven clock) | 80 kHz–200 MHz (3.3V)<br>80 KHz–166.6 MHz (2.5V)     | Field programmable<br>Serially programmable<br>Commercial temperature |

| CY22150FI   | 6       | 8 MHz–30 MHz (external crystal)<br>1 MHz–133 MHz (driven clock) | 80 kHz – 166.6 MHz (3.3V)<br>80 KHz – 150 MHz (2.5V) | Field programmable<br>Serially programmable<br>Industrial temperature |

#### **Pin Summary**

| Pin Name            | Pin Number | Pin Description                                                                                                                                                                                                                                           |

|---------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN                 | 1          | <b>Reference Input</b> . Driven by a crystal (8 MHz – 30 MHz) or external clock (1 MHz – 133 MHz). Programmable input load capacitors allow for maximum flexibility in selecting a crystal, regardless of manufacturer, process, performance, or quality. |

| VDD                 | 2          | 3.3V voltage supply                                                                                                                                                                                                                                       |

| AVDD                | 3          | 3.3V analog voltage supply                                                                                                                                                                                                                                |

| SDAT                | 4          | Serial data input                                                                                                                                                                                                                                         |

| AVSS                | 5          | Analog ground                                                                                                                                                                                                                                             |

| VSSL                | 6          | LCLK ground                                                                                                                                                                                                                                               |

| LCLK1               | 7          | Configurable clock output 1 at V <sub>DDL</sub> level (3.3V or 2.5V)                                                                                                                                                                                      |

| LCLK2               | 8          | Configurable clock output 2 at V <sub>DDL</sub> level (3.3V or 2.5V)                                                                                                                                                                                      |

| LCLK3               | 9          | Configurable clock output 3 at V <sub>DDL</sub> level (3.3V or 2.5V)                                                                                                                                                                                      |

| SCLK                | 10         | Serial clock input                                                                                                                                                                                                                                        |

| VDDL                | 11         | LCLK voltage supply (2.5V or 3.3V)                                                                                                                                                                                                                        |

| LCLK4               | 12         | Configurable clock output 4 at V <sub>DDL</sub> level (3.3V or 2.5V)                                                                                                                                                                                      |

| VSS                 | 13         | Ground                                                                                                                                                                                                                                                    |

| CLK5                | 14         | Configurable clock output 5 (3.3V)                                                                                                                                                                                                                        |

| CLK6                | 15         | Configurable clock output 6 (3.3V)                                                                                                                                                                                                                        |

| XOUT <sup>[1]</sup> | 16         | Reference output                                                                                                                                                                                                                                          |

#### **Frequency Calculation and Register Definitions**

The CY22150 is an extremely flexible clock generator with four basic variables that can be used to determine the final output frequency. They are the input reference frequency (REF), the internally calculated P and Q dividers, and the post divider, which can be a fixed or calculated value. There are three basic formulas for determining the final output frequency of a CY22150-based design:

- CLK = ((REF \* P)/Q)/Post Divider

- CLK = REF/Post Divider

- CLK = REF.

Note:

1. Float XOUT if XIN is driven by an external clock source.

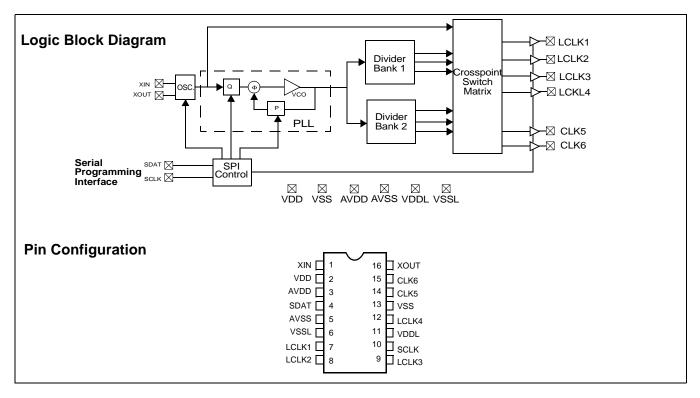

The basic PLL block diagram is shown in *Figure 1*. Each of the six clock outputs on the CY22150 has a total of seven output options available to it. There are six post divider options available: /2 (two of these), /3, /4, /DIV1N and /DIV2N. DIV1N and DIV2N are independently calculated and are applied to individual output groups. The post divider options can be applied to the calculated VCO frequency ((REF\*P)/Q) or to the REF directly.

In addition to the six post divider output options, the seventh option bypasses the PLL and passes the REF directly to the crosspoint switch matrix.

Figure 1. Basic Block Diagram of CY22150 PLL

#### Default Start-up Condition for the CY22150

The default (programmed) condition of the device is generally set by the distributor who programs the device using a customer-specific JEDEC file produced by CyClocksRT<sup>™</sup>. Parts shipped from the factory are blank and unprogrammed. In this condition, all bits are set to 0, all outputs are three-stated, and the crystal oscillator circuit is active.

While you can develop your own subroutine to program any or all of the individual registers described in the following pages, it may be easier to use CyClocksRT to produce the required register setting file.

The serial interface address of the CY22150 is 69H. Should there be a conflict with any other devices in your system, this can also be changed using CyClocksRT.

#### Frequency Calculations and Register Definitions Using the Serial Programming Interface

The CY22150 provides an industry standard serial interface for volatile, in-system programming of unique frequencies and options. Serial programming and reprogramming allows for quick design changes and product enhancements, eliminates inventory of old design parts, and simplifies manufacturing.

The Serial Programming Interface (SPI) provides volatile programming, i.e., when the target system is powered down, the CY22150 reverts to its pre-SPI state, as defined above (programmed or unprogrammed). When the system is powered back up again, the SPI registers will need to be reconfigured again.

All programmable registers in the CY22150 are addressed with eight bits and contain eight bits of data. The CY22150 is a slave device with an address of 1101001 (69H).

*Table 1* lists the SPI registers and their definitions. Specific register definitions and their allowable values are listed below.

#### **Reference Frequency**

The REF can be a crystal or a driven frequency. For crystals, the frequency range must be between 8 MHz and 30 MHz. For a driven frequency, the frequency range must be between 1 MHz and 133 MHz.

#### Using a Crystal as the Reference Input

The input crystal oscillator of the CY22150 is an important feature because of the flexibility it allows the user in selecting a crystal as a REF source. The input oscillator has programmable gain, allowing for maximum compatibility with a reference crystal, regardless of manufacturer, process, performance and quality.

#### Programmable Crystal Input Oscillator Gain Settings

The Input crystal oscillator gain (XDRV) is controlled by two bits in register 12H, and are set according to *Table 2*. The parameters controlling the gain are the crystal frequency, the internal crystal parasitic resistance (ESR, available from the manufacturer), and the CapLoad setting during crystal start-up.

Bits 3 and 4 of register 12H control the input crystal oscillator gain setting. Bit 4 is the MSB of the setting, and bit 3 is the LSB. The setting is programmed according to *Table 2*. All other bits in the register are reserved and should be programmed as shown in *Table 3*.

#### Using an External Clock as the Reference Input

The CY22150 can also accept an external clock as reference, with speeds up to 133 MHz. With an external clock, the XDRV (register 12H) bits must be set according to *Table 4*.

| Register | Description                            | D7                   | D6                  | D5             | D4                   | D3             | D2                  | D1                  | D0                  |

|----------|----------------------------------------|----------------------|---------------------|----------------|----------------------|----------------|---------------------|---------------------|---------------------|

| 09H      | CLKOE control                          | 0                    | 0                   | CLK6           | CLK5                 | LCLK4          | LCLK3               | LCLK2               | LCLK1               |

| OCH      | DIV1SRC mux and<br>DIV1N divider       | DIV1SRC              | DIV1N(6)            | DIV1N(5)       | DIV1N(4)             | DIV1N(3)       | DIV1N(2)            | DIV1N(1)            | DIV1N(0)            |

| 12H      | Input crystal oscillator drive control | 0                    | 0                   | 1              | XDRV(1)              | XDRV(0)        | 0                   | 0                   | 0                   |

| 13H      | Input load capacitor<br>control        | CapLoad<br>(7)       | CapLoad<br>(6)      | CapLoad<br>(5) | CapLoad<br>(4)       | CapLoad<br>(3) | CapLoad<br>(2)      | CapLoad<br>(1)      | CapLoad<br>(0)      |

| 40H      | Charge Pump and PB                     | 1                    | 1                   | 0              | Pump(2)              | Pump(1)        | Pump(0)             | PB(9)               | PB(8)               |

| 41H      | counter                                | PB(7)                | PB(6)               | PB(5)          | PB(4)                | PB(3)          | PB(2)               | PB(1)               | PB(0)               |

| 42H      | PO counter, Q<br>counter               | PO                   | Q(6)                | Q(5)           | Q(4)                 | Q(3)           | Q(2)                | Q(1)                | Q(0)                |

| 44H      | Crosspoint switch<br>matrix control    | CLKSRC2<br>for LCLK1 |                     |                | CLKSRC2<br>for LCLK2 |                |                     |                     |                     |

| 45H      |                                        |                      |                     |                | CLKSRC0<br>for LCLK4 |                | CLKSRC1<br>for CLK5 | CLKSRC0<br>for CLK5 | CLKSRC2<br>for CLK6 |

| 46H      |                                        | CLKSRC1<br>for CLK6  | CLKSRC0<br>for CLK6 | 1              | 1                    | 1              | 1                   | 1                   | 1                   |

| 47H      | DIV2SRC mux and<br>DIV2N divider       | DIV2SRC              | DIV2N(6)            | DIV2N(5)       | DIV2N(4)             | DIV2N(3)       | DIV2N(2)            | DIV2N(1)            | DIV2N(0)            |

#### Table 2. Programmable Crystal Input Oscillator Gain Settings

|               | Calculated CapLoad Value | 00H ·       | 00H – 20H   |             | - 30H       | 30H – 40H   |             |

|---------------|--------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

|               | Crystal ESR              | <b>30</b> Ω | <b>60</b> Ω | <b>30</b> Ω | <b>60</b> Ω | <b>30</b> Ω | <b>60</b> Ω |

| Crystal Input | 8 – 15 MHz               | 00          | 01          | 01          | 10          | 01          | 10          |

| Frequency     | 15 – 20 MHz              | 01          | 10          | 01          | 10          | 10          | 10          |

|               | 20 – 25 MHz              | 01          | 10          | 10          | 10          | 10          | 11          |

|               | 25 – 30 MHz              | 10          | 10          | 10          | 11          | 11          | N/A         |

#### Table 3. Bit Locations and Values

| Address | D7 | D6 | D5 | D4      | D3      | D2 | D1 | D0 |

|---------|----|----|----|---------|---------|----|----|----|

| 12H     | 0  | 0  | 1  | XDRV(1) | XDRV(0) | 0  | 0  | 0  |

#### Table 4. Programmable External Reference Input Oscillator Drive Settings

| Reference Frequency | 1 – 25 MHz | 25 – 50 MHz | 50 – 90 MHz | 90 – 133 MHz |

|---------------------|------------|-------------|-------------|--------------|

| Drive Setting       | 00         | 01          | 10          | 11           |

#### Input Load Capacitors

Input load capacitors allow the user to set the load capacitance of the CY22150 to match the input load capacitance from a crystal. The value of the input load capacitors is determined by 8 bits in a programmable register [13H]. Total load capacitance is determined by the formula:

CapLoad = (CL- CBRD - CCHIP)/0.09375 pF

where:

- C<sub>L</sub> = specified load capacitance of your crystal.

- C<sub>BRD</sub> = the total board capacitance, due to external capacitors and board trace capacitance. In CyClocksRT, this value defaults to 2 pF.

- C<sub>CHIP</sub> = 6 pF.

- 0.09375 pF = the step resolution available due to the 8-bit register.

In CyclocksRT, only the crystal capacitance (C<sub>L</sub>) is specified. C<sub>CHIP</sub> is set to 6 pF, and C<sub>BRD</sub> defaults to 2 pF. If your board capacitance is higher or lower than 2 pF, the formula above can be used to calculate a new CapLoad value and programmed into register 13H.

In CyClocksRT, enter the crystal capacitance (C<sub>L</sub>). The value of CapLoad will be determined automatically and programmed into the CY22150. Through the SDAT and SCLK pins, the value can be adjusted up or down if your board capacitance is greater or less than 2 pF. For an external clock source, CapLoad defaults to 0. See *Table 5* for CapLoad bit locations and values.

The input load capacitors are placed on the CY22150 die to reduce external component cost. These capacitors are true parallel-plate capacitors, designed to reduce the frequency shift that occurs when non-linear load capacitance is affected by load, bias, supply and temperature changes.

#### PLL Frequency, Q Counter [42H(6..0)]

The first counter is known as the Q counter. The Q counter divides REF by its calculated value. Q is a 7 bit divider with a maximum value of 127 and minimum value of 0. The primary value of Q is determined by 7 bits in register 42H (6..0), but 2 is added to this register value to achieve the total Q, or  $Q_{total}$ .  $Q_{total}$  is defined by the formula:

#### $Q_{total} = Q + 2$

The minimum value of  $Q_{total}$  is 2. The maximum value of  $Q_{total}$  is 129. Register 42H is defined in the table.

Stable operation of the CY22150 cannot be guaranteed if REF/Q<sub>total</sub> falls below 250 kHz. Q<sub>total</sub> bit locations and values are defined in *Table 6*.

## PLL Frequency, P Counter [40H(1..0)], [41H(7..0)], [42H(7)

The next counter definition is the P (product) counter. The P counter is multiplied with the (REF/ $Q_{total}$ ) value to achieve the VCO frequency. The product counter, defined as P<sub>total</sub>, is

made up of two internal variables, PB and PO. The formula for calculating  $\mathsf{P}_{total}$  is:

#### $P_{total} = (2(PB + 4) + PO).$

PB is a 10-bit variable, defined by registers 40H(1:0) and 41H(7:0). The 2 LSBs of register 40H are the two MSBs of variable PB. Bits 4..2 of register 40H are used to determine the charge pump settings (see Section 5). The 3 MSBs of register 40H are preset and reserved and cannot be changed. PO is a single bit variable, defined in register 42H(7). This allows for odd numbers in P<sub>total</sub>.

The remaining seven bits of 42H are used to define the Q counter, as shown in *Table 6*.

The minimum value of  $P_{total}$  is 8. The maximum value of  $P_{total}$  is 2055. To achieve the minimum value of  $P_{total}$ , PB and PO should both be programmed to 0. To achieve the maximum value of  $P_{total}$ , PB should be programmed to 1023, and PO should be programmed to 1.

Stable operation of the CY22150 cannot be guaranteed if the value of  $(P_{total}^{*}(REF/Q_{total}))$  is above 400 MHz or below 100 MHz. Registers 40H, 41H and 42H are defined in *Table 7*. PLL Post Divider Options [OCH(7..0)], [47H(7..0)]

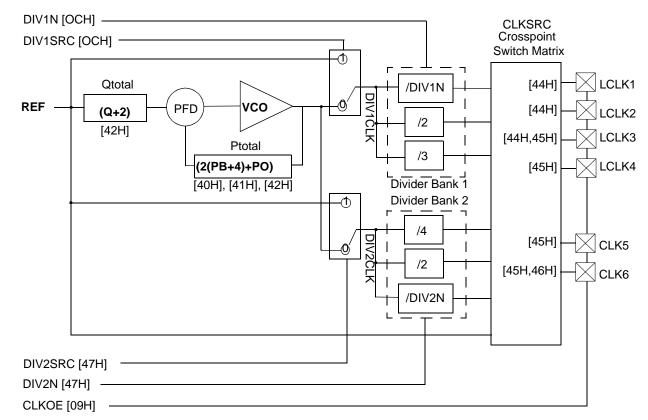

The output of the VCO is routed through two independent muxes, then to two divider banks to determine the final clock output frequency. The mux determines if the clock signal feeding into the divider banks is the calculated VCO frequency or REF. There are two select muxes (DIV1SRC and DIV2SRC) and two divider banks (Divider Bank 1 and Divider Bank 2) used to determine this clock signal. The clock signal passing through DIV1SRC and DIV2SRC is referred to as DIV1CLK and DIV2CLK, respectively.

The divider banks have 4 unique divider options available: /2, /3, /4, and /DIVxN. DIVxN is a variable that can be independently programmed (DIV1N and DIV2N) for each of the two divider banks. The minimum value of DIVxN is 4. The maximum value of DIVxN is 127. A value of DIVxN below 4 is not guaranteed to work properly.

DIV1SRC is a single bit variable, controlled by register OCH. The remaining seven bits of register OCH determine the value of post divider DIV1N.

DIV2SRC is a single bit variable, controlled by register 47H. The remaining seven bits of register 47H determine the value of post divider DIV2N.

Register OCH and 47H are defined in Table 8.

#### Charge Pump Settings [40H(2..0)]

The correct pump setting is important for PLL stability. Charge pump settings are controlled by bits (4..2) of register 40H, and are dependent on internal variable PB (see "*PLL Frequency, P Counter*[40H(1..0)], [41H(7..0)], [42H(7)]"). Table 9 summarizes the proper charge pump settings, based on Ptotal.

See Table 10 for register 40H bit locations and values.

Table 5. Input Load Capacitor Register Bit Settings

| Address | D7         | D6         | D5         | D4         | D3         | D2         | D1         | D0         |

|---------|------------|------------|------------|------------|------------|------------|------------|------------|

| 13H     | CapLoad(7) | CapLoad(6) | CapLoad(5) | CapLoad(4) | CapLoad(3) | CapLoad(2) | CapLoad(1) | CapLoad(0) |

#### Table 6. P Counter Register Definition

| Address | D7    | D6    | D5    | D4      | D3      | D2      | D1    | D0    |

|---------|-------|-------|-------|---------|---------|---------|-------|-------|

| 40H     | 1     | 1     | 0     | Pump(2) | Pump(1) | Pump(0) | PB(9) | PB(8) |

| 41H     | PB(7) | PB(6) | PB(5) | PB(4)   | PB(3)   | PB(2)   | PB(1) | PB(0) |

| 42H     | PO    | Q(6)  | Q(5)  | Q(4)    | Q(3)    | Q(2)    | Q(1)  | Q(0)  |

#### Table 7. P Counter Register Definition

| Address | D7    | D6    | D5    | D4      | D3      | D2      | D1    | D0    |

|---------|-------|-------|-------|---------|---------|---------|-------|-------|

| 40H     | 1     | 1     | 0     | Pump(2) | Pump(1) | Pump(0) | PB(9) | PB(8) |

| 41H     | PB(7) | PB(6) | PB(5) | PB(4)   | PB(3)   | PB(2)   | PB(1) | PB(0) |

| 42H     | PO    | Q(6)  | Q(5)  | Q(4)    | Q(3)    | Q(2)    | Q(1)  | Q(0)  |

#### Table 8. PLL Post Divider Options

| Address | D7      | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

|---------|---------|----------|----------|----------|----------|----------|----------|----------|

| OCH     | DIV1SRC | DIV1N(6) | DIV1N(5) | DIV1N(4) | DIV1N(3) | DIV1N(2) | DIV1N(1) | DIV1N(0) |

| 47H     | DIV2SRC | DIV2N(6) | DIV2N(5) | DIV2N(4) | DIV2N(3) | DIV2N(2) | DIV2N(1) | DIV2N(0) |

#### Table 9. Charge Pump Settings

| Charge Pump Setting – Pump(20) | Calculated P <sub>total</sub>        |

|--------------------------------|--------------------------------------|

| 000                            | 16 - 44                              |

| 001                            | 45 – 479                             |

| 010                            | 480 - 639                            |

| 011                            | 640 – 799                            |

| 100                            | 800 – 1023                           |

| 101, 110, 111                  | Do not use – device will be unstable |

#### Table 10. Register 40H Change Pump Bit Settings

| Address | D7 | D6 | D5 | D4      | D3      | D2      | D1    | D0    |

|---------|----|----|----|---------|---------|---------|-------|-------|

| 40H     | 1  | 1  | 0  | Pump(2) | Pump(1) | Pump(0) | PB(9) | PB(8) |

Although using the above table will guarantee stability, it is recommended to use the Print Preview function in CyClocksRT to determine the correct charge pump settings for optimal jitter performance.

PLL stability cannot be guaranteed for values below 16 and above 1023. If values above 1023 are needed, use CyClocksRT to determine the best charge pump setting.

#### Clock Output Settings: CLKSRC – Clock Output Crosspoint Switch Matrix [44H(7..0)], [45H(7..0)], [46H(7..6)]

#### CLKOE – Clock Output Enable Control [09H(5..0)]

Every clock output can be defined to come from one of seven unique frequency sources. The CLKSRC(2..0) crosspoint switch matrix defines which source is attached to each individual clock output. CLKSRC(2..0) is set in Registers 44H, 45H, and 46H. The remainder of register 46H(5:0) must be written with the values stated in the register table when writing register values 46H(7:6).

In addition, each clock output has individual CLKOE control, set by register 09H(5..0).

When DIV1N is divisible by four, then CLKSRC(0,1,0) is guaranteed to be rising edge phase-aligned with

CLKSRC(0,0,1). When DIV1N is six, then CLKSRC(0,1,1) is guaranteed to be rising edge phase-aligned with CLKSRC(0,0,1).

When DIV2N is divisible by four, then CLKSRC(1,0,1) is guaranteed to be rising edge phase-aligned with CLKSRC(1,0,0). When DIV2N is divisible by eight, then CLKSRC(1,1,0) is guaranteed to be rising edge phase-aligned with CLKSRC(1,0,0).

Each clock output has its own output enable, controlled by register 09H(5..0). To enable an output, set the corresponding CLKOE bit to 1. CLKOE settings are in *Table 13*.

The output swing of LCLK1 through LCLK4 is set by  $V_{DDL}.$  The output swing of CLK5 and CLK6 is set by  $V_{DD}.$

#### Test, Reserved, and Blank Registers

Writing to any of the following registers will cause the part to exhibit abnormal behavior, as follows.

| <ul> <li>Reserved</li> </ul>  |

|-------------------------------|

| <ul> <li>Reserved</li> </ul>  |

| <ul> <li>Reserved.</li> </ul> |

|                               |

#### Table 11.

| CLKSRC2 | CLKSRC1 | CLKSRC0 | Definition and Notes                                                                                                                             |

|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | 0       | Reference input.                                                                                                                                 |

| 0       | 0       | 1       | DIV1CLK/DIV1N. DIV1N is defined by register [OCH]. Allowable values for DIV1N are 4 to 127. If Divider Bank 1 is not being used, set DIV1N to 8. |

| 0       | 1       | 0       | DIV1CLK/2. Fixed /2 divider option. If this option is used, DIV1N must be divisible by 4.                                                        |

| 0       | 1       | 1       | DIV1CLK/3. Fixed /3 divider option. If this option is used, set DIV1N to 6.                                                                      |

| 1       | 0       | 0       | DIV2CLK/DIV2N. DIV2N is defined by Register [47H]. Allowable values for DIV2N are 4 to 127. If Divider Bank 2 is not being used, set DIV2N to 8. |

| 1       | 0       | 1       | DIV2CLK/2. Fixed /2 divider option. If this option is used, DIV2N must be divisible by 4.                                                        |

| 1       | 1       | 0       | DIV2CLK/4. Fixed /4 divider option. If this option is used, DIV2N must be divisible by 8.                                                        |

| 1       | 1       | 1       | Reserved – do not use.                                                                                                                           |

#### Table 12.

| Address | D7                  | D6                  | D5        | D4        | D3        | D2        | D1        | D0        |

|---------|---------------------|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 44H     | CLKSRC2             | CLKSRC1             | CLKSRC0   | CLKSRC2   | CLKSRC1   | CLKSRC0   | CLKSRC2   | CLKSRC1   |

|         | for LCLK1           | for LCLK1           | for LCLK1 | for LCLK2 | for LCLK2 | for LCLK2 | for LCLK3 | for LCLK3 |

| 45H     | CLKSRC0             | CLKSRC2             | CLKSRC1   | CLKSRC0   | CLKSRC2   | CLKSRC1   | CLKSRC0   | CLKSRC2   |

|         | for LCLK3           | for LCLK4           | for LCLK4 | for LCLK4 | for CLK5  | for CLK5  | for CLK5  | for CLK6  |

| 46H     | CLKSRC1<br>for CLK6 | CLKSRC0<br>for CLK6 | 1         | 1         | 1         | 1         | 1         | 1         |

#### Table 13. CLKOE Bit Setting

| Address | D7 | D6 | D5   | D4   | D3    | D2    | D1    | D0    |

|---------|----|----|------|------|-------|-------|-------|-------|

| 09H     | 0  | 0  | CLK6 | CLK5 | LCLK4 | LCLK3 | LCLK2 | LCLK1 |

#### **Programmable Interface Timing**

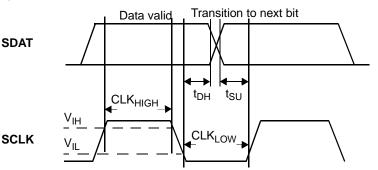

The CY22150 utilizes a 2-wire serial-interface SDAT and SCLK that operates up to 400 kbits/second in Read or Write mode. The basic Write serial format is as follows.

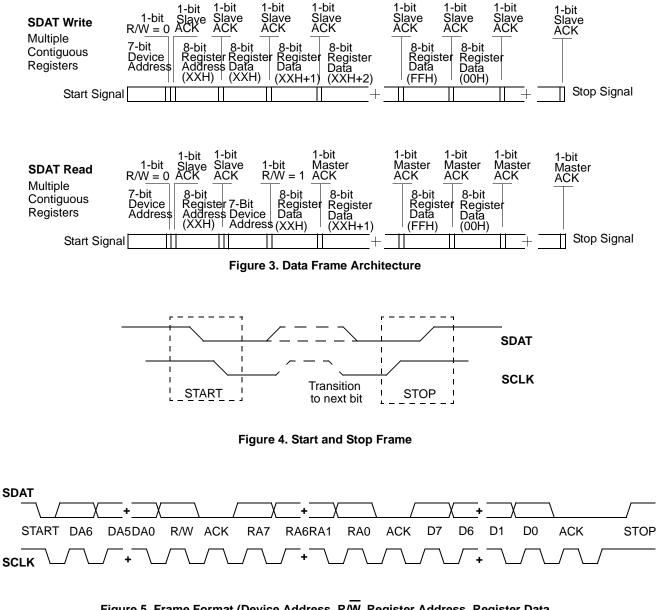

Start Bit; seven-bit Device Address (DA); R/W Bit; Slave Clock Acknowledge (ACK); eight-bit Memory Address (MA); ACK; eight-bit data; ACK; eight-bit data in MA + 1 if desired; ACK; eight-bit data in MA+2; ACK; etc. until STOP bit.The basic serial format is illustrated in *Figure 3*.

#### Data Valid

Data is valid when the Clock is HIGH, and may only be transitioned when the clock is LOW, as illustrated in *Figure 2*.

#### **Data Frame**

Every new data frame is indicated by a start and stop sequence, as illustrated in *Figure 4*.

**Start Sequence** – Start frame is indicated by SDAT going LOW when SCLK is HIGH. Every time a Start signal is given, the next eight-bit data must be the device address (seven bits) and a R/W bit, followed by register address (eight bits) and register data (eight bits).

**Stop Sequence** – Stop frame is indicated by SDAT going HIGH when SCLK is HIGH. A Stop frame frees the bus for writing to another part on the same bus or writing to another random register address.

#### **Acknowledge Pulse**

During Write mode, the CY22150 will respond with an ACK pulse after every eight bits. This is accomplished by pulling the SDAT line LOW during the N\*9<sup>th</sup> clock cycle, as illustrated in *Figure 5.* (N = the number of eight-bit segments transmitted.) During Read mode, the ACK pulse after the data packet is sent is generated by the master.

Figure 2. Data Valid and Data Transition Periods

| Figure 5. Frame Format (Device Address | , R/W, Register Address, Register Data |

|----------------------------------------|----------------------------------------|

|----------------------------------------|----------------------------------------|

| Parameter           | Description                                | Min. | Max. | Unit |

|---------------------|--------------------------------------------|------|------|------|

| f <sub>SCLK</sub>   | Frequency of SCLK                          |      | 400  | kHz  |

|                     | Start mode time from SDA LOW to SCL LOW    | 0.6  |      | μs   |

| CLK <sub>LOW</sub>  | SCLK LOW period                            | 1.3  |      | μs   |

| CLK <sub>HIGH</sub> | SCLK HIGH period                           | 0.6  |      | μs   |

| t <sub>SU</sub>     | Data transition to SCLK HIGH               | 100  |      | ns   |

| t <sub>DH</sub>     | Data hold (SCLK LOW to data transition)    | 0    |      | ns   |

|                     | Rise time of SCLK and SDAT                 |      | 300  | ns   |

|                     | Fall time of SCLK and SDAT                 |      | 300  | ns   |

|                     | Stop mode time from SCLK HIGH to SDAT HIGH | 0.6  |      | μs   |

|                     | Stop mode to Start mode                    | 1.3  |      | μs   |

#### Applications

#### **Controlling Jitter**

Jitter is defined in many ways including: phase noise, long-term jitter, cycle to cycle jitter, period jitter, absolute jitter, and deterministic. These jitter terms are usually given in terms of rms, peak to peak, or in the case of phase noise dBC/Hz with respect to the fundamental frequency.

Power Supply Noise and clock output loading are two major system sources of clock jitter. Power Supply noise can be mitigated by proper power supply decoupling (0.1  $\mu$ F ceramic cap 0.25") of the clock and ensuring a low impedance ground to the chip. Reducing capacitive clock output loading to a minimum lowers current spikes on the clock edges and thus reduces jitter.

Reducing the total number of active outputs will also reduce jitter in a linear fashion. However, it is better to use two outputs to drive two loads than one output to drive two loads.

**Test Circuit**

The rate and magnitude that the PLL corrects the VCO frequency is directly related to jitter performance. If the rate is too slow, then long term jitter and phase noise will be poor. Therefore, to improve long-term jitter and phase noise, reducing Q to a minimum is advisable. This technique will increase the speed of the Phase Frequency Detector which in turn drive the input voltage of the VCO. In a similar manner increasing P till the VCO is near its maximum rated speed will also decrease long term jitter and phase noise. For example: Input Reference of 12 MHz; desired output frequency of 33.3 MHz. One might arrive at the following solution: Set Q = 3, P = 25, Post Div = 3. However, the best jitter results will be Q = 2, P = 50, Post Div = 9.

For more information, refer to the application note "*Jitter in PLL-Based Systems: Causes, Effects, and Solutions*" available at http://www.cypress.com/clock/appnotes.html, or contact your local Cypress field applications engineer.

Figure 8. Peak-to-Peak Jitter

#### Table 14. Absolute Maximum Conditions

| Parameter        | Description                                           | Min.                  | Max.                   | Unit |

|------------------|-------------------------------------------------------|-----------------------|------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                                        | -0.5                  | 7.0                    | V    |

| V <sub>DDL</sub> | I/O Supply Voltage                                    | -0.5                  | 7.0                    | V    |

| Τ <sub>S</sub>   | Storage Temperature <sup>[2]</sup>                    | -65                   | 125                    | °C   |

| TJ               | Junction Temperature                                  |                       | 125                    | °C   |

|                  | Package Power Dissipation – Commercial Temp           |                       | 450                    | mW   |

|                  | Package Power Dissipation – Industrial Temp           |                       | 380                    | mW   |

|                  | Digital Inputs                                        | $AV_{SS} - 0.3$       | AV <sub>DD</sub> + 0.3 | V    |

|                  | Digital Outputs referred to V <sub>DD</sub>           | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3  | V    |

|                  | Digital Outputs referred to V <sub>DDL</sub>          | $V_{SS} - 0.3$        | V <sub>DDL</sub> +0.3  | V    |

| ESD              | Static Discharge Voltage per MIL-STD-833, Method 3015 |                       | 2000                   | V    |

#### Table 15. Recommended Operating Conditions

| Parameter                         | Description                                                                                   | Min.  | Тур. | Max.  | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>DD</sub>                   | Operating Voltage                                                                             | 3.135 | 3.3  | 3.465 | V    |

| VDDL <sub>HI</sub> <sup>[3]</sup> | Operating Voltage                                                                             | 3.135 | 3.3  | 3.465 | V    |

| VDDL <sub>LO</sub> <sup>[3]</sup> | Operating Voltage                                                                             | 2.375 | 2.5  | 2.625 | V    |

| T <sub>AC</sub>                   | Ambient Commercial Temp                                                                       | 0     |      | 70    | °C   |

| T <sub>AI</sub>                   | Ambient Industrial Temp                                                                       | -40   |      | 85    | °C   |

| C <sub>LOAD</sub>                 | Max. Load Capacitance, V <sub>DD</sub> /V <sub>DDL</sub> = 3.3V                               |       |      | 15    | pF   |

| C <sub>LOAD</sub>                 | Max. Load Capacitance, V <sub>DDL</sub> = 2.5V                                                |       |      | 15    | pF   |

| f <sub>REFD</sub>                 | Driven REF                                                                                    | 1     |      | 133   | MHz  |

| f <sub>REFC</sub>                 | Crystal REF                                                                                   | 8     |      | 30    | MHz  |

| t <sub>PU</sub>                   | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) | 0.05  |      | 500   | ms   |

#### Table 16. DC Electrical Characteristics

| Parameter <sup>[4]</sup>          | Name                                      | Description                                                   | Min. | Тур. | Max. | Unit            |

|-----------------------------------|-------------------------------------------|---------------------------------------------------------------|------|------|------|-----------------|

| I <sub>OH3.3</sub>                | Output High Current                       | $V_{OH} = V_{DD} - 0.5, V_{DD}/V_{DDL} = 3.3V \text{ (sink)}$ | 12   | 24   |      | mA              |

| I <sub>OL3.3</sub>                | Output Low Current                        | $V_{OL} = 0.5, V_{DD}/V_{DDL} = 3.3V$ (source)                | 12   | 24   |      | mA              |

| I <sub>OH2.5</sub>                | Output High Current                       | $V_{OH} = V_{DDL} - 0.5$ , $V_{DDL} = 2.5V$ (source)          | 8    | 16   |      | mA              |

| I <sub>OL2.5</sub>                | Output Low Current                        | $V_{OL} = 0.5, V_{DDL} = 2.5V \text{ (sink)}$                 | 8    | 16   |      | mA              |

| V <sub>IH</sub>                   | Input High Voltage                        | CMOS levels, 70% of V <sub>DD</sub>                           | 0.7  |      |      | V <sub>DD</sub> |

| V <sub>IL</sub>                   | Input Low Voltage                         | CMOS levels, 30% of V <sub>DD</sub>                           |      |      | 0.3  | V <sub>DD</sub> |

| C <sub>IN</sub>                   | Input Capacitance                         | SCLK and SDAT Pins                                            |      |      | 7    | pF              |

| I <sub>IZ</sub>                   | Input Leakage Current                     | SCLK and SDAT Pins                                            |      | 5    |      | μΑ              |

| V <sub>HYS</sub>                  | Hysteresis of Schmitt<br>triggered inputs | SCLK and SDAT Pins                                            | 0.05 |      |      | V <sub>DD</sub> |

| I <sub>VDD</sub> <sup>[5,6]</sup> | Supply Current                            | AV <sub>DD</sub> /V <sub>DD</sub> Current                     |      | 45   |      | mA              |

| I <sub>VDDL3.3</sub> [5,6]        | Supply Current                            | V <sub>DDL</sub> Current (V <sub>DDL</sub> = 3.465V)          |      | 25   |      | mA              |

| I <sub>VDDL2.5</sub> [5,6]        | Supply Current                            | $V_{DDL}$ Current ( $V_{DDL}$ = 2.625V)                       |      | 17   |      | mA              |

Notes:

Rated for 10 years.

V<sub>DDL</sub> is only specified and characterized at 3.3V ± 5% and 2.5V ± 5%. V<sub>DDL</sub> may be powered at any value between 3.465V and 2.375V.

Not 100% tested.

IV\_DD currents specified for two CLK outputs running at 125 MHz, two LCLK outputs running at 80 MHz, and two LCLK outputs running at 66.6 MHz.

Use CyClocksRT to calculate actual I<sub>VDD</sub> and I<sub>VDDL</sub> for specific output frequency configurations.

#### **Table 17. AC Electrical Characteristics**

| Parameter <sup>[7]</sup> | Name                                                                                                                                                                                                                       | Description                                                                                          | Min.          | Тур. | Max.  | Unit |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------|------|-------|------|

| t1                       | Output Frequency,                                                                                                                                                                                                          | Clock output limit, 3.3V                                                                             | 0.08 (80 kHz) |      | 200   | MHz  |

|                          | Output Frequency,<br>Commercial Temp         Output Frequency,<br>Industrial Temp         Output Duty Cycle         Output Duty Cycle         Rising Edge Slew<br>Rate (V <sub>DDL</sub> = 2.5V)         Falling Edge Slew | Clock output limit, 2.5V                                                                             | 0.08 (80 kHz) |      | 166.6 | MHz  |

|                          |                                                                                                                                                                                                                            | Clock output limit, 3.3V                                                                             | 0.08 (80 kHz) |      | 166.6 | MHz  |

|                          | Industrial Temp                                                                                                                                                                                                            | Clock output limit, 2.5V                                                                             | 0.08 (80 kHz) |      | 150   | MHz  |

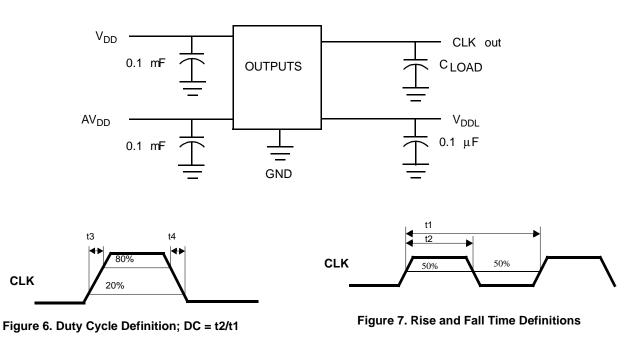

| t2 <sub>LO</sub>         | Output Duty Cycle                                                                                                                                                                                                          | Duty cycle is defined in <i>Figure 6</i> ; t1/t2<br>fOUT < 166 MHz, 50% of V <sub>DD</sub>           | 45            | 50   | 55    | %    |

| t2 <sub>HI</sub>         | Output Duty Cycle                                                                                                                                                                                                          | Duty cycle is defined in <i>Figure 6</i> ; t1/t2<br>fOUT > 166 MHz, 50% of V <sub>DD</sub>           | 40            | 50   | 60    | %    |

| t3 <sub>LO</sub>         |                                                                                                                                                                                                                            | Output clock rise time, 20% – 80% of V <sub>DDL</sub> .<br>Defined in <i>Figure 7</i> .              | 0.6           | 1.2  |       | V/ns |

| t4 <sub>LO</sub>         | Falling Edge Slew<br>Rate (V <sub>DDL</sub> = 2.5V)                                                                                                                                                                        | Output dlock fall time, 80% – 20% of V <sub>DDL</sub> .<br>Defined in <i>Figure 7</i> .              | 0.6           | 1.2  |       | V/ns |

| t3 <sub>HI</sub>         | Rising Edge Slew<br>Rate (V <sub>DDL</sub> = 3.3V)                                                                                                                                                                         | Output dlock rise time, 20% – 80% of V <sub>DD</sub> /V <sub>DDL</sub> . Defined in <i>Figure</i> 7. | 0.8           | 1.4  |       | V/ns |

| t4 <sub>HI</sub>         | Falling Edge Slew<br>Rate (V <sub>DDL</sub> = 3.3V)                                                                                                                                                                        | Output dlock fall time, 80% – 20% of V <sub>DD</sub> /V <sub>DDL</sub> . Defined in <i>Figure</i> 7. | 0.8           | 1.4  |       | V/ns |

| t5 <sup>[8]</sup>        | Skew                                                                                                                                                                                                                       | Output-output skew between related outputs.                                                          |               |      | 250   | ps   |

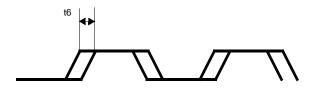

| t6 <sup>[9]</sup>        | Clock Jitter                                                                                                                                                                                                               | Peak-to-peak period jitter                                                                           |               | 250  |       | ps   |

| t10                      | PLL Lock Time                                                                                                                                                                                                              |                                                                                                      |               | 0.30 | 3     | ms   |

#### **Device Characteristics**

| Parameter     | Name             | Value  | Unit        |  |

|---------------|------------------|--------|-------------|--|

| $\theta_{JA}$ | theta JA         | 115    | °C/W        |  |

| Complexity    | Transistor Count | 74,600 | transistors |  |

#### **Ordering Information**

| Ordering Code                 | Package Name                  | Package Type  | Operating Range          | Operating Voltage |

|-------------------------------|-------------------------------|---------------|--------------------------|-------------------|

| CY22150FC                     | Z16                           | 16-lead TSSOP | Commercial (0 to 70°C)   | 3.3V              |

| CY22150FI                     | Z16                           | 16-lead TSSOP | Industrial (-40 to 85°C) | 3.3V              |

| CY22150ZC-xxx <sup>[10]</sup> | Z16                           | 16-lead TSSOP | Commercial (0 to 70°C)   | 3.3V              |

| CY22150ZI-xxx <sup>[10]</sup> | 150ZI-xxx <sup>[10]</sup> Z16 |               | Industrial (-40 to 85°C) | 3.3V              |

| CY3672                        | FTG Development System        | N/A           |                          |                   |

| CY3672ADP000                  | CY22150F Socket               |               |                          |                   |

Notes:

7. 8. 9.

Not 100% tested, guaranteed by design. Skew value guaranteed when outputs are generated from the same divider bank. See Logic Diagram for more information. Jitter measurement will vary. Actual jitter is dependent on XIN jitter and edge rate, number of active outputs, output frequencies, V<sub>DDL</sub>, (2.5V or 3.3V jitter in "PLL-Based Systems: Causes, Effects, and Solutions," available at http://www.cypress.com/clock/appnotes.html, or contact your local Cypress field appli-

acations engineer).

The CY22150ZC-xxx and CY22150ZI-xxx are factory programmed configurations. Factory programming is available for high-volume design opportunities of 100Ku/year or more in production. For more details, contact your local Cypress FAE or Cypress Sales Representative.

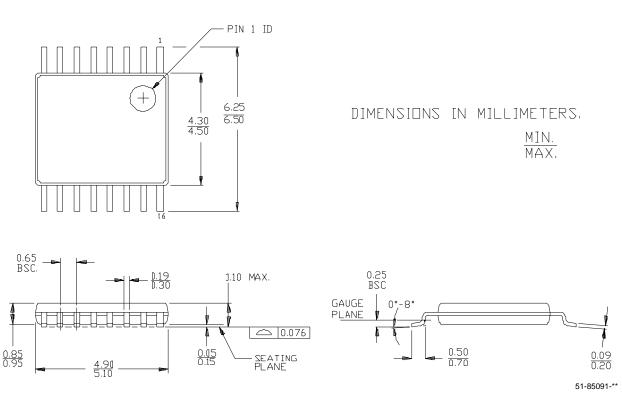

#### Package Diagram

16-lead Thin Shrunk Small Outline Package (4.40 MM Body) Z16

BP Microsystems is a trademark of BP Microsystems. HiLo Systems is a trademark of Hi-Lo Systems, Inc. CyClocks is a trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor des not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor against all charges.

### Document History Page

| Document Title: CY22150 One-PLL General-Purpose Flash-Programmable and 2-Wire Serially-Programmable Clock<br>Generator |  |

|------------------------------------------------------------------------------------------------------------------------|--|

| Document Number: 38-07104                                                                                              |  |

| REV. | ECN<br>NO. | lssue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                          |

|------|------------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 107498     | 08/08/01      | CKN                | New Data Sheet                                                                                                                                                                                                                                                                                 |

| *A   | 110043     | 02/06/02      | CKN                | Preliminary to Final                                                                                                                                                                                                                                                                           |

| *B   | 113514     | 05/01/02      | CKN                | Removed overline on <i>Figure 5</i> Register Address Register Data<br>Changed CLK <sub>HIGH</sub> unit from ns to $\mu$ s in parameter description table<br>Added (sink) to rows 1 and 4 and added (source) to rows 2 and 3 in the DC<br>Electrical Characteristics table ( <i>Figure 16</i> ) |

| *C   | 121868     | 12/14/02      | RBI                | Power-up requirements added to Operating Conditions Information                                                                                                                                                                                                                                |

| *D   | 125453     | 05/19/03      | CKN                | Changed 0 to 1 under 12H/D5 of <i>Table 1</i> and <i>Table 3</i> .<br>Reworded and reformatted Programmable Crystal Input Oscillator Gain<br>Settings text.                                                                                                                                    |