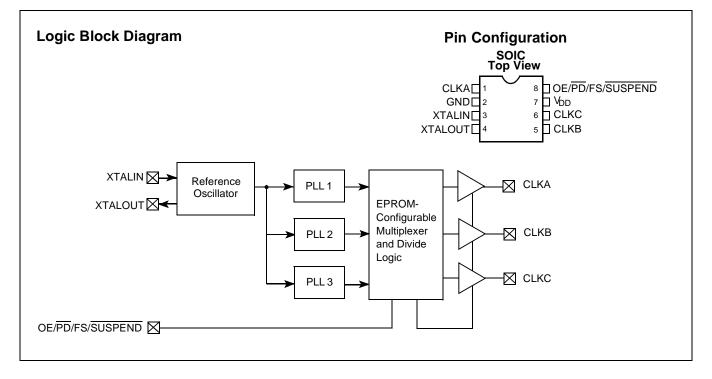

## Three-PLL General-Purpose EPROM-Programmable Clock Generator

#### Features

- Factory-EPROM configurable for quick availability and prototyping

- General purpose clock synthesizer for all applications

such as modems, disk drives, CD-ROM drives, Video CD players, games, set-top boxes, data/telecommunications, etc.

- · Three independent configurable clock outputs

- Outputs ranging from 500 kHz to 100 MHz (5V) and up to 80 MHz for 3.3V operation

- Configurable output control pin (pin 8) can be used as an output enable, power-down, suspend or select line.

- Phase-locked loop oscillator input derived from external crystal (10 MHz to 25 MHz) or external reference clock (1 MHz to 30 MHz)

- 3.3V or 5V operation (factory configured)

- 8-pin 150-mil packaging achieves minimum footprint for space-critical applications

- Sophisticated internal loop filter requires no external components or manufacturing tweaks as commonly required with external filters

#### **Functional Description**

The CY2081 is a general-purpose clock synthesizer designed for use in applications such as modems, disk drives, CD-ROM drives, Video CD players, games, set-top boxes and data/telecommunications. This devices offers three configurable clock outputs in an 8-pin 150-mil SOIC package and can be configured to operate off either a 3.3V or 5V power supply. The on-chip reference oscillator is designed for 10 MHz to 25 MHz crystals. Alternatively, a reference clock between 1 MHz and 30 MHz can be used.

The CY2081 also features an output control pin (pin 8), which can be configured as an output enable, power down, frequency select, or suspend input. This gives the user the ability to three-state the output, power down the device, change the CLKA output frequency during operation, or suspend any of the outputs. Asserting the PD input will result in all the PLLs and the outputs being shut down. The PLLs will have to re-lock when the PD input is deasserted.

The CY2081 outputs three clocks: CLKA, CLKB, and CLKC, whose frequencies can possess any value within the specified range. Additionally, the reference frequency can be obtained on any output. Custom configurations with user-defined features and frequencies can be obtained by filling out the custom configuration form located at the back of this data sheet and contacting your local Cypress representative.

The CY2081 can replace multiple Metal Can Oscillators (MCO) in a synchronous system, providing cost and board space savings to manufacturers. Hence, this device is ideally suited for applications that require multiple, accurate, and stable clocks synthesized from low-cost generators in small packages. A hard disk drive is an example of such an application. In this case, CLKA drives the PLL in the Read Controller, while CLKB and CLKC drive the MCU and associated sequencers.

Consider using the CY2291, CY2292, or CY2907 for applications that require more than three output clocks.

**Cypress Semiconductor Corporation** • Document #: 38-07136 Rev. \*A

3901 North First Street

San Jose

CA 95134

408-943-2600

Revised December 14, 2002

## **Pin Summary**

| Name                     | Number | Description                                                                                                                     |  |

|--------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|--|

| CLKA                     | 1      | Configurable Clock Output                                                                                                       |  |

| GND                      | 2      | Ground                                                                                                                          |  |

| XTALIN <sup>[1]</sup>    | 3      | Reference Crystal Input or External Reference Clock Input                                                                       |  |

| XTALOUT <sup>[1,2]</sup> | 4      | Reference Crystal Feedback                                                                                                      |  |

| CLKB                     | 5      | Configurable Clock Output                                                                                                       |  |

| CLKC                     | 6      | Configurable Clock Output                                                                                                       |  |

| V <sub>DD</sub>          | 7      | Voltage Supply                                                                                                                  |  |

| OE/PD/FS/SUSPEND         | 8      | Output control pin; either active-HIGH Output Enable, active-LOW power down, CLKA Frequency Select, or active-LOW Suspend input |  |

## Maximum Ratings

| (Above which the useful life may be impain lines, not tested.) | ed. For user guide-            |

|----------------------------------------------------------------|--------------------------------|

| Supply Voltage                                                 | –0.5V to +7.0V                 |

| DC Input Voltage                                               | -0.5V to V <sub>DD</sub> +0.5V |

| Storage Temperature            | –65°C to +150°C |

|--------------------------------|-----------------|

| Junction Temperature           | 150°C           |

| Static Discharge Voltage       | >2000V          |

| (per MIL-STD-883, Method 3015) |                 |

## **Operating Conditions**<sup>[3]</sup>

| Parameter        | Description                                                                                    | Min.      | Max.      | Unit |

|------------------|------------------------------------------------------------------------------------------------|-----------|-----------|------|

| V <sub>DD</sub>  | Supply Voltage                                                                                 | 4.5 (3.0) | 5.5 (3.6) | V    |

| T <sub>A</sub>   | Operating Temperature, Ambient                                                                 | 0         | 70        | °C   |

| CL               | Max. Load Capacitance per output                                                               |           | 25 (15)   | pF   |

| f <sub>REF</sub> | External Reference Crystal                                                                     | 10.0      | 25.0      | MHz  |

| f <sub>REF</sub> | External Reference Clock <sup>[4, 5]</sup>                                                     | 1.0       | 30.0      | MHz  |

| t <sub>PU</sub>  | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05      | 50        | ms   |

## **Electrical Characteristics** $V_{DD}$ = 5V (3.3V) ±10%, $T_A$ = 0°C to +70°C

| Parameter        | Description                                             | Conditions                                                                    | Min. | Тур.    | Max.    | Unit |

|------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|------|---------|---------|------|

| V <sub>OH</sub>  | HIGH-Level Output Voltage                               | I <sub>OH</sub> = -4.0 mA                                                     | 2.4  |         |         | V    |

| V <sub>OL</sub>  | LOW-Level Output Voltage                                | I <sub>OL</sub> = 4.0 mA                                                      |      |         | 0.4     | V    |

| V <sub>IH</sub>  | HIGH-Level Input Voltage <sup>[6]</sup>                 | Except Crystal Pins                                                           | 2.0  |         |         | V    |

| V <sub>IL</sub>  | LOW-Level Output Voltage <sup>[6]</sup>                 | Except Crystal Pins                                                           |      |         | 0.8     | V    |

| I <sub>IH</sub>  | Input HIGH Current                                      | $V_{IN} = V_{DD} - 0.5V$                                                      |      | <100    | 150     | μΑ   |

| IIL              | Input LOW Current                                       | V <sub>IN</sub> = 0.5V                                                        |      | <100    | 150     | μΑ   |

| I <sub>OZ</sub>  | Output Leakage Current                                  | Three State Outputs                                                           |      |         | 250     | μΑ   |

| I <sub>DD</sub>  | V <sub>DD</sub> Supply Current <sup>[7]</sup>           | $V_{DD} = V_{DD}$ max. 5V (3.3V) operation, C <sub>L</sub><br>= 25 pF (15 pF) |      | 40 (24) | 60 (40) | mA   |

| I <sub>DDS</sub> | V <sub>DD</sub> Power Supply Current in Power-down Mode | Power-down Active, 5V Operation                                               |      | 100     | 200     | μA   |

#### Electrical Characteristics $V_{DD} = 5V (3.3V) \pm 10\%$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$

|--|

Notes:

1. 2.

For best accuracy, use a parallel-resonant crystal,  $C_L$ =17 pF. Float XTALOUT pin if XTALIN is driven by reference clock (as opposed to an external crystal). Electrical parameters are guaranteed with these operating conditions. Values for 3.3V operation are shown in parentheses. External input reference clock must have a duty cycle between 40% and 60%, measured at  $V_{DD}/2$ . Please refer to application note "Crystal Oscillator Topics" for information on AC-coupling the external input reference clock. Xtal inputs have CMOS thresholds. Load – max, typical configuration, for = 14.318 MHz. Specific configurations may vary. 2. 3. 4. 5.

6. 7. Load = max, typical configuration, f<sub>REF</sub> = 14.318 MHz. Specific configurations may vary.

## Switching Characteristics<sup>[8]</sup>

| Parameter       | Name Description                  |                                                                                             | Min.             | Тур. | Max.              | Unit       |  |

|-----------------|-----------------------------------|---------------------------------------------------------------------------------------------|------------------|------|-------------------|------------|--|

| t <sub>1</sub>  | Output Period                     | Clock output range, 5V operation 10<br>[100 MHz]                                            |                  |      | 2000<br>[500 KHz] | ns         |  |

| t <sub>1</sub>  | Output Period                     | Clock output range, 3.3V operation                                                          | 12.5<br>[80 MHz] |      | 2000<br>[500 KHz] | ns         |  |

| t <sub>1A</sub> | Clock Jitter <sup>[9]</sup>       | Peak-to-peak period jitter,% of clock period $(f_{OUT} \le 4 \text{ MHz})$                  | <0.5             | 1    | %                 |            |  |

| t <sub>1B</sub> | Clock Jitter <sup>[9]</sup>       | Peak-to-peak period jitter<br>(4 MHz ≤ f <sub>OUT</sub> ≤ 16 MHz)                           | <0.7             | 1    | ns                |            |  |

| t <sub>1C</sub> | Clock Jitter <sup>[9]</sup>       | Peak-to-peak period jitter<br>(16 MHz < f <sub>OUT</sub> ≤ 50 MHz)                          |                  | <400 | 500               | ps         |  |

| t <sub>1D</sub> | Clock Jitter <sup>[9]</sup>       | Peak-to-peak period jitter<br>(f <sub>OUT</sub> > 50 MHz)                                   |                  | <250 | 350               | ps         |  |

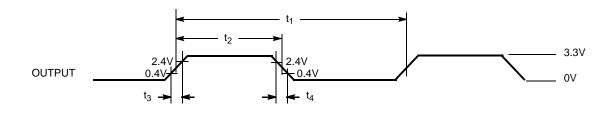

|                 | Output Duty Cycle <sup>[10]</sup> | Duty cycle for outputs, defined as $t_2 \div t_1^{[11]}$ $f_{OUT} > 66.67 \text{ MHz}$      | 40%              | 50%  | 60%               |            |  |

|                 |                                   | Duty cycle for outputs, defined as $t_2 \div t_1^{[11]}$<br>$f_{OUT} \le 66.67 \text{ MHz}$ | 45%              | 50%  | 55%               |            |  |

| t <sub>3</sub>  | Rise time                         | Output clock rise time <sup>[12]</sup> at $C_L=25 \text{ pF}$ (15 pF at 3.3V operation)     |                  | 3    | 5                 | ns         |  |

| t <sub>4</sub>  | Fall time                         | Output clock fall time <sup>[12]</sup> at C <sub>L</sub> =25 pF (15 pF at 3.3V operation)   |                  | 2.5  | 4                 | ns         |  |

| t <sub>5</sub>  | Frequency Slew Rate               | Rate of change of frequency of CLKA 1                                                       |                  | 5    | 40                | MHz/<br>ms |  |

| t <sub>6</sub>  | Power Up Stabiliza-<br>tion Time  | Output clock stable time after power up                                                     |                  | < 25 | 50                | ms         |  |

#### **Switching Waveforms**

#### All Outputs Duty Cycle and Rise/Fall Time

### Switching Waveforms

#### Notes:

- Guaranteed by design, not 100% tested.

- Jitter varies with configuration. All standard configurations sample tested at the factory conform to this limit. For more information on jitter, please refer to the application note: "Jitter in PLL-Based Systems." 9

- Reference Output duty cycle depends on XTALIN duty cycle. 10

- Measured at 1.4V. Measured between 0.4V and 2.4V. 11. 12.

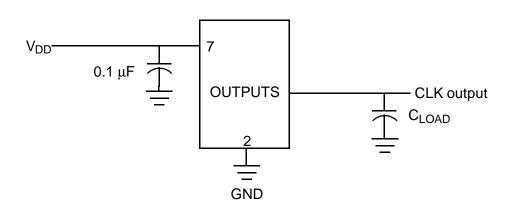

# **Test Circuit**

#### **Customer Configuration Request Procedure**

The CY2081 is programmed at the wafer level, and is therefore only available as a factory programmed device. There is no field programming for the CY2081.

For CY2081 programmed configurations, design opportunities must be 50 Ku per year in production. If the design opportunity does not meet the factory minimums, the design can be implemented using the CY2292 (3-PLLs, 16-SOIC, field programmable), or the CY22381 (3-PLLs, 8-SOIC, field programmable).

For factory programmed samples, all requests must be submitted to your local Cypress FAE or sales representative. The method to use to request factory configurations is:

Use CyClocks software. This software automatically calculates the output frequencies that can be generated by the CY2081 and provides a printout of final pinout. Output frequencies requested will be matched as closely as the internal PLL divider and multiplier options allow. This printout and the design entry file produced by CyClocks (<filename>.ENT) can be submitted (in electronic format) to your local FAE or sales representative. CyClocks software is available free of charge from the Cypress website (http://www.cypress.com) or from your local FAE or sales representative.

Once the custom request has been processed you will receive a part number with a three-digit extension (e.g., CY2081SC-357) specific to the frequencies and pinout of your device. This will be the part number used for samples requests and production orders.

#### **Ordering Information**

| Ordering Code | Package Name | Package Type         | Operating Range                  |

|---------------|--------------|----------------------|----------------------------------|

| CY2081SC-XXX  | S8           | 8-Pin (150-Mil) SOIC | 5.0V, Commercial <sup>[13]</sup> |

| CY2081SL-XXX  | S8           | 8-Pin (150-Mil) SOIC | 3.3V, Commercial <sup>[13]</sup> |

Note:

13. 0°C to +70°C

CyClocks is a trademark of Cypress Semiconductor Corporation.

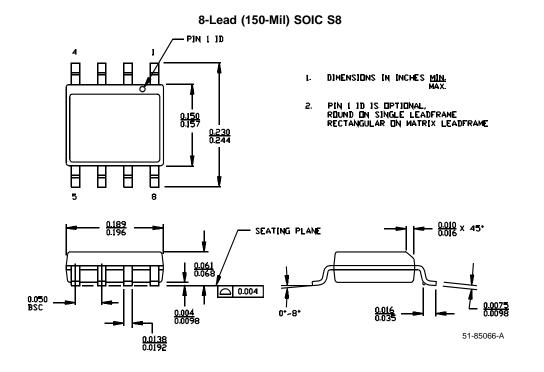

### Package Diagram

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

| Document Title: CY2081 Three-PLL General Purpose EPROM-Programmable Clock Generator<br>Document Number: 38-07136 |         |               |                    |                                                                 |  |  |

|------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------------------------------------------------|--|--|

| REV.                                                                                                             | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                           |  |  |

| **                                                                                                               | 110245  | 10/28/01      | SZV                | Change from Spec number: 38-00463 to 38-07136                   |  |  |

| *A                                                                                                               | 121825  | 12/14/02      | RBI                | Power up requirements added to Operating Conditions Information |  |  |