# CX28394/28395/28398

## Quad/x16/Octal—T1/E1/J1 Framers

The CX28394/28395/28398 is a family of multiple framers for T1/E1/J1 and Integrated Service Digital Network (ISDN) primary rate interfaces operating at 1.544 Mbps or 2.048 Mbps. All framers are totally independent, and each combines a sophisticated framing synchronizer and transmit/receive slip buffers. Operations are controlled through a series of memory-mapped registers accessible via a parallel microprocessor port. Extensive register support is provided for alarm and error monitoring, signaling supervision (including ISDN D-channel/SS7 process), per-channel trunk conditioning, and Facility Data Link (FDL) maintenance. A flexible serial Time Division Multiplexed (TDM) system interface that supports bus rates from 1.536 to 8.192 MHz is featured. Extensive test and diagnostic functions include a full set of loopbacks, Pseudo Random Bit Sequence (PRBS) test pattern generation, Bit Error Rate (BER) meter, and forced error insertion.

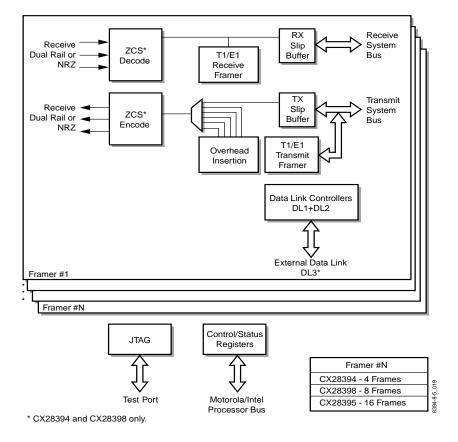

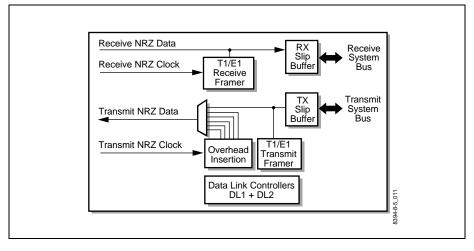

### **Functional Block Diagram**

#### **Distinguishing Features**

- Up to 16 T1/E1/J1 Framers in one package

- Extensive support of various protocols

- T1: SF, ESF, SLC<sup>®</sup>96, T1DM, TTC JT(J1)

- E1: PCM-30, G.704, G.706, G.732, ISDN primary rate (ETS300 011, INS 500)

- Extracts and inserts signaling bits

- Dual HDLC controllers per framer for data link and LAPD/SS7 signaling

- Two-frame transmit and receive PCM slip buffers

- Separate or multiplexed system bus interfaces

- Parallel 8-bit microprocessor port supports Intel or Motorola buses

- BERT generation and counting

- B8ZS/HDB3/Bit 7 zero suppression (CX28394 and CX28398 only)

- Operates from a single +3.3 Vdc ± 5% power supply

- Low-power CMOS technology

#### Applications

- Multiline T1/E1 Channel Service Unit/Data Service Unit (CSU/DSU)

- Digital Access Cross-Connect System (DACS)

- T1/E1 Multiplexer (MUX)

- PBXs and PCM channel bank

- ISDN Primary Rate Access (PRA)

- Frame Relay Switches and Access Devices (FRADS)

- SONET/SDH add/drop multiplexers

- T3/E3 channelized access concentrators

© 1999, 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>TM</sup>, the Conexant C symbol, and "What's Next in Communications Technologies"<sup>TM</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

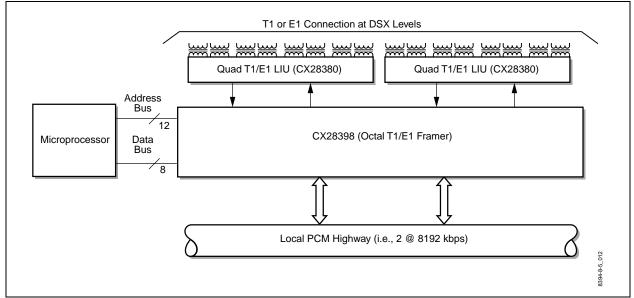

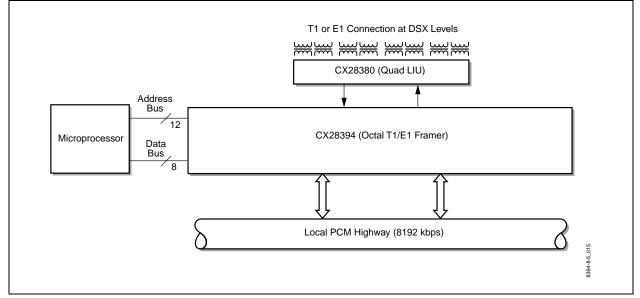

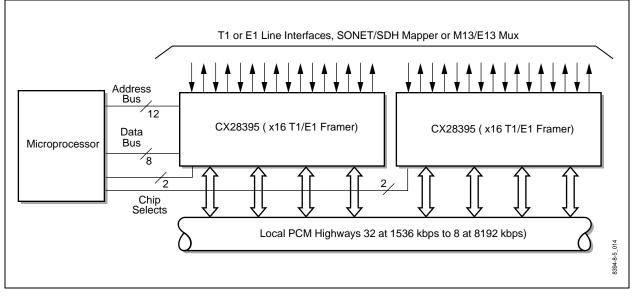

Typical Quad T1/E1 Application

## **Ordering Information**

| Model Number  | Number of Framers | Package                      | Operating Temperature |

|---------------|-------------------|------------------------------|-----------------------|

| CX28394-22    | 4                 | 128-pin TQFP                 | –40 to 85 °C          |

| CX28398-22    | 8                 | 208-pin PQFP                 | –40 to 85 °C          |

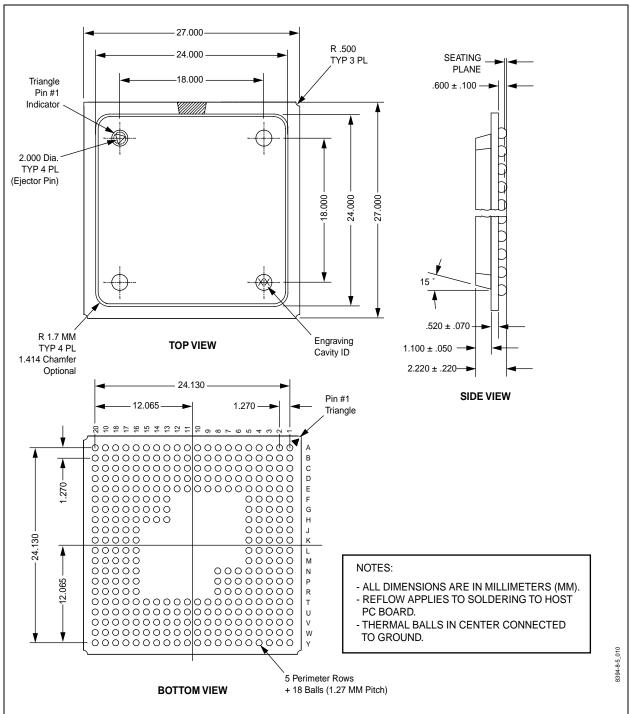

| CX28398-23    | 8                 | 272-pin BGA                  | –40 to 85 °C          |

| CX28395-19    | 16                | 318-pin BGA                  | –40 to 85 °C          |

| CX28395-18    | 16                | 318-pin BGA                  | 0 to 70 °C            |

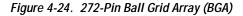

| CX28398-24    | 8                 | 208-pin CABGA                | –40 to 85 °C          |

| BT00-D660-001 | CX2               | 28398/CX28380 Evaluation Moc | lule                  |

### **Detailed Feature Summary**

#### Frame Alignment

- Framed formats:

- Independent transmit and receive framing modes

- T1: FT/SF/ESF/SLC/T1DM/TTC-JT(J1)

- E1: FAS/MFAS/FAS+CAS/MFAS+CAS

- Maximum Average Reframe Time

(MART) less than 50 ms

- Transmitter alignment modes:

- Align to system bus data

- Align to system bus sync

- Align to buffer data (embedded framing)

- Unframed mode

#### Signaling

- T1: 2-, 4-, or 16-state robbed bit ABCD signaling

- E1: Channel Associated Signaling (CAS)

- Common Channel Signaling (CCS) in any time slot

- Per-channel receive signaling stack

- Signaling state change interrupt

- Automatic and manual signaling freeze

- Debounce signaling (2-bit integration)

- UNICODE detection

- Signaling reinsertion on PCM system

bus

- Separate I/O for system bus signaling

- Per-channel transparent

#### Loopbacks

- Remote loopback toward line

Retains BPV transparency (CX28394 and CX28398 only)

- Payload loopback

- Per-channel DS0 remote loopback

- Local loopback towards system

- Framer digital loopback

- Per-channel DS0 local loopback

- Inband loopback code detection/ generation

- Simultaneous local and remote line loopbacks

#### Processor Interface

Parallel 8-bit bus

100054E

- Data strobes (Motorola) or address latch enable (Intel)

- Multiplexed or non-multiplexed address/data bus

- Synchronous or asynchronous data transfers

- Open drain interrupt output with maskable sources

## Out-of-Service Testing and Maintenance

- Pseudo-Random Bit Sequence (PRBS):

- Independent transmit and receive

- 2<sup>11</sup>; 2<sup>15</sup>; 2<sup>20</sup>; 2<sup>23</sup> patterns

- Framed or unframed mode

- Optional 7/14 zero limit

- Bit Error Counter (BERR)

- Single error insertion:

- PRBS error

- Framing error

- CRC error

- BPV/LCV error (CX28394 and CX28398 only)

- COFA error

#### System Bus Interface (SBI)

- System bus data rates:

- 1536 kbps (T1 without F-bits)

- 1544 kbps (T1)

- 2048 kbps (E1)

- 4096 kbps (2E1)

- 8192 kbps (4E1)

- Clock operation at 1x or 2x data rate

- Selectable I/O clock edges

- Master, slave, or mixed bus timing

- Bit and time slot frame sync offsets

- DS0 drop/insert indicators for external mux

- Embedded T1 framing transport per G.802

- Receive and transmit slip buffers

- Bypass, 2-frame, or 64-bit depth

Slip detection with directional status

- Slip buffer phase status

- Per-channel idle code insertion

- Processor accessible data buffers

- Direct connection to upper layer devices:

- Link layer: Bt8474

- ATM layer: CN8228

- Direct connection to physical line interface

- CX28380

- Supported system bus formats:

ATT Concentration Highway

- Interface (CHI) - Multi-Vendor Integration Protocol

- (MVIP)

- Mitel ST-bus

- Separate or internally multiplexed bus modes

Conexant

#### In-Service Performance Monitoring

- One-second timer I/O to synchronize reporting

- Receive error detectors with accumulators:

- Bipolar/Line Code Violations (LCV) (CX28394 and CX28398 only)

- Excessive Zeros (EXZ)

- Loss of Frame (RLOF)

- Framing Errors (FERR)

- CRC Errors (CERR)

- Far End Block Errors (FEBE)

- Severely Errored Frames (SEF)

- Change of Frame Alignment (COFA)

- Transmit error detectors:

- Loss of Frame (TLOF)

- Framing Errors (TFERR)

- Multiframe Errors (TMERR)

- CRC Errors (TCERR)

- Loss of Transmit Clock (TLOC)

- Receive alarm detectors:

- Alarm Indication Signal (AIS)

- Loss of Signal (RLOS)

RAI/Yellow Alarm (YEL)

Multiframe Yellow (MYEL)

- Lost Multiframe Alignment

8:1 dual slope integration

Controlled Frame Slip (RFSLIP)

Uncontrolled Frame Slip (RUSLIP)

Automatic and on-demand transmit

AIS following RLOS and/or TLOC

Automatic AIS clock switching

YEL following 100ms reframe

YEL following FRED

MYEL following MRED

FEBE following CERR

(MRED)

alarms:

timeout

\_

\_

\_

Lost Frame Alignment (FRED)

Carrier Failure Alarm (CFA) with

#### Data Links

- Two full-featured data link controllers (DL1 and DL2):

- 64-octet transmit and receive FIFOs

- HDLC Message Oriented Protocol (MOP)

- Unformatted data transfer

- Unformatted circular buffer

- End of message/buffer interrupt

- Near full/empty interrupts at selected depth

- Access any bit combination in any time slot:

- ISDN D-channels at 16, 32, or 64 kbps

- National/spare bits (SA-bits) in 4 kbps increments

- CCS/SS7

- T1DM R-bits

- Access T1 F-bits in even, odd, or all frames:

- Automatic Performance Report Message (PRM) generator

- ESF Facility Data Link (FDL)

- Unformatted SLC-96 overhead

- Bit-Oriented Protocol (BOP) priority codeword generation and detection

- Separate I/O for external data link (DL3) on CX28394 and CX28398 devices

## **Table of Contents**

| List of                  | Figur               | es        |             | xv                      |  |  |

|--------------------------|---------------------|-----------|-------------|-------------------------|--|--|

| List of                  | List of Tables xvii |           |             |                         |  |  |

| 1.0 Product Description  |                     |           |             |                         |  |  |

|                          | 1.1                 |           |             | 1-1                     |  |  |

|                          |                     |           |             | atalink                 |  |  |

|                          |                     |           |             | IDO                     |  |  |

|                          |                     |           |             | Port                    |  |  |

|                          |                     | 1.1.4     | Iransmit/R  | Peceive Line Interface  |  |  |

|                          | 1.2                 | Pin Assig | nments      |                         |  |  |

| 2.0 Circuit Description. |                     |           |             |                         |  |  |

|                          | 2.1                 | Functiona | al Block Di | agram                   |  |  |

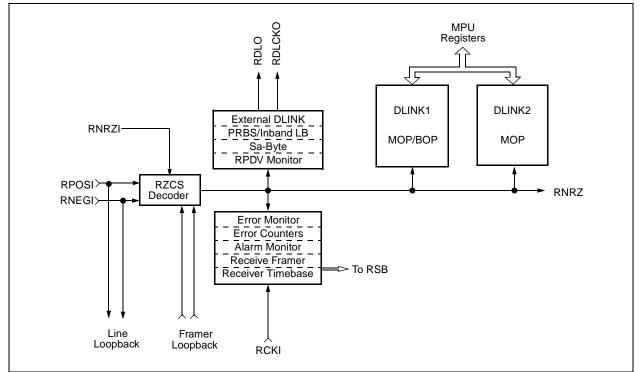

|                          | 2.2                 | Receiver  |             |                         |  |  |

|                          |                     | 2.2.1     | ZCS Decod   | ler                     |  |  |

|                          |                     | 2.2.2     | In-Band Lo  | popback Code Detection  |  |  |

|                          |                     | 2.2.3     | Error Cour  | ters                    |  |  |

|                          |                     | :         | 2.2.3.1     | Frame Bit Error Counter |  |  |

|                          |                     | :         | 2.2.3.2     | CRC Error Counter       |  |  |

|                          |                     | :         | 2.2.3.3     | LCV Error Counter       |  |  |

|                          |                     | :         | 2.2.3.4     | FEBE Counter            |  |  |

|                          |                     | 2.2.4     | Error Moni  | tor                     |  |  |

|                          |                     | :         | 2.2.4.1     | Frame Bit Error         |  |  |

|                          |                     | :         | 2.2.4.2     | MFAS Error              |  |  |

|                          |                     | :         | 2.2.4.3     | CAS Error               |  |  |

|                          |                     | :         | 2.2.4.4     | CRC Error               |  |  |

|                          |                     | :         | 2.2.4.5     | Pulse Density Violation |  |  |

|     | 2.2.5   | Alarm Mo           | nitor                                        | 2-7    |

|-----|---------|--------------------|----------------------------------------------|--------|

|     |         | 2.2.5.1            | Loss of Frame                                | 2-8    |

|     |         | 2.2.5.2            | Loss of Signal                               | 2-8    |

|     |         | 2.2.5.3            | Receive Analog Loss of Signal                | 2-8    |

|     |         | 2.2.5.4            | Alarm Indication Signal                      | 2-8    |

|     |         | 2.2.5.5            | Yellow Alarm                                 | 2-8    |

|     |         | 2.2.5.6            | Multiframe YEL                               | 2-9    |

|     |         | 2.2.5.7            | Severely Errored Frame                       | 2-9    |

|     |         | 2.2.5.8            | Change of Frame Alignment                    | 2-9    |

|     |         | 2.2.5.9            | Receive Multiframe AIS                       | 2-9    |

|     | 2.2.6   | Test Patte         | rn Receiver                                  | 2-9    |

|     | 2.2.7   | Receive F          | raming                                       | . 2-10 |

|     | 2.2.8   | External R         | Receive Data Link (CX28394 and CX28398 Only) | . 2-15 |

|     | 2.2.9   | Sa-Byte R          | leceive Buffers                              | . 2-15 |

|     | 2.2.10  | Receive D          | ata Link                                     | . 2-16 |

|     |         | 2.2.10.1           | Data Link Controllers.                       | . 2-16 |

|     |         | 2.2.10.2           | RBOP Receiver                                | . 2-20 |

| 2.3 | System  | Bus                |                                              | 2-21   |

|     | 2.3.1   |                    | iplexed Mode                                 |        |

|     | 2.3.2   |                    | Multiplexed Mode                             |        |

|     | 2.3.3   |                    | Multiplexed Mode                             |        |

|     | 2.3.4   | <u> </u>           | ystem Bus                                    |        |

|     | 2.011   | 2.3.4.1            |                                              |        |

|     |         | 2.3.4.2            | Slip Buffer                                  |        |

|     |         | 2.3.4.3            | Signaling Buffer                             |        |

|     |         | 2.3.4.4            | Signaling Stack                              |        |

|     |         | 2.3.4.5            | Embedded Framing                             |        |

|     | 2.3.5   |                    | System Bus                                   |        |

|     |         | 2.3.5.1            | Timebase                                     |        |

|     |         | 2.3.5.2            | Slip Buffer                                  | . 2-35 |

|     |         | 2.3.5.3            | Signaling Buffer                             |        |

|     |         | 2.3.5.4            | Transmit Framing                             |        |

|     |         | 2.3.5.5            | Embedded Framing                             |        |

| 2.4 | Transmi | ittor              |                                              |        |

| 2.4 | 2.4.1   |                    | ransmit Data Link (CX28394 and CX28398 Only) |        |

|     | 2.4.1   |                    | Data Links                                   |        |

|     | 2.4.2   | 2.4.2.1            | Data Links Controllers.                      |        |

|     |         |                    |                                              |        |

|     |         | 2.4.2.2<br>2.4.2.3 | Circular Buffer                              |        |

|     |         | 2.4.2.3            | Transmit Data Link FIFO Buffer               |        |

|     |         |                    |                                              |        |

|     |         | 2.4.2.5            | End of Message                               |        |

|     |         | 2.4.2.6            | Programming the Data Link Controller         |        |

|     |         | 2.4.2.7            | PRM Generator                                |        |

|     |         | 2.4.2.8            | TBOP Transceiver                             | . 2-46 |

|     |     | 2.4.3    | Sa-Byte Ov   | verwrite Buffer                | 2-46 |

|-----|-----|----------|--------------|--------------------------------|------|

|     |     | 2.4.4    | Overhead     | Pattern Generation             | 2-47 |

|     |     |          | 2.4.4.1      | Framing Pattern Generation     | 2-47 |

|     |     |          | 2.4.4.2      | Alarm Generation               | 2-47 |

|     |     |          | 2.4.4.3      | CRC Generation                 | 2-49 |

|     |     |          | 2.4.4.4      | Far-End Block Error Generation | 2-49 |

|     |     | 2.4.5    | Test Patter  | rn Generation                  | 2-50 |

|     |     | 2.4.6    | Transmit E   | Error Insertion                | 2-50 |

|     |     | 2.4.7    | In-Band Lo   | oopback Code Generation        | 2-51 |

|     |     | 2.4.8    | ZCS Encod    | der                            | 2-51 |

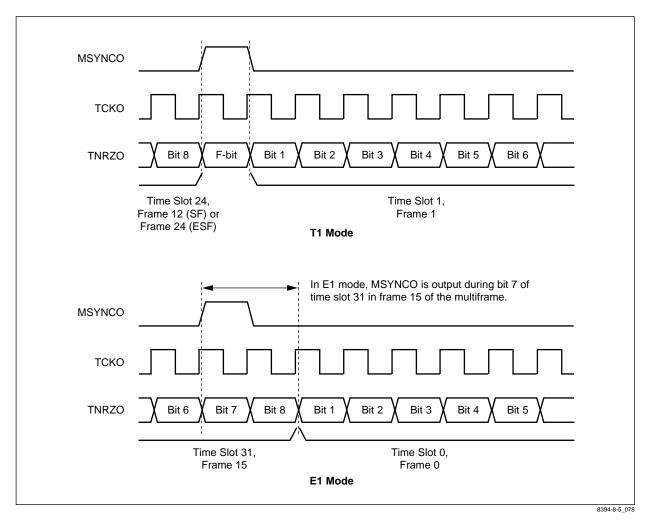

|     | 2.5 | Microp   | rocessor Int | terface                        | 2-55 |

|     |     | 2.5.1    | Address/D    | Data Bus                       | 2-56 |

|     |     | 2.5.2    | Bus Contro   | ol Signals                     | 2-56 |

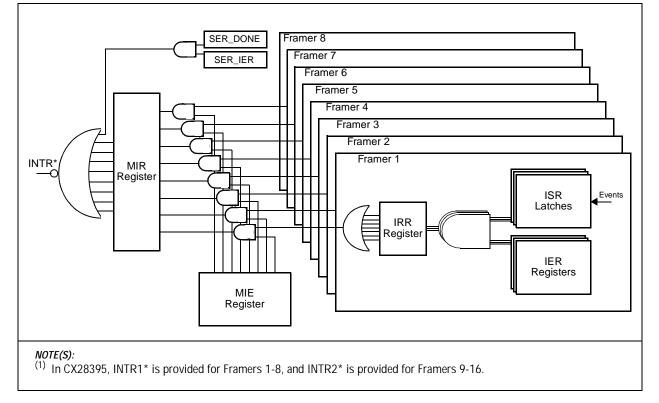

|     |     | 2.5.3    | Interrupt F  | Requests                       | 2-56 |

|     |     | 2.5.4    | Device Res   | set                            | 2-58 |

|     | 2.6 | Loopba   | cks          |                                | 2-59 |

|     |     | 2.6.1    | Remote Li    | ine Loopback                   | 2-59 |

|     |     | 2.6.2    | Remote Pa    | ayload Loopback                | 2-59 |

|     |     | 2.6.3    | Remote Pe    | er-Channel Loopback            | 2-59 |

|     |     | 2.6.4    | Local Fram   | ner Loopback                   | 2-60 |

|     |     | 2.6.5    | Local Per-   | Channel Loopback               | 2-60 |

|     | 2.7 | Serial I | nterface     |                                | 2-61 |

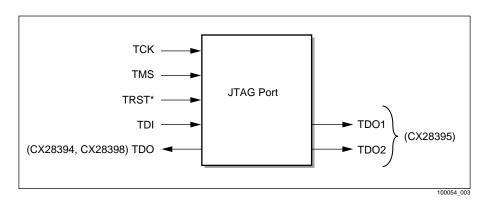

|     | 2.8 | Joint Te | est Access G | Group                          | 2-62 |

|     |     | 2.8.1    |              | 'ns                            |      |

|     |     | 2.8.2    |              | entification Register          |      |

| 3.0 | Dog | ictore   |              |                                | 0.1  |

| 3.0 |     |          |              |                                |      |

|     | 3.1 |          |              |                                |      |

|     | 3.2 | Global   | Control and  | Status Registers               | 3-8  |

|     |     |          | 000—Dev      | rice Identification (DID)      | 3-8  |

|     |     |          | 080—Fran     | mer Control Register (FCR)     | 3-8  |

|     |     |          | 081—Mas      | ster Interrupt Request (MIR)   | 3-9  |

|     |     |          | 082—Mas      | ster Interrupt Enable (MIE)    | 3-10 |

|     |     |          | 083—Test     | t Configuration (TEST)         | 3-10 |

|     | 3.3 | Primary  | y Control an | nd Status Register             | 3-11 |

|     |     |          | 001—Prin     | nary Control Register (CR0)    | 3-11 |

|     | 3.4 | Interrup | ot Control R | egister                        | 3-13 |

|     |     |          |              | errupt Request Register (IRR)  |      |

| 3.5 | Interrupt Status Registers                             |

|-----|--------------------------------------------------------|

|     | 004—Alarm 1 Interrupt Status (ISR7)                    |

|     | 005—Alarm 2 Interrupt Status (ISR6)                    |

|     | 006—Error Interrupt Status (ISR5)                      |

|     | 007—Counter Overflow Interrupt Status (ISR4)           |

|     | 008—Timer Interrupt Status (ISR3) 3-19                 |

|     | 009—Data Link 1 Interrupt Status (ISR2)                |

|     | 00A—Data Link 2 Interrupt Status (ISR1)                |

|     | 00B—Pattern Interrupt Status (ISR0)                    |

| 3.6 | Interrupt Enable Registers                             |

|     | 00C—Alarm 1 Interrupt Enable Register (IER7)           |

|     | 00D—Alarm 2 Interrupt Enable Register (IER6)           |

|     | 00E—Error Interrupt Enable Register (IER5)             |

|     | 00F—Count Overflow Interrupt Enable Register (IER4)    |

|     | 010—Timer Interrupt Enable Register (IER3) 3-25        |

|     | 011—Data Link 1 Interrupt Enable Register (IER2)       |

|     | 012—Data Link 2 Interrupt Enable Register (IER1) 3-26  |

|     | 013—Pattern Interrupt Enable Register (IER0) 3-26      |

| 3.7 | Primary Control and Status Registers 3-27              |

|     | 014—Loopback Configuration Register (LOOP)             |

|     | 015—External Data Link Time Slot (DL3_TS)              |

|     | 016—External Data Link Bit (DL3_BIT)                   |

|     | 017—Offline Framer Status (FSTAT)                      |

|     | 018—Programmable Input/Output (PIO)                    |

|     | 019—Programmable Output Enable (POE) 3-33              |

|     | 01A—Clock Input Mux (CMUX)                             |

|     | 020—Receive Alarm Configuration (RAC)                  |

|     | 021—Receive Line Code Status (RSTAT)                   |

| 3.8 | Serial Interface Registers                             |

|     | 022—Serial Control (SER_CTL) 3-36                      |

|     | 023—Serial Data (SER_DAT) 3-36                         |

|     | 024—Serial Status (SER_STAT) 3-36                      |

|     | 025—Serial Configuration (SER_CONFIG)                  |

|     | 026—RAM Test                                           |

| 3.9 | Receiver Registers                                     |

|     | 040—Receiver Configuration (RCR0)                      |

|     | 041—Receive Test Pattern Configuration (RPATT)         |

|     | 042—Receive Loopback Code Detector Configuration (RLB) |

|     | 043—Loopback Activate Code Pattern (LBA)               |

|     | 044—Loopback Deactivate Code Pattern (LBD)             |

|     | 045—Receive Alarm Signal Configuration (RALM)          |

|     | 046—Alarm/Error/Counter Latch Configuration (LATCH)    |

|     | 047—Alarm 1 Status (ALM1)                              |

|     | 048—Alarm 2 Status (ALM2)                              |

|     | 049—Alarm 3 Status (ALM3)                              |

| 3.10 | Performance Monitoring Registers                                                       | 3-49         |

|------|----------------------------------------------------------------------------------------|--------------|

|      | 050—Framing Bit Error Counter LSB (FERR)                                               | 3-49         |

|      | 051—Framing Bit Error Counter MSB (FERR)                                               | 3-49         |

|      | 052—CRC Error Counter LSB (CERR)                                                       | 3-49         |

|      | 053—CRC Error Counter MSB (CERR)                                                       | 3-49         |

|      | 054—Line Code Violation Counter LSB (LCV)                                              | 3-50         |

|      | 055—Line Code Violation Counter MSB (LCV)                                              | 3-50         |

|      | 056—Far End Block Error Counter LSB (FEBE)                                             | 3-50         |

|      | 057—Far End Block Error Counter MSB (FEBE)                                             | 3-50         |

|      | 058—PRBS Bit Error Counter LSB (BERR)                                                  | 3-50         |

|      | 059—PRBS Bit Error Counter MSB (BERR)                                                  | 3-51         |

|      | 05A—SEF/FRED/COFA Alarm Counter (AERR)                                                 | 3-51         |

| 11   | Receive Sa-Byte Buffers                                                                | 3-52         |

|      | 05B—Receive Sa4 Byte Buffer (RSA4)                                                     | 3-52         |

|      | 05C—Receive Sa5 Byte Buffer (RSA5)                                                     | 3-52         |

|      | 05D—Receive Sa6 Byte Buffer (RSA6)                                                     | 3-53         |

|      | 05E—Receive Sa7 Byte Buffer (RSA7)                                                     |              |

|      | 05F—Receive Sa8 Byte Buffer (RSA8)                                                     | 3-54         |

| 12   | Transmitter Registers                                                                  | 3-55         |

|      | 070—Transmit Framer Configuration (TCR0)                                               | 3-55         |

|      | 071—Transmitter Configuration (TCR1)                                                   |              |

|      | 072—Transmit Frame Format (TFRM).                                                      |              |

|      | 073—Transmit Error Insert (TERROR)                                                     | 3-62         |

|      | 074—Transmit Manual Sa-Byte/FEBE Configuration (TMAN)                                  |              |

|      | 076—Transmit Test Pattern Configuration (TPATT)                                        |              |

|      | 077—Transmit Inband Loopback Code Configuration (TLB)                                  | 3-66         |

|      | 078—Transmit Inband Loopback Code Pattern (LBP)                                        | 3-67         |

| .13  | Transmit Sa-Byte Buffers.                                                              | 3-68         |

|      | 07B—Transmit Sa4 Byte Buffer (TSA4)                                                    | 3-68         |

|      | 07C—Transmit Sa5 Byte Buffer (TSA5)                                                    | 3-68         |

|      | 07D—Transmit Sa6 Byte Buffer (TSA6)                                                    | 3-69         |

|      | 07E—Transmit Sa7 Byte Buffer (TSA7)                                                    | 3-69         |

|      | 07F—Transmit Sa8 Byte Buffer (TSA8)                                                    |              |

|      |                                                                                        |              |

| .14  | Bit-Oriented Protocol Registers                                                        | 3-71         |

| .14  | Bit-Oriented Protocol Registers.           0A0—Bit Oriented Protocol Transceiver (BOP) |              |

| .14  |                                                                                        | 3-71         |

| 14   | 0A0—Bit Oriented Protocol Transceiver (BOP)                                            | 3-71<br>3-73 |

| 3.15 | Data Link Registers.                                       | 3-75  |

|------|------------------------------------------------------------|-------|

|      | 0A4—DL1 Time Slot Enable (DL1_TS)                          | 3-75  |

|      | 0A5—DL1 Bit Enable (DL1_BIT)                               | 3-76  |

|      | 0A6—DL1 Control (DL1_CTL)                                  | 3-76  |

|      | 0A7—RDL #1 FIFO Fill Control (RDL1_FFC)                    | 3-77  |

|      | 0A8—Receive Data Link FIFO #1 (RDL1)                       | 3-79  |

|      | 0A9—RDL #1 Status (RDL1_STAT)                              | 3-80  |

|      | 0AA—Performance Report Message (PRM)                       | 3-81  |

|      | 0AB—TDL #1 FIFO Empty Control (TDL1_FEC)                   | 3-82  |

|      | OAC—TDL #1 End Of Message Control (TDL1_EOM)               | 3-83  |

|      | OAD—Transmit Data Link FIFO #1 (TDL1)                      | 3-83  |

|      | 0AE—TDL #1 Status (TDL1_STAT)                              | 3-83  |

|      | OAF—DL2 Time Slot Enable (DL2_TS)                          | 3-84  |

|      | 0B0—DL2 Bit Enable (DL2_BIT)                               | 3-85  |

|      | 0B1—DL2 Control (DL2_CTL)                                  | 3-85  |

|      | 0B2—RDL #2 FIFO Fill Control (RDL2_FFC)                    | 3-87  |

|      | 0B3—Receive Data Link FIFO #2 (RDL2)                       | 3-88  |

|      | 0B4—RDL #2 Status (RDL2_STAT)                              |       |

|      | 0B6—TDL #2 FIFO Empty Control (TDL2_FEC)                   | 3-90  |

|      | 0B7—TDL #2 End Of Message Control (TDL2_EOM)               |       |

|      | 0B8—Transmit Data Link FIFO #2 (TDL2)                      | 3-91  |

|      | 0B9—TDL #2 Status (TDL2_STAT)                              | 3-91  |

|      | OBA—DLINK Test Configuration (DL_TEST1)                    | 3-92  |

|      | OBB—DLINK Test Status (DL_TEST2)                           | 3-92  |

|      | OBC—DLINK Test Status (DL_TEST3)                           |       |

|      | OBD—DLINK Test Control #1 or Configuration #2 (DL_TEST4)   |       |

|      | OBE—DLINK Test Control #2 or Configuration #2 (DL_TEST5)   | 3-93  |

| 3.16 | System Bus Registers                                       | 3-94  |

|      | 0D0—System Bus Interface Configuration (SBI_CR)            | 3-94  |

|      | 0D1—Receive System Bus Configuration (RSB_CR)              | 3-96  |

|      | 0D2—RSB Sync Bit Offset (RSYNC_BIT)                        | 3-97  |

|      | 0D3—RSB Sync Time Slot Offset (RSYNC_TS)                   | 3-98  |

|      | 0D4—Transmit System Bus Configuration (TSB_CR)             | 3-99  |

|      | 0D5—TSB Sync Bit Offset (TSYNC_BIT)                        |       |

|      | 0D6—TSB Sync Time Slot Offset (TSYNC_TS)                   |       |

|      | 0D7—Receive Signaling Configuration (RSIG_CR)              | 3-102 |

|      | 0D8—Signaling Reinsertion Frame Offset (RSYNC_FRM)         |       |

|      | 0D9—Slip Buffer Status (SSTAT)                             |       |

|      | 0DA—Receive Signaling Stack (STACK)                        |       |

|      | ODB—RSLIP Phase Status (RPHASE)                            |       |

|      | ODC—TSLIP Phase Status (TPHASE)                            |       |

|      | ODD—RAM Parity Status (PERR)                               |       |

|      | 0E0–0FF—System Bus Per-Channel Control (SBCn; n = 0 to 31) |       |

|      | 100–11F—Transmit Per-Channel Control (TPCn; n = 0 to 31)   |       |

|      | 120–13F—Transmit Signaling Buffer (TSIGn; n = 0 to 31)     | 3-112 |

|       |             | 140–15F—Transmit PCM Slip Buffer (TSLIP_LOn; n = 0 to 31) |

|-------|-------------|-----------------------------------------------------------|

|       |             | 160–17F—Transmit PCM Slip Buffer (TSLIP_HIn; n = 0 to 31) |

|       |             | 180–19F—Receive Per-Channel Control (RPCn; n = 0 to 31)   |

|       |             | 1A0–1BF—Receive Signaling Buffer (RSIGn; n = 0 to 31)     |

|       |             | 1E0–1FF—Receive PCM Slip Buffer (RSLIP_HIn; n = 0 to 31)  |

|       | 3.17        | Register Summary                                          |

| 4.0   | Elec        | trical/Mechanical Specifications                          |

|       | 4.1         | Absolute Maximum Ratings 4-1                              |

|       | 4.2         | Recommended Operating Conditions 4-2                      |

|       | 4.3         | Electrical Characteristics                                |

|       | 4.4         | AC Characteristics. 4-4                                   |

|       | 4.5         | MPU Interface Timing                                      |

|       | 4.6         | System Bus Interface (SBI) Timing                         |

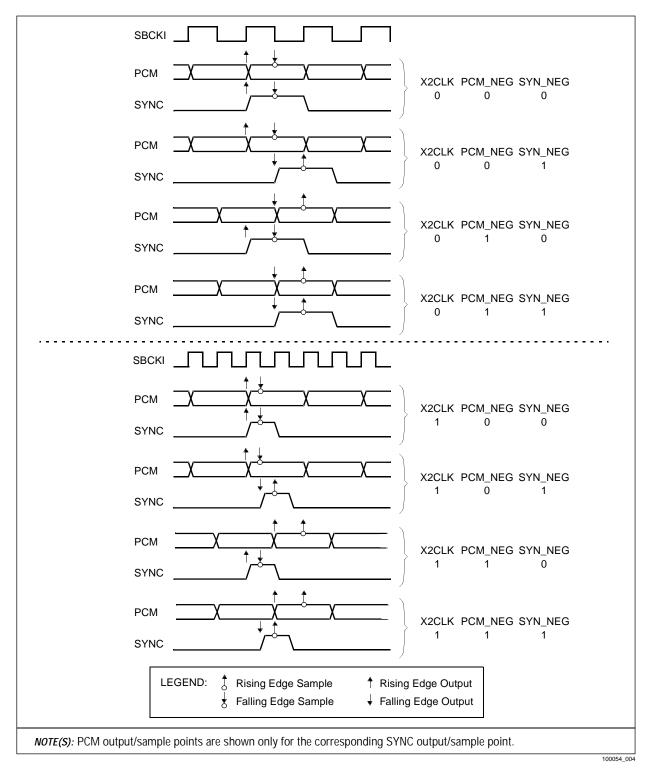

|       | 4.7         | JTAG Interface Timing                                     |

|       | 4.8         | Mechanical Specifications                                 |

| Appen | dix A       | A-1                                                       |

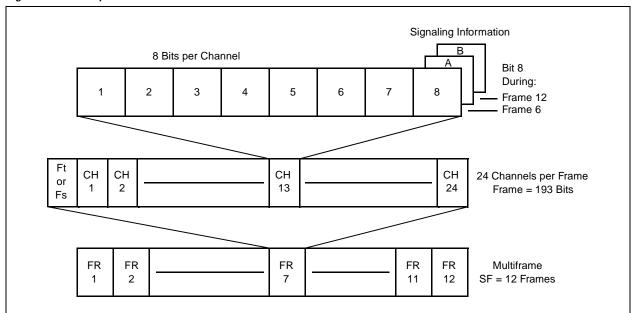

|       | <b>A</b> .1 | Superframe Format (SF) A-1                                |

|       | A.2         | T1DM Format                                               |

|       | A.3         | SLC 96 Format (SLC)                                       |

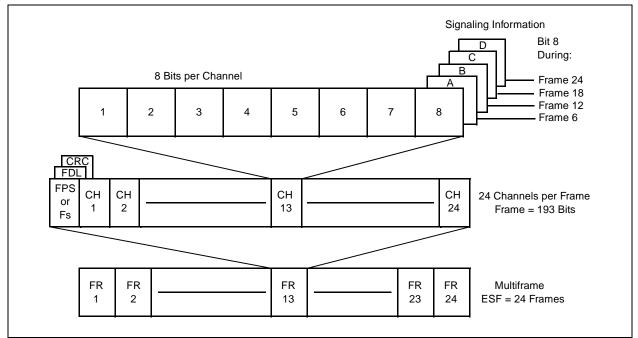

|       | A.4         | Extended Superframe Format (ESF) A-5                      |

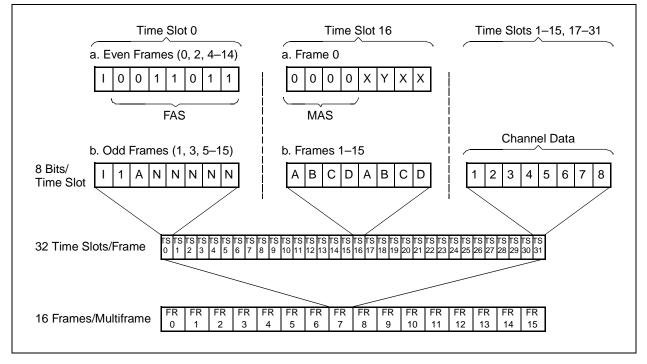

|       | A.5         | E1 Frame Format A-8                                       |

|       | A.6         | IRSM CEPT Frame Format. A-10                              |

| Appen | dix B       |                                                           |

|       | <b>B</b> .1 | Applicable Standards                                      |

| Appen | dix C       | C-1                                                       |

|       | C.1         | System Bus Compatibility                                  |

|       | 0.1         | C.1.1 AT&T Concentration Highway Interface (CHI):         |

|       |             | C.1.2 CHI Programming Options: C-2                        |

| Appen | dix D       | D-1                                                       |

|       | D.1         | Notation and Acronyms                                     |

|       |             | D.1.1 Arithmetic Notation D-1                             |

|       | D.2         | Acronyms and Abbreviations D-2                            |

| Appen | dix E       | E-1                                                       |

|       | E.1         | Revision History E-1                                      |

## List of Figures

| Figure 1-1.  | CX28395 Functional Block Diagram 1-2                                |

|--------------|---------------------------------------------------------------------|

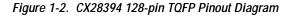

| Figure 1-2.  | CX28394 128-pin TQFP Pinout Diagram 1-4                             |

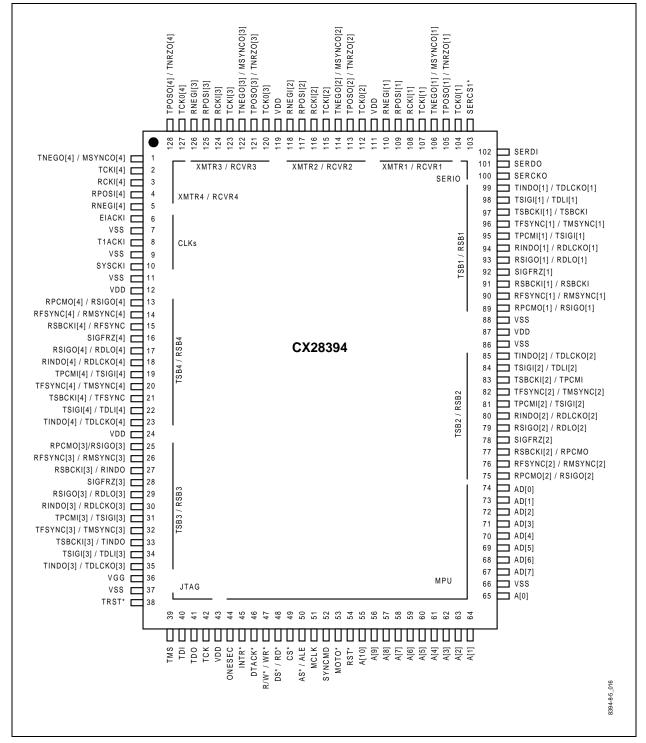

| Figure 1-3.  | CX28395 318-pin BGA Pinout Diagram 1-5                              |

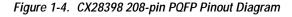

| Figure 1-4.  | CX28398 208-pin PQFP Pinout Diagram 1-6                             |

| Figure 1-5.  | CX28398 208-pin CABGA Pinout Diagram 1-7                            |

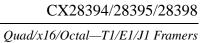

| Figure 1-6.  | CX28398 272-pin BGA Pinout Diagram 1-8                              |

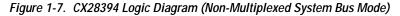

| Figure 1-7.  | CX28394 Logic Diagram (Non-Multiplexed System Bus Mode)             |

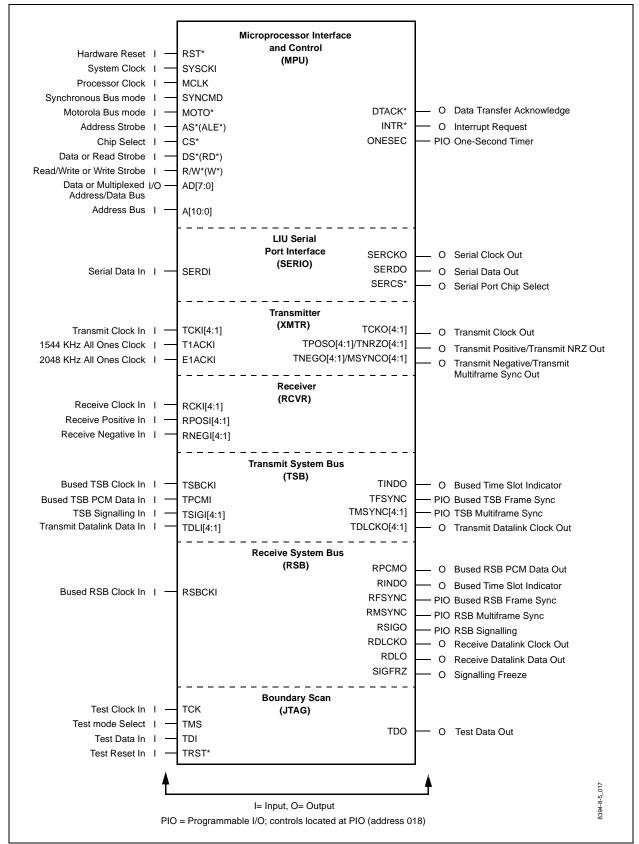

| Figure 1-8.  | CX28394 Logic Diagram (Multiplexed System Bus Mode) 1-26            |

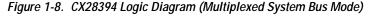

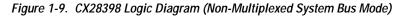

| Figure 1-9.  | CX28398 Logic Diagram (Non-Multiplexed System Bus Mode) 1-27        |

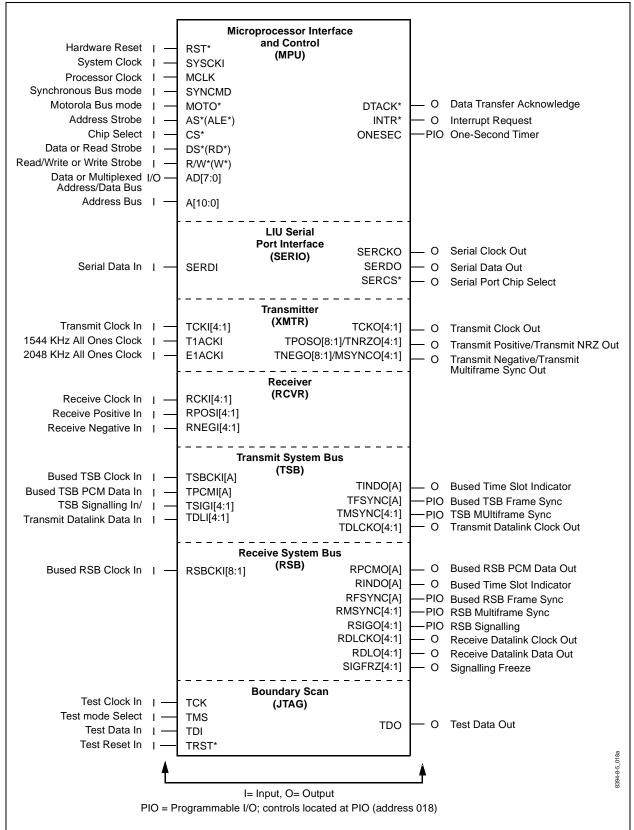

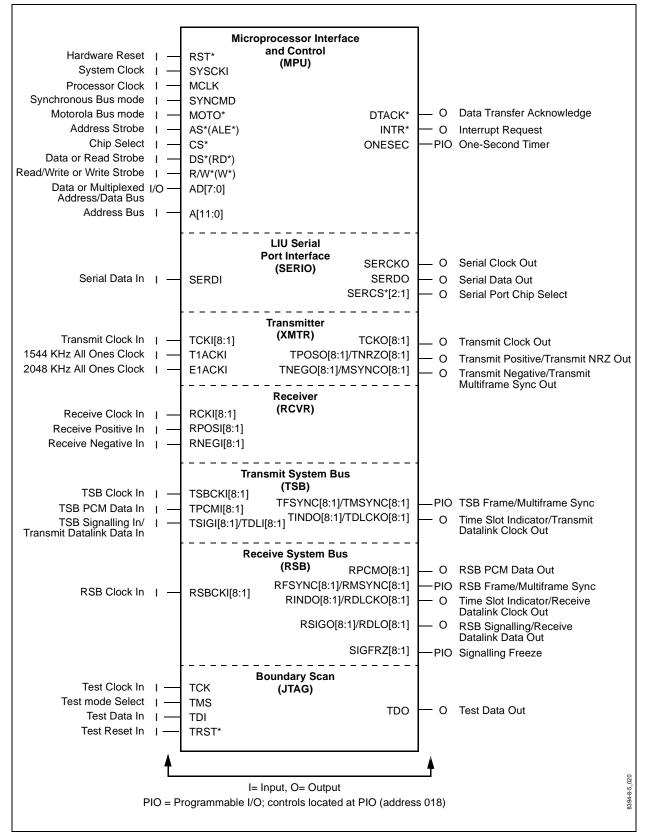

| Figure 1-10. | CX28398 Logic Diagram (Multiplexed System Bus Mode) 1-28            |

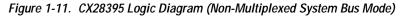

| Figure 1-11. | CX28395 Logic Diagram (Non-Multiplexed System Bus Mode) 1-29        |

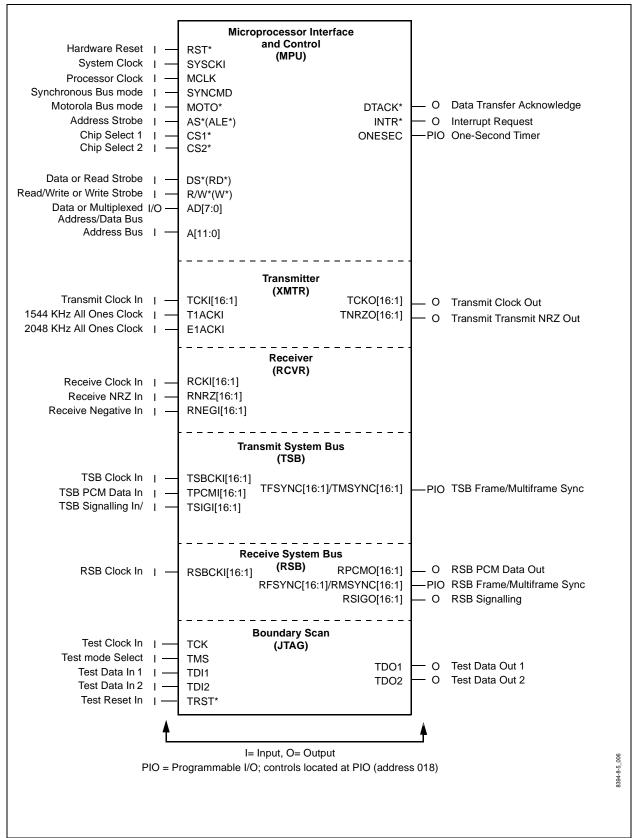

| Figure 1-12. | CX28395 Logic Diagram (Multiplexed System Bus Mode)                 |

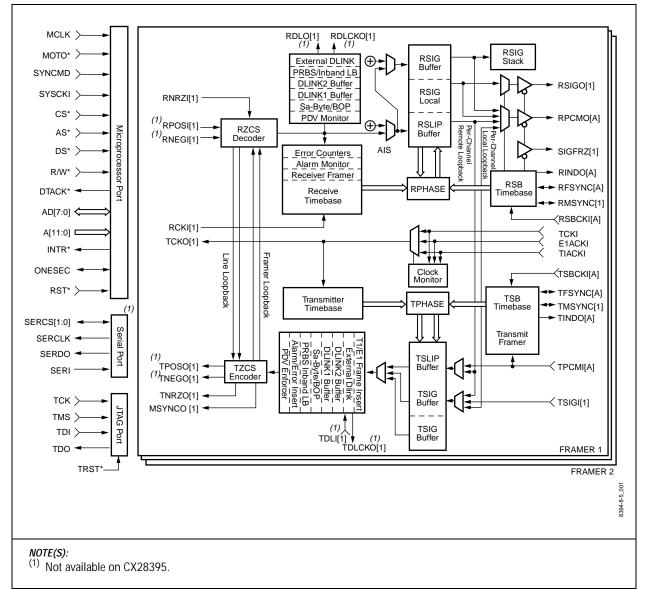

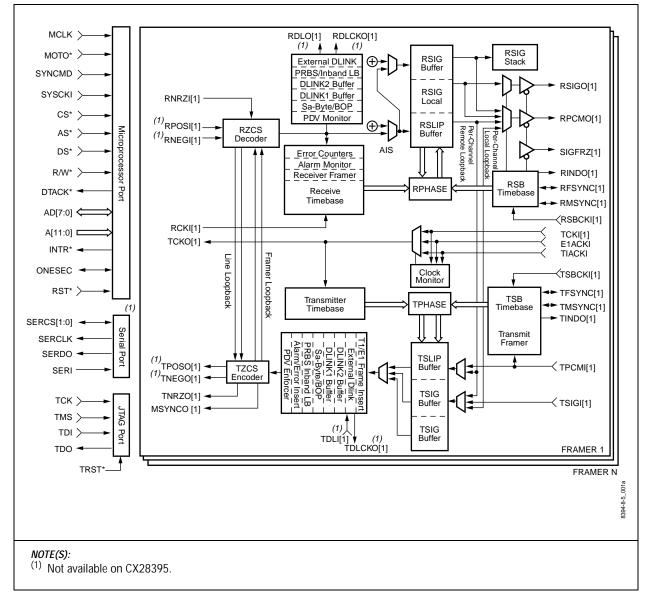

| Figure 2-1.  | Detailed Framer Block Diagram (Multiplexed System Bus Mode) 2-2     |

| Figure 2-2.  | Detailed Framer Block Diagram (Non-multiplexed System Bus Mode) 2-3 |

| Figure 2-3.  | RCVR Diagram 2-4                                                    |

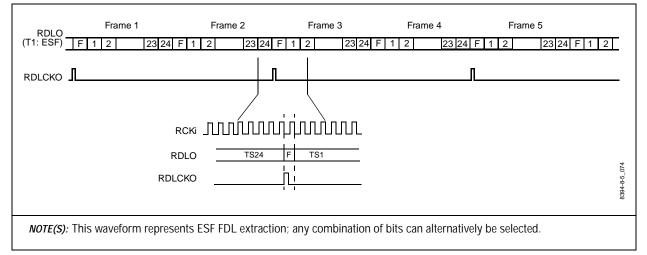

| Figure 2-4.  | Receive External Data Link Waveforms 2-15                           |

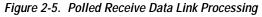

| Figure 2-5.  | Polled Receive Data Link Processing                                 |

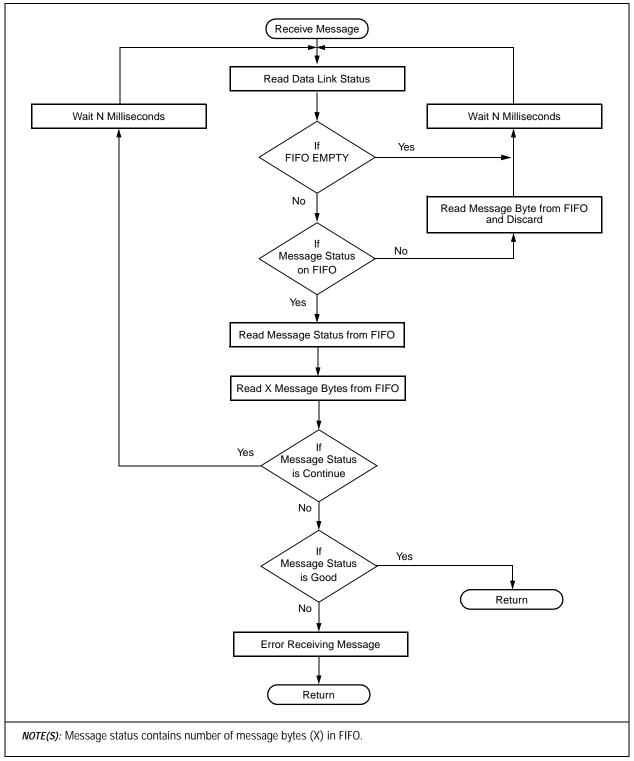

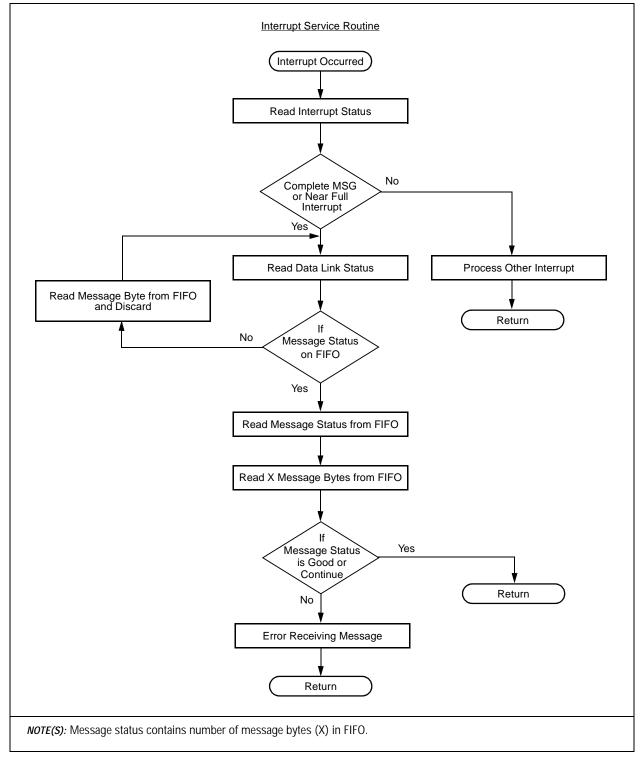

| Figure 2-6.  | Interrupt-Driven Receive Data Link Processing 2-19                  |

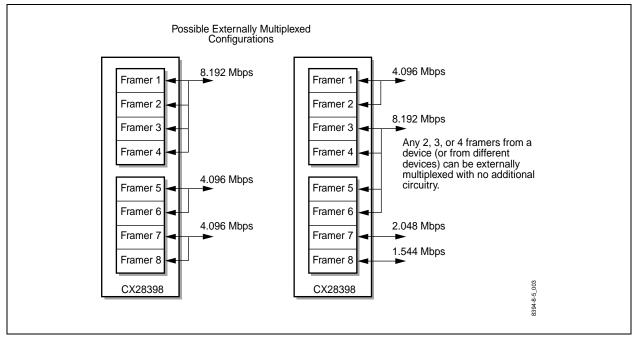

| Figure 2-7.  | Externally Multiplexed Configuration Examples 2-22                  |

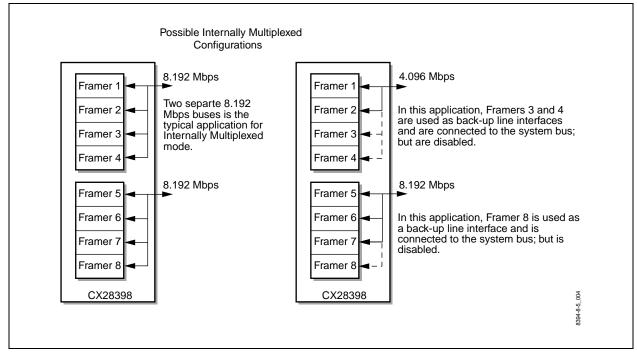

| Figure 2-8.  | Internally Multiplexed Configuration Examples 2-24                  |

| Figure 2-9.  | RSB Waveforms         2-25                                          |

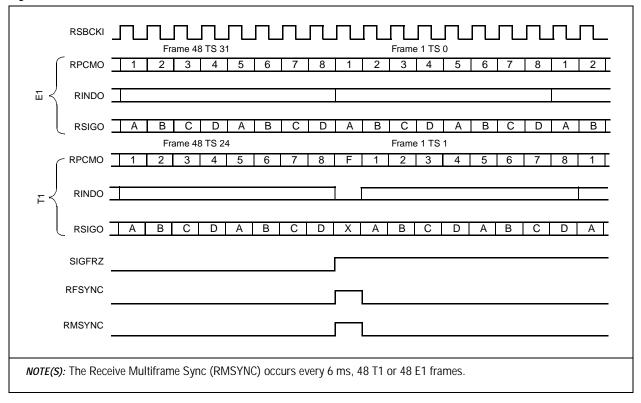

| Figure 2-10. | RSB 4096K Bus Mode Time Slot Interleaving 2-26                      |

| Figure 2-11. | RSB 8192K Bus Mode Time Slot Interleaving 2-26                      |

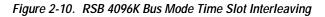

| Figure 2-12. | RSB Diagram                                                         |

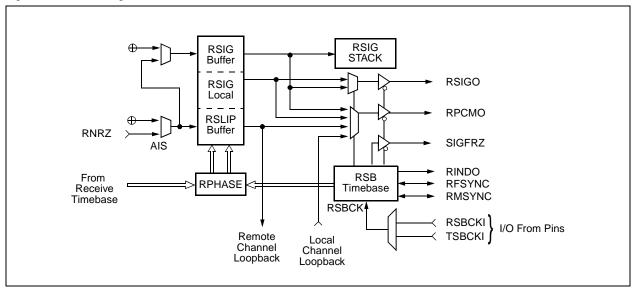

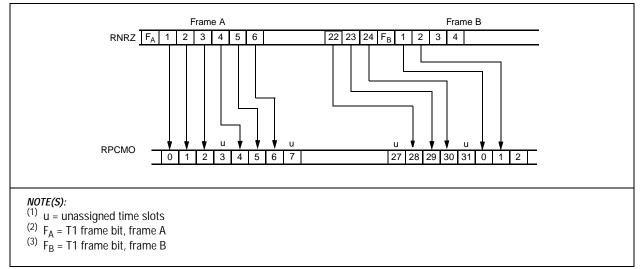

| Figure 2-13. | T1 Line to E1 System Bus Time Slot Mapping                          |

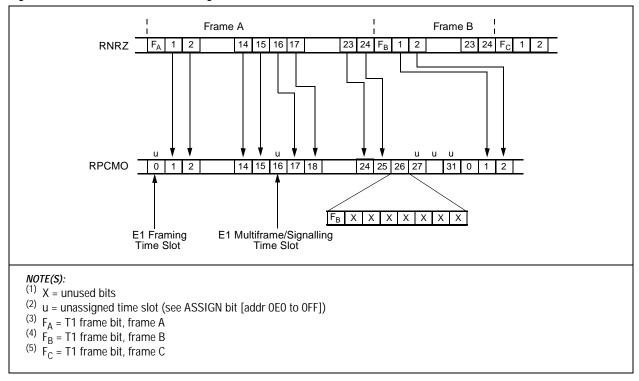

| Figure 2-14. | G.802 Embedded Framing                                              |

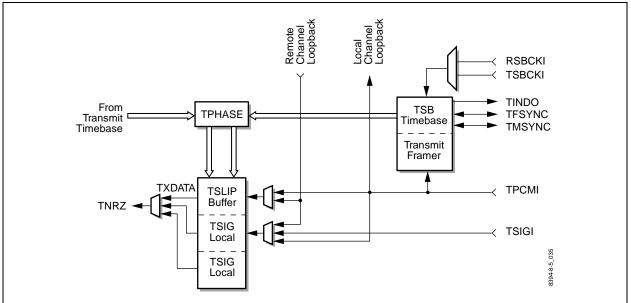

| Figure 2-15. | TSB Interface Block Diagram                                         |

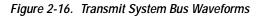

| Figure 2-16. | Transmit System Bus Waveforms    2-33                               |

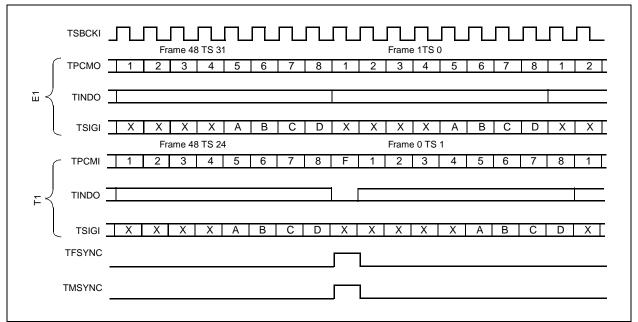

| Figure 2-17. | TSB 4096K Bus Mode Time Slot Interleaving 2-34                      |

| Figure 2-18. | TSB 8192K Bus Mode Time Slot Interleaving 2-34                      |

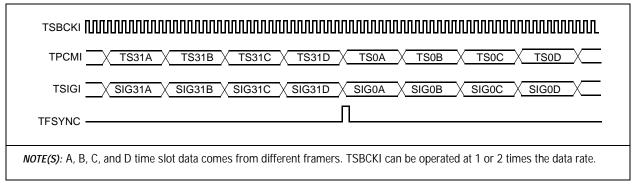

| Figure 2-19. | Transmit Framing and Timebase Alignment Options                     |

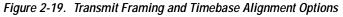

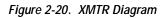

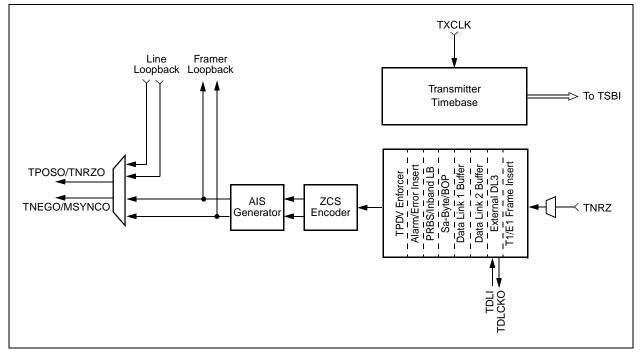

| Figure 2-20. | XMTR Diagram         2-40                                           |

| Figure 2-21. | Transmit External Data Link Waveforms 2-41                          |

| Figure 2-22. | Polled Transmit Data Link Processing                                |

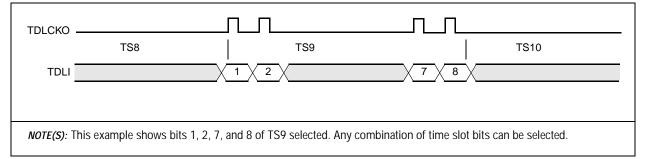

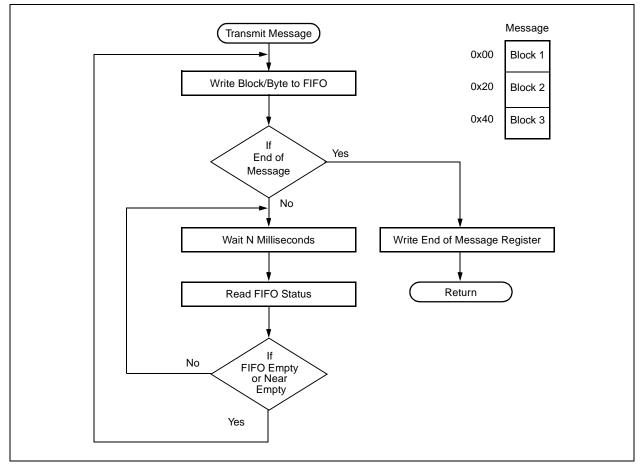

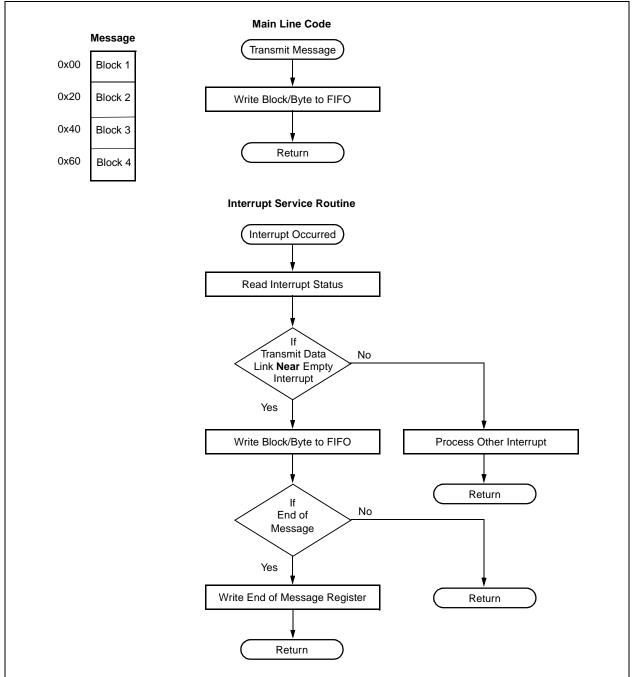

| Figure 2-23. | Interrupt-Driven Transmit Data Link Processing                      |

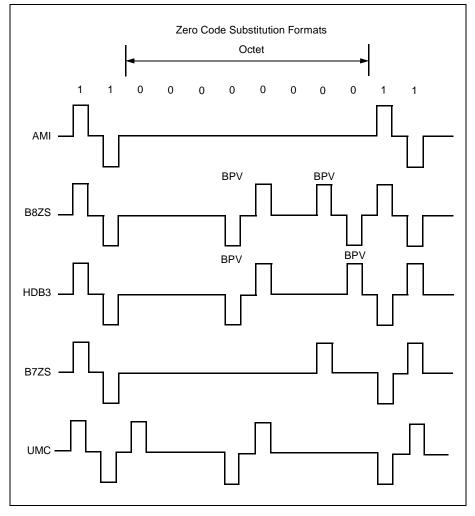

| Figure 2-24. | Zero Code Substitution Formats 2-52                                 |

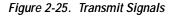

| Figure 2-25. | Transmit Signals                                                    |

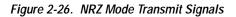

| Figure 2-26. | NRZ Mode Transmit Signals                                           |

| Figure 2-27. | Microprocessor Interface Block Diagram 2-55                         |

| Figure 2-28. | Interrupt Generation Block Diagram                                         |

|--------------|----------------------------------------------------------------------------|

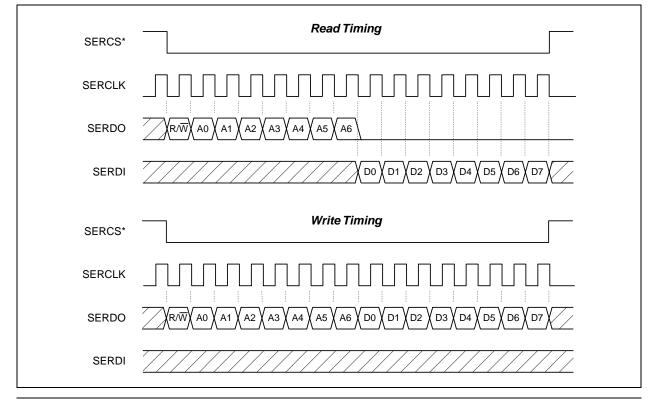

| Figure 2-29. | Serial Interface Timing Diagram                                            |

| Figure 2-30. | Test Access Port (TAP) Diagram    2-62                                     |

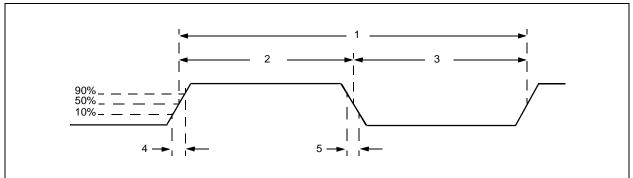

| Figure 4-1.  | Minimum Clock Pulse Widths                                                 |

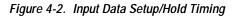

| Figure 4-2.  | Input Data Setup/Hold Timing 4-7                                           |

| Figure 4-3.  | Output Data Delay Timing 4-7                                               |

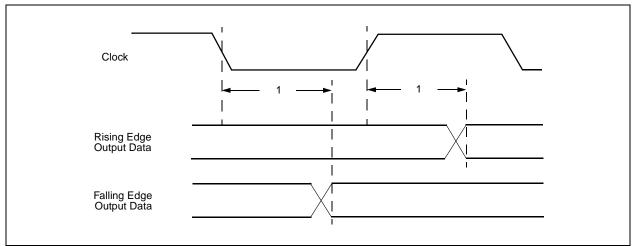

| Figure 4-4.  | One-Second Input/Output Timing 4-7                                         |

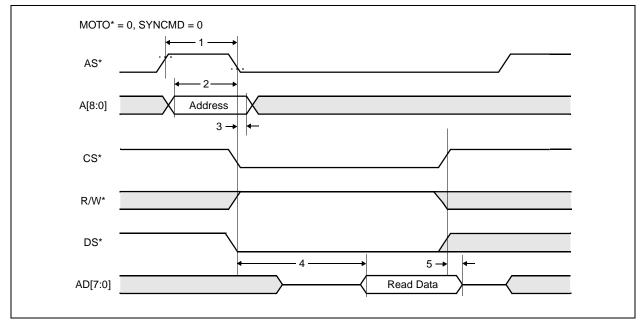

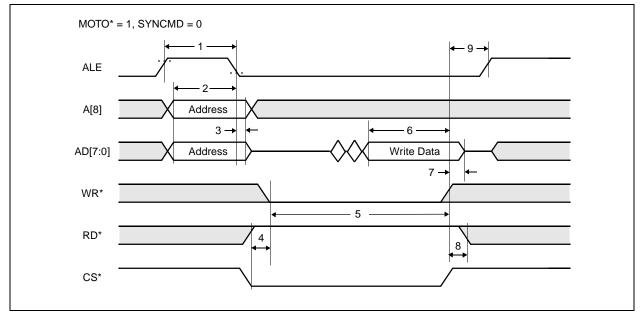

| Figure 4-5.  | Motorola Asynchronous Read Cycle 4-8                                       |

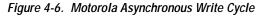

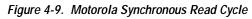

| Figure 4-6.  | Motorola Asynchronous Write Cycle 4-9                                      |

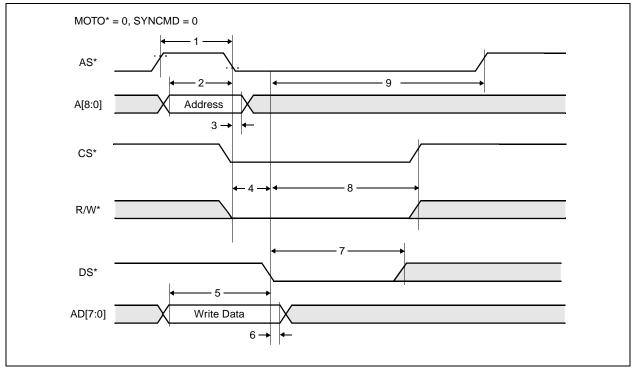

| Figure 4-7.  | Intel Asynchronous Read Cycle 4-10                                         |

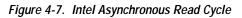

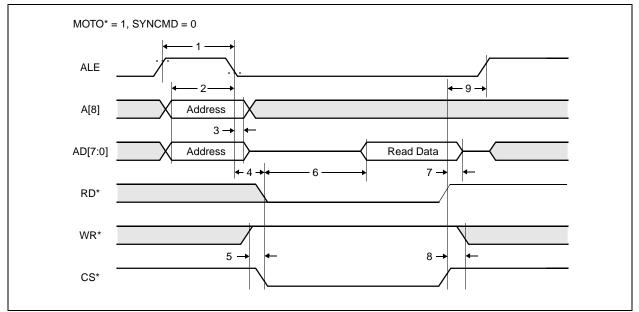

| Figure 4-8.  | Intel Asynchronous Write Cycle 4-11                                        |

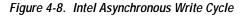

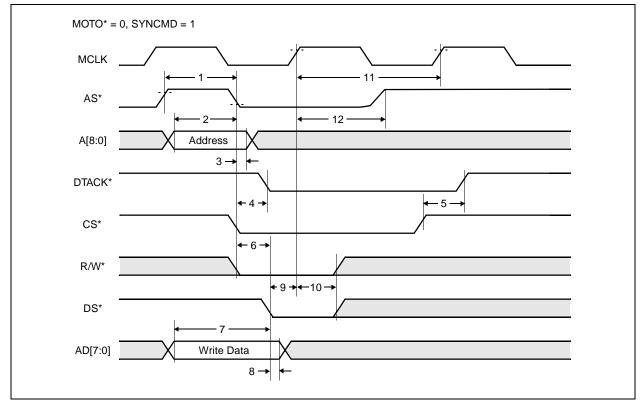

| Figure 4-9.  | Motorola Synchronous Read Cycle 4-12                                       |

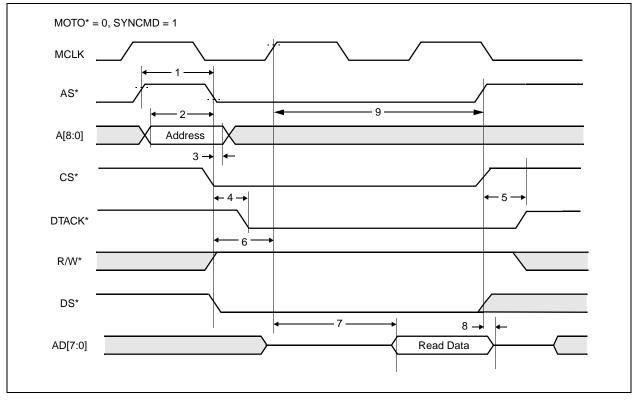

| Figure 4-10. | Motorola Synchronous Write Cycle 4-13                                      |

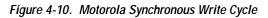

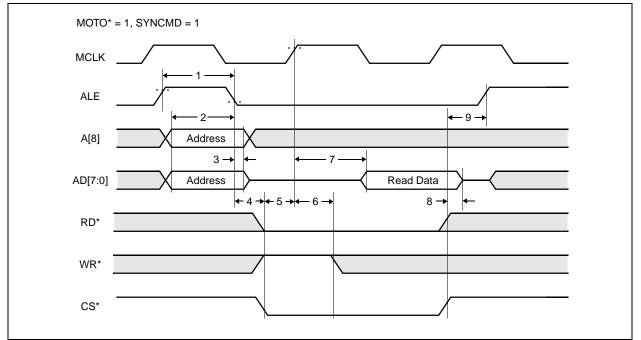

| Figure 4-11. | Intel Synchronous Read Cycle                                               |

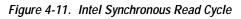

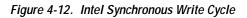

| Figure 4-12. | Intel Synchronous Write Cycle 4-15                                         |

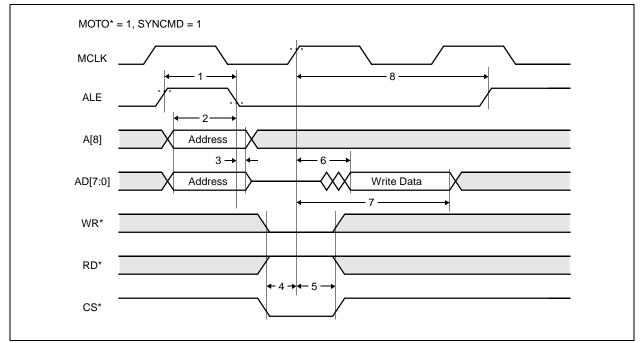

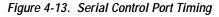

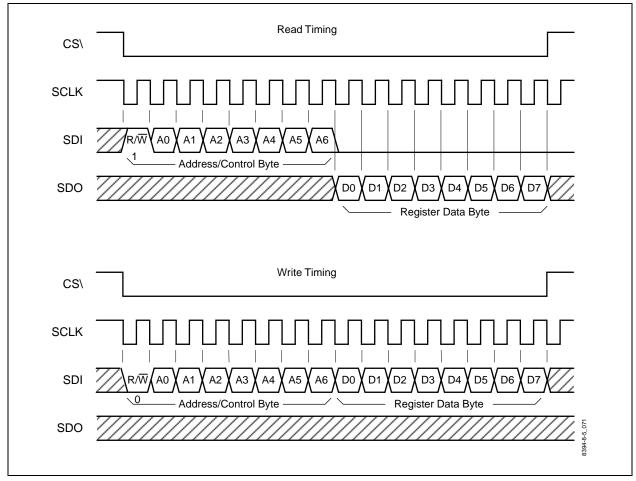

| Figure 4-13. | Serial Control Port Timing                                                 |

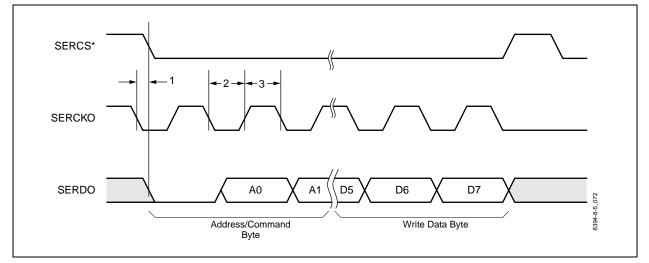

| Figure 4-14. | Serial Control Port Write Timing 4-16                                      |

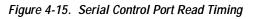

| Figure 4-15. | Serial Control Port Read Timing 4-17                                       |

| Figure 4-16. | SBI Timing—1536K Mode(1) 4-18                                              |

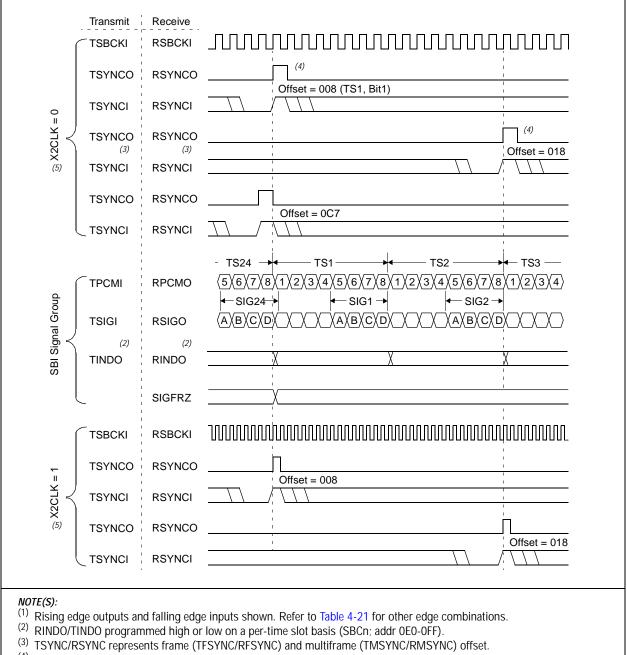

| Figure 4-17. | SBI Timing—1544K Mode(1) 4-19                                              |

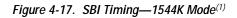

| Figure 4-18. | SBI Timing—2048K Mode(1) 4-20                                              |

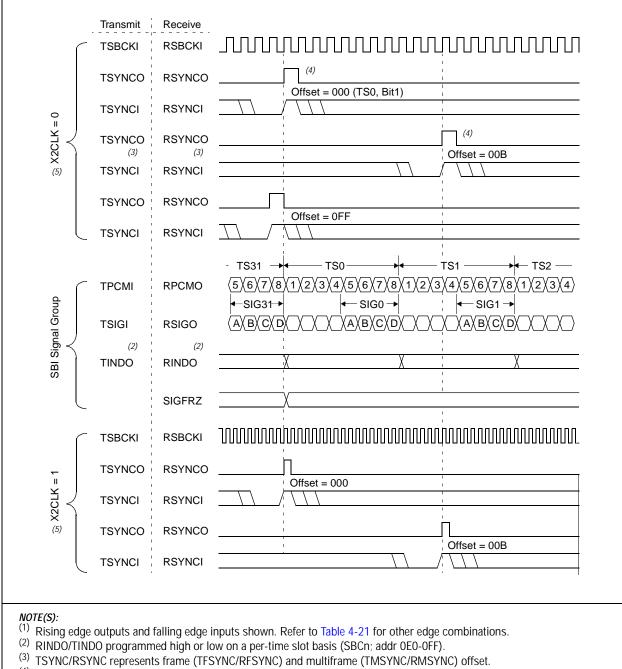

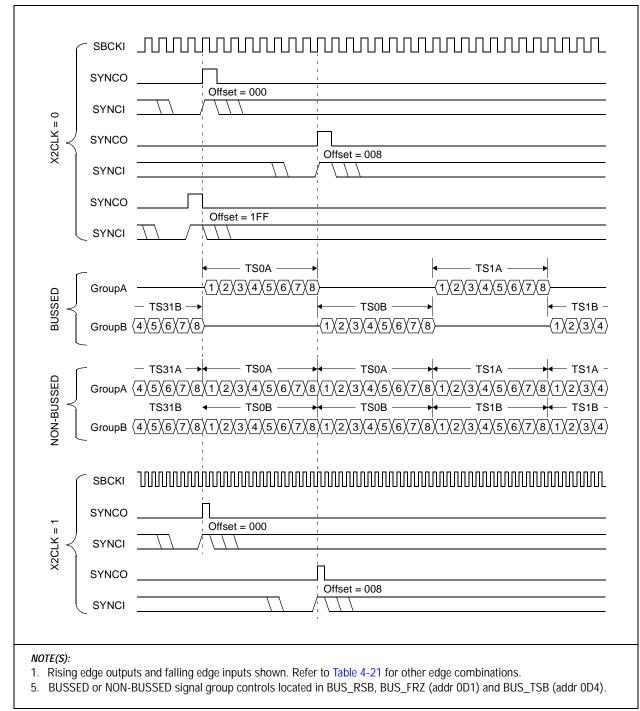

| Figure 4-19. | SBI Timing—4096K Mode(1),(5) 4-21                                          |

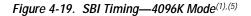

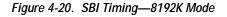

| Figure 4-20. | SBI Timing—8192K Mode                                                      |

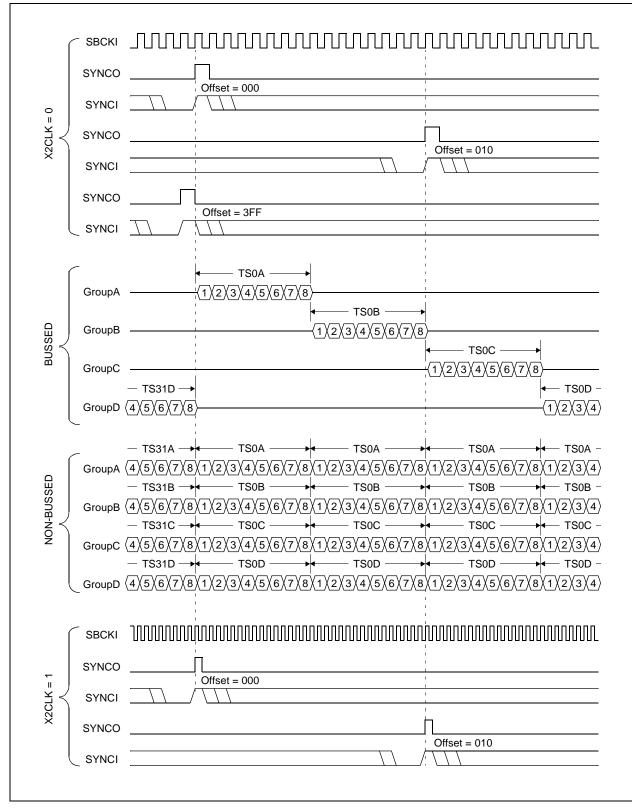

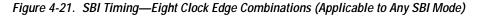

| Figure 4-21. | SBI Timing—Eight Clock Edge Combinations (Applicable to Any SBI Mode) 4-23 |

| Figure 4-22. | JTAG Interface Timing                                                      |

| Figure 4-23. | 318-Pin Ball Grid Array (BGA)                                              |

| Figure 4-24. | 272-Pin Ball Grid Array (BGA)                                              |

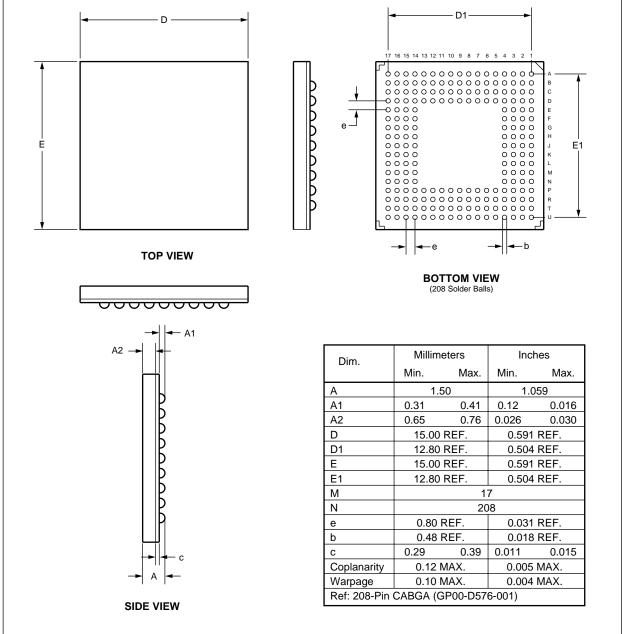

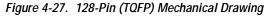

| Figure 4-25. | 208-Pin Ball Grid Array (CABGA)                                            |

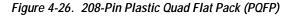

| Figure 4-26. | 208-Pin Plastic Quad Flat Pack (PQFP) 4-28                                 |

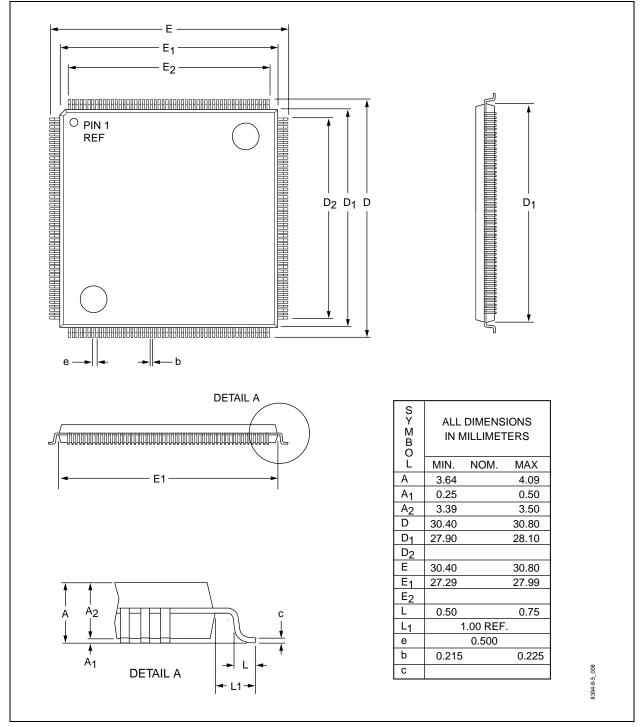

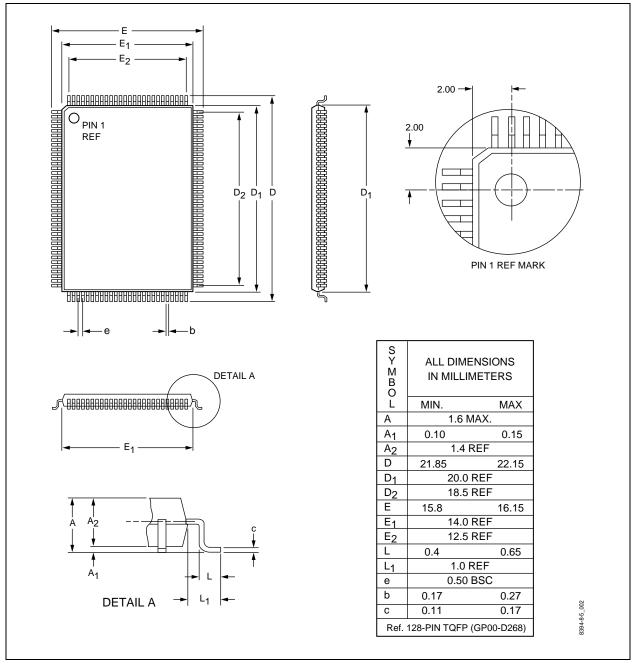

| Figure 4-27. | 128-Pin (TQFP) Mechanical Drawing 4-29                                     |

| Figure A-1.  | T1 Superframe PCM Format A-1                                               |

| Figure A-2.  | T1 Extended Superframe Format                                              |

| Figure A-3.  | E1 Format                                                                  |

## **List of Tables**

| Table 1-1.  | Pin Assignments (SBI1, SBI2, SBI3, SBI4) 1-9              |

|-------------|-----------------------------------------------------------|

| Table 1-2.  | Pin Assignments (SBI5, SBI6, SBI7, SBI8) 1-11             |

| Table 1-3.  | Pin Assignments (SBI9, SBI10, SBI11, SBI12) 1-13          |

| Table 1-4.  | Pin Assignments (SBI13, SBI14, SBI15, SBI16) 1-14         |

| Table 1-5.  | Pin Assignments                                           |

| Table 1-6.  | Hardware Signal Definitions                               |

| Table 2-1.  | Receive Framer Modes                                      |

| Table 2-2.  | Criteria for Loss/Recovery of Receive Framer Alignment    |

| Table 2-3.  | Commonly Used Data Link Settings 2-16                     |

| Table 2-4.  | RSB Interface Time Slot Mapping 2-27                      |

| Table 2-5.  | Commonly Used Data Link Settings 2-43                     |

| Table 2-6.  | Yellow Alarm Generation                                   |

| Table 2-7.  | Microprocessor Interface Operating Modes                  |

| Table 2-8.  | JTAG Instructions                                         |

| Table 2-9.  | CX28394 Device Identification JTAG Register               |

| Table 2-10. | CX28395 Device Identification JTAG Register               |

| Table 2-11. | CX28398 Device Identification JTAG Register               |

| Table 3-1.  | Address Offset Map (CX28394)                              |

| Table 3-2.  | Address Offset Map (CX28398)                              |

| Table 3-3.  | Address Offset Map (CX28395).         3-2                 |

| Table 3-4.  | Address Map                                               |

| Table 3-5.  | Receive Framer Modes    3-12                              |

| Table 3-6.  | Interrupt Status Register Summary                         |

| Table 3-7.  | Counter Overflow Behavior                                 |

| Table 3-8.  | Maximum Average Reframe Time (MART) and Framer Timeout    |

| Table 3-9.  | System Bus Sync Mode Summary 3-32                         |

| Table 3-10. | Common TFSYNC and TMSYNC Configurations                   |

| Table 3-11. | Common RFSYNC and RMSYNC Configurations                   |

| Table 3-12. | Receive PRBS Test Pattern Measurements    3-39            |

| Table 3-13. | Receive Yellow Alarm Set/Clear Criteria    3-42           |

| Table 3-14. | Receive Yellow Alarm                                      |

| Table 3-15. | E1 Transmit Framer Modes (T1/E1N = 0) 3-56                |

| Table 3-16. | T1 Transmit Framer Modes (T1/E1N = 1) 3-57                |

| Table 3-17. | Criteria for E1 Loss/Recovery of Transmit Frame Alignment |

| Table 3-18. | Criteria for T1 Loss/Recovery of Transmit Frame Alignment |

| Table 3-19. | Transmit Framer Position    3-59                          |

| Table 3-20. | Transmit Zero Code Suppression                            |

| Table 3-21. | Transmit PRBS Test Pattern Measurements                   |

| Table 3-22. | DLI Configuration for T1-ESF, FDL                         |

| Table 3-23. | Remote DS0 Channel Loopback                                     | . 3-111     |

|-------------|-----------------------------------------------------------------|-------------|

| Table 3-24. | Signaling Loopback.                                             | . 3-111     |

| Table 3-25. | Global Control and Status Registers                             | . 3-117     |

| Table 3-26. | Primary Control Register                                        | . 3-117     |

| Table 3-27. | Interrupt Control Register                                      | . 3-117     |

| Table 3-28. | Interrupt Status Registers                                      | . 3-118     |

| Table 3-29. | Interrupt Enable Registers                                      | . 3-118     |

| Table 3-30. | Primary Control and Status Registers                            | . 3-119     |

| Table 3-31. | Serial Interface Registers                                      | . 3-119     |

| Table 3-32. | Receiver Registers                                              |             |

| Table 3-33. | Performance Monitoring Registers                                | . 3-121     |

| Table 3-34. | Receive Sa-Byte Buffers                                         |             |

| Table 3-35. | Transmitter Registers                                           |             |

| Table 3-36. | Transmit Sa-Byte Buffers.                                       | . 3-122     |

| Table 3-37. | Bit-Oriented Protocol Registers.                                | . 3-123     |

| Table 3-38. | Data Link Registers                                             | . 3-123     |

| Table 3-39. | System Bus Registers                                            | . 3-124     |

| Table 4-1.  | Absolute Maximum Ratings                                        | 4-1         |

| Table 4-2.  | Recommended Operating Conditions                                | 4-2         |

| Table 4-3.  | DC Characteristics.                                             | 4-3         |

| Table 4-4.  | Input Clock Timing                                              | 4-4         |

| Table 4-5.  | Input Data Setup and Hold Timing                                | 4-5         |

| Table 4-6.  | Output Data Delay Timing                                        | 4-6         |

| Table 4-7.  | One-Second Input/Output Timing                                  | 4-6         |

| Table 4-8.  | Motorola Asynchronous Read Cycle                                | 4-8         |

| Table 4-9.  | Motorola Asynchronous Write Cycle                               | 4-9         |

| Table 4-10. | Intel Asynchronous Read Cycle                                   | 4-10        |

| Table 4-11. | Intel Asynchronous Write Cycle                                  | 4-11        |

| Table 4-12. | Motorola Synchronous Read Cycle                                 | 4-12        |

| Table 4-13. | Motorola Synchronous Write Cycle                                | 4-13        |

| Table 4-14. | Intel Synchronous Read Cycle.                                   | 4-14        |

| Table 4-15. | Intel Synchronous Write Cycle                                   | 4-15        |

| Table 4-16. | Host Serial Port Timing                                         | 4-17        |

| Table 4-17. | Test and Diagnostic Interface Timing Requirements               | 4-24        |

| Table 4-18. | Test and Diagnostic Interface Switching Characteristics         | 4-24        |

| Table A-1.  | Superframe Format                                               | A-2         |

| Table A-2.  | T1DM Frame Format                                               | A-3         |

| Table A-3.  | SLC-96 Fs Bit Contents                                          | A-4         |

| Table A-4.  | Extended Superframe Format                                      | A-6         |

| Table A-5.  | Performance Report Message Structure                            |             |

| Table A-6.  | ITU–T CEPT Frame Format Time Slot 0 Bit Allocations             | A-9         |

| Table A-7.  | IRSM CEPT Frame Format Time Slot 0 Bit Allocations              |             |

| Table A-8.  | CEPT (ITU–T and IRSM) Frame Format Time Slot 16 Bit Allocations | <b>A-11</b> |

| Table B-1.  | Applicable Standards.                                           | B-1         |

| Table E-1.  | Document Revision History                                       | E-1         |

## **1.0 Product Description**

## 1.1 Overview

The CX2839x devices each contain multiple T1/E1 framers which provide the data access and framing portion of T1 and E1 physical layer interfaces:

| Device  | Number of Framers |

|---------|-------------------|

| CX28394 | 4                 |

| CX28398 | 8                 |

| CX28395 | 16                |

While the framers are identical, there are minor differences among the devices due to the pins provided. These differences are summarized below.

## 1.1.1 External Datalink

The CX28394 and CX28398 devices include an External Datalink (DL3) which provides signal access to any bit(s) in any time slot of all frames, odd frames, or even frames, including T1 framing bits. Refer to Section 2.2.8, *External Receive Data Link (CX28394 and CX28398 Only)*, and 2.4.1, *External Transmit Data Link (CX28394 and CX28398 Only)*. The DL3 signals are not available on the CX28395 device.

## 1.1.2 RINDO/TINDO

Receive and Transmit Time Slot Indicator signals are provided by each framer to mark selected (programmable) receive and transmit system bus time slots. On the CX28394 and CX28398 devices, these signals appear on different pins depending on whether Multiplexed System Bus mode or Non-Multiplexed System Bus mode is selected. On the CX28395, they are available only in Multiplexed Bus mode.

#### 1.1 Overview

## 1.1.3 LIU Serial Port

The CX28394 and CX28398 devices include a serial interface which allows a microprocessor to indirectly communicate with a line interface unit such as the CX28380 Quad T1/E1 LIU. This interface allows the microprocessor to control and query the LIU status. This serial interface is not available on the CX28395.

## 1.1.4 Transmit/Receive Line Interface

The CX28394 and CX28398 devices include line interfaces which can operate in either of two modes: bipolar NRZ or unipolar NRZ. In bipolar NRZ mode, receiver signals RPOSI, RNEGI, and RCKI are used; and transmitter signals TPOSO, TNEGO, and TCKO are used. In unipolar NRZ mode, receiver signals RNRZ and RCKI are used, and transmitter signals TNRZO and TCKO are used. The CX28395 device provides only unipolar NRZ operation and signals. Figure 1-1 illustrates the CX28395 Functional Block Diagram (single framer).

Figure 1-1. CX28395 Functional Block Diagram

## 1.2 Pin Assignments

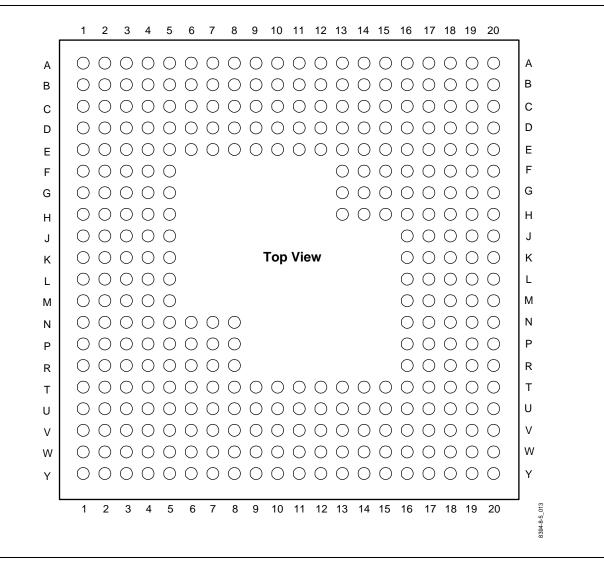

The CX28394 is packaged in a 128-pin Quad Flat Pack (TQFP). The CX28395 is packaged in a 318-pin Ball Grid Array (BGA) multi-chip module (MCM). The CX28398 has two package alternatives: a 208-pin Quad Flat Pack (MQFP) and a 272-pin BGA. Pinout diagrams are provided in Figures 1-2 through 1-6 and Tables 1-1 through 1-4 summarize pin assignments for system bus pins. Table 1-5 lists all other pin assignments.

Figures 1-7 through 1-12 illustrate the devices' logic, and Table 1-6 defines the hardware signals.

The following input pins contain an internal pullup resistor (>50 k $\Omega$ ) and may remain unconnected if the active high input state is desired:

| A[7:0]               | Address lines unused in INTEL bus mode.         |

|----------------------|-------------------------------------------------|

| MOTO*                | Pullup selects INTEL bus mode if unconnected.   |

| SYNCMD               | Pullup selects synchronous processor interface. |

| TDI (CX28394/28398)  | JTAG unused if not connected.                   |

| TDI1, TDI2 (CX28395) | JTAG unused if not connected.                   |

| TMS                  | JTAG unused if not connected.                   |

| TCK                  | Disables JTAG if not connected.                 |

| TRST*                | Disables JTAG reset if not connected.           |

| RST*                 | Disables hardware reset if not connected.       |

| SERDI                | May be left unconnected if not used.            |

1.2 Pin Assignments

| Figure 1-3. | CX28395 318-pin BGA Pinou | t Diagram |

|-------------|---------------------------|-----------|

|-------------|---------------------------|-----------|

Quad/x16/Octal—T1/E1/J1 Framers

| ſ | 1          | 2 | 3          | 4          | 5 | 6          | 7          | 8  | 9          | 10         | 11         | 12         | 13         | 14         | 15         | 16         | 17         | 7 |

|---|------------|---|------------|------------|---|------------|------------|----|------------|------------|------------|------------|------------|------------|------------|------------|------------|---|

| А | 0          | 0 | 0          | 0          | 0 | $\bigcirc$ | $\bigcirc$ | 0  | $\bigcirc$ | 0          | 0          | 0          | 0          | 0          | 0          | 0          | $\bigcirc$ | А |

| в | $\bigcirc$ | 0 | 0          | 0          | 0 | $\bigcirc$ | 0          | 0  | 0          | 0          | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | в |

| с | $\bigcirc$ | 0 | $\bigcirc$ | 0          | 0 | $\bigcirc$ | 0          | 0  | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | 0          | 0          | 0          | $\bigcirc$ | с |

| D | $\bigcirc$ | 0 | $\bigcirc$ | 0          | 0 | $\bigcirc$ | 0          | 0  | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | D |

| Е | 0          | 0 | $\bigcirc$ | 0          |   |            |            |    |            |            |            |            |            | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | E |

| F | 0          | 0 | $\bigcirc$ | $\bigcirc$ |   |            |            |    |            |            |            |            |            | 0          | 0          | $\bigcirc$ | $\bigcirc$ | F |

| G | $\bigcirc$ | 0 | $\bigcirc$ | 0          |   |            |            |    |            |            |            |            |            | 0          | 0          | 0          | $\bigcirc$ | G |

| н | $\bigcirc$ | 0 | $\bigcirc$ | 0          |   |            |            |    |            |            |            |            |            | 0          | 0          | 0          | $\bigcirc$ | н |

| J | $\bigcirc$ | 0 | $\bigcirc$ | 0          |   |            |            | То | p Vi       | ew         |            |            |            | $\bigcirc$ | 0          | 0          | $\bigcirc$ | J |

| к | $\bigcirc$ | 0 | $\bigcirc$ | Ο          |   |            |            |    |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | к |

| L | $\bigcirc$ | 0 | 0          | Ο          |   |            |            |    |            |            |            |            |            | $\bigcirc$ | 0          | 0          | $\bigcirc$ | L |

| м | 0          | 0 | $\bigcirc$ | 0          |   |            |            |    |            |            |            |            |            | 0          | 0          | 0          | $\bigcirc$ | М |

| Ν | $\bigcirc$ | Ο | $\bigcirc$ | Ο          |   |            |            |    |            |            |            |            |            | $\bigcirc$ | Ο          | $\bigcirc$ | $\bigcirc$ | Ν |

| Р | $\bigcirc$ | 0 | Ο          | Ο          | Ο | $\bigcirc$ | Ο          | Ο  | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | 0          | 0          | 0          | $\bigcirc$ | Р |

| R | $\bigcirc$ | 0 | $\bigcirc$ | Ο          | Ο | $\bigcirc$ | 0          | 0  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | 0          | 0          | $\bigcirc$ | $\bigcirc$ | R |

| т | $\bigcirc$ | 0 | $\bigcirc$ | Ο          | Ο | $\bigcirc$ | 0          | 0  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | 0          | 0          | $\bigcirc$ | $\bigcirc$ | Т |

| U | 0          | 0 | 0          | 0          | 0 | $\bigcirc$ | 0          | 0  | 0          | 0          | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | 0          | 0          | 0          | U |

| Į | 1          | 2 | 3          | 4          | 5 | 6          | 7          | 8  | 9          | 10         | 11         | 12         | 13         | 14         | 15         | 16         | 17         |   |

|   | 1          | 2 | 3          | 4          | 5 | 6          | 7          | 8  | 9          | 10         | 11         | 12         | 13         | 14         | 15         | 16         | 17         |   |

1.2 Pin Assignments

| F | 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 10         | 11         | 12         | 13         | 14         | 15         | 16         | 17         | 18         | 19         | 20         | _               |

|---|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----------------|

| А | 0          | $\bigcirc$ | A               |

| в | $\bigcirc$ | 0          | 0          | 0          | 0          | $\bigcirc$ | 0          | 0          | 0          | 0          | $\bigcirc$ | 0          | 0          | 0          | 0          | 0          | $\bigcirc$ | 0          | 0          | $\bigcirc$ | в               |

| c | 0          | $\bigcirc$ | 0          | 0          | 0          | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0          | 0          | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | С               |

| D | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | 0          | 0          | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | D               |

| E | 0          | $\bigcirc$ | 0          | 0          |            |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | E               |

| F | $\bigcirc$ | Ο          | $\bigcirc$ | $\bigcirc$ |            |            |            |            | т          | op         | Viev       | N          |            |            |            |            | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | F               |

| G | 0          | Ο          | 0          | Ο          |            |            |            |            | -          | - 6        |            |            |            |            |            |            | Ο          | 0          | 0          | $\bigcirc$ | G               |

| н | $\bigcirc$ | Ο          | Ο          | Ο          |            |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | 0          | 0          | $\bigcirc$ | Н               |

| J | 0          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | $\bigcirc$ | 0          |            |            |            |            | $\bigcirc$ | 0          | 0          | $\bigcirc$ | J               |

| к | 0          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | 0          | 0          | K               |

| L | 0          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | 0          | 0          | L               |

| м | 0          | 0          | 0          | 0          |            |            |            |            | Ο          | 0          | 0          | 0          |            |            |            |            | 0          | 0          | 0          | 0          | M               |

| N | 0          | 0          | 0          | 0          |            |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | 0          | 0          | 0          | N               |

| P | 0          | 0          | 0          | 0          |            |            |            |            |            |            |            |            |            |            |            |            | 0          | 0          | 0          | 0          | P               |

| R | 0          | 0          | 0          | 0          |            |            |            |            |            |            |            |            |            |            |            |            | 0          | 0          | 0          | 0          | R               |

| Т | 0          | 0          | 0          | 0          | $\frown$   | $\frown$   | $\frown$   | $\sim$     | $\frown$   | 0          | 0          | $\bigcirc$ | 0          | Т<br>           |

| U | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | 0          | 0          | $\bigcirc$ | 0          | 0          | 0          | 0          | 0          | $\bigcirc$ | 0          |                 |

| V | 0          | $\bigcirc$ | V<br>W          |

| W | 0          | $\bigcirc$ | 0          |                 |

| Y | U          | $\cup$     | $\bigcirc$ | U          | U          | $\bigcirc$ | $\bigcirc$ | 0          | U          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$ | U          | $\bigcirc$ | 0          | $\bigcirc$ | Y               |

| L | 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 10         | 11         | 12         | 13         | 14         | 15         | 16         | 17         | 18         | 19         | 20         | -5 005 <b>-</b> |

|   |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            | 8394-8-5 005    |

1.2 Pin Assignments

|                         | Р                       | in Numbe | er  |                        | System Bus Inter                                       | face Pin Functions                                 |  |  |  |

|-------------------------|-------------------------|----------|-----|------------------------|--------------------------------------------------------|----------------------------------------------------|--|--|--|

| CX28394<br>128-pin TQFP | CX28398<br>208-pin PQFP |          |     | CX28395<br>318-pin BGA | Non-Multiplexed Mode<br>SBIMODE[0] = 0 [FCR; addr 080] | Multiplexed Mode<br>SBIMODE[0] = 1 [FCR; addr 080] |  |  |  |

| 89                      | 94                      | R12      | V15 | J3                     | RPCMO[1]                                               | RSIGO[1]                                           |  |  |  |

| 90                      | 95                      | P11      | W16 | J4                     | RFSYNC[1]/RMSYNC[1]                                    | RMSYNC[1]                                          |  |  |  |

| 91                      | 96                      | U14      | Y17 | J2                     | RSBCKI[1]                                              | RSBCKI[A]                                          |  |  |  |

| 92                      | 97                      | T14      | V16 | _                      | SIGFRZ[1]                                              | SIGFRZ[1]                                          |  |  |  |

| 93                      | 98                      | R13      | W17 | _                      | RSIGO[1] / RDLO[1]                                     | RDLO[1]                                            |  |  |  |

| _                       | _                       | _        | _   | J1                     | RSIGO[1]                                               | TSTO[1]                                            |  |  |  |

| 94                      | 99                      | P12      | Y18 | _                      | RINDO[1] / RDLCKO[1]                                   | RDLCKO[1]                                          |  |  |  |

| 95                      | 100                     | U15      | V17 | K4                     | TPCMI[1]                                               | TSIGI[1]                                           |  |  |  |

| 96                      | 101                     | U16      | W18 | K1                     | TFSYNC[1]/TMSYNC[1]                                    | TMSYNC[1]                                          |  |  |  |

| 97                      | 102                     | R14      | Y19 | K3                     | TSBCKI[1]                                              | TSBCKI[A]                                          |  |  |  |

| 98                      | 103                     | P13      | V18 | _                      | TSIGI[1] / TDLI[1]                                     | TDLI[1]                                            |  |  |  |

|                         | _                       | _        | _   | K2                     | TSIGI[1]                                               | TSTI[1]                                            |  |  |  |

| 99                      | 104                     | T15      | W19 | _                      | TINDO[1] / TDLCKO[1]                                   | TDLCKO[1]                                          |  |  |  |

|                         | _                       | _        | _   | K5                     | TINDO[1]                                               | _                                                  |  |  |  |

| 75                      | 69                      | R6       | W8  | E4                     | RPCMO[2]                                               | RSIGO[2]                                           |  |  |  |

| 76                      | 70                      | T6       | Y8  | E3                     | RFSYNC[2]/RMSYNC[2]                                    | RMSYNC[2]                                          |  |  |  |

| 77                      | 71                      | U7       | V9  | E2                     | RSBCKI[2]                                              | RPCMO[A]                                           |  |  |  |

| 78                      | 72                      | P7       | W9  | _                      | SIGFRZ[2]                                              | SIGFRZ[2]                                          |  |  |  |

| 79                      | 73                      | R7       | Y9  | _                      | RSIGO[2] / RDLO[2]                                     | RDLO[2]                                            |  |  |  |

| _                       | _                       | _        | _   | F4                     | RSIGO[2]                                               | TSTO[2]                                            |  |  |  |

| 80                      | 74                      | T7       | W10 | _                      | RINDO[2] / RDLCKO[2]                                   | RDLCKO[2]                                          |  |  |  |

| 81                      | 75                      | U8       | V10 | F3                     | TPCMI[2]                                               | TSIGI[2]                                           |  |  |  |

| 82                      | 76                      | P8       | Y10 | F2                     | TFSYNC[2]/TMSYNC[2]                                    | TMSYNC[2]                                          |  |  |  |

| 83                      | 77                      | R8       | Y11 | E1                     | TSBCKI[2]                                              | TPCMI[A]                                           |  |  |  |

| 84                      | 78                      | Т8       | W11 |                        | TSIGI[2] / TDLI[2]                                     | TDLI[2]                                            |  |  |  |

| _                       |                         |          | _   | F1                     | TSIGI[2]                                               | TSTI[2]                                            |  |  |  |

| 85                      | 79                      | U9       | V11 |                        | TINDO[2] / TDLCKO[2]                                   | TDLCKO[2]                                          |  |  |  |

| _                       |                         |          |     | H5                     | TINDO[2]                                               | —                                                  |  |  |  |

| 25                      | 198                     | C6       | C6  | U9                     | RPCMO[3]                                               | RSIGO[3]                                           |  |  |  |

| 26                      | 199                     | D6       | B5  | Y9                     | RFSYNC[3]/RMSYNC[3]                                    | RMSYNC[3]                                          |  |  |  |

Quad/x16/Octal—T1/E1/J1 Framers

## Table 1-1. Pin Assignments (SBI1, SBI2, SBI3, SBI4) (2 of 2)

|                         | Р                       | in Numbe                 | er                     |                        | System Bus Interface Pin Functions                     |                                                    |  |  |  |  |

|-------------------------|-------------------------|--------------------------|------------------------|------------------------|--------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| CX28394<br>128-pin TQFP | CX28398<br>208-pin PQFP | CX28398<br>208-pin CABGA | CX28398<br>272-pin BGA | CX28395<br>318-pin BGA | Non-Multiplexed Mode<br>SBIMODE[0] = 0 [FCR; addr 080] | Multiplexed Mode<br>SBIMODE[0] = 1 [FCR; addr 080] |  |  |  |  |

| 27                      | 200                     | C5                       | A4                     | U10                    | RSBCKI[3]                                              | RINDO[A]                                           |  |  |  |  |

| 28                      | 201                     | D5                       | C5                     | _                      | SIGFRZ[3]                                              | SIGFRZ[3]                                          |  |  |  |  |

| 29                      | 202                     | B5                       | B4                     | _                      | RSIGO[3] / RDLO[3]                                     | RDL0[3]                                            |  |  |  |  |

|                         | _                       | _                        | _                      | Y10                    | RSIGO[3]                                               | TSTO[3]                                            |  |  |  |  |

| 30                      | 203                     | A4                       | A3                     | _                      | RINDO[3] / RDLCKO[3]                                   | RDLCKO[3]                                          |  |  |  |  |

| 31                      | 204                     | A3                       | C4                     | V9                     | TPCMI[3]                                               | TSIGI[3]                                           |  |  |  |  |

| 32                      | 205                     | B3                       | B3                     | W10                    | TFSYNC[3]/TMSYNC[3]                                    | TMSYNC[3]                                          |  |  |  |  |

| 33                      | 206                     | C4                       | B2                     | V10                    | TSBCKI[3]                                              | TINDO[A]                                           |  |  |  |  |

| 34                      | 207                     | A2                       | A2                     | _                      | TSIGI[3] / TDLI[3]                                     | TDLI[3]                                            |  |  |  |  |

|                         | _                       | _                        | _                      | W9                     | TSIGI[3]                                               | TSTI[3]                                            |  |  |  |  |

| 35                      | 208                     | B4                       | C3                     | _                      | TINDO[3] / TDLCKO[3]                                   | TDLCKO[3]                                          |  |  |  |  |

|                         | _                       | _                        | _                      | T10                    | TINDO[3]                                               | _                                                  |  |  |  |  |

| 13                      | 178                     | A11                      | B11                    | U5                     | RPCMO[4]                                               | RSIGO[4]                                           |  |  |  |  |

| 14                      | 179                     | B10                      | C11                    | W5                     | RFSYNC[4]/RMSYNC[4]                                    | RMSYNC[4]                                          |  |  |  |  |

| 15                      | 180                     | C10                      | A11                    | V6                     | RSBCKI[4]                                              | RFSYNC[A]                                          |  |  |  |  |

| 16                      | 181                     | D10                      | A10                    | _                      | SIGFRZ[4]                                              | SIGFRZ[4]                                          |  |  |  |  |

| 17                      | 182                     | A10                      | B10                    | _                      | RSIGO[4] / RDLO[4]                                     | RDLO[4]                                            |  |  |  |  |