# Multi-Purpose Audio/Video Embedded Processor

#### **Features**

- Dual 32-bit RISC processors (81 MIPS each)

- 32-bit DSP (81 MIPS)

- Digital video input for Picture-in-Picture (PIP)

- On-screen display generator

- 8-bit graphic engine with advanced vertical flicker filter

- Programmable audio decoder

- MPEG1 & MPEG2 video decoder

- System interface supports ATAPI CD loaders and hard disk drives

- Host interface supports peripherals such as 10/100 Ethernet controllers, DSPs, etc.

- V.90 soft-modem support

- AC'97 link support

- 2 channels of audio input

- 8 channels of audio output

- 2 channel IEC60958 transmitter

- Remote control input support

- Large number of GPIO increases design flexibility

- On-chip PLLs generate system clocks from 27 MHz

- SDRAM, SGRAM, and Flash memory support

- Available in a 208 pin MQFP

### **Description**

The CS7808 processor is a single chip solution that provides all of the processing functions you need for a broad range of audio and video applications including thin media clients, CD recorders, advanced set-top boxes, interactive TV and much more. It supports all CD formats, disk control, video decoding and up to eight channels of output. Achieve new levels of performance with 240 highly configurable MIPS of processing power. Its flexible set of design features maximizes performance, reduces system complexity, and minimizes system cost. CS7808 is the perfect choice.

Working on your next consumer entertainment product design? Combine CS7808 with other Cirrus mixed-signal converters, DSP chips, and factory firmware for a highly integrated platform crucial for Video-on-demand, set-top boxes, and other similar platforms. CS7808 is a Total-E™ (Total Entertainment) IC solution specifically designed for consumer entertainment electronics.

#### ORDERING INFORMATION

CS7808-CM 0° to 70° C 208-pin MQFP

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

#### TABLE OF CONTENTS

| 1. | CHARACTERISTICS AND SPECIFICATIONS      | 5  |

|----|-----------------------------------------|----|

|    | 1.1 AC and DC Parametric Specifications | 5  |

|    | 1.1.1 Absolute Maximum Rating           | 5  |

|    | 1.1.2 Recommended Operating Conditions  | 5  |

|    | 1.1.3 Electrical Characteristics        | 6  |

|    | 1.2 DC Characteristics                  | 7  |

|    | 1.2.1 Host Interface                    | 7  |

|    | 1.2.2 SDRAM Interface                   | 8  |

|    | 1.2.3 ROM/NVRAM Interface               | 10 |

|    | 1.2.4 Video Output Interface            | 11 |

|    | 1.2.5 Video Input Interface             | 12 |

|    | 1.2.6 Audio Input Interface             | 13 |

|    | 1.2.7 Audio Output Interface            | 14 |

|    | 1.2.8 AC97/CODEC Interface              | 15 |

|    | 1.2.9 Miscellaneous Interface Timing    | 16 |

|    | TYPICAL APPLICATION                     |    |

| 3. | FUNCTIONAL DESCRIPTION                  | 18 |

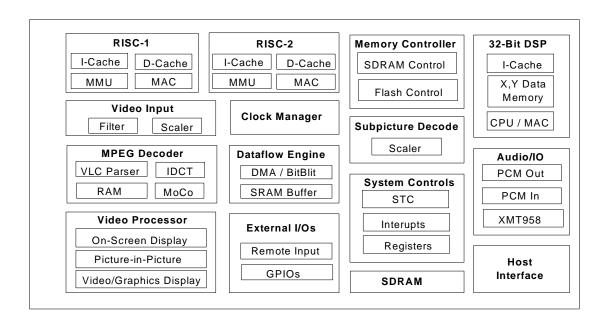

|    | 3.1 Block Diagram                       | 18 |

|    | 3.2 CS7808 Device Details               |    |

|    | 3.2.1 RISC-32 Processors                |    |

|    | 3.2.2 Powerful 32-Bit DSP               |    |

|    | 3.2.3 System Controls                   | 18 |

|    | 3.2.4 Memory Controller                 | 19 |

|    | 3.2.5 Data Flow Engine                  |    |

|    | 3.2.6 Audio Interface                   |    |

|    | 3.2.7 Video Input                       | 19 |

|    | 3.2.8 External Interface                |    |

|    | 3.2.9 Video Processor                   |    |

|    | 3.2.10 Cursor                           | 19 |

|    | 3.2.11 System Functions                 |    |

|    | 3.3 RISC Processor                      | 20 |

|    | 3.4 DSP Processor                       |    |

|    | 3.5 Memory Control                      |    |

|    | 3.6 Dataflow Control (DMA)              |    |

|    | 3.7 System Control Functions            | 20 |

### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, including use of this information as the basis for manufacture or sale of any items, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and by furnishing this information, Cirrus Logic, Inc. grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights of Cirrus Logic, Inc., copyright owner of the information contained herein, gives consent for copies to be made of the information only for use within your organization with respect to Cirrus Logic integrated circuits or other parts of Cirrus Logic, Inc. The same consent is given for similar information contained on any Cirrus Logic web site or disk. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective own

Purchase of I2C components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Phillips I2C Patent Rights to use those components in a standard I2C system.

|        | 3.8 Host Interface                                                |    |

|--------|-------------------------------------------------------------------|----|

|        | 3.9 MPEG Video Decoding                                           | 21 |

|        | 3.10 Audio Processing                                             | 21 |

|        | 3.11 Soft Modem                                                   | 21 |

|        | 3.12 Video                                                        | 21 |

|        | 4. MEMORY MAP                                                     | 23 |

|        | 4.1 Processor Memory Map                                          | 23 |

|        | 4.2 Host Port Memory Map                                          |    |

|        | 4.3 Internal I/O Space Map                                        |    |

| ,      | 5. REGISTER DESCRIPTION                                           |    |

|        | 5.1 CS7808 Register Space                                         |    |

|        | 6. PIN DESCRIPTION                                                |    |

|        | 6.1 Pin Assignments                                               |    |

|        | 6.2 Miscellaneous Interface Pins                                  |    |

|        | 6.3 SDRAM Interface                                               |    |

|        | 6.4 ROM/NVRAM Interface                                           |    |

|        | 6.5 Video Output Interface                                        |    |

|        | 6.6 Video Input Interface                                         |    |

|        | 6.7 Audio Output/Input Interface                                  |    |

|        | 6.8 AC97/CODEC Interface                                          |    |

|        | 6.9 Host Master/ATAPI Interface                                   |    |

|        | 6.10 General Purpose Input/Output (GPIO)                          |    |

|        | 6.11 Power and Ground                                             |    |

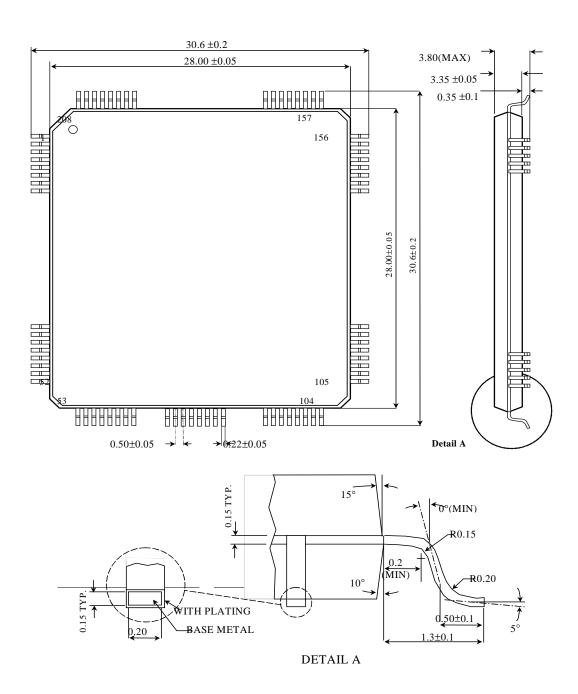

|        | 7. PACKAGE SPECIFICATIONS                                         |    |

|        | Figure 1. Host Timing Diagram                                     |    |

|        | Figure 2. SDRAM Refresh Transaction                               | 8  |

|        | Figure 3. SDRAM Burst Write Transaction                           |    |

|        | Figure 4. SDRAM Burst Read Transaction                            |    |

|        | Figure 5. SDRAM Timing                                            |    |

|        | Figure 6. ROM/RVRAM Timing                                        |    |

|        | Figure 7. Video Output Timing                                     |    |

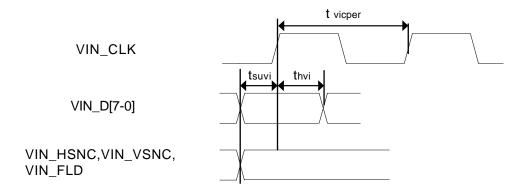

|        | Figure 8. Video Input Timing                                      |    |

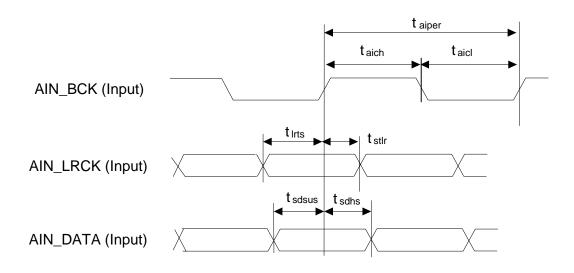

|        | Figure 9. Audio Input Timings                                     |    |

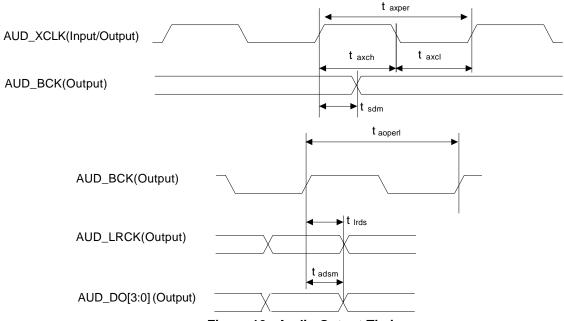

|        | Figure 10. Audio Output Timing                                    |    |

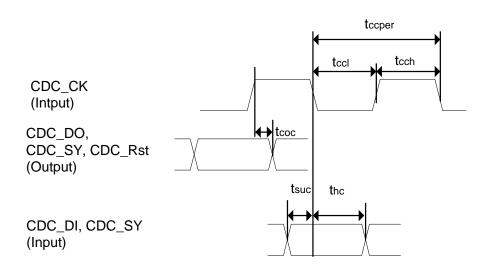

|        | Figure 11. CODEC Timing                                           |    |

|        | Figure 12. Miscellaneous Timing                                   |    |

|        | Figure 13. CS7808 Typical Application                             |    |

|        | Figure 14. CS7808 Block Diagram                                   |    |

|        | Figure 15. CS7808 Pinouts                                         |    |

|        | Figure 16. 208-Pin Package Drawing                                | 50 |

| LIST   | OF TABLES                                                         |    |

| LIUI ( |                                                                   | -  |

|        | Table 1. Host Interface Symbols / Characterization Data           |    |

|        | Table 2. SDRAM Interface Symbols and Characterization Data        |    |

|        | Table 3. ROM/NVRAM Interface Symbols and Characterization Data    |    |

|        | Table 4. Video Output Interface Symbols and Characterization Data |    |

|        | Table 5. Video Input Interface Symbols and Characterization Data  |    |

|        | Table 6. Audio Input Interface Symbols and Characterization Data  |    |

|        | Table 8. AC97/CODEC Interface Symbols and Characterization Data   | 15 |

| Table 9. Miscellaneous Interface Symbols and Characterization Data | 16 |

|--------------------------------------------------------------------|----|

| Table 10. Memory Map-RISC0 Processor                               | 23 |

| Table 11. Host Port Memory Map                                     | 23 |

| Table 12. Internal I/O Space Map                                   | 23 |

| Table 13. CS7808 Register Map and Blocks                           | 24 |

| Table 14. CS7808 Registers                                         | 24 |

| Table 15. Pin Type Legend                                          | 33 |

| Table 16. 208-Pin Package Assignments                              |    |

| Table 17. Miscellaneous Interface Pins                             |    |

| Table 18. SDRAM Interface                                          | 41 |

| Table 19. ROM/NVRAM Interface                                      | 42 |

| Table 20. Video Output Interface                                   | 43 |

| Table 21. Video Input Interface                                    | 44 |

| Table 22. Audio Input/Output Interface                             | 45 |

| Table 23. AC97/CODEC Interface                                     | 46 |

| Table 24. Host Master/ATAPI Interface                              |    |

| Table 25. General Purpose I/O Interface                            | 48 |

| Table 26. Power and Ground                                         | 49 |

# 1. CHARACTERISTICS AND SPECIFICATIONS

# 1.1 AC AND DC PARAMETRIC SPECIFICATIONS

(AGND, DGND=0V, all voltages with respect to 0V)

### 1.1.1 ABSOLUTE MAXIMUM RATING

| Symbol              | Description                                   | Min  | Max | Unit  |

|---------------------|-----------------------------------------------|------|-----|-------|

| VDD <sub>IO</sub>   | Power Supply Voltage on I/O ring              | -0,5 | 4.6 | Volts |

| VDD <sub>CORE</sub> | Power Supply Voltage on core logic and PLL    | -0.5 | 3.6 | Volts |

| V <sub>I</sub>      | Digital Input Applied Voltage (power applied) | -0.5 | 5.5 | Volts |

| I <sub>I</sub>      | Digital Input Forced Current                  | -10  | 10  | mA    |

| I <sub>O</sub>      | Digital Output Forced Current                 | -50  | 50  | mA    |

| T <sub>SOL</sub>    | Lead Soldering Temperature                    | -    | 260 | °C    |

| T <sub>VSOL</sub>   | Vapor Phase Soldering Temperature             | -    | 220 | °C    |

| T <sub>STOR</sub>   | Storage Temperature (no power applied)        | -40  | 125 | °C    |

| T <sub>AMB</sub>    | Ambient Temperature (power applied)           | 0    | 70  | °C    |

| P <sub>total</sub>  | Total Power consumption                       | -    | 2.5 | W     |

**CAUTION:** Operating beyond these Minimum and Maximum limits can result in permanent damage to the device. Cirrus Logic recommends that CS7808 devices operate at the settings described in the next table.

# 1.1.2 RECOMMENDED OPERATING CONDITIONS

| Parameter                           | Symbol           | Min  | Тур | Max  | Units |

|-------------------------------------|------------------|------|-----|------|-------|

| Supply Voltage, IO                  | $V_{DD}$         | 3.0  | 3.3 | 3.6  | Volts |

| Supply Voltage, core and PLL        | $V_{DD}$         | 2.25 | 2.5 | 2.75 | Volts |

| Ambient Temperature (power applied) | T <sub>AMB</sub> | 0    | 25  | 70   | °C    |

# 1.1.3 ELECTRICAL CHARACTERISTICS

| Parameter                    | Symbol          | Conditions                     | Min | Тур | Max | Units |

|------------------------------|-----------------|--------------------------------|-----|-----|-----|-------|

| Supply Current, IO           | I <sub>DD</sub> | Normal Operating               | -   | 45  | -   | mA    |

| Supply Current, core and PLL | I <sub>DD</sub> | Normal Operating               | -   | 550 | -   | mA    |

| Input Voltage, High          | V <sub>IH</sub> |                                | 2.0 | -   | 5.0 | Volts |

| Input Voltage, Low           | V <sub>IL</sub> |                                | -   | -   | 0.8 | Volts |

| Input Current                | I <sub>IN</sub> | $V_{IN} = V_{DD}$ or $V_{SS}$  | -1  | -   | +1  | μΑ    |

| Input Pull up/down resistor  | R <sub>I</sub>  |                                | -   | 75  | -   | ΚΩ    |

| Output Voltage, High         | V <sub>OH</sub> | @ buffer rating                | 2.4 | -   | -   | Volts |

| Output Voltage, Low          | V <sub>OL</sub> | @ buffer rating                | -   | -   | 0.4 | Volts |

| High-Z Leakage               | l <sub>oz</sub> | $V_{OUT} = V_{SS}$ or $V_{DD}$ | -10 | -   | +10 | μΑ    |

| Input Capacitance            | C <sub>IN</sub> |                                | -   | 3   | -   | pF    |

### 1.2 DC CHARACTERISTICS

(T<sub>A</sub>= 25°C; VDD\_PLL=VDD\_CORE=2.5V±10%, VDD\_IO=3.3V±10%)

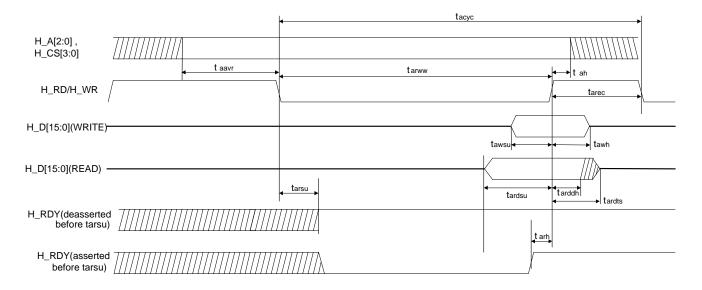

### 1.2.1 Host Interface

CS7808 can interface with a ATAPI-type slave loader gluelessly. Figure 1 illustrates a read ATAPI transaction and a write ATAPI transaction. PIO mode 4 is implemented to enable a sufficient data transfer rate between ATAPI device and CS7808.

| Symbol             | Description                         | Min | Тур | Max | Unit |

|--------------------|-------------------------------------|-----|-----|-----|------|

| <sup>t</sup> acyc  | Cycle Time <sup>1</sup>             | 98  |     |     | ns   |

| <sup>t</sup> aavr  | Address Valid to HMRD-/HMWR- Setup  | 10  |     |     | ns   |

| <sup>t</sup> ah    | Address Hold from HMRD-/HMWR- Setup | 10  |     |     | ns   |

| <sup>t</sup> arww  | H_RD-/H_WR- Pulse Width             | 72  |     |     | ns   |

| <sup>t</sup> arec  | H_RD-/H_WR- Recovery Time           | 22  |     |     | ns   |

| <sup>t</sup> awsu  | H_WR- Data Setup                    | 20  |     |     | ns   |

| <sup>t</sup> awh   | H_WR- Data Hold                     | 10  |     |     | ns   |

| <sup>t</sup> ardsu | H_RD- Data Setup                    | 20  |     |     | ns   |

| <sup>t</sup> arddh | H_RD- Data hold                     | 0   |     |     | ns   |

| <sup>t</sup> arddh | H_RD- Data High-Z                   | 0   |     | 10  |      |

| <sup>t</sup> arsu  | H_RDY Setup Time                    |     |     | 12  | ns   |

| <sup>t</sup> arh   | H_RDY Hold Time <sup>1</sup>        | 0   |     |     | ns   |

**Table 1. Host Interface Characteristics**

1. Values are guaranteed by design only.

Figure 1. Host Timing Diagram

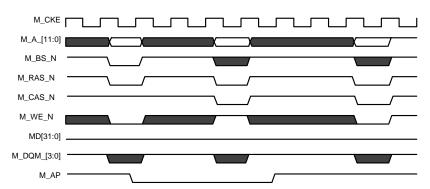

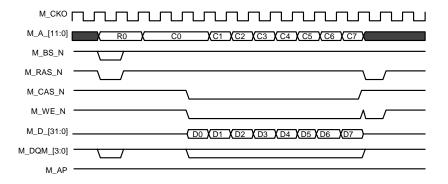

#### 1.2.2 SDRAM Interface

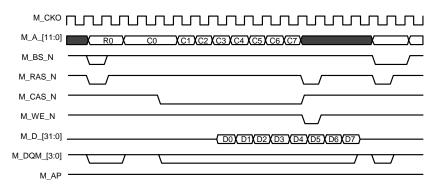

CS7808 interfaces with either SDRAM or SGRAM for high data bandwidth transfer. Figure 2 shows the refresh cycle performed by CS7808. Figure 3 shows a burst write (length = 8) transaction. Figure 4 on page 9 shows a burst read (length = 8) transaction, while Figure 5 on page 9 shows detailed SDRAM interface timing. In both Figure 3 and Figure 4, CAS latency is programmed to 3.

| Symbol            | Description                            | Min  | Тур  | Max | Unit |

|-------------------|----------------------------------------|------|------|-----|------|

| t <sub>msur</sub> | M_D[31:0] setup to M_CKO               | 3    |      |     | ns   |

| t <sub>mhr</sub>  | M_D[31:0] hold time after M_CKO        | 0    |      |     | ns   |

| t <sub>mco</sub>  | M_CKO active edge to Output transition |      |      | 7   | ns   |

| t <sub>mper</sub> | M_CKO Period <sup>1</sup>              | 10.5 | 12.2 |     | ns   |

| t <sub>mhw</sub>  | M_D[31:0] valid time after M_CKO       | 5    |      |     | ns   |

| t <sub>mdow</sub> | M_D[31:0] delay from M_CKO rising edge |      |      | 5   | ns   |

**Table 2. SDRAM Interface Characteristics**

1. Values are guaranteed by design only.

Figure 2. SDRAM Refresh Transaction

Figure 3. SDRAM Burst Write Transaction

Figure 4. SDRAM Burst Read Transaction

Figure 5. SDRAM Timing

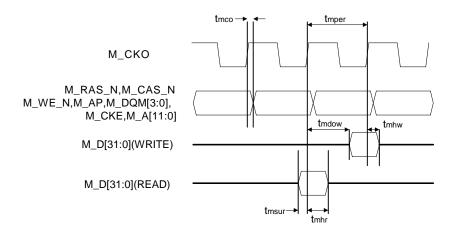

### 1.2.3 ROM/NVRAM Interface

| Symbol            | Description                | Min  | Тур  | Max | Unit |

|-------------------|----------------------------|------|------|-----|------|

| <sup>t</sup> mper | M_CKO period <sup>1</sup>  | 10.5 | 12.2 |     | ns   |

| <sup>t</sup> nco  | M_CKO to WE or OE out      |      |      | 5   | ns   |

| <sup>t</sup> nwdo | M_CKO to write data out    |      |      | 10  | ns   |

| <sup>t</sup> nsur | Data setup to M_CKO        | 5    |      |     | ns   |

| <sup>t</sup> nhw  | Data hold from WE inactive | 5    |      |     | ns   |

| <sup>t</sup> nhr  | Data hold from OE inactive | 0    |      |     | ns   |

**Table 3. ROM/NVRAM Interface Characteristics**

1. Values are guaranteed by design only.

Figure 6. ROM/RVRAM Timing

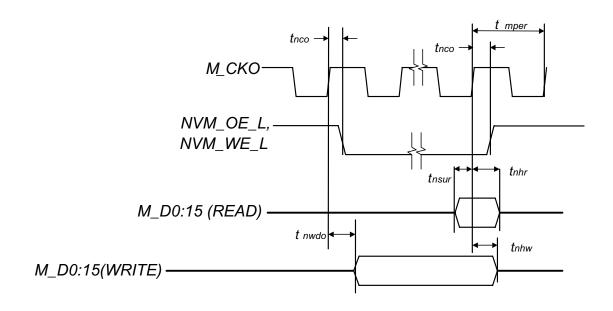

# 1.2.4 Video Output Interface

| Symbol              | Description                               | Min | Тур    | Max | Unit |

|---------------------|-------------------------------------------|-----|--------|-----|------|

| t <sub>suvo</sub>   | Vsync/Hsync input setup to CLK27_O        | 5   |        |     | ns   |

| t <sub>covo1</sub>  | VDAT[7:0] delay from CLK27_O transition   |     |        | 10  | ns   |

| t <sub>covo2</sub>  | Vsync/Hsync delay from CLK27_O transition |     |        | 10  | ns   |

| t <sub>vocper</sub> | CLK27_O High Time <sup>1</sup>            |     | 37.037 |     | ns   |

**Table 4. Video Output Interface Characteristics**

1. Values are guaranteed by design only

Figure 7. Video Output Timing

# 1.2.5 Video Input Interface

| Symbol              | Description                                    | Min | Тур    | Max | Unit |

|---------------------|------------------------------------------------|-----|--------|-----|------|

| t <sub>suvi</sub>   | VIN_D[7:0] set up to VIN_CLK                   | 5   |        |     | ns   |

| t <sub>hvi</sub>    | VIN_D[7:0] hold time after VIN_CLK rising edge | 2   |        |     | ns   |

| t <sub>vicper</sub> | VIN_CLK High Time <sup>1</sup>                 |     | 37.087 |     | ns   |

**Table 5. Video Input Interface Characteristics**

1. Active clock edge is programmable. Timing is referenced from active edge

.

Figure 8. Video Input Timing

# 1.2.6 Audio Input Interface

| Symbol             | Description                                          | Min | Тур | Max | Units |

|--------------------|------------------------------------------------------|-----|-----|-----|-------|

| t <sub>aicl</sub>  | AIN_BCK Low Time <sup>1, 2</sup>                     | 40  | 50  |     | %     |

| t <sub>aich</sub>  | AIN_BCK High Time <sup>1, 2</sup>                    | 40  | 50  |     | %     |

| t <sub>aiper</sub> | AIN_BCK period <sup>1, 2</sup>                       | 216 |     |     | ns    |

| t <sub>stlr</sub>  | Time form AIN_LRCK transition to AIN_BCK active edge | 5   |     | -   | ns    |

| t <sub>Irts</sub>  | Time form AIN_LRCK transition to AIN_BCK active edge | 2   |     | -   | ns    |

| t <sub>sdsus</sub> | AIN_DATA setup to AIN_BCK transition                 | 5   |     | -   | ns    |

| t <sub>sdhs</sub>  | AIN_DATA hold time after AIN_BCK transition          | 2   |     | -   | ns    |

**Table 6. Audio Input Interface Characteristics**

- 1. Values are guaranteed by design only

- 2. Active clock edge is programmable. Timing is referenced from active edge

Figure 9. Audio Input Timings

# 1.2.7 Audio Output Interface

| Symbol             | Description                                                   | Min | Тур | Max | Units |

|--------------------|---------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>axch</sub>  | AUD_XCLK High Time (AUD_XCLK is Input/Output) <sup>1, 2</sup> | 40  | 50  | -   | %     |

| t <sub>axcl</sub>  | AUD_XCLK Low Time (AUD_XCLK is Input/Output) <sup>1, 2</sup>  | 40  | 50  | -   | %     |

| t <sub>axper</sub> | AUD_XCLK period (Input/Output) <sup>1, 2</sup>                | 27  |     |     | ns    |

| t <sub>aoper</sub> | AUD_BCK period (Output) <sup>1, 2</sup>                       | 216 |     |     | ns    |

| t <sub>sdm</sub>   | AUD_BCK delay from AUD_XCLK transition                        | -   |     | 5   | ns    |

| t <sub>sdm</sub>   | AUD_BCK delay from AUD_XCLK transition                        | -   |     | 3   | ns    |

| t <sub>Irds</sub>  | AUD_LRCK delay from AUD_BCK transition                        | -   |     | 3   | ns    |

**Table 7: Audio Output Interface Characteristics**

- 1. Values are guaranteed by design only

- 2. Active clock edge is programmable. Timing is referenced from active edge

Figure 10. Audio Output Timing

### 1.2.8 AC97/CODEC Interface

| Symbol             | Description                                        | Min | Тур | Max | Units |

|--------------------|----------------------------------------------------|-----|-----|-----|-------|

| t <sub>suc</sub>   | Data set up to CDC_CK                              | 5   |     |     | ns    |

| t <sub>hc</sub>    | Data hold time after CDC_CK                        | 0   |     |     | ns    |

| t <sub>coc</sub>   | Time from active edge of CDC_CK to Data transition |     |     | 10  | ns    |

| t <sub>cch</sub>   | CDC_CK High Time <sup>1, 2</sup>                   | 40  | 50  |     | %     |

| t <sub>ccl</sub>   | CDC_CK Low Time <sup>1, 2</sup>                    | 40  | 50  |     | %     |

| t <sub>ccper</sub> | CDC_CK period <sup>1, 2</sup>                      | 216 |     |     | ns    |

Table 8. AC97/CODEC Interface Characteristics

- 1. Values are guaranteed by design only

- 2. Active clock edge is programmable. Timing is referenced from active edge

Figure 11. CODEC Timing

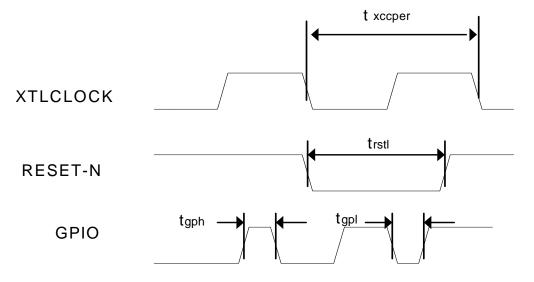

# 1.2.9 Miscellaneous Interface Timing

| Symbol              | Description                  | Min  | Тур    | Max | Units |

|---------------------|------------------------------|------|--------|-----|-------|

| t <sub>xccper</sub> | XTLCLOCK period <sup>1</sup> |      | 37.037 |     | ns    |

| t <sub>rstl</sub>   | RESET_N Pulse Width          | 1000 |        |     | ns    |

| t <sub>gpl</sub>    | GPIO PW Low                  | 50   |        |     | ns    |

| t <sub>gpl</sub>    | GPIO PW High                 | 50   |        |     | ns    |

**Table 9. Miscellaneous Interface Characteristics**

1.XTLCLOCK must meet the requirement of external the video encoder for correct chroma (27 MHz  $\pm$  1 KHz).

Figure 12. Miscellaneous Timing

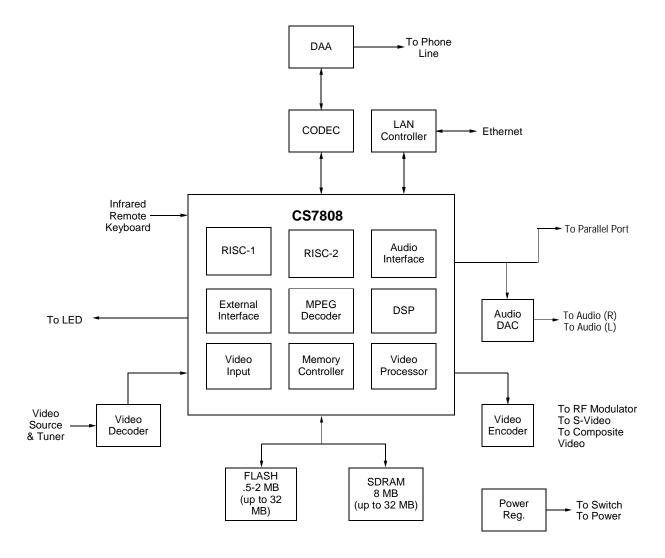

# 2. TYPICAL APPLICATION

The Figure 13 shows a typical example of a complete Set-Top Box solution using the CS7808.

Figure 13. CS7808 Typical Application

#### 3. FUNCTIONAL DESCRIPTION

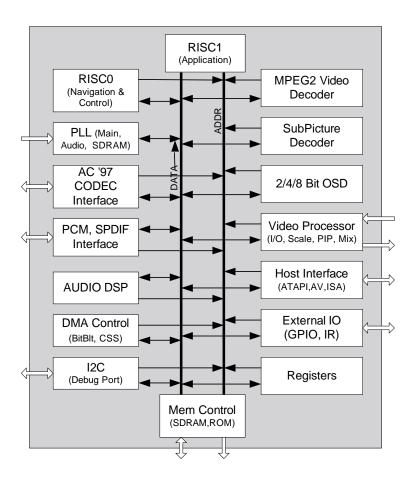

### 3.1 Block Diagram

The CS7808 block diagram is shown in Figure 14.

#### 3.2 CS7808 Device Details

#### 3.2.1 RISC-32 Processors

- Two Powerful 32-bit RISC processors (RISC0 and RISC1)

- Virtual memory support

- · Optimizing C compiler

- Big or little endian data formats support

- MAC multiply/accumulate in 2 cycles with C support

- 4 Kbyte instruction cache, 2 Kbyte data cache

- Single cycle instructions, runs at 81 Mhz

#### 3.2.2 Powerful 32-Bit DSP

- Powerful 32/24-bit DSP processor

- 24-bit fixed point logic, with 54-bit accumulator

- Single-cycle throughput, 2-cycle latency multiply accumulate, 34-bit simple integer logic

- 8-Kbyte instruction cache, 8-Kbyte program visible local memory

- Single cycle instructions, runs at 81 Mhz

### 3.2.3 System Controls

- Includes several hardware lockable semaphore registers

- General-purpose register for inter-processor communication

- 32-bit timers for I/O and other uses, with programmable interval rates

- Both hardware and software interrupts on data or debug

Figure 14. CS7808 Block Diagram

Built in PLLs generate all required clocks from 27 Mhz input clock

#### 3.2.4 Memory Controller

- Supports SDRAM, and SGRAM, from 2 Mbytes to 32 Mbytes

- Supports multiple banks of FLASH and ROM up to 16 Mbytes

- 32-bit data bus for DRAM, 8 or 16-bit data bus for ROM

#### 3.2.5 Data Flow Engine

- 2432 bytes of internal memory

- DMA to/from main RAM into local SRAM

- Supports endian conversion and byte, short, long data formats on DMA

- Supports block transfers for graphics bit blits

#### 3.2.6 Audio Interface

- Supports PCM, I<sup>2</sup>S and IEC-958 outputs at up to 96 KHz output rate

- 8 output channels, 2 input channels

#### 3.2.7 Video Input

- NTSC/PAL video decoder input interface

- Built in variable down scaling, handles CCIR 601 to QCIF input formats

- Video input image can be displayed in small window, or as main picture

#### 3.2.8 External Interface

- Serial I<sup>2</sup>C<sup>®</sup> master and slave port

- 29 independent fully programmable bi-directional I/O pins

- 8 edge or level detection interrupt pins

- Hardware assisted support for infrared remote devices, such as remote control, infrared keyboard, mouse, printer, and more

- Programmable parallel host master and slave interface supports many formats including ATAPI, ISA, and more

- Serial interface supports AC-97 and other standard MODEM CODEC protocols

#### 3.2.9 Video Processor

- Supports 24-bit 4:2:0 and 4:2:2 video modes and 16-bit true color graphics modes.

- On screen display module supports 2-bit, 4-bit, or 8bit pixel modes, while supporting 3 separate regions and 16 transparency overlay levels

- Picture-in-picture module includes horizontal and vertical downscaling with programmable output sizes, positions, and borders

- Overlay mixer with RGB to YUV conversion and output formatting

- Supports 4:2:0, 4:2:2, YUV655, RGB565 and RGB555 frame buffer inputs

- Outputs 4:2:2 video in CCIR-601 or CCIR-656 format

- High quality scaling using a vertical and a horizontal 16 taps polyphase programmable filter and supports any size image up to 768x576

- Programmable sharpening and de-blocking filters

- 5 taps programmable adaptive anti-flicker filtering for graphics source

- Master or Slave video sync configuration

- Multiple video plains overlay (main video / video input / picture\_in\_picture / picture/on\_screen / display/cursor)

- Gamma correction

#### 3.2.10 Cursor

- 4-bit color

- 16-level alpha blending

#### 3.2.11 System Functions

- 208-pin PQFP packages

- All I/O pins are 3 V with 5 V tolerance

- Advanced 0.25 micron CMOS technology

- Internal processors run at 81 MHz

- Supports Low Power modes and clock shutoff

#### 3.3 RISC Processor

The CS7808 includes two powerful, proprietary 32-bit RISC processors, RISC0 and RISC1, with optimizing C compiler support and source level debugger. The RISC processors fully support many Real Time Operation Systems (RTOS).

In addition to being compatible with the standard MIPS<sup>®</sup> R3000<sup>®</sup> instruction set, the RISC processors also have a MAC engine, which performs multiply/accumulate in 2 cycles in a pipelined fashion with C support, effectively achieving single cycle throughout.

### 3.4 DSP Processor

The CS7808 contains a proprietary digital signal processor (DSP), which is optimized for audio applications. The DSP performs 32-bit simple integer operations, and has a 24-bit fixed point logic unit, with a 54-bit accumulator. There are 32 general-purpose registers, and eight independent address generation registers, featuring: linear and circular buffer operations, and dual operand read from memory. The multiply-accumulator has single-cycle throughput, with two cycle latency. The DSP is optimized for bit packing and unpacking operations. The interface to main memory is designed for handling flexible block sizes and skip counts.

# 3.5 Memory Control

The DRAM Interface performs the SDRAM control and arbitration functions for all the other modules in the CS7808. The DRAM interface services and arbitrates a number of clients and stores their code and/or data within the local memory. This arbitration and scheduling guarantees the allocation of sufficient bandwidth to the various clients. The DRAM Interface supports up to 32 Mbytes. For a

typical application, the CS7808 requires 8 Mbytes memory space.

Sharing the same interface, CS7808 also supports FLASH ROM, OTP, or mask ROM interface. Code is stored in ROM. After the system is booted, the code is shadowed inside SDRAM for execution. The FLASH ROM interface is provided so that the code can be upgraded in the field once the communications channel is established (via modem port, CD-R, or serial port). Utility software will be provided to debug and upgrade code for the system manufacturer.

# 3.6 Dataflow Control (DMA)

The DMA controller moves data between the external memory and internal memory. The external memory address can be specified using a register, or in FIFO mode, using start and end address registers. Separate start/end address registers are used for DMA read and write operations. The DMA interface also has a block transfer function, which allows for the transfer of one block of data from one external memory location to another external memory location. In effect, this feature combines a DMA read and write into one operation. In addition, the DMA write operation allows for byte, short, word, and other types of masking.

# 3.7 System Control Functions

The system control functions are used to coordinate the activities of the multiple processors, and to provide the supporting system operations. Four 32-bit communication registers are available for interprocessor communication, and eight semaphore registers are used for resource locking. Timers are available for general-purpose functions, as well as more specialized functions such as watchdog timers and performance monitoring.

The large number of general purpose I/Os offers flexibility in system configurations. An  $I^2C$  master allows for control of other  $I^2C$  devices, such as a video encoder. An  $I^2C$  slave port shares the same pins, and can be used for debug functions. Inter-

rupts can be generated on specific or generic events. Infrared inputs can be filtered to make them free of glitches or stored unfiltered into memory. Control of all the internal clocks is also possible. Internal PLLs are used to generate the internal system and memory clocks and audio clocks of any widely used frequency.

# 3.8 Host Interface

The CS7808 has a programmable interface port which can be configured to connect to industry-standard ATAPI interfaces without external glue logic.

The Host interface can be set up in ATAPI mode, to connect directly to any ATAPI hard-disk drive (using two chip selects).

# 3.9 MPEG Video Decoding

Compressed MPEG data is read from Internet through Ethernet controller(Host I/F) or soft modem(CODEC I/F) into an input FIFO in DRAM. The data flow (DMA) controller moves Video packets from the input FIFO into the MPEG decoder's input FIFO (also in DRAM). The DMA controller can also perform advanced functions such as start code search, relieving the RISC processors. The System Synchronization function is used to control the timing of MPEG picture decoding. The MPEG Video decoder processes I, B, and P frames, and writes to video frame buffers in DRAM for output to the display. Special anti-tearing logic ensures that currently displayed frame buffers are not overwritten.

### 3.10 Audio Processing

Compressed Audio data is decompressed, then written to a PCM output FIFO, also in DRAM The DMA and decompression stages of audio processing can be done with a combination of the DMA unit, DSP, and RISC processors. The DSP is optimized for audio processing, so most common formats can be handled by the DSP alone, including AC-3, DTS, MPEG2 audio, and MP3. The DSP has

enough reserve bandwidth to handle the Karaoke echo-mix and pitch shift, and AC-3 down-mix functions.

The audio output data is written into a DRAM FIFO in 16-, 18-, 20- or 24-bit PCM format. A flexible audio output stage can simultaneously output 8 channels of PCM data to audio DACs, or 6 channels of audio data plus an IEC-958 encoded output, at up to 96 KHz. The audio interface also includes a flexible PCM input interface, which can input a wide range of protocols from an audio ADC or an IEC-958 receiver.

#### 3.11 Soft Modem

The soft modem processing is handled by one of the RISC processors, which is typically dedicated for that function. Data rates up to 56 Kbits (V.90 protocol) are supported. The CS7808 interfaces to a simple external CODEC/DAA circuit using a flexible serial interface. The serial interface is a fully programmable, bi-directional interface and can be used either as a PCM interface or as an AC97 interface. In PCM mode, the sample size could be adjusted to 20, 18 or 16 bits to match common DAC and ADC formats, or any other specific size. In AC97 mode, any slot can be used to interface either a modem CODEC or an audio CODEC.

#### 3.12 Video

The Digital Video Interface provides flexible and powerful means of outputting digital video data to external devices in CCIR601/3 and CCIR656 formats. The interface directly supports NTSC/PAL video encoding, in both master and slave synchronization configurations. The internal frame buffer format could be 4:2:0, 4:2:2, YUV655, RGB565 and RGB555. Cirrus Logic provides some easy-to-use utilities in order to get the best advantage of the powerful video filtering capabilities of the CS7808. The CS7808 also features an NTSC/PAL video decoder input interface. The interface accepts CCIR601, CIF, and QCIF formats, out of many TV decoders on the market. The video processor also

allows overlay of multiple video planes (main video / video input / picture\_in\_picture / on\_screen display / cursor). CS7808 has been proven to work with many TV encoders on the market with brands such as: Crystal, Brooktree, ADI, and AVS.

The Video Input Scaler (VIS) module inputs 8-bit digital video data from a camera or PAL/NTSC decoder, optionally down-scales to SIF or QSIF, and stores the data in one to three DRAM frame buffers. The scaled image, with a border, can be over-

laid anywhere on the screen into a ½ or ¼-screen sized window by the Picture in Picture (PIP) module.

An alternate method of using the Video Input function is to input a full sized picture and present it on the screen full size (bypass mode). An internal glitch-free mux can switch the video processor clock source from the internal clock to the Video Input clock, allowing the PIP mode to switch back and forth on the fly, with no dropout.

# 4. MEMORY MAP

# 4.1 Processor Memory Map

The CS7808 externally supports up to 32 Mbytes DRAM and 16 Mbytes ROM/NVRAM. Table 10, Table 11 and Table 12 on the next page list the memory map as viewed by the RISC processors, and identifies whether each segment is mapped or cacheable.

For detailed information on programming CS7808 memory, see *CS7808 Memory Interface User's Manual* (DS525UMD1).

# 4.2 Host Port Memory Map

Table 11 on page 23 lists the memory map as viewed by host slave port.

# 4.3 Internal I/O Space Map

Table 10, Table 11, and Table 12 show how the Internal I/O space is mapped between general registers, internal SRAM ports, and the RISC processors' debug port.

| Processor Byte Address | Description                    | Cacheable |

|------------------------|--------------------------------|-----------|

| 0000_0000 - 07FF_FFFF  | DRAM (mapped)                  | Y         |

| 8000_0000 - 81FF_FFFF  | DRAM (32 Mbytes)               | Y         |

| 9400_0000 - 9CFF_FFFF  | 16-bit NVRAM write (16 Mbytes) | N         |

| 9C00_0000 - 9CFF_FFFF  | 16-bit NVRAM/ROM (16 Mbytes)   | Y         |

| 9D00_0000 – 9DFF_FFFF  | 8-bit NVRAM/ROM (16 Mbytes)    | Y         |

| A000_0000 – A1FF_FFFF  | DRAM (32 Mbytes)               | N         |

| B000_0000 - B003_FFFF  | Internal I/O (256 Kbytes)      | N         |

| B400_0000 - BCFF_FFFF  | 16-bit NVRAM write (16 Mbytes) | N         |

| BC00_0000 - BCFF_FFFF  | 16-bit NVRAM/ROM (16 Mbytes)   | N         |

| BD00_0000 – BDFF_FFFF  | 8-bit NVRAM/ROM (16 Mbytes)    | N         |

| C000_0000 – FFFF_FFF   | DRAM (mapped)                  | Y         |

Table 10. Memory Map-RISC0 Processor

| Host Byte Address     | Description             |

|-----------------------|-------------------------|

| 0000 0000 – 003F FFFF | Internal I/O Space      |

| 1000 0000 – 13FF FFFF | DRAM space (16 Mbytes)  |

| 1400 0000 – 17FF FFFF | NVRAM space (16 Mbytes) |

**Table 11. Host Port Memory Map**

| Byte Address Offset | Description                    |

|---------------------|--------------------------------|

| 0_0000 - 0_2FFF     | General registers              |

| 0_3000 - 1_FFFF     | General Internal SRAM          |

| 2_0000 - 2_FFFF     | RISC_0 Internal SRAM/Registers |

| 3_0000 - 3_FFFF     | RISC_1 Internal SRAM/Registers |

Table 12. Internal I/O Space Map

# 5. REGISTER DESCRIPTION

# 5.1 CS7808 Register Space

Table 13 lists the register groups, and how they are split among the main CS7808 functional blocks. Table 14 lists all the registers for the CS7808 and their addresses, and indicates whether the registers are read/write (R/W), read only (RO), or write only (WO).

| CS7808 Register | Block                   |

|-----------------|-------------------------|

| 000xx, 010xx    | General                 |

| 001xx           | Host                    |

| 002xx           | DRC                     |

| 003xx           | DMA                     |

| 005xx           | Serial Interface        |

| 006xx           | DSP                     |

| 007xx           | Synchronization Control |

| 008xx           | MPEG Video Decoder      |

| 009xx           | Video Input Scaler      |

| 00Axx           | Picture-in-picture      |

| 00Bxx           | Video Processor         |

| 00Cxx           | Subpicture Display      |

| 00Dxx           | On-screen Display       |

| 00Exx           | PCM In/Out              |

| 02xxxx          | RISC_0                  |

| 03xxxx          | RISC_1                  |

Table 13. CS7808 Register Map and Blocks

| Address | Туре | Function | Register Name             |

|---------|------|----------|---------------------------|

| 000     | R/W  | General  | Command                   |

| 010     | R/W  | General  | InterProc_Comm_Register_0 |

| 014     | R/W  | General  | InterProc_Comm_Register_1 |

| 018     | R/W  | General  | InterProc_Comm_Register_2 |

| 10C     | R/W  | General  | InterProc_Comm_Register_3 |

| 020     | R/W  | General  | Semaphore_Register_0      |

| 024     | R/W  | General  | Semaphore_Register_1      |

| 028     | R/W  | General  | Semaphore_Register_2      |

| 02C     | R/W  | General  | Semaphore_Register_3      |

| 030     | R/W  | General  | Semaphore_Register_4      |

| 034     | R/W  | General  | Semaphore_Register_5      |

| 038     | R/W  | General  | Semaphore_Register_6      |

Table 14. CS7808 Registers

| Address | Туре | Function | Register Name                      |

|---------|------|----------|------------------------------------|

| 03C     | R/W  | General  | Semiphore_Register_7               |

| 040     | RO   | General  | GenIO_Read_Data                    |

| 044     | R/W  | General  | GenIO_Write_Data                   |

| 048     | R/W  | General  | GenIO_Three_State_Enable           |

| 04C     | R/W  | General  | GenIO_Positive_Edge                |

| 050     | R/W  | General  | GenIO_Negative_Edge                |

| 054     | R/W  | General  | GenIO_Interrupt_Status             |

| 058     | R/W  | General  | GenIO_Positive_Edge_Mask           |

| 05C     | R/W  | General  | GenIO_Negative_Edge_Mask           |

| 060     | R/W  | General  | GenIO_Level_Mask                   |

| 064     | R/W  | General  | GenIO_Mode Register                |

| 1040    | RO   | General  | GenIOMIS_Read_Data                 |

| 1044    | R/W  | General  | GenIOMIS_Write_Data                |

| 1048    | R/W  | General  | GenIOMIS_Three_State_Enable        |

| 104C    | R/W  | General  | GenIOMIS_Positive_Edge             |

| 1050    | R/W  | General  | GenIOMIS_Negative_Edge             |

| 1054    | R/W  | General  | GenIOMIS_Interrupt_Status          |

| 1058    | R/W  | General  | GenIOMIS_Positive_Edge_Mask        |

| 105C    | R/W  | General  | GenIOMIS_Negative_Edge_Mask        |

| 1060    | R/W  | General  | GenIOMIS_Level_Mask                |

| 1064    | R/W  | General  | GenIOMIS_Mode Register             |

| 1068    | RO   | General  | GenIOD_Read_Data                   |

| 106C    | R/W  | General  | GenIOD_Write_Data                  |

| 1070    | R/W  | General  | GenIOD_HiZ_State_Enable            |

| 1074    | RO   | General  | GenIOHST_Read_Data                 |

| 1078    | R/W  | General  | GenIOHST_Write_Data                |

| 107C    | R/W  | General  | GenIOHST_HiZ_State_Enable          |

| 068     | R/W  | General  | I <sup>2</sup> C_Mstr_Read_Comand  |

| 06C     | R/W  | General  | I <sup>2</sup> C_Mstr_Write_1Byte  |

| 070     | R/W  | General  | I <sup>2</sup> C_Mstr_Write_2Bytes |

| 074     | R/W  | General  | I <sup>2</sup> C_Mstr_Control      |

| 078     | RO   | General  | I <sup>2</sup> C_Mstr_Status       |

| 07C     | RO   | General  | I <sup>2</sup> C_Mstr_Read_Data    |

| 080     | R/W  | General  | RSK0_Interrupt_Mask                |

| 084     | WO   | General  | RSK0_Interrupt_Set                 |

| 088     | R/W  | General  | RSK0_Interrupt_Status              |

| 08C     | RO   | General  | RSK0_Interrupt_Cause               |

| 090     | R/W  | General  | DSP_Interrupt_Mask                 |

| 094     | WO   | General  | DSP_Interrupt_Set                  |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function | Register Name             |

|---------|------|----------|---------------------------|

| 098     | R/W  | General  | DSP_Interrupt_Status      |

| 09C     | RO   | General  | DSP_Interrupt_Cause       |

| 0A0     | R/W  | General  | RSK0_Interrupt_Mask2      |

| 0A4     | WO   | General  | RSK0_Interrupt_Set2       |

| 0A8     | R/W  | General  | RSK0_Interrupt2_Status    |

| 0AC     | RO   | General  | RSK0_Interrupt_Cause2     |

| 1080    | R/W  | General  | RSK1_Interrupt_Mask       |

| 1084    | WO   | General  | RSK1_Interrupt_Set        |

| 1088    | R/W  | General  | RSK1_Interrupt_Status     |

| 108C    | RO   | General  | RSK1_Interrupt_Cause      |

| 10A0    | R/W  | General  | RSK1_Interrupt_Mask2      |

| 10A4    | WO   | General  | RSK1_Interrupt_Set2       |

| 10A8    | R/W  | General  | RSK1_Interrupt2_Status    |

| 10AC    | RO   | General  | RSK1_Interrupt_Cause2     |

| 0B0     | R/W  | General  | DSP_Interrupt_Mask2       |

| 0B4     | WO   | General  | DSP_Interrupt_Set2        |

| 0B8     | R/W  | General  | DSP_Interrupt2_Status     |

| 0BC     | RO   | General  | DSP_Interrupt_Cause2      |

| 0C0     | R/W  | General  | Timer_0                   |

| 0C4     | R/W  | General  | Timer_1                   |

| 0C8     | R/W  | General  | Timer_2                   |

| 0CC     | R/W  | General  | Timer_3                   |

| 0D0     | R/W  | General  | Timer_Control             |

| 0D4     | RO   | General  | Performance_Monitor_Count |

| 0D8     | R/W  | General  | Timer_M_Over_N            |

| 0E0     | R/W  | General  | IR_Control                |

| 0E4     | R/W  | General  | IR_Dram_Start_Address     |

| 0E8     | R/W  | General  | IR_Dram_End_Address       |

| 0EC     | RO   | General  | IR_Dram_Write_Address     |

| 0F0     | R/W  | General  | PLL_Control_Register1     |

| 10F0    | R/W  | General  | Low_Power_Clock_Control   |

| 0F4     | R/W  | General  | PLL_Control_Register2     |

| 10F4    | R/W  | General  | PLL_Control_Register3     |

| 0F8     | R/W  | General  | PLL_Turn_Off              |

| 0FC     | R/W  | General  | PLL_Clock_Divider         |

| 100     | R/W  | Host     | Device_1_Control          |

| 104     | R/W  | Host     | Device_2_Control          |

| 108     | R/W  | Host     | Device_3_Control          |

| 10C     | R/W  | Host     | Device_4_Control          |

| 110     | R/W  | Host     | Write_Data_Port           |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function        | Register Name                    |

|---------|------|-----------------|----------------------------------|

| 114     | RO   | Host            | Read_Data_Port                   |

| 120     | R/W  | Host            | Host_Start_Address               |

| 124     | R/W  | Host            | DRAM Start Address               |

| 128     | R/W  | Host            | Stream_Transfer_Size             |

| 12C     | R/W  | Host            | DRAM_Burst_Threshold             |

| 13C     | R/W  | Host            | Host_Master_Control              |

| 200     | R/W  | DRAM controller | DRAM_Controller_Priority0        |

| 204     | R/W  | DRAM controller | DRAM_Controller_Priority1        |

| 208     | R/W  | DRAM controller | DRAM_Controller_Priority2        |

| 20C     | R/W  | DRAM controller | DRAM_Controller_Priority3        |

| 210     | R/W  | DRAM controller | DRAM_Controller_Priority4        |

| 214     | R/W  | DRAM controller | DRAM_Controller_Setup            |

| 218     | R/W  | DRAM controller | DRAM_Command                     |

| 21C     | R/W  | DRAM controller | DRAM_Controller_Mb_Width         |

| 220     | R/W  | DRAM controller | DRAM_Controller_Debug_Control    |

| 224     | RO   | DRAM controller | DRAM_Debug_Status                |

| 300     | WO   | DMA             | DMA_Enable                       |

| 304     | R/W  | DMA             | DMA_Control                      |

| 308     | RO   | DMA             | DMA_Status                       |

| 30C     | R/W  | DMA             | Xfer_Byte_Cnt                    |

| 310     | R/W  | DMA             | Dram_Byte_Start_Addr             |

| 314     | R/W  | DMA             | Sram_Byte_Start_Addr             |

| 318     | R/W  | DMA             | Fifo_Start_Rd_Addr               |

| 31C     | R/W  | DMA             | Fifo_Start_Wr_Addr               |

| 328     | R/W  | DMA             | Search_Control                   |

| 32C     | RO   | DMA             | Search_Status                    |

| 330     | R/W  | DMA             | Fifo_End_Rd_Addr                 |

| 334     | R/W  | DMA             | Fifo_End_Wr_Addr                 |

| 338     | R/W  | DMA             | Lines_and_Skip                   |

| 33C     | R/W  | DMA             | Byte_Mask_Pattern                |

| 540     | R/W  | SER/DCI         | Serial_Frame_Sync_Control        |

| 544     | R/W  | SER/DCI         | Serial_Output_Input_Control      |

| 548     | R/W  | SER/DCI         | AC97_Codec_Control               |

| 54C     | R/W  | SER/DCI         | AC97_Codec_Command               |

| 550     | R/W  | SER/DCI         | Serial_Output_Fifo_Start_Address |

| 554     | R/W  | SER/DCI         | Serial_Output_Fifo_End_Address   |

| 558     | R/W  | SER/DCI         | Serial_Input_Fifo_Start_Address  |

| 55C     | R/W  | SER/DCI         | Serial_Input_Fifo_End_Address    |

| 560     | RO   | SER/DCI         | Serial_Output_Fifo_Read_Address  |

| 564     | RO   | SER/DCI         | Serial_Input_Fifo_Write_Address  |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function                | Register Name                         |

|---------|------|-------------------------|---------------------------------------|

| 568     | R/W  | SER/DCI                 | Serial_Clock_Synthesis_Parameters     |

| 56C     | RO   | SER/DCI                 | Codec_Register_Status                 |

| 570     | R/W  | SER/DCI                 | Slot5_Register_Data                   |

| 574     | R/W  | SER/DCI                 | Slot10_Register_Data                  |

| 578     | R/W  | SER/DCI                 | Slot11_Register_Data                  |

| 57C     | R/W  | SER/DCI                 | Slot12_Register_Data                  |

| 580     | R/W  | SER/DCI                 | Out_fifo_int                          |

| 584     | R/W  | SER/DCI                 | In_fifo_int                           |

| 588     | R/W  | SER/DCI                 | Rate_Control                          |

| 600     | WO   | DSP                     | DSP_Boot_Code_Start_Address           |

| 604     | WO   | DSP                     | DSP_Run_Enable                        |

| 6XX     | RO   | DSP                     | DSP_Program_CntRun_Status             |

| 700     | R/W  | Synchronization Control | Audio_Sync_Control                    |

| 704     | R/W  | Synchronization Control | Video_Sync_Control                    |

| 708     | RO   | Synchronization Control | Video_Sync_Status                     |

| 70C     | R/W  | Synchronization Control | Wait_Line                             |

| 710     | R/W  | Synchronization Control | Frame_Period                          |

| 714     | R/W  | Synchronization Control | STC_Interval                          |

| 718     | R/W  | Synchronization Control | System_Time_Clock                     |

| 71C     | R/W  | Synchronization Control | Top_Bits                              |

| 720     | R/W  | Synchronization Control | Video_PTS_FIFO_Start_Address          |

| 724     | R/W  | Synchronization Control | Video_PTS_FIFO_End_Address            |

| 728     | R/W  | Synchronization Control | Video_PTS_FIFO_Write_Address          |

| 72C     | RO   | Synchronization Control | Video_PTS_FIFO_Read_Address           |

| 730     | R/W  | Synchronization Control | Subpicture_PTS_FIFO_Start_Address     |

| 734     | R/W  | Synchronization Control | Subpicture_PTS_FIFO_End_Address       |

| 738     | R/W  | Synchronization Control | Subpicture_PTS_FIFO_Write_Address     |

| 73C     | RO   | Synchronization Control | Subpicture_PTS_FIFO_Read_Address      |

| 740     | R/W  | Synchronization Control | Highlight_Start_PTS                   |

| 744     | R/W  | Synchronization Control | Highlight_End_PTS                     |

| 748     | R/W  | Synchronization Control | Button_End_PTS                        |

| 74C     | RW   | Synchronization Control | Highlight_Control_Information_Address |

| 750     | R/W  | Synchronization Control | Video_PTS                             |

| 754     | R/W  | Synchronization Control | Audio_PTS                             |

| 758     | RO   | Synchronization Control | Subpicture_PTS                        |

| 75C     | RO   | Synchronization Control | Audio_Time                            |

| 760     | RO   | Synchronization Control | Video_Sync_Debug                      |

| 764     | R/W  | Synchronization Control | SP_DRC_VPTS_Debug                     |

| 768     | R/W  | Synchronization Control | Frame_Count_Interrupt                 |

| 76C     | R/W  | Synchronization Control | Video_DTS                             |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function                | Register Name                   |

|---------|------|-------------------------|---------------------------------|

| 770     | RO   | Synchronization Control | Sync_Interrupt_Status           |

| 774     | R/W  | Synchronization Control | Sync_Interrupt_Control          |

| 778     | WO   | Synchronization Control | Sync_Interrupt_Set              |

| 77C     | WO   | Synchronization Control | Sync_Interrupt_Clear            |

| 800     | R/W  | MPEG Video Decoder      | MPEG_Video_Control              |

| 804     | R/W  | MPEG Video Decoder      | MPEG_Video_Setup                |

| 808     | R/W  | MPEG Video Decoder      | MPEG_Video_FIFO_Start_Address   |

| 80C     | R/W  | MPEG Video Decoder      | MPEG_Video_FIFO_End_Address     |

| 810     | RO   | MPEG Video Decoder      | MPEG_Video_FIFO_Current_Address |

| 814     | RO   | MPEG Video Decoder      | MPEG_Video_Horiz_Pan_Vector     |

| 818     | WO   | MPEG Video Decoder      | MPEG_Video_FIFO_Add_Bytes       |

| 81C     | RO   | MPEG Video Decoder      | MPEG_Video_FIFO_Curr_Bytes      |

| 820     | R/W  | MPEG Video Decoder      | MPEG_Video_FIFO_Interrupt_Bytes |

| 824     | RO   | MPEG Video Decoder      | MPEG_Video_FIFO_Total_Bytes     |

| 828     | RO   | MPEG Video Decoder      | MPEG_Video_Status               |

| 82C     | R/W  | MPEG Video Decoder      | Macroblock Width_Height         |

| 830     | RO   | MPEG Video Decoder      | MPEG_Video_Debug                |

| 834     | R/W  | MPEG Video Decoder      | MPEG_U_Offset                   |

| 83C     | R/W  | MPEG Video Decoder      | MPEG_I_Base_Register            |

| 840     | R/W  | MPEG Video Decoder      | MPEG_P_Base_Register            |

| 844     | R/W  | MPEG Video Decoder      | MPEG_Dest_Control               |

| 848     | RO   | MPEG Video Decoder      | MPEG_Software_Flags             |

| 84C     | R/W  | MPEG Video Decoder      | MPEG_V_Offset                   |

| 854     | R/W  | MPEG Video Decoder      | MPEG_AntiTearWindow             |

| 858     | R/W  | MPEG Video Decoder      | MPEG_Error_Pos                  |

| 900     | R/W  | Video Input Scaler      | VIS_Control                     |

| 904     | R/W  | Video Input Scaler      | VIS_StartX                      |

| 908     | R/W  | Video Input Scaler      | VIS_EndX                        |

| 90C     | R/W  | Video Input Scaler      | VIS_StartY                      |

| 910     | R/W  | Video Input Scaler      | VIS_EndY                        |

| 914     | R/W  | Video Input Scaler      | VIS_Frame_Base                  |

| 918     | R/W  | Video Input Scaler      | VIS_U_Offset                    |

| 91C     | R/W  | Video Input Scaler      | VIS_V_Offset                    |

| 920     | R/W  | Video Input Scaler      | VIS_Frame_Size                  |

| A00     | R/W  | Picture-in-Picture      | PIP_Control                     |

| A04     | R/W  | Picture-in-Picture      | PIP_VidBrdStartX                |

| A08     | R/W  | Picture-in-Picture      | PIP_VidBrdEndX                  |

| A0C     | R/W  | Picture-in-Picture      | PIP_VidBrdStartY                |

| A10     | R/W  | Picture-in-Picture      | PIP_VidBrdEndY                  |

| A14     | R/W  | Picture-in-Picture      | PIP_BorderClr                   |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function           | Register Name                    |

|---------|------|--------------------|----------------------------------|

| A18     | R/W  | Picture-in-Picture | PIP_Vscale                       |

| A1C     | R/W  | Picture-in-Picture | PIP_Line_Offnum_Bot              |

| A20     | R/W  | Picture-in-Picture | PIP_FrBaseY                      |

| A24     | R/W  | Picture-in-Picture | PIP_FrBaseU                      |

| A28     | R/W  | Picture-in-Picture | PIP_FrBaseV                      |

| A2C     | R/W  | Picture-in-Picture | PIP_Line_Width                   |

| A30     | R/W  | Picture-in-Picture | PIP_ Line_Offnum_Top             |

| A34     | R/W  | Picture-in-Picture | PIP_Frame_Size                   |

| B00     | R/W  | Video Processor    | Video_Processor_Control          |

| B04     | R/W  | Video Processor    | Video_DRAM_Line_Length           |

| B08     | R/W  | Video Processor    | Display_ActiveX                  |

| B0C     | R/W  | Video Processor    | Display_ActiveY                  |

| B10     | R/W  | Video Processor    | Blank_Color                      |

| B14     | R/W  | Video Processor    | Internal_Hsync_Count             |

| B18     | R/W  | Video Processor    | Internal_Vsync_Count             |

| B1C     | R/W  | Video Processor    | Horizontal_Y_Offset              |

| B20     | R/W  | Video Processor    | Horizontal_UV_Offset             |

| B24     | R/W  | Video Processor    | Vertical_Offset                  |

| B28     | R/W  | Video Processor    | Video_Line_Size                  |

| B2C     | R/W  | Video Processor    | Frame_Buffer_Base                |

| B30     | R/W  | Video Processor    | Video_Line_Mode_Buffer           |

| B34     | R/W  | Video Processor    | Horizontal_Vertical_Filter       |

| B38     | R/W  | Video Processor    | Source_X_Offset                  |

| B3C     | R/W  | Video Processor    | Horizontal_Video_Scaling         |

| B40     | R/W  | Video Processor    | Frame_V_Buffer_Compressed_Offset |

| B44     | WO   | Video Processor    | Mb_Width                         |

| B48     | WO   | Video Processor    | Anti-Flicker                     |

| B4C     | WO   | Video Processor    | Anti-Flicker                     |

| B50     | WO   | Video Processor    | Anti-Flicker                     |

| B54     | WO   | Video Processor    | Anti-Flicker                     |

| B58     | WO   | Video Processor    | Anti-Flicker                     |

| B5c     | WO   | Video Processor    | Gamma Control                    |

| B60     | WO   | Video Processor    | Gamma Control                    |

| B64     | WO   | Video Processor    | Gamma Control                    |

| B68     | WO   | Video Processor    | Gamma Control                    |

| B6C     | WO   | Video Processor    | Gamma Control                    |

| B70     | WO   | Video Processor    | Gamma Control                    |

| B74     | WO   | Video Processor    | Gamma Control                    |

| B78     | WO   | Video Processor    | Gamma Control                    |

| B7C     | R/W  | Video Processor    | Vid_Sync Adjust                  |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function          | Register Name             |

|---------|------|-------------------|---------------------------|

| C00     | R/W  | Subpicture        | Subpicture_Color0         |

| C04     | R/W  | Subpicture        | Subpicture_Color1         |

| C08     | R/W  | Subpicture        | Subpicture_Color2         |

| C0C     | R/W  | Subpicture        | Subpicture_Color3         |

| C10     | R/W  | Subpicture        | Subpicture_Color4         |

| C14     | R/W  | Subpicture        | Subpicture_Color5         |

| C18     | R/W  | Subpicture        | Subpicture_Color6         |

| C1C     | R/W  | Subpicture        | Subpicture_Color7         |

| C20     | R/W  | Subpicture        | Subpicture_Color8         |

| C24     | R/W  | Subpicture        | Subpicture_Color9         |

| C28     | R/W  | Subpicture        | Subpicture_Color10        |

| C2C     | R/W  | Subpicture        | Subpicture_Color11        |

| C30     | R/W  | Subpicture        | Subpicture_Color12        |

| C34     | R/W  | Subpicture        | Subpicture_Color13        |

| C38     | R/W  | Subpicture        | Subpicture_Color14        |

| C3C     | R/W  | Subpicture        | Subpicture_Color15        |

| C40     | R/W  | Subpicture        | Subpicture_DCI_Address    |

| C44     | R/W  | Subpicture        | Subpicture_HLI_Address    |

| C50     | R/W  | Subpicture        | Subpicture_Control        |

| C54     | R/W  | Subpicture        | Subpicture_Display_Offset |

| C58     | R/W  | Subpicture        | Subpicture_Display_Scale  |

| D00     | RO   | On Screen Display | OSD_Status                |

| D04     | R/W  | On Screen Display | OSD_Control               |

| D08     | R/W  | On Screen Display | OSD_Color_Number          |

| D0C     | R/W  | On Screen Display | OSD_Color_Data            |

| D10     | R/W  | On Screen Display | OSD_Region1_Control       |

| D14     | R/W  | On Screen Display | OSD_Region1_Hlimits       |

| D18     | R/W  | On Screen Display | OSD_Region1_Vlimits       |

| D1C     | R/W  | On Screen Display | OSD_Region1_DramBase      |

| D20     | R/W  | On Screen Display | OSD_Region2_Control       |

| D24     | R/W  | On Screen Display | OSD_Region2_Hlimits       |

| D28     | R/W  | On Screen Display | OSD_Region2_Vlimits       |

| D2C     | R/W  | On Screen Display | OSD_Region2_DramBase      |

| D30     | R/W  | On Screen Display | OSD_Region3_Control       |

| D34     | R/W  | On Screen Display | OSD_Region3_Hlimits       |

| D38     | R/W  | On Screen Display | OSD_Region3_Vlimits       |

| D3C     | R/W  | On Screen Display | OSD_Region3_DramBase      |

| D40     | R/W  | On Screen Display | OSD_Blend                 |

| D44     | R/W  | On Screen Display | OSD_Debug1                |

| D48     | R/W  | On Screen Display | OSD_Debug2                |

Table 14. CS7808 Registers (Continued)

| Address | Туре | Function | Register Name                        |

|---------|------|----------|--------------------------------------|

| E00     | R/W  | PCM      | PCM_Run_Clear                        |

| E04     | R/W  | PCM      | PCM_Output_Control                   |

| E08     | R/W  | PCM      | PCM_Out_FIFO_Start_Address           |

| E0C     | R/W  | PCM      | PCM_Out_FIFO_End_Address             |

| E10     | R/W  | PCM      | PCM_Out_FIFO_Interrupt_Address       |

| E14     | RO   | PCM      | PCM_Out_FIFO_Current_Address         |

| E18     | R/W  | PCM      | SPDIF_Channel_Status                 |

| E20     | R/W  | PCM      | PCM_Input_Control                    |

| E24     | R/W  | PCM      | PCM_In_FIFO_Start_Address            |

| E28     | R/W  | PCM      | PCM_In_FIFO_End_Address              |

| E2C     | R/W  | PCM      | PCM_In_FIFO_Interrupt_Address        |

| E30     | R/W  | PCM      | PCM_Out_FIFO_Interrupt_Address2      |

| E34     | R/W  | PCM      | PCM_Out_FIFO_Interrupt_Address3      |

| E38     | RO   | PCM      | PCM_In_FIFO_Current_Address          |

| E3C     | RW   | PCM      | SPDIF_Output_Control                 |

| E40     | RW   | PCM      | SPDIF_Output_FIFO_Start_Address      |

| E44     | RW   | PCM      | SPDIF_Output _FIFO_End_Address       |

| E48     | RO   | PCM      | SPDIF_Output _FIFO_Current_Address   |

| E4C     | RW   | PCM      | SPDIF_Output _FIFO_Interrupt_Address |

| E50     | RW   | PCM      | SPDIF_Output_Add_Block               |

| 2XXXX   | R/W  | RISC0    | RISC 0 Processor registers           |

| 3XXXX   | R/W  | RISC1    | RISC 1 Processor registers           |

Table 14. CS7808 Registers (Continued)

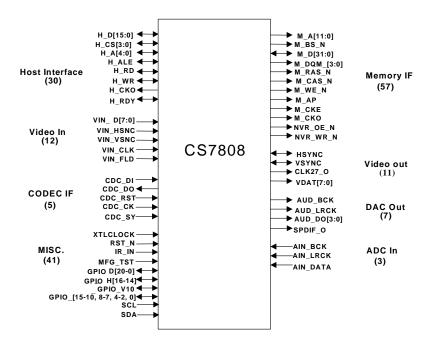

# 6. PIN DESCRIPTION

Figure 15. CS7808 Pinouts

Table 15 lists the conventions used to identify the pin type and direction.

| Pin Type | Direction                                                   |  |  |  |

|----------|-------------------------------------------------------------|--|--|--|

| I        | Input                                                       |  |  |  |

| IS       | Input, with schmitt trigger                                 |  |  |  |

| ID       | Input, with pull down resistor                              |  |  |  |

| IU       | Input, with pull up resistor                                |  |  |  |

| 0        | Output                                                      |  |  |  |

| O4       | Output – 4 mA drive                                         |  |  |  |

| O8       | Output – 8 mA drive                                         |  |  |  |

| T4       | High-Z Output – 4mA drive                                   |  |  |  |

| В        | Bi-direction                                                |  |  |  |

| B4       | Bi-direction – 4 mA drive                                   |  |  |  |

| B4U      | Bi-direction – 4 mA drive, with pull-up                     |  |  |  |

| B8U      | Bi-direction – 8 mA drive, with pull-up                     |  |  |  |

| B4S      | Bi-direction – 4 mA drive, with schmitt trigger             |  |  |  |

| B4SU     | Bi-direction – 4 mA drive, with pull-up and Schmitt trigger |  |  |  |

| Pwr      | +2.5 V or +3.3 V power supply voltage                       |  |  |  |

| Gnd      | Power supply ground                                         |  |  |  |

| Name_N   | Low active                                                  |  |  |  |

Table 15. Pin Type Legend

# 6.1 Pin Assignments

Table 16 lists the pin number, pin name, and pin type for the 208 pin CS7808 package. The primary function and pin direction is shown for all signal pins. For some signal pins, a secondary function and direction are also shown. For pins having more than one function, the primary function is chosen when the chip is reset.

| VDD_PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin | Name     | Туре | Primary Function      | Dir | Secondary Function      | Dir | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|-----------------------|-----|-------------------------|-----|------|

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   | VDD_PLL  | Pwr  | PLL Power 2.5V        | I   |                         |     |      |

| GPIO_D18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2   | M_A_11   | O8   | SDRAM Address[11]     | 0   | ROM/NVRAM Address[11]   | 0   |      |