# CS5376

# Low Power Multi-Channel Decimation Filter

#### Features

- 1 to 4 Channel Digital Decimation Filters

- Coefficient Programmable FIR Filters

- Coefficient Programmable IIR Filters

- · On-chip FIR and IIR Coefficient Set

- 62.5 sps 4000 sps Output Word Rate

- Programmable Offset and Gain Correction

- High Speed Serial Data Output Port

- DAC Test Bit Stream Generator

- 12 General Purpose I/O Pins

- Secondary Master Mode Serial Port

- IEEE 1149.1 JTAG Test Access Port

- Configuration by Microcontroller or EEPROM

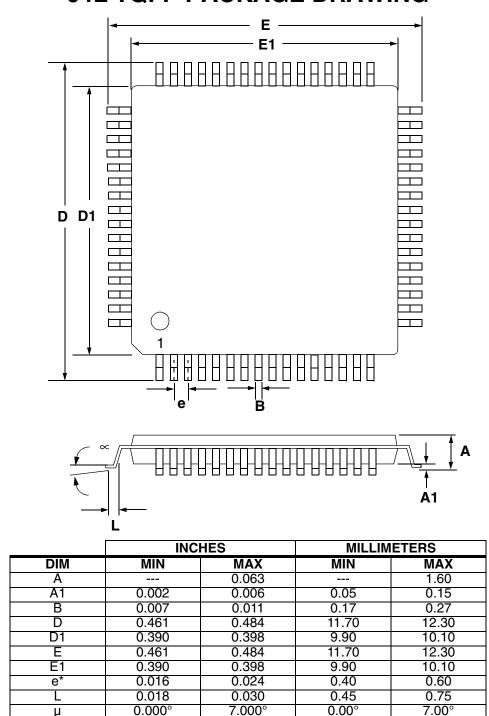

- Small Footprint 64 Pin TQFP Package

- Low Power at < 6 mW per Channel

- 3.0 V or 5.0 V Operation

### Description

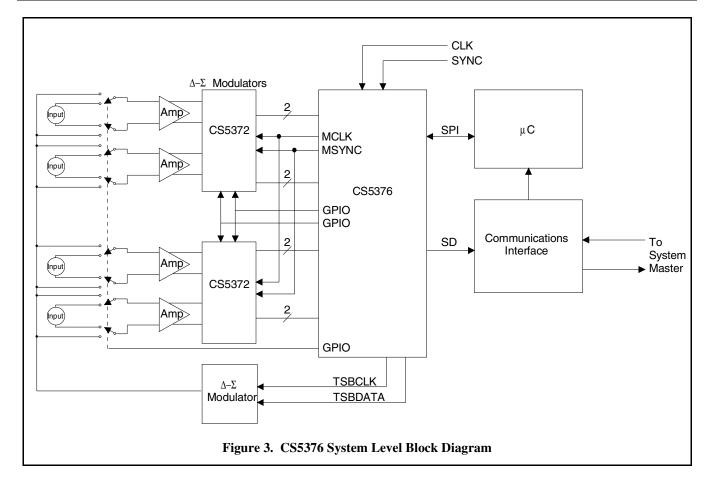

The CS5376 is a multi-function digital filter utilizing a low-power signal processing architecture to achieve efficient filtering for up to four  $\Delta-\Sigma$  modulators. Used in combination with the CS5371 and CS5372  $\Delta-\Sigma$  modulators, a unique high resolution A/D measurement system results.

Digital filter coefficients for the CS5376 FIR and IIR filters can be programmed for custom applications, or the onchip coefficient set can be used for a simple setup. Filter configuration is initialized through a serial port using a microcontroller or a configuration EEPROM.

The CS5376 includes a test bit stream generator that produces a 1-bit  $\Delta$ - $\Sigma$  modulated output suitable for driving a test DAC. It also includes 12 general purpose I/O pins for local hardware control, a secondary master mode SPI port to communicate with serial peripherals, and an IEEE 1149.1 JTAG test port for boundary scan.

#### ORDERING INFORMATION

CS5376-BS -40 to +85 °C

64-pin TQFP

Advance Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

CIRRUS LOGIC® P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2001 (All Rights Reserved)

#### **TABLE OF CONTENTS**

| 1. | CHARACTERISTICS/SPECIFICATIONS          | . 7 |

|----|-----------------------------------------|-----|

|    | 5.0 V AND 3.0 V DIGITAL CHARACTERISTICS | . 7 |

|    | POWER SUPPLY CHARACTERISTICS            |     |

|    | ABSOLUTE MAXIMUM RATINGS                |     |

|    | SWITCHING CHARACTERISTICS               |     |

| 2. | GENERAL DESCRIPTION                     | 10  |

|    | 2.1 System Configurations               | 10  |

|    | 2.2 Digital Filter Description          |     |

|    | 2.3 Integrated Hardware Peripherals     |     |

|    | 2.4 Register Descriptions               |     |

| 3. | SYSTEM DESIGN                           |     |

|    | 3.1 Power Supply Voltages               |     |

|    | 3.1.1 Bypass Capacitors                 |     |

|    | 3.2 Clock and Synchronization Signals   |     |

|    | 3.2.1 Master Clock Jitter and Skew      |     |

|    | 3.2.2 Synchronization Jitter and Skew   |     |

|    | 3.3 EEPROM Programming                  |     |

|    | 3.4 Boundary Scan Testing               |     |

|    | 3.4.1 TRST and RESET Pins               |     |

|    | 3.5 Functional Testing                  |     |

|    | 3.5.1 Analog Test DAC                   |     |

|    | 3.5.2 Step Input and Group Delay        |     |

|    | 3.6 System Registers                    |     |

| 4. | RESET CONTROL                           |     |

|    | 4.1 Reset Pin Descriptions              |     |

|    | 4.2 Boot Configurations                 |     |

| _  | 4.3 Reset Self-Tests                    |     |

| 5. | SERIAL PERIPHERAL INTERFACE 1           |     |

|    | 5.1 SPI 1 Pin Descriptions              |     |

|    | 5.2 SPI 1 Stand-Alone Mode              |     |

|    | 5.2.1 EEPROM Organization               |     |

|    | 5.2.2 EEPROM Commands                   |     |

|    | 5.2.3 CS5376 to EEPROM Transactions     |     |

|    | 5.3 SPI 1 Coprocessor Mode              |     |

| -  | 5.3.1 SPI 1 Registers                   | 29  |

| 6. | SERIAL PERIPHERAL INTERFACE 2           |     |

|    | 6.1 SPI 2 Pin Descriptions              |     |

|    | 6.2 SPI 2 Physical Interface            | 43  |

#### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

# CS5376

| 6.3 SPI 2 Registers                      |    |

|------------------------------------------|----|

| 6.3.1 SPI 2 Command Register             |    |

| 6.3.2 SPI 2 Data Register                |    |

| 6.3.3 SPI 2 Configuration Register       |    |

| 7. MODULATOR DATA INTERFACE              |    |

| 7.1 Modulator Interface Pin Descriptions |    |

| 7.2 Modulator Data Inputs                |    |

| 7.3 Modulator Flag Inputs                |    |

| 7.4 Modulator Clock Generation           |    |

| 7.4.1 Modulator Clock Enables            |    |

| 7.5 Modulator Synchronization            |    |

| 7.5.1 Modulator Sync Enable              |    |

| 8. DIGITAL DECIMATION FILTER             |    |

| 8.1 Filter Initialization                |    |

| 8.1.1 Decimation Engine Clock            | 56 |

| 8.1.2 Channel Enable                     |    |

| 8.1.3 Output Filter Selection            | 57 |

| 8.1.4 Output Word Rate                   | 58 |

| 8.2 Hardware Sinc Filter                 | 61 |

| 8.2.1 SINC1 Filter                       | 61 |

| 8.2.2 SINC2 Filter                       | 61 |

| 8.2.3 Sinc Filter Synchronization        | 63 |

| 8.3 FIR Filters                          |    |

| 8.3.1 FIR1 Filter                        |    |

| 8.3.2 FIR2 Filter                        |    |

| 8.3.3 Maximum FIR Coefficients           |    |

| 8.3.4 FIR Coefficient Upload             |    |

| 8.3.5 FIR Filter Synchronization         |    |

| 8.4 IIR Filter                           |    |

| 8.4.1 1st Order IIR                      |    |

| 8.4.2 2nd Order IIR                      |    |

| 8.4.3 3rd Order IIR                      |    |

| 8.4.4 IIR coefficient upload             |    |

| 8.4.5 IIR Filter Synchronization         |    |

| 8.5 Reference Coefficients               |    |

| 8.5.1 Reference FIR coefficients         |    |

| 8.5.2 Reference IIR coefficient set      |    |

| 9. GAIN AND OFFSET CORRECTION            |    |

|                                          |    |

| 9.1 Gain Correction                      |    |

| 9.1.1 Gain Register Calculation          |    |

| 9.2 Offset Correction                    |    |

| 9.2.1 Offset Register Calculation        |    |

| 9.3 Offset Calibration                   |    |

| 10. SERIAL DATA OUTPUT PORT              |    |

| 10.1 SD Port Pin Descriptions            |    |

| 10.2 Serial Data Transactions            |    |

| 10.3 SD Port Configurations              |    |

| 10.4 SD Port Data Format                 |    |

| 11. TIME BREAK FUNCTION                  |    |

| 11.1 Time Break Pin Description          |    |

| 11.2 Time Break Delay                    |    |

| 11.3 TB Flag Output                      |    |

| 12. SYSTEM SYNCHRONIZATION               | 80 |

# CS5376

|     | 12.1 Synchronous Clocking                | . 80 |

|-----|------------------------------------------|------|

|     | 12.2 Synchronization Signals             |      |

|     | 12.3 CS5376 Internal Synchronization     |      |

|     | 12.3.1 Sinc Filter Synchronization       | 81   |

|     | 12.3.2 Decimation Engine Synchronization | 82   |

|     | 12.3.3 SD Port Synchronization           |      |

|     | 12.3.4 Time Break Synchronization        |      |

|     | 12.3.5 Test Bit Stream Synchronization   |      |

|     | 12.4 Modulator Synchronization           |      |

|     | 13.1 TBS Generator Architecture          |      |

|     | 13.2 TBS Pin Descriptions                |      |

|     | 13.3 TBS Data Source                     |      |

|     | 13.3.1 TBS ROM Data                      |      |

|     | 13.3.2 TBS Uploaded Data                 |      |

|     | 13.4 TBS Configuration                   |      |

|     | 13.4.1 Interpolation Factor              |      |

|     | 13.4.2 Clock Rate                        |      |

|     | 13.4.3 Clock Delay                       |      |

|     | 13.4.4 Loopback Enable                   |      |

|     | 13.4.5 Run Enable                        |      |

|     | 13.4.6 Data Delay                        |      |

| 14. | GENERAL PURPOSE I/O PINS                 |      |

|     | 14.1 GPIO Input Mode                     |      |

|     | 14.2 GPIO Output Mode                    |      |

|     | 14.2.1 GPIO Read In Output Mode          |      |

|     | 14.3 GPIO Chip Select                    |      |

|     | 14.4 GPIO Pin Descriptions               |      |

| 15. | JTAG TEST PORT (IEEE 1149.1)             | 92   |

|     | 15.1 JTAG Pin Definitions                | 92   |

|     | 15.2 JTAG Architecture                   | 92   |

|     | 15.2.1 TAP Controller                    | 92   |

|     | 15.2.2 Boundary Scan Cells               | . 93 |

| 16. | WATCHDOG TIMER                           |      |

|     | 16.1 Watchdog Timer Initialization       | . 94 |

|     | 16.2 Watchdog Timer Restart              | . 94 |

| 17. | REGISTER SUMMARY                         | . 97 |

### 1. CHARACTERISTICS/SPECIFICATIONS

# 5.0 V AND 3.0 V DIGITAL CHARACTERISTICS Notes: T\_A = 25 °C; VDD = 5.0 V $\pm$ 5% or 3.0 V

± 5%; GND = 0 V

| Parameter                                               | Symbol           | Min       | Тур | Max  | Unit |

|---------------------------------------------------------|------------------|-----------|-----|------|------|

| Digital Characteristics                                 |                  |           |     | •    |      |

| High-Level Input Drive Voltage                          | V <sub>IH</sub>  | VDD - 0.6 | -   | -    | V    |

| Low-Level Input Drive Voltage                           | V <sub>IL</sub>  | -         | -   | 1.0  | V    |

| High-Level Output Drive Voltage $I_{out} = -40 \ \mu A$ | V <sub>OH</sub>  | VDD - 0.3 | -   | -    | V    |

| Low-Level Output Drive Voltage $I_{out} = +40 \ \mu A$  | V <sub>OL</sub>  | -         | -   | 0.3  | V    |

| Input Leakage Current                                   | l <sub>in</sub>  | -         | ± 1 | ± 10 | μA   |

| 3-State Leakage Current                                 | I <sub>OZ</sub>  | -         | -   | ± 10 | μA   |

| Digital Input Capacitance                               | C <sub>IN</sub>  | -         | 9   | -    | pF   |

| Digital Output Pin Capacitance                          | C <sub>out</sub> | -         | 9   | -    | pF   |

# **POWER SUPPLY CHARACTERISTICS** Notes: T<sub>A</sub> = 25 °C; GND, GND1, GND2 = 0 V

| Parameter                | Symbol | Min | Тур  | Max  | Unit |

|--------------------------|--------|-----|------|------|------|

| DC Supply                |        |     |      |      | I    |

| Digital Supply Pins      | VD     | 2.5 | 3.0  | 5.25 | V    |

| I/O Interface Pins       | VDD1   | 2.5 | -    | 5.25 | V    |

| Modulator Interface Pins | VDD2   | 2.5 | -    | 5.25 | V    |

| Power                    |        |     |      | •    |      |

| One Channel              | P1CH   | -   | 6.0  | -    | mW   |

| Four Channel             | P4CH   | -   | 22.0 | -    | mW   |

| Standby                  | PSBY   | -   | 100  | -    | μW   |

### **ABSOLUTE MAXIMUM RATINGS** Notes: T<sub>A</sub> = 25 °C; GND, GND1, GND2 = 0 V; All voltages refer-

enced to ground

| Parameter                              |                     | Symbol | Min  | Max  | Unit |

|----------------------------------------|---------------------|--------|------|------|------|

| DC power supplies:                     | Digital Supply      | VD     | -0.3 | 5.25 | V    |

|                                        | I/O Interface       | VDD1   | -0.3 | 5.25 | V    |

|                                        | Modulator Interface | VDD2   | -0.3 | 5.25 | V    |

| Input current, any pin except supplies |                     |        |      | ± 10 | mA   |

| Operating temperature (power applied)  |                     | Tmax   | -55  | +85  | °C   |

| Storage temperature                    |                     | Tstg   | -65  | +150 | °C   |

**SWITCHING CHARACTERISTICS** Notes:  $T_A = -40$  °C to +85 °C; VD = 3.0 V ± 5% or 5.0 V ± 5%; VDD1 = 3.3 V ± 5% or 5.0 V ± 5%; VDD2 = 3.3 V ± 5% or 5.0 V ± 5%; GND = GND1 = GND2 = 0 V; Logic Levels: Logic 0 = 0 V, Logic 1 = VD, VDD1, VDD2; CL = 50pF

|                   | Parameter                             | Symbol            | Min | Тур    | Max   | Unit |

|-------------------|---------------------------------------|-------------------|-----|--------|-------|------|

| Master Clock Fre  | quency (Note 1)                       | CLK               | 0.1 | 32.768 | 33    | MHz  |

| Master Clock Dut  | ty Cycle                              |                   | 40  | -      | 60    | %    |

| Rise Times        | Any Digital Input Except SCK (Note 2) | t <sub>rise</sub> | -   | -      | 1.0   | μs   |

|                   | SCK                                   |                   | -   | -      | 100   | μs   |

|                   | Any Digital Output                    |                   | -   | 50     | -     | ns   |

| Fall Times        | Any Digital Input Except SCK (Note 2) | t <sub>fall</sub> | -   | -      | 1.0   | μs   |

|                   | SCK                                   |                   | -   | -      | 100   | μs   |

|                   | Any Digital Output                    |                   | -   | 50     | -     | ns   |

| Modulator Data    | Interface                             |                   |     |        |       |      |

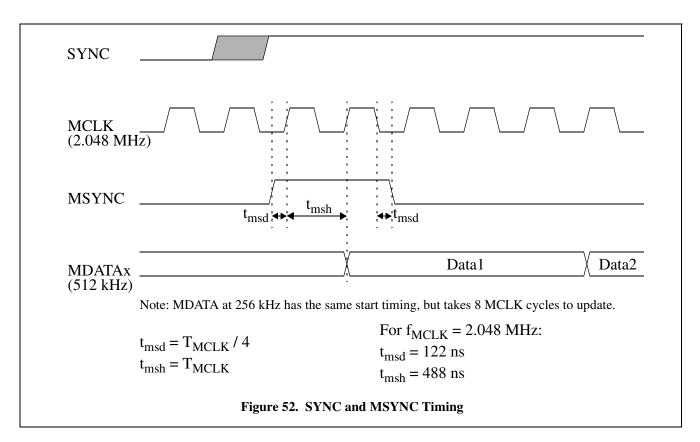

| MSYNC Setup Ti    | me to MCLK rising                     | t <sub>mss</sub>  | -20 | -      | -     | ns   |

| MCLK rising to V  | alid MDATA                            | t <sub>mdv</sub>  | -   | -40    | 75    | ns   |

| MSYNC falling to  | MCLK rising                           | t <sub>msf</sub>  | -20 | -      | -     | ns   |

| Serial Port Timi  | ng in SPI Slave Mode                  |                   |     | •      | L     |      |

| Serial Clock Free | uency                                 | SCK               | -   | -      | 4.096 | MHz  |

| Serial Clock      | Pulse Width High                      | t <sub>1</sub>    | 100 | -      | -     | ns   |

|                   | Pulse Width Low                       | t <sub>2</sub>    | 100 | -      | -     | ns   |

Notes: 1. Master clock frequencies below 32.768 MHz will affect generated clock frequencies.

2. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.

# SWITCHING CHARACTERISTICS (Continued)

| Parameter                                            | Symbol         | Min | Тур | Max | Unit |

|------------------------------------------------------|----------------|-----|-----|-----|------|

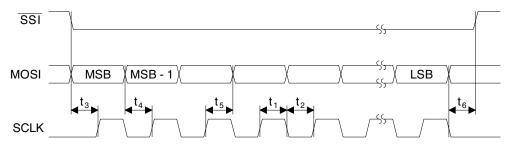

| MOSI Write Timing                                    |                |     |     |     |      |

| SSI Enable to Valid Latch Clock                      | t <sub>3</sub> | 50  | -   | -   | ns   |

| Data Set-up Time Prior to SCK Rising                 | t <sub>4</sub> | 50  | -   | -   | ns   |

| Data Hold Time After SCK Rising                      | t <sub>5</sub> | 100 | -   | -   | ns   |

| SCK Falling Prior to $\overline{\text{SSI}}$ Disable | t <sub>6</sub> | 100 | -   | -   | ns   |

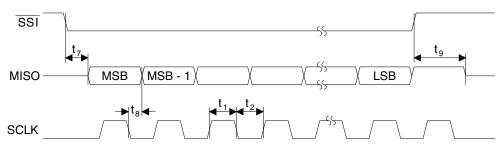

| MISO Read Timing                                     |                |     |     |     |      |

| SSI Enable to Valid Latch Clock                      | t <sub>7</sub> | -   | -   | 150 | ns   |

| SCK Falling to New Data Bit                          | t <sub>8</sub> | -   | -   | 150 | ns   |

| SSI Rising to MISO Hi-Z                              | t <sub>9</sub> | -   | -   | 150 | ns   |

Figure 1. MOSI Write Timing in SPI Slave Mode (Not to Scale)

Figure 2. MISO Read Timing in SPI Slave Mode (Not to Scale)

### 2. GENERAL DESCRIPTION

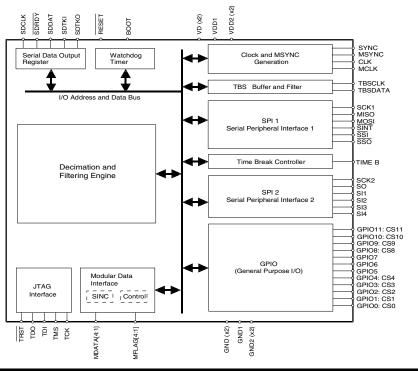

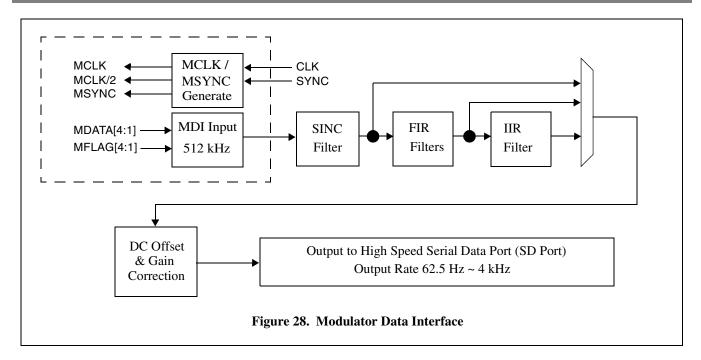

The CS5376 is a multi-channel digital filter with integrated system peripherals. The digital decimation filter uses a coefficient programmable signal processing architecture to filter up to four  $\Delta$ - $\Sigma$  modulator bit streams. An on-chip reference coefficient set is included to provide an easy set up for applications that do not require custom digital filter coefficients.

The CS5376 integrated peripherals simplify system design by providing a buffered high speed serial data output port, a test bit stream generator suitable for driving a test DAC, general purpose I/O pins for local hardware control, a secondary master mode SPI port for serial peripherals, and a JTAG port for boundary scan testing. In addition, a clock and synchronization block synchronizes the CS5376 to the host system, and a time break controller generates timing reference information in the output data stream.

#### 2.1 System Configurations

#### **Coprocessor or Stand-Alone Configurations**

Figure 3 illustrates a simplified block diagram of the CS5376 in a multi-channel system architecture. This diagram shows the CS5376 in coprocessor mode, where an external microcontroller operates as the local host. The microcontroller writes configuration commands and filter coefficients into the CS5376 from non-volatile memory or from the communications channel. This system configuration allows the microcontroller to change the filtering function of the CS5376 when instructed to do so by the system controller.

Alternately, the CS5376 can be used in stand-alone mode, where a configuration EEPROM replaces the microcontroller. The CS5376 reads configuration commands and filter coefficients directly from EEPROM, and then enters a fixed operational state. The stand-alone configuration simplifies system design by eliminating the CS5376 to microcontroller interface.

#### 2.2 Digital Filter Description

#### Multi-Stage Signal Processing Architecture

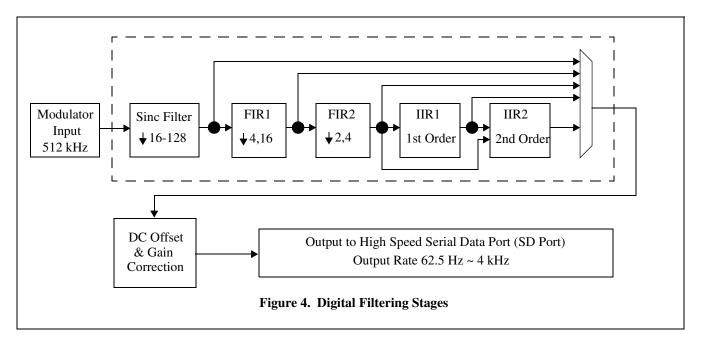

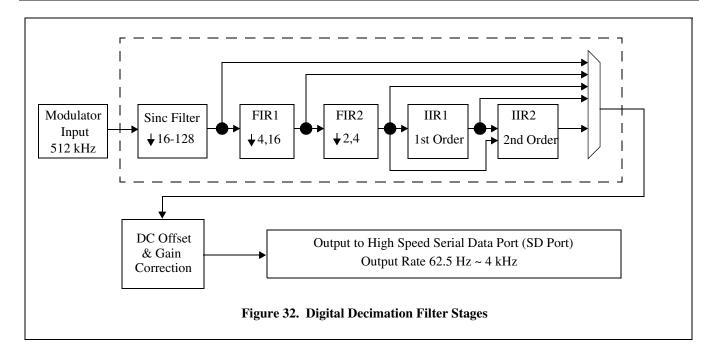

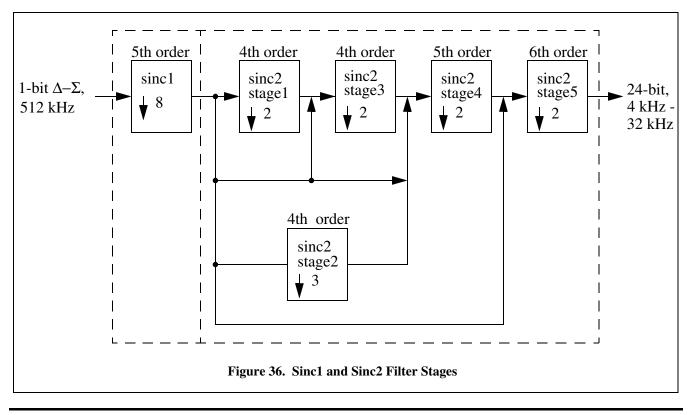

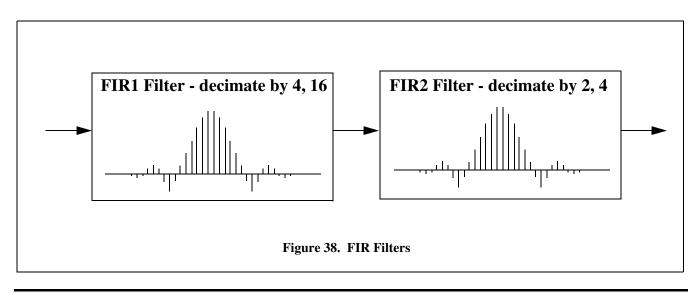

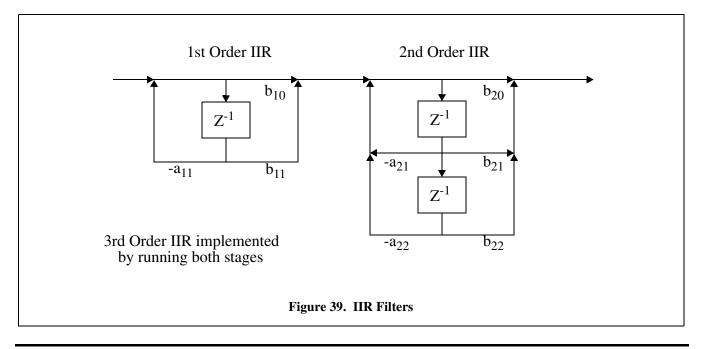

The CS5376 has a multi-stage signal processing architecture consisting of a hardware sinc filter, two FIR filters, and a selectable 1st, 2nd, or 3rd order IIR filter. The filter architecture is flexible, with the capability to bypass later filter stages and output data immediately following any filter. Figure 4 illustrates the digital filter stages of the CS5376.

The digital filters have decimation ratios that can achieve data output word rates (OWRs) between 62.5 sps and 4000 sps. Figure 5 lists the standard OWRs and their associated output periods. Slower output word rates can be achieved by scaling down the master clock input.

#### **Programmable or Fixed Coefficients**

The CS5376 is designed to load custom filter coefficients and other configuration information via the SPI 1 serial port from either a microcontroller or a configuration EEPROM.

The programmed FIR filter coefficients can implement any type of finite impulse response filter. Linear phase, minimum phase, phase compensation, or other complex filter types can be used depending on the application requirements. The programmed IIR filter coefficients can implement a 1st, 2nd, or

| Output Word Rate | Output Period |

|------------------|---------------|

| (OWR)            |               |

| 4000 sps         | 0.25 ms       |

| 2000 sps         | 0.5 ms        |

| 1000 sps         | 1.0 ms        |

| 500 sps          | 2.0 ms        |

| 333.3 sps        | 3.0 ms        |

| 250 sps          | 4.0 ms        |

| 125 sps          | 8.0 ms        |

| 62.5 sps         | 16.0 ms       |

Figure 5. Digital Filter OWRs

3rd order infinite impulse response filter with any corner frequency in the measurement bandwidth.

A set of on-chip FIR and IIR coefficients are included in the CS5376 to provide an easy set up for applications that do not require custom filter coefficients. These coefficients have excellent filtering characteristics, with the low-pass FIR filters having a corner frequency at 40%  $f_s$ , in-band ripple less than ±0.01 dB, and stop-band attenuation greater than 130 dB. The high-pass IIR filter provides a 3rd order Butterworth response with a corner frequency at 2%  $f_s$ .

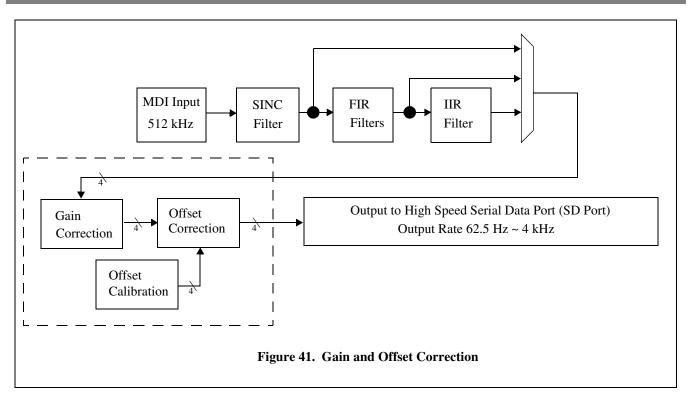

#### Programmable Gain and Offset Correction

The final operation of the digital filter is to apply a user defined gain and offset correction to the output data. The gain correction value is independently programmable for each channel and is used to normalize sensor gain across a network. Similarly, the offset correction is independently programmable for each channel and is used to correct for DC offset in a sensor. The CS5376 also includes a built in offset calibration routine that will calculate offset correction values automatically.

### 2.3 Integrated Hardware Peripherals

#### High Speed Serial Data Output Port

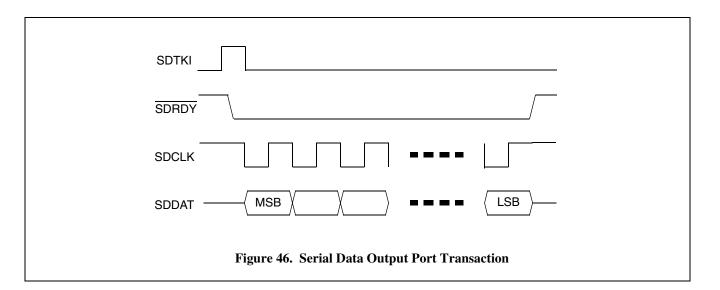

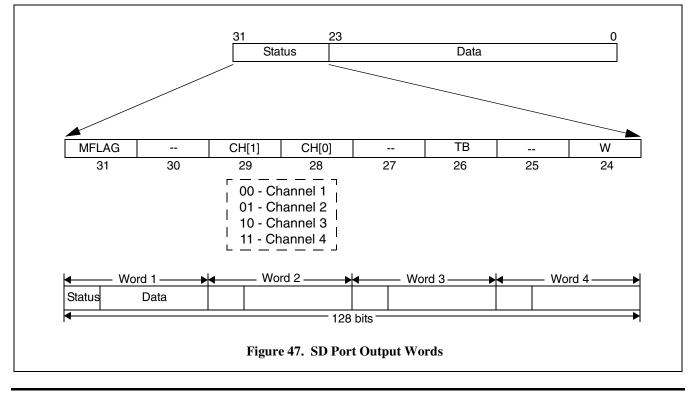

After filtering is completed, each 24-bit output sample is combined with an 8-bit status word that encodes the channel number, a time break flag, and any error conditions. This 32-bit data word is written to an 8-deep FIFO buffer and then transmitted on request to the communications interface through the high speed serial data output port. In a typical system, the communication interface will be a proprietary design.

#### Test Bit Stream Generator

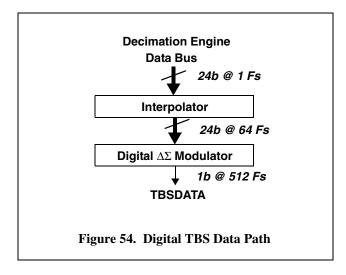

The CS5376 includes a programmable test bit stream (TBS) generator that produces a 1-bit  $\Delta$ - $\Sigma$  modulated bitstream with 24-bits of precision, suit-

able for driving a test DAC to verify the analog performance of the conversion channel. The TBS generator also includes an internal digital loopback option so the digital filters and communication interface can be tested independently of the analog circuitry. The TBS generator can easily be programmed to produce a number of test signals using the included 1024 point sine wave data table. By writing a single configuration register many common test frequencies can be generated, including 31.25 Hz, 50.0 Hz, and 125.0 Hz. Custom test signal frequencies can be generated by writing a new sine wave data table.

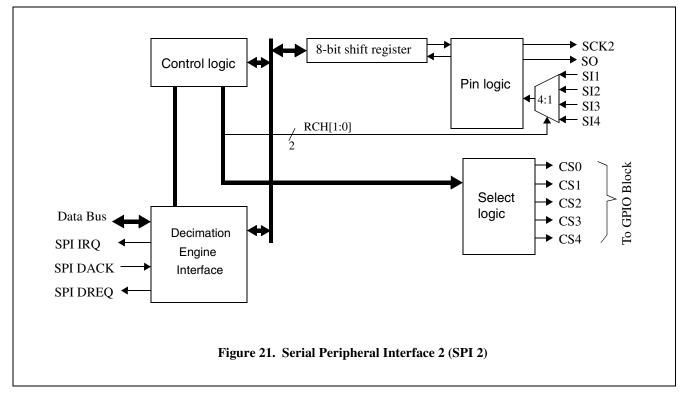

#### Secondary SPI Port

A secondary master mode SPI 2 port allows serial peripherals to be controlled through the primary SPI 1 port. The CS5376 acts as an arbiter to conduct transactions between the communications interface connected to the primary SPI 1 port and serial peripherals connected to the secondary SPI 2 port. This simplifies system design by requiring only one SPI connection to the communication interface to control the CS5376 and multiple serial peripherals.

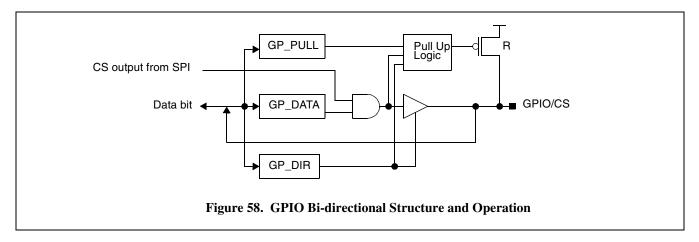

#### General Purpose I/O Pins

Twelve general purpose I/O pins on the CS5376 can be used for local hardware control or as chip selects for the SPI ports. These pins are independently programmable as inputs or outputs, with or without an internal pull-up resistor.

#### JTAG Test Port

The CS5376 includes a standard IEEE 1149.1 JTAG test port for system level testing via boundary scan.

#### **Clock and Synchronization Block**

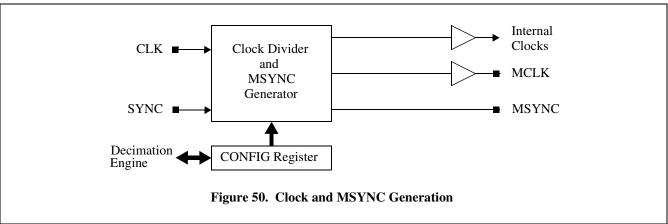

A clock and synchronization block in the CS5376 establishes synchronous timing when used in a distributed measurement network. An input SYNC signal from the host system resets the modulator

sampling instant, digital filter phase, and test bitstream phase to ensure measurement timing is consistent across the network.

#### Time Break Controller

The CS5376 time break controller places a timing reference flag in the status bits of the digital filter output word. This timing reference flag is used to mark measurement events in the digital data, or as a digital sync to align multiple data streams during post-processing. An externally generated TIMEB signal starts a programmable sample counter (used to correct for digital filter group delay), and when it expires the time break flag is set in the next output data word.

#### 2.4 Register Descriptions

#### **Decimation Engine Registers**

Hardware functions and digital filter settings in the

CS5376 are controlled by registers in the decimation engine. A summary of decimation engine registers is shown in Figure 6 on page 12. See "Decimation Engine Registers" on page 99 for a detailed listing of all decimation engine register bit settings.

#### SPI 1 Registers

Decimation engine registers are not directly accessible to the communication interface. Instead, they are indirectly read and written using SPI 1 registers. See "Serial Peripheral Interface 1" on page 21 for a description of how to use the SPI 1 port to access decimation engine registers.

Each 24-bit SPI 1 register is divided into three 8-bit registers consisting of a high, mid, and low byte. A summary of SPI 1 registers is shown in Figure 6 on page 12. See "SPI 1 Registers" on page 94 for a detailed listing of all SPI 1 register bit settings.

# Decimation Engine Registers

| Name     | Addr. | Туре | # Bits | Description                                   |

|----------|-------|------|--------|-----------------------------------------------|

| CONFIG   | 00    | R/W  | 24     | Decimation Engine Configuration               |

| RESERVED | 01-0D | R/W  | 24     | Reserved                                      |

| GPCFG0   | 0E    | R/W  | 24     | GPIO[7:0] Direction, Pullup Enable, and Data  |

| GPCFG1   | 0F    | R/W  | 24     | GPIO[11:8] Direction, Pullup Enable, and Data |

| SPI2CTRL | 10    | R/W  | 24     | SPI 2 Configuration                           |

| SPI2CMD  | 11    | R/W  | 16     | SPI 2 Command                                 |

| SPI2DAT  | 12    | R/W  | 24     | SPI 2 Data                                    |

| RESERVED | 13-1F | R/W  | 24     | Reserved                                      |

| FILT_CFG | 20    | R/W  | 24     | Filter Configuration                          |

| GAIN1    | 21    | R/W  | 24     | Gain Correction Channel 1                     |

| GAIN2    | 22    | R/W  | 24     | Gain Correction Channel 2                     |

| GAIN3    | 23    | R/W  | 24     | Gain Correction Channel 3                     |

| GAIN4    | 24    | R/W  | 24     | Gain Correction Channel 4                     |

| OFFSET1  | 25    | R/W  | 24     | Offset Correction Channel 1                   |

| OFFSET2  | 26    | R/W  | 24     | Offset Correction Channel 2                   |

| OFFSET3  | 27    | R/W  | 24     | Offset Correction Channel 3                   |

| OFFSET4  | 28    | R/W  | 24     | Offset Correction Channel 4                   |

| TIMEBRK  | 29    | R/W  | 24     | Time Break Counter Configuration              |

| TBS_CFG  | 2A    | R/W  | 24     | Test Bit Stream Configuration                 |

| WD_CFG   | 2B    | R/W  | 24     | Watchdog Counter Configuration                |

| SYSTEM1  | 2C    | R/W  | 24     | User Defined System Register 1                |

| SYSTEM2  | 2D    | R/W  | 24     | User Defined System Register 2                |

| VERSION  | 2E    | R/W  | 24     | Hardware Version ID                           |

| SELFTEST | 2F    | R/W  | 24     | Self-Test Result Code                         |

# SPI 1 Registers

| Name     | Addr.   | Туре | # Bits  | Description            |

|----------|---------|------|---------|------------------------|

| SPI1CTRL | 00 - 02 | R/W  | 8, 8, 8 | SPI 1 Control Register |

| SPI1CMD  | 03 - 05 | R/W  | 8, 8, 8 | DE <-> SPI 1 Command   |

| SPI1DAT1 | 06 - 08 | R/W  | 8, 8, 8 | DE <-> SPI 1 Data 1    |

| SPI1DAT2 | 09 - 0B | R/W  | 8, 8, 8 | DE <-> SPI 1 Data 2    |

Figure 6. Decimation Engine and SPI 1 Registers

CS5376

#### 3. SYSTEM DESIGN

System issues to consider when designing with the CS5376 include power supply voltages, distribution of clock and synchronization signals, connections for EEPROM reprogramming, connections for boundary scan testing, and extra circuitry required for functional tests.

#### 3.1 Power Supply Voltages

The CS5376 has three sets of power supply inputs. Two sets supply power to the I/O pins of the chip (VDD1, VDD2), and the third set supplies power to the logic core (VD). The I/O pin power supplies determine the maximum input and output voltages when interfacing to peripherals, and the logic core power supply determines the power consumption of the CS5376.

The voltage choice for a specific power supply depends on two considerations.

1) Available voltages.

It's simpler to drive all power supplies from a single 5 V or 3.3 V supply if it's already available in the design. This reduces system cost by eliminating additional voltage regulators. Power sensitive applications, however, will require a 3 V supply into the logic core to minimize power consumption.

2) Required interface voltages.

The two I/O pin power supplies are separated into a 'modulator side' and a 'microcontroller side'. If some elements in the design are specified to interface at 5 V and other elements in the design are specified to interface at another voltage, 3.3 V for example, the I/O pin power supplies can be independently driven to match.

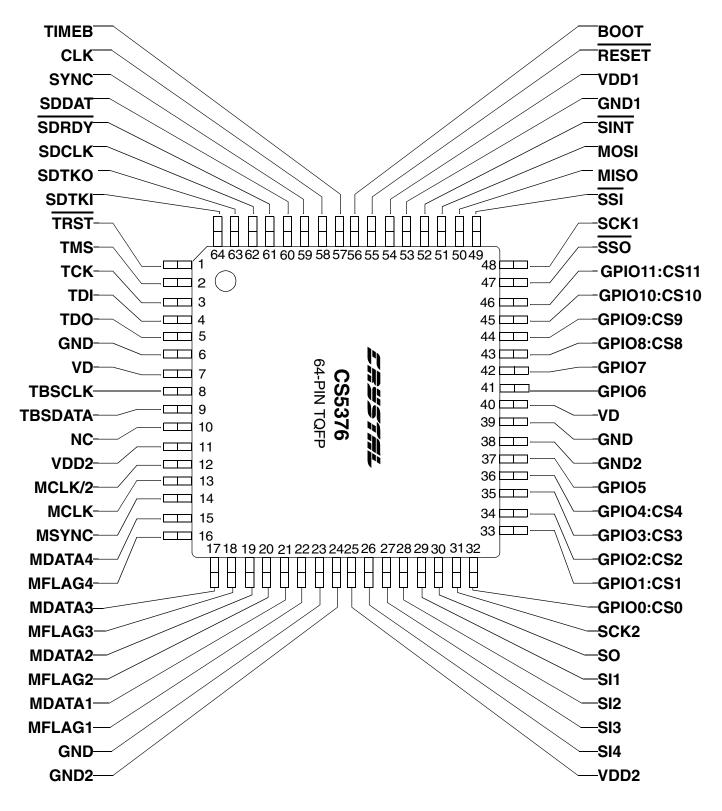

#### VDD1, GND1 - Pins 54, 53

This I/O pin power supply sets the interface voltage to the microcontroller, communications channel, and related peripherals. Pins driven by the VDD1 power supply are:

- RESET, BOOT, CLK, SYNC, TIMEB

- $\overline{SSI}$ , SCK1, MOSI, MISO,  $\overline{SINT}$ ,  $\overline{SSO}$

- SDTKI, SDRDY, SDCLK, SDDAT, SDTKO

- GPIO6 GPIO11

- TRST, TMS, TCK, TDI, TDO

#### VDD2, GND2 - Pins 11, 25, 24, 38

This I/O pin power supply sets the interface voltage to the modulators, test DAC, and related peripherals.

Pins driven by the VDD2 power supply are:

- MDATA1 MDATA4, MFLAG1 MFLAG4

- MCLK, MCLK/2, MSYNC

- SCK2, SI1 SI4, SO

- TBSCLK, TBSDATA

- GPIO0 GPIO5

#### VD, GND - Pins 7, 40, 6, 23, 39

This power supply sets the operational voltage for the CS5376 logic core. Lowering this voltage to 3 V will minimize power consumption.

#### 3.1.1 Bypass Capacitors

All power supply pins should be bypassed to provide noise immunity. The bypass capacitors should be placed as close as possible to the pins of the CS5376, between the power supply pin and its associated ground. Suggested values for bypass capacitors are two parallel caps of 1  $\mu$ F and 0.01  $\mu$ F, or a single cap of 0.1  $\mu$ F. Bypass capacitors can be ceramic, tantalum, or any other dielectric type.

#### 3.2 Clock and Synchronization Signals

Many applications of the CS5376 will use a multichannel distributed measurement network. To be useful, data collection must occur with synchronous timing between the measurement channels.

Careful design of a clock distribution and synchronization network is crucial for keeping these timing relationships consistent.

### CLK - Pin 58

The CS5376 master clock pin, CLK, has a nominal input frequency of 32.768 MHz. A slower master clock can be used if the frequencies from the generated clocks (MCLK, MCLK/2, SCK1, SCK2, and TBSCLK) are permitted to run slower. The CS5376 is a fully static design and can have the master clock gated off to place the system in a low-power standby mode.

#### 3.2.1 Master Clock Jitter and Skew

The clock distribution network should supply a low-jitter, low-skew master clock signal. Clock jitter on the master clock pin, CLK, will result in jitter on all generated clocks. Jitter on the modulator clocks (MCLK, MCLK/2) and the test bit stream clock (TBSCLK) will cause inaccurate conversions of analog-to-digital and digital-to-analog signals. Great care should be taken to ensure recovered clocks have as low jitter as possible.

Clock skew across a measurement network will cause inaccurate results when reconstructing measurement data during post-processing. By making measurements at slightly different instants in time, sensors with clock skew between them cause signals to appear slower or faster than reality. A good measurement network design should minimize clock skew.

#### 3.2.2 Synchronization Jitter and Skew

Similar problems face the distribution of the SYNC signal. The SYNC input on the CS5376 aligns the internal clock edges and digital filter phase to the external system, establishing a precise timing relationship across the measurement network. Jitter and skew on the input SYNC signal will result in phase errors in the CS5376 digital filter data.

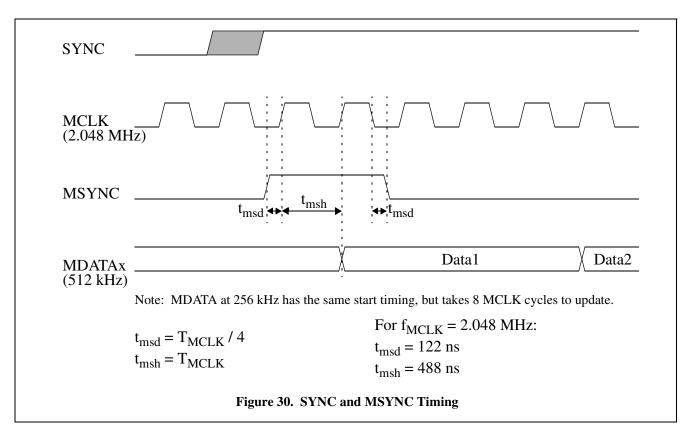

The SYNC signal is also used to generate the MSYNC signal to the modulators. The MSYNC signal synchronizes the modulator sampling instant and ensures all modulators are operating with identical timing across the network. Since the sampling instant is defined by the MSYNC signal, errors generating the SYNC signal will result in measurement timing errors by the modulators.

See "System Synchronization" on page 77 for more information on synchronizing the CS5376 measurement system.

#### 3.3 EEPROM Programming

The CS5376 in stand-alone mode automatically boots from EEPROM after reset. The configuration EEPROM holds the commands and data needed to initialize the system into a fixed operational state. If stand-alone boot mode is used, the system should include a way to address the configuration EE-PROM for in-circuit reprogramming. This can be performed locally by a technician through a connector, or remotely through the communications channel.

See "Serial Peripheral Interface 1" on page 21 for more information about booting the CS5376 using an EEPROM.

#### 3.4 Boundary Scan Testing

During system design and in the field, in-circuit testing is a valuable diagnostic tool. The CS5376 JTAG test port enables boundary scan testing by providing access to all pins via internal boundary scan cells. To use the JTAG test port, a system design must provide in-circuit access to the CS5376 JTAG pins (TRST, TMS, TCK, TDI, and TDO). They can be accessed locally by a technician through a connector, or remotely through the communications channel.

See "JTAG Test Port (IEEE 1149.1)" on page 89 for more information on the JTAG test port.

#### 3.4.1 TRST and RESET Pins

As required by the IEEE 1149.1 specification, the JTAG reset signal,  $\overline{\text{TRST}}$ , is independent of the CS5376 reset signal,  $\overline{\text{RESET}}$ . The status of the TRST pin should be considered during system design since the TAP controller must be reset before using the JTAG port.

In systems not using the JTAG test port, the TRST pin can be connected directly to the RESET pin, or can be connected to ground. In systems using the JTAG test port, the TRST and RESET pins should be independently driven to provide reset capability during boundry scan.

#### 3.5 Functional Testing

While boundary scan testing gives the ability to check connections between circuit elements, testing the functionality of the circuit elements themselves requires operation of the measurement channel.

#### 3.5.1 Analog Test DAC

To test the full signal path of a CS5376 system, an analog test signal should be applied to the modulator inputs. The CS5376 provides a test bit stream generator that produces a  $\Delta$ - $\Sigma$  bit stream suitable for driving an external test DAC. The analog output signal from the DAC can be multiplexed to the inputs of the measurement channel through relays or analog multiplexers. Switching the analog test signal into the measurement channel is typically performed on command from the communication channel, and requires appropriate control signals to be defined during system design.

Included as part of the CS5376 test bit stream generator is an internal feedback path into the digital filters. This loopback mode provides a fully digital signal path to test the digital filters and communications interface. If this is the only test mode used, no external circuitry is required.

See "Test Bit Stream Generator" on page 81 for more information about using the test bit stream generator.

#### 3.5.2 Step Input and Group Delay

Characterizing the step response of a combination analog and digital measurement channel can be difficult. A simple method to empirically measure the step response and group delay through the analog and digital portions of a CS5376 measurement channel is to use the time break signal as both a timing reference and an analog step input. This test requires the system design to include relays or analog multiplexers to connect the time break signal to the analog inputs.

See "Time Break Function" on page 75 for more information about the time break signal.

#### 3.6 System Registers

Several registers are included in the CS5376 for system information.

The VERSION register (0x2E) in the decimation engine holds hardware version ID information.

Two registers in the decimation engine, SYSTEM1 and SYSTEM2 (0x2C, 0x2D), are provided for user defined system information. These are general purpose registers and will hold any 24-bit data values written to them.

# 3.6.1 VERSION Register - 0x2E

| (MSB) 23 | 22    | 21    | 20    | 19    | 18    | 17    | 16      |

|----------|-------|-------|-------|-------|-------|-------|---------|

| TYPE7    | TYPE6 | TYPE5 | TYPE4 | TYPE3 | TYPE2 | TYPE1 | TYPE0   |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 1     | 1     | 1     | 0     | 1     | 1     | 0       |

| •        |       | •     | •     | •     |       | •     |         |

| 15       | 14    | 13    | 12    | 11    | 10    | 9     | 8       |

| HW7      | HW6   | HW5   | HW4   | HW3   | HW2   | HW1   | HW0     |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 0     | 0     | 0     | 1       |

| •        |       | •     | •     | •     |       | •     |         |

| 7        | 6     | 5     | 4     | 3     | 2     | 1     | (LSB) 0 |

| ROM7     | ROM6  | ROM5  | ROM4  | ROM3  | ROM2  | ROM1  | ROM0    |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 0     | 0     | 0     | 1       |

#### Figure 7. Hardware Version ID Register VERSION

| I/O Address: 0x2E |                                                                               |  |

|-------------------|-------------------------------------------------------------------------------|--|

| <br>R<br>W<br>R/W | Not defined;<br>read as 0<br>Readable<br>Writable<br>Readable and<br>Writable |  |

| 2100 111          | bottom rows<br>et condition                                                   |  |

|                   |                                                                               |  |

| 23:16 | TYPE<br>[7:0] | Chip Type<br>76 - CS5376 | 15:8 | HW<br>[7:0] | Hardware Revision<br>01 - Rev A | 7:4 | ROM<br>[7:0] | ROM Version<br>01 - Ver 1.0 |

|-------|---------------|--------------------------|------|-------------|---------------------------------|-----|--------------|-----------------------------|

|       | []            |                          |      | []          |                                 |     | [,]          |                             |

# 3.6.2 SYSTEM1, SYSTEM2 Registers - 0x2C, 0x2D

| (MSB) 23 | 22    | 21    | 20    | 19    | 18    | 17    | 16      |

|----------|-------|-------|-------|-------|-------|-------|---------|

| SYS23    | SYS22 | SYS21 | SYS20 | SYS19 | SYS18 | SYS17 | SYS16   |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0       |

|          |       | -     | -     |       |       | -     |         |

| 15       | 14    | 13    | 12    | 11    | 10    | 9     | 8       |

| SYS15    | SYS14 | SYS13 | SYS12 | SYS11 | SYS10 | SYS9  | SYS8    |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0       |

|          |       |       |       |       |       |       |         |

| 7        | 6     | 5     | 4     | 3     | 2     | 1     | (LSB) 0 |

| SYS7     | SYS6  | SYS5  | SYS4  | SYS3  | SYS2  | SYS1  | SYS0    |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0       |

#### Figure 8. User Defined System Register SYSTEM1

| I/O Ad  | I/O Address: 0x2C      |  |  |

|---------|------------------------|--|--|

|         | Not defined; read as 0 |  |  |

| R       | Readable               |  |  |

| W       | Writable               |  |  |

| R/W     | Readable and           |  |  |

|         | Writable               |  |  |

| Bits in | bottom rows            |  |  |

| are res | et condition           |  |  |

|         |                        |  |  |

| 23:16 SYS[23:16] | System Register<br>Upper Byte | 15:8 | SYS[15:8] | System Register<br>Middle Byte | 15:8 | SYS[7:0] | System Register<br>Lower Byte |

|------------------|-------------------------------|------|-----------|--------------------------------|------|----------|-------------------------------|

|                  |                               |      |           |                                |      |          |                               |

#### 4. RESET CONTROL

When the  $\overline{\text{RESET}}$  signal is released, the CS5376 automatically performs a series of self-tests. Depending on the state of the BOOT pin, it then either actively boots from EEPROM or waits for configuration information to be written by a microcontroller.

#### 4.1 Reset Pin Descriptions

#### **RESET** - Pin 55

**RESET** is an active low signal that places the CS5376 into a reset state when asserted.

#### BOOT - Pin 56

The BOOT signal selects how the CS5376 loads configuration information. The logic state of this pin is latched 1  $\mu$ s after RESET is released to select between coprocessor or stand-alone boot modes. A logical low selects coprocessor boot mode, a logical high selects stand-alone boot mode.

#### 4.2 Boot Configurations

When booting in coprocessor mode, a microcontroller or other SPI bus master is required to write configuration information. When booting in standalone mode, the CS5376 reads configuration information from EEPROM and no microcontroller is required. A hybrid mode can also be used which reads an initial configuration from EEPROM and then writes changes using a microcontroller.

#### **Coprocessor Mode**

Coprocessor mode is designed for systems required to run multiple configurations from a common set of hardware. The ability to change configurations in real time gives maximum flexibility in the field.

This mode requires a microcontroller or other SPI bus master to be connected to the CS5376 SPI 1 port. The microcontroller can rewrite the filter coefficients, change the filter output stage, enable and disable the test bit stream, and manually update the gain and offset correction values during operation. To set the CS5376 configuration, the microcontroller writes a series of command and data values to the decimation engine through the SPI 1 port. See "Serial Peripheral Interface 1" on page 21 for more information on connecting a microcontroller to the SPI 1 port.

#### Stand-Alone Mode

If the CS5376 is designed into a system with a fixed configuration, no microcontroller is required. Stand-alone mode boots from EEPROM to a fixed configuration and immediately begins operation. The EEPROM contains all configuration information including filter coefficients, register settings, and test bit stream data.

It might not be possible to know the gain and offset correction values in advance of deploying a system. If the configuration EEPROM is in-circuit reprogrammable, the system can be booted with offset and gain correction disabled and the appropriate correction values calculated. The new correction values can then be programmed into the EEPROM and the CS5376 re-booted with gain and offset correction enabled.

See "Serial Peripheral Interface 1" on page 21 for more information on booting from a configuration EEPROM, and the format required for EEPROM data.

#### Hybrid Mode

A boot configuration that requires more engineering effort to implement is a hybrid coprocessor / stand-alone boot mode. In hybrid mode the CS5376 initially boots in stand-alone mode from a configuration EEPROM. After booting, a microcontroller updates the configuration information in coprocessor mode by writing commands to the decimation engine through the SPI 1 port.

Hybrid mode is more complex at the system level because it requires the ability to tri-state the micro-

controller to SPI 1 connection during the initial EE-PROM boot. After the initial configuration is loaded, the microcontroller seizes control of the SPI 1 port and updates the configuration as required. The EEPROM will not interfere with microcontroller to SPI 1 transactions provided the initial stand-alone boot was completed.

Updated configuration information from the microcontroller can not be written until the EEPROM boot loader has relinquished control of the SPI 1 port. To guarantee this, the microcontroller should monitor the CS5376 CS11 / GPIO11 pin into the EEPROM for inactivity, or simply wait the maximum time required to boot from EEPROM. The required boot time from EEPROM depends on the number of coefficients written, the number of registers written, and if test bit stream data is written.

A final requirement for hybrid boot mode is the ability to address both the CS5376 and the configuration EEPROM. When writing to the CS5376 SPI 1 port, serial transactions use an 8-bit address. Supported serial EEPROMs, however, require serial transactions to use 16-bit addressing. If a microcontroller is to interface with the CS5376 and also be able to in-circuit reprogram the configuration EEPROM, the serial port connection must support both addressing modes.

See "Serial Peripheral Interface 1" on page 21 for information about connections to the SPI 1 port, the format required for EEPROM data, and the SPI 1 commands available for updating the configuration.

#### 4.3 Reset Self-Tests

After the reset signal is de-asserted but before the CS5376 starts the boot operation, a series of self test are run. These tests check the operation of the decimation engine and report pass/fail codes in the SELFTEST register (0x2F). The full suite of self tests require approximately 60ms to complete.

#### **Program ROM Test**

This self-test calculates a checksum from the contents of program ROM and compares against an expected value. The result of this test is 0x00000A if passed or 0x00000F if failed.

#### Data ROM Test

This self-test calculates a checksum from the contents of data ROM and compares against an expected value. The result of this test is 0x0000A0 if passed or 0x0000F0 if failed.

### Program RAM Test

This self-test writes a series of patterns into the program RAM and compares against expected read values. The result of this test is 0x000A00 if passed or 0x000F00 if failed.

### Data RAM Test

This self-test writes a series of patterns into the data RAM and compares against expected read values. The result of this test is 0x00A000 if passed or 0x00F000 if failed.

### **Execution Unit Test**

This self-test exercises the execution unit with a sequence of calculations, comparing against expected values. The result of this test is 0x0A0000 if passed or 0x0F0000 if failed.

# 4.3.1 SELFTEST Register - 0x2F

| (MSB) 23 | 22    | 21    | 20    | 19    | 18    | 17    | 16      |

|----------|-------|-------|-------|-------|-------|-------|---------|

|          |       |       |       | EU3   | EU2   | EU1   | EU0     |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 0        | 0     | 0     | 0     | 1     | 0     | 1     | 0       |

|          |       |       |       |       |       |       |         |

| 15       | 14    | 13    | 12    | 11    | 10    | 9     | 8       |

| DRAM3    | DRAM2 | DRAM1 | DRAM0 | PRAM3 | PRAM2 | PRAM1 | PRAM0   |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 1        | 0     | 1     | 0     | 1     | 0     | 1     | 0       |

|          |       |       |       |       |       |       |         |

| 7        | 6     | 5     | 4     | 3     | 2     | 1     | (LSB) 0 |

| DROM3    | DROM2 | DROM1 | DROM0 | PROM3 | PROM2 | PROM1 | PROM0   |

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |

| 1        | 0     | 1     | 0     | 1     | 0     | 1     | 0       |

#### Figure 9. Self Test Result Register SELFTEST

| I/O Ac            | dress: 0x2F                                                                   |

|-------------------|-------------------------------------------------------------------------------|

| <br>R<br>W<br>R/W | Not defined;<br>read as 0<br>Readable<br>Writable<br>Readable and<br>Writable |

|                   | bottom rows<br>et condition                                                   |

| 23:20 |             | reserved                                      | 15:12 | DRAM<br>[3:0] | Data RAM Test<br>'A': Pass<br>'F': Fail    | 7:4 | DROM<br>[3:0] | Data ROM Test<br>'A': Pass<br>'F': Fail    |

|-------|-------------|-----------------------------------------------|-------|---------------|--------------------------------------------|-----|---------------|--------------------------------------------|

| 19:16 | EU<br>[3:0] | Execution Unit Test<br>'A': Pass<br>'F': Fail | 11:8  | PRAM<br>[3:0] | Program RAM Test<br>'A': Pass<br>'F': Fail | 3:0 | PROM<br>[3:0] | Program ROM Test<br>'A': Pass<br>'F': Fail |

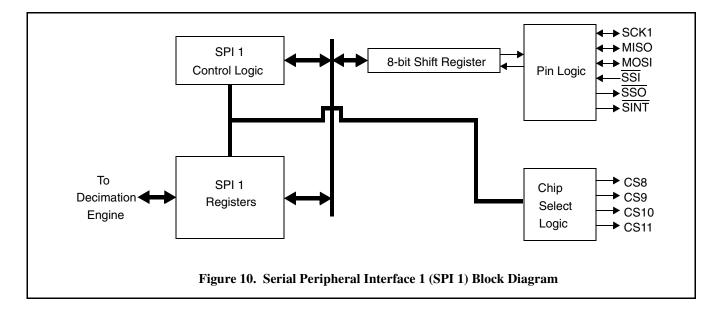

#### 5. SERIAL PERIPHERAL INTERFACE 1

The Serial Peripheral Interface 1 (SPI 1) port is an industry standard master / slave SPI interface, and is the primary interface to the CS5376 decimation engine. The port operates as an SPI bus master when booting from a configuration EEPROM in stand-alone mode, and as an SPI slave when communicating with a microcontroller in coprocessor mode.

#### Master Mode

The SPI 1 port operates in master mode only while loading configuration information from EEPROM during stand-alone boot mode. In this mode the CS5376 actively initiates serial transactions to read configuration register values, digital filter coefficients, and test bit stream data from EEPROM memory. After booting from EEPROM, the SPI 1 port reverts to slave mode to interface with a microcontroller, if present.

Master mode serial transactions in the CS5376 generate a chip select output on the CS11 / GPIO11 pin, and a serial clock output on the SCK1 pin. Serial data is output from the CS5376 on the MOSI pin, and input from the EEPROM on the MISO pin. To be compatible with many serial EEPROMs, transactions in master mode use 16-bit addresses, different from the 8-bit addresses required when accessing the CS5376 in slave mode.

#### Slave Mode

When booting from a microcontroller in coprocessor mode, or after booting from EEPROM in standalone mode has completed, the SPI 1 port operates in slave mode. In slave mode the CS5376 is passive, with serial transactions initiated by a microcontroller or other SPI bus master. The microcontroller uses SPI 1 commands to write configuration register values, digital filter coefficients, and test bit stream data from a local memory or from the communications channel.

Slave mode serial transactions require the microcontroller to use the  $\overline{SSI}$  pin as the CS5376 chip select, and to generate a serial clock input on the SCK1 pin. Serial data is received from the microcontroller on the MOSI pin, and output from the CS5376 on the MISO pin.

When pulled low the  $\overline{SSI}$  pin (Slave Select Input) places the SPI 1 port into a default configuration that requires 8-bit addresses, different from the 16-

bit addresses generated when accessing an EE-PROM in master mode.

#### 5.1 SPI 1 Pin Descriptions

The Serial Peripheral Interface 1 port is a standard 3-wire, bidirectional, synchronous serial interface. The SCK1, MISO, and MOSI pins, along with either the CS11 or  $\overline{SSI}$  chip select pins, are used to interface the decimation engine of the CS5376 to external serial devices. Several miscellaneous pins,  $\overline{SINT}$ ,  $\overline{SSO}$ , and CS8 - CS10 are not used but are defined to make the SPI 1 port extensible in the future.

#### CS11 - Pin 46

Master mode chip select output pin, active low. EE-PROM chip select signal automatically generated when booting in stand-alone mode.

#### **SSI** - Pin 49

Slave mode chip select input pin, active low. Chip select signal that places the SPI 1 port into slave mode to receive commands from a microcontroller.

#### SCK1 - Pin 48

Master mode serial clock output, slave mode serial clock input. In both modes a serial clock rising edge indicates valid data, a falling edge indicates a data transition.

In master mode the SCK1 pin is an output that generates a serial clock to read data from the configuration EEPROM. The serial clock output rate in master mode defaults to 1.024 MHz.

In slave mode the SCK1 pin is an input that receives a serial clock from a microcontroller. The serial clock input rate in slave mode can be any rate up to a maximum of 4.096 MHz.

#### MOSI - Pin 51

Master Out, Slave In data pin. Data output in master mode, data input in slave mode. Data is valid on the rising edge of SCK1, and transitions on the falling edge.

#### MISO - Pin 50

Master In, Slave Out data pin. Data input in master mode, data output in slave mode. Data is valid on the rising edge of SCK1, and transitions on the falling edge.

### SINT - Pin 52

SPI 1 interrupt output pin, active low. A pulsed output indicates data was written to the SPI 1 registers by the decimation engine. Not used by CS5376 rev A, reserved for future revisions.

#### **SSO** - Pin 47

Slave select output pin, active low. Chip select output that mirrors the  $\overline{SSI}$  pin. Not used by CS5376 rev A, reserved for future revisions.

#### CS8 - CS10 - Pins 43 - 46

Additional chip selects for SPI 1 master mode. Not used by CS5376 rev A, reserved for future revisions.

#### 5.2 SPI 1 Stand-Alone Mode

In stand-alone mode, the SPI 1 port operates as an SPI bus master to load configuration information from an EEPROM. Commands to write configuration registers, filter coefficients, and test bit stream data are programmed into the EEPROM along with the required data words.

The CS5376 automatically reads 1-byte command and 3-byte data words from EEPROM memory until the 'Filter Start' command is received. The 'Filter Start' command initializes the CS5376 digital filters and places the SPI 1 port into slave mode. See "SPI 1 Coprocessor Mode" on page 27 for more information about SPI 1 slave mode.

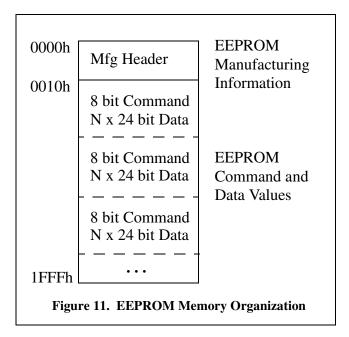

### 5.2.1 EEPROM Organization

The configuration EEPROM is programmed with a series of command and data values. Commands are one byte (8-bit) values that select the type of EE-PROM loader operation. Data words are three byte (24-bit) values used by the EEPROM loader.

The CS5376 expects EEPROM programming to start at memory location 0x10, with the bytes from 0x00 to 0x0F defined for manufacturing header information. The first CS5376 to EEPROM transaction reads a 1-byte command from memory location 0x10. Depending on the command type, multiple 3-byte data words are read to complete the command. The CS5376 continues reading command and data values until the 'Filter Start' command is recognized. Figure 11 illustrates the organization of an 8 Kbyte (64 Kbit) configuration EEPROM.

The maximum data that can be written for a single configuration is approximately 5 Kbyte (40 Kbit), which includes command overhead:

- 22 Configuration Registers, 154 bytes

- 255 + 255 FIR Coefficients, 1537 bytes

- 3 + 5 IIR Coefficients, 25 bytes

- 1024 Test Bit Stream Data, 3076 bytes

- Filter Start Command, 1 byte

Supported serial configuration EEPROMs are SPI mode 0 (0,0) compatible, 16-bit addresses, 8bit data, and larger than 5 Kbyte. ATMEL AT25640, AT25128, or similar serial EEPROMs are recommended.

### 5.2.2 EEPROM Commands

The configuration EEPROM contains a series of 1byte command and 3-byte data words. After an EE-PROM command is read, multiple data words are read to complete the programmed operation. Not all EEPROM commands require additional data words.

EEPROM commands can write decimation engine registers, write FIR filter coefficients, write IIR filter coefficients, write test bitstream data, and start the digital filters. A summary of available EE-PROM commands is shown in Figure 12 on page 24.

### Write Register - 0x01

| Туре | Description                   |

|------|-------------------------------|

| CMD  | 0x01 - Register Write Command |

| DATA | Register Address              |

| DATA | Register Write Data           |

This EEPROM command writes a data value to the specified decimation engine register. Decimation engine registers control hardware and filtering functions. See "Decimation Engine Registers" on page 99 for information about the bit definitions of the decimation engine registers.

| EEPROM Command         | Command Opcode | Data Format <sup>1</sup>                        |

|------------------------|----------------|-------------------------------------------------|

| Nop                    | 0x00           |                                                 |

| Write I/O Register     | 0x01           | Address<br>Write Data                           |

| Write FIR Coefficients | 0x02           | Num FIR1 Coeff<br>Num FIR2 Coeff<br>(FIR Coeff) |

| Write IIR Coefficients | 0x03           | (IIR Coeff)                                     |

| Write ROM Coefficients | 0x04           |                                                 |

| Write TBS Data         | 0x05           | Num TBS Data<br>(TBS Data)                      |

| Write ROM TBS Data     | 0x06           |                                                 |

| Filter Start           | 0x07           |                                                 |

<sup>1</sup> (data) indicates multiple data words of this type to be written.

Figure 12. EEPROM Boot Loader Commands

#### Write FIR Coefficients - 0x02

| Туре | Description                      |

|------|----------------------------------|

| CMD  | 0x02 - FIR Coefficient Write Cmd |

| DATA | Number of FIR1 Coefficients      |

| DATA | Number of FIR2 Coefficients      |

| DATA | (FIR Coefficients)               |

This EEPROM command writes custom coefficients for the FIR1 and FIR2 filters. The first two

data words set the number of FIR1 and FIR2 coefficients to be written. The remaining data words are the concatenated FIR1 and FIR2 coefficients.

A maximum of 255 coefficients can be written for each FIR filter, though the available decimation engine computation cycles will limit their practical size. See "FIR Filters" on page 60 for more information about the FIR filters and the cycle limitations of the decimation engine.

#### Write IIR Coefficients - 0x03

| Туре | Description                      |

|------|----------------------------------|

| CMD  | 0x03 - IIR Coefficient Write Cmd |

| DATA | IIR Coefficient a11              |

| DATA | IIR Coefficient b10              |

| DATA | IIR Coefficients b11             |

| DATA | IIR Coefficients a21             |

| DATA | IIR Coefficients a22             |

| DATA | IIR Coefficients b20             |

| DATA | IIR Coefficients b21             |

| DATA | IIR Coefficients b22             |

This EEPROM command uploads custom coefficients for the two stage IIR filter. The IIR architecture and number of coefficients is fixed, so eight data words containing coefficient values immediately follow the command byte. The IIR coefficient write order is: a11, b10, b11, a21, a22, b20, b21, and b22.

The IIR filter consists of a 1st order filter requiring three coefficients (a11, b10, b11) and a 2nd order filter requiring five coefficients (a21, a22, b20, b21, b22). A 3rd order filter is implemented by running both the 1st and 2nd order filters. See "IIR Filter" on page 61 for more information about the IIR filter.

#### Write ROM Coefficients - 0x04

| Туре | Description                      |

|------|----------------------------------|

| CMD  | 0x04 - ROM Coefficient Write Cmd |

This EEPROM command writes the on-chip reference coefficients for FIR1, FIR2, IIR 1st order, and IIR 2nd order filters for use by the decimation engine. No data words are required for this EEPROM command. See "Reference Coefficients" on page 63 for more information about the reference FIR and IIR coefficient sets.

#### Write TBS Data - 0x05

| Туре | Description               |

|------|---------------------------|

| CMD  | 0x05 - TBS Data Write Cmd |

| DATA | Number of TBS Data        |

| DATA | (TBS Data)                |

This EEPROM command uploads a custom data set for the test bit stream (TBS) generator. The first data word sets the number of TBS data to be written and the remaining data words are the TBS data values.

This command, along with the ability to program the test bit stream generator interpolation and clock rate, allows the creation of custom frequency test signals. See "Test Bit Stream Generator" on page 81 for information on generating specific test frequencies using custom test bit stream data sets.

#### Write ROM TBS Data - 0x06

| Туре | Description                   |

|------|-------------------------------|

| CMD  | 0x06 - TBS ROM Data Write Cmd |

This EEPROM command writes the on-chip test bit stream (TBS) data for use by the TBS generator. No data words are required for this EEPROM command. See "Test Bit Stream Generator" on page 81 for information on generating test frequencies using the on-chip test bit stream data set.

#### Filter Start - 0x07

| Туре | Description                 |

|------|-----------------------------|

| CMD  | 0x07 - Filter Start Command |

This EEPROM command initializes the decimation engine and starts the digital filters. It also ends the EEPROM boot loader operation and places the SPI 1 port into slave mode. No data words are required for this EEPROM command.

After receiving the Filter Start command, the decimation engine uses the filter configuration specified in the FILT\_CFG register (0x20) and filter

coefficients specified by prior EEPROM commands.

#### 5.2.3 CS5376 to EEPROM Transactions

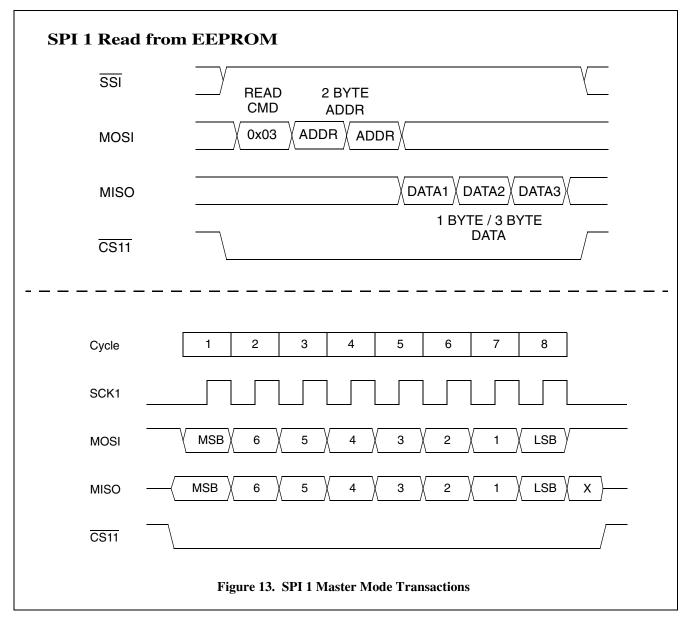

When reading data from EEPROM in stand-alone boot mode, the SPI 1 port operates as a bus master. Two types of serial transactions are generated by the CS5376, command reads and data reads. Command reads are 4-byte serial transactions to read a command byte, and data reads are 6-byte serial transactions to read a data word. Master mode CS5376 to EEPROM transaction timing is shown in Figure 13.

#### **Command Read Transactions**

A CS5376 to EEPROM command read transaction reads a 1-byte command from EEPROM memory. It requires a 4-byte serial transaction to complete: a 1-byte SPI 'read' opcode (0x03), a 2-byte EE-PROM address, and the returned 1-byte command value. Based on the returned command value, the

CS5376 initiates multiple data read transactions to complete the command.

The CS5376 initiates a command read transaction by pulling the CS11 / GPIO11 pin low to act as the EEPROM chip select. It then writes serial clocks to the SCK1 pin, writes the SPI 'read' opcode and EE-PROM address to the MOSI pin, and reads the returned command value from the MISO pin. All MOSI and MISO data are shifted MSB first, with data valid on the rising edge of SCK1 and transitioning on the falling edge.

#### Data Read Transactions

A CS5376 to EEPROM data read transaction reads a 3-byte data word from EEPROM memory. It requires a 6-byte serial transaction to complete: a 1byte SPI 'read' opcode (0x03), a 2-byte EEPROM address, and the returned 3-byte data value. Depending on the command type, the CS5376 initiates multiple data reads to complete it.

The CS5376 initiates a data read transaction by pulling the CS11 / GPIO11 pin low to act as the EEPROM chip select. It then writes serial clocks to the SCK1 pin, writes the SPI 'read' opcode and EE-PROM address to the MOSI pin, and reads the returned data value from the MISO pin. All MOSI and MISO data are shifted MSB first, with data valid on the rising edge of SCK1 and transitioning on the falling edge.

#### 5.3 SPI 1 Coprocessor Mode

In coprocessor mode the CS5376 operates as an SPI slave. A microcontroller or other SPI bus master initiates serial transactions to the SPI 1 port to write configuration information and start the digital filters. Coprocessor mode is the most flexible method of configuring the CS5376 since it permits real time changes to the measurement setup.

The CS5376 digital filters and embedded test functions are configured by writing command and data values to the decimation engine. The decimation engine is not directly addressable through the SPI 1 port, but instead the command and data values are written indirectly through a set of SPI 1 registers. Available SPI 1 coprocessor mode commands can read or write the decimation engine registers, write digital filter coefficients, write test bit stream data, and enable or disable the digital filters.

#### 5.3.1 SPI 1 Registers

Coprocessor mode commands are invoked by writing command and data values to a set of SPI 1 registers. The SPI1CTRL, SPI1CMD, SPI1DAT1, and SPI1DAT2 registers are 24-bit registers mapped into an 8-bit register space as high, mid, and low bytes.

SPI 1 registers are separate from decimation engine registers, with only SPI 1 registers directly addressable by a microcontroller or other SPI bus master. Decimation engine registers are read or written with the 'Read Register' or 'Write Register' SPI 1 commands.

| Name      | Addr.   | Туре | # Bits  | Description            |

|-----------|---------|------|---------|------------------------|

| SPI1CTRLH | 00 - 02 | R/W  | 8, 8, 8 | SPI 1 Control Register |

| SPI1CMDH  | 03 - 05 | R/W  | 8, 8, 8 | DE <-> SPI 1 Command   |

| SPI1DAT1H | 06 - 08 | R/W  | 8, 8, 8 | DE <-> SPI 1 Data 1    |

| SPI1DAT2H | 09 - 0B | R/W  | 8, 8, 8 | DE <-> SPI 1 Data 2    |

Figure 14. SPI 1 Register Space

# 5.3.2 SPI1CTRL Register

| (MSB) 23 | 22    | 21     | 20     | 19   | 18      | 17      | 16      |

|----------|-------|--------|--------|------|---------|---------|---------|

|          |       | SCK1PO | SCK1PH | WOM  | SCK1FS2 | SCK1FS1 | SCK1FS0 |

| R/W1     | R/W1  | R/W    | R/W    | R/W  | R/W     | R/W     | R/W     |

| 0        | 0     | 0      | 0      | 1    | 0       | 1       | 1       |

|          |       |        |        |      |         |         |         |

| 15       | 14    | 13     | 12     | 11   | 10      | 9       | 8       |

| SMODF    | PROM  | DEOP   | EMOP   | SWEF | SINT    | IEN     | E2DREQ  |

| R        | R/W   | R      | R      | R    | R/W     | R/W     | R/W     |

| 0        | 0     | 0      | 0      | 0    | 0       | 0       | 0       |

|          |       | •      | •      |      | •       |         |         |

| 7        | 6     | 5      | 4      | 3    | 2       | 1       | (LSB) 0 |

| DNUM2    | DNUM1 | DNUM0  | CS11   | CS10 | CS9     | CS8     | D2SREQ  |

| R/W      | R/W   | R/W    | R/W    | R/W  | R/W     | R/W     | R/W     |

| 0        | 0     | 1      | 0      | 0    | 0       | 0       | 0       |

#### Figure 15. SPI Control Register SPI1CTRL

| SPI 1 | Address: 0x00<br>0x01<br>0x02 |

|-------|-------------------------------|

|       | Not defined;                  |

| D     | read as 0                     |

| R     | Readable                      |

| W     | Writable                      |

| R/W   | Readable and                  |

|       | Writable                      |

|       | bottom rows<br>et condition   |

| 23:22 |                 | reserved                                                                                         | 15 | SMODF  | SPI 1 mode fault error                              | 7:5 | DNUM<br>[2:0] | DE number of bytes in transaction (1-8 or 2-9)                                     |

|-------|-----------------|--------------------------------------------------------------------------------------------------|----|--------|-----------------------------------------------------|-----|---------------|------------------------------------------------------------------------------------|

| 21    | SCK1PO          | SCK1 polarity<br>1: On falling edge<br>0: On rising edge                                         | 14 | PROM   | PROM mode<br>1: 2-byte address<br>0: 1-byte address | 4   | CS11          | SPI 1 chip select 11                                                               |

| 20    | SCK1PH          | SCK1 phase<br>1: Data out at first SCK1<br>edge<br>0: Data out before first<br>SCK1 edge         | 13 | DEOP   | DE to SPI 1 operation in progress                   | 3   | CS10          | SPI 1 chip select 10                                                               |

| 19    | WOM             | <ul><li>Wired-OR logic</li><li>1: Enabled (open drain)</li><li>0: Disabled (push-pull)</li></ul> | 12 | EMOP   | External master to SPI 1 operation in progress      | 2   | CS9           | SPI 1 chip select 9                                                                |

| 18:16 | SCK1FS<br>[2:0] | SCK1 output freq.<br>111: reserved                                                               | 11 | SWEF   | SPI 1 write collision<br>error flag                 | 1   | CS8           | SPI 1 chip select 8                                                                |

|       |                 | 110: reserved<br>101: 4.096 MHz<br>100: 2.048 MHz<br>011: 1.024 MHz<br>(default)                 | 10 | SINT   | Serial Interrupt                                    | 0   | D2SREQ        | DE to SPI request<br>1: Request operation<br>0: Operation done<br>(cleared by SPI) |

|       |                 | (default)<br>010: 512 kHz                                                                        | 9  | IEN    | SPI 1 Interrupt enable                              |     |               |                                                                                    |

|       |                 | 001: 256 kHz<br>000: 32 kHz                                                                      | 8  | E2DREQ | External master to DE request                       |     |               |                                                                                    |

|       |                 |                                                                                                  |    |        |                                                     |     |               |                                                                                    |

# 5.3.3 SPI1CMD Register

| S     | 16      | 17      | 18      | 19      | 20      | 21      | 22      | (MSB) 23 |

|-------|---------|---------|---------|---------|---------|---------|---------|----------|

|       | S1CMD16 | S1CMD17 | S1CMD18 | S1CMD19 | S1CMD20 | S1CMD21 | S1CMD22 | S1CMD23  |

|       | R/W      |

|       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        |

| -   - |         |         |         |         |         |         |         |          |

|       | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15       |

| ]     | S1CMD8  | S1CMD9  | S1CMD10 | S1CMD11 | S1CMD12 | S1CMD13 | S1CMD14 | S1CMD15  |

|       | R/W      |

|       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        |

|       |         |         |         |         |         |         |         |          |

|       | (LSB) 0 | 1       | 2       | 3       | 4       | 5       | 6       | 7        |

|       | S1CMD0  | S1CMD1  | S1CMD2  | S1CMD3  | S1CMD4  | S1CMD5  | S1CMD6  | S1CMD7   |

| 6     | R/W      |

|       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0        |

#### Figure 16. SPI 1 Command Register SPI1CMD

| SPI 1      | Address: 0x03<br>0x04<br>0x05                     |

|------------|---------------------------------------------------|

| <br>R<br>W | Not defined;<br>read as 0<br>Readable<br>Writable |

| R/W        | Readable and<br>Writable                          |

|            | bottom rows<br>et condition                       |

| 23:16 | S1CMD[23:16] | SPI 1 Command | 15:8 | S1CMD[15:8] | SPI 1 Command | 15:8 | S1CMD[7:0] | SPI 1 Command Low |

|-------|--------------|---------------|------|-------------|---------------|------|------------|-------------------|

|       |              | High Byte     |      |             | Middle Byte   |      |            | Byte              |

|       |              |               |      |             |               |      |            |                   |

# 5.3.4 SPI1DAT1 Register

| (MSB) 23 | 22      | 21      | 20      | 19      | 18      | 17      | 16      |

|----------|---------|---------|---------|---------|---------|---------|---------|

| S1DAT23  | S1DAT22 | S1DAT21 | S1DAT20 | S1DAT19 | S1DAT18 | S1DAT17 | S1DAT16 |

| R/W      | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

|          |         |         | •       | •       |         |         | •       |

| 15       | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

| S1DAT15  | S1DAT14 | S1DAT13 | S1DAT12 | S1DAT11 | S1DAT10 | S1DAT9  | S1DAT8  |

| R/W      | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

|          |         |         | •       | •       |         |         | •       |

| 7        | 6       | 5       | 4       | 3       | 2       | 1       | (LSB) 0 |

| S1DAT7   | S1DAT6  | S1DAT5  | S1DAT4  | S1DAT3  | S1DAT2  | S1DAT1  | S1DAT0  |

| R/W      | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

#### Figure 17. SPI 1 Data Register SPI1DAT1

| SPI 1   | Address:           | 0x06<br>0x07<br>0x08 |

|---------|--------------------|----------------------|

|         | Not def<br>read as | ,                    |

| R       | Readab             | le                   |

| W       | Writabl            | e                    |

| R/W     | Readab             | le and               |

|         | Writabl            | e                    |