# Low Side PWM FET Controller

## Description

The CS7054 is a monolithic integrated circuit designed primarily to control the rotor speed of permanent magnet, direct current (DC) brush motors. It drives the gate of an N channel power MOSFET or IGBT with a user-adjustable, fixed frequency, variable duty cycle, pulse width modulated (PWM) signal. The CS7054 can also be used to control other loads such as incandescent bulbs and solenoids. Inductive current from the motor or solenoid is recirculated through an external diode.

The CS7054 accepts a DC level input signal of 0 to 5V to control the pulse width of the output signal. This signal can be generated by a

potentiometer referenced to the onchip 5V linear regulator, or a filtered 0% to 100% PWM signal also referenced to the 5V regulator.

The IC is placed in a sleep state by pulling the CTL lead below 0.5V. In this mode everything on the chip is shut down except for the on-chip regulator and the overall current draw is less than 275  $\mu$ A. There are a number of on-chip diagnostics that look for potential failure modes and can disable the external power MOSFET.

## Features

- 200 mA Peak PWM Gate Drive Output

- Patented Voltage Compensation Circuit

- 100% Duty Cycle Capability

- 5V, ± 3% Linear Reg.

- Low Current Sleep Mode

- Overvoltage Protection

- Over Current Protection of External MOSFET / IGBT

- Output Inhibit

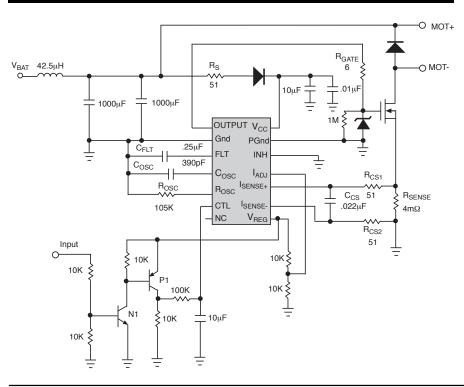

## **Application Diagram**

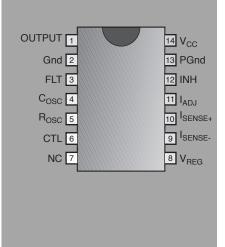

## **Package Options**

14 Lead PDIP

Consult factory for 16 lead SO wide package.

Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600 Fax: (401)885-5786 Email: info@cherry-semi.com Web Site: www.cherry-semi.com

## Absolute Maximum Ratings

| Storage Temperature               |  |

|-----------------------------------|--|

| ESD Capability (Human Body Model) |  |

| PARAMETER                           | TEST CONDITIONS                                                          | MIN                   | TYP  | MAX          | UNIT     |

|-------------------------------------|--------------------------------------------------------------------------|-----------------------|------|--------------|----------|

| V <sub>CC</sub> Supply              |                                                                          |                       |      |              |          |

| Operating Current Supply            |                                                                          |                       | 5    | 10           | mA       |

| Quiescent Current                   | $V_{CC} = 12V$                                                           |                       | 170  | 275          | μΑ       |

| Overvoltage Shutdown                |                                                                          | 18                    | 19.5 | 21           | V        |

| Overvoltage Hysteresis              |                                                                          | 150                   | 325  | 500          | mV       |

| Control (CTL)                       |                                                                          |                       |      |              |          |

| Control Input Current               | CTL = 0V  to  5V                                                         | -2                    | 0.1  | 2            | μΑ       |

| Sleep Mode Threshold                |                                                                          | 8%                    | 10%  | 12%          | $V_{RE}$ |

| Sleep Mode Hysteresis               |                                                                          | 50                    | 100  | 150          | mV       |

| Current Sense                       |                                                                          |                       |      |              |          |

| Differential Voltage Sense          | $I_{ADJ}$ =51.2% $V_{REG}$ and $R_{CS1}$ = 51 $\Omega$                   | 60.5                  |      | 79.5         | mV       |

| I <sub>ADJ</sub> Input Current      | $I_{ADJ} = 0V \text{ to } 5V$                                            | -5                    | 0.3  | 2            | μΑ       |

| Linear Regulator $V_{REG}$          |                                                                          |                       |      |              |          |

| Output Voltage                      | $V_{CC} = 13.2V$                                                         | 4.85                  | 5.00 | 5.15         | V        |

| Inhibit                             |                                                                          |                       |      |              |          |

| Inhibit Threshold                   |                                                                          | 40%                   | 50%  | 60%          | $V_{RE}$ |

| Inhibit Hysteresis                  |                                                                          | 150                   | 325  | 500          | mV       |

| External Drive (OUTPUT)             |                                                                          |                       |      |              |          |

| Output Frequency                    | $R_{OSC} = 105k\Omega$ , $C_{OSC} = 390pF$                               | 17                    | 20   | 23           | kH       |

| Voltage to Duty Cycle<br>Conversion | $V_{CC} = 13V, CTL = 30\% V_{REG}$<br>$V_{CC} = 13V, CTL = 70\% V_{REG}$ | 26.3<br>69.5          |      | 38.5<br>81.5 | %<br>%   |

| Output Rise Time                    | $V_{CC} = 13V$ , $R_{GATE} = 6\Omega$ , $C_{GATE} = 5nF$                 |                       | .25  | 1            | μs       |

| Output Fall Time                    | $V_{CC} = 13V$ , $R_{GATE} = 6\Omega$ , $C_{GATE} = 5nF$                 |                       | .30  | 1            | μs       |

| Output Sink Current                 | $V_{CC} = 13V$ , $R_{GATE} = 6\Omega$ , $C_{GATE} = 5nF$                 |                       | 400  |              | mA       |

| Output Source Current               | $V_{CC} = 13V$ , $R_{GATE} = 6\Omega$ , $C_{GATE} = 5nF$                 |                       | 400  |              | mA       |

| Output High Voltage                 | $I_{OUT} = 1mA$                                                          | V <sub>CC</sub> - 1.7 |      |              | V        |

| Output Low Voltage                  | $I_{OUT} = -1mA$                                                         |                       |      | 1.3          | V        |

| PACKAGE LEAD # | LEAD SYMBOL      | FUNCTION                       |

|----------------|------------------|--------------------------------|

| 14 Lead PDIP   |                  |                                |

| 1              | OUTPUT           | MOSFET Gate Drive              |

| 2              | Gnd              | Ground                         |

| 3              | FLT              | Fault time out capacitor       |

| 4              | C <sub>OSC</sub> | Oscillator capacitor           |

| 5              | $R_{OSC}$        | Oscillator resistor            |

| 6              | CTL              | Pulse width control input      |

| 7              | NC               | No connection                  |

| 8              | $V_{REG}$        | 5V linear regulator            |

| 9              | $I_{SENSE}$      | Current sense minus            |

| 10             | $I_{SENSE+}$     | Current sense plus             |

| 11             | $I_{ADJ}$        | Current limit adjust           |

| 12             | INH              | Output Inhibit                 |

| 13             | PGnd             | Power ground for on chip clamp |

| 14             | $V_{CC}$         | Positive power supply input    |

## **Application Information**

## **Theory Of Operation**

#### Oscillator

The IC sets up a constant frequency triangle wave at the  $C_{OSC}$  lead whose frequency is determined by the external components  $R_{OSC}$  and  $C_{OSC}$  by the following equation:

$$Frequency = \frac{0.83}{R_{OSC} \times C_{OSC}}$$

The peak and valley of the triangle wave are proportional to  $V_{CC}$  by the following:

$$V_{VALLEY} = 0.2 \times V_{CC}$$

$$V_{PEAK} = 0.8 \times V_{CC}$$

This is required to make the voltage compensation function properly. In order to keep the frequency of the oscillator constant the current that charges  $C_{OSC}$  must also vary with supply.  $R_{OSC}$  sets up the current which charges  $C_{OSC}$ . The voltage across  $R_{OSC}$  is 50% of  $V_{CC}$  and therefore:

$$I_{ROSC} = 0.5 \times \frac{V_{CC}}{R_{OSC}}$$

$I_{ROSC}$  is multiplied by two (2) internally and transferred to the  $C_{OSC}$  lead. Therefore:

$$I_{COSC} = \pm \frac{V_{CC}}{R_{OSC}}$$

The period of the oscillator is:

$$T = 2C_{OSC} \times \frac{(V_{PEAK} - V_{VALLEY})}{I_{COSC}}$$

The  $R_{OSC}$  and  $C_{OSC}$  components can be varied to create frequencies over the range of 15Hz to 25kHz. With the suggested values of  $105k\Omega$  and 390pF for  $R_{OSC}$  and  $C_{OSC}$  respectively, the nominal frequency will be approximately 20 kHz.  $I_{ROSC}$ , at  $V_{CC}$  = 14V, will be 66.7  $\mu A.$   $I_{ROSC}$  should not change over a more than 2:1 ratio and therefore  $C_{OSC}$  should be changed to adjust the oscillator frequency.

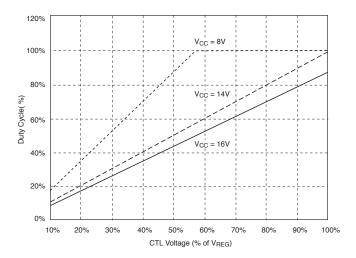

#### Voltage Duty Cycle Conversion

The IC translates an input voltage at the CTL lead into a duty cycle at the OUTPUT lead. The transfer function incorporates Cherry Semiconductor's patented Voltage Compensation method to keep the average voltage and current across the load constant regardless of fluctuations

## **Application Information: continued**

in the supply voltage. The duty cycle is varied based upon the input voltage and supply voltage by the following equation:

Duty Cycle =

$$100\% \times \frac{2.8 \times V_{CTL}}{V_{CC}}$$

An internal DC voltage equal to:

$$V_{DC} = (1.683 \times V_{CTL}) + (V_{VALLEY})$$

is compared to the oscillator voltage to produce the compensated duty cycle. The transfer is set up so that at  $V_{CC} = 14 V$  the duty will equal  $V_{CTL}$  divided by  $V_{REG}.$  For example at  $V_{CC} = 14 V, V_{REG} = 5 V$  and  $V_{CTL} = 2.5 V$ , the duty cycle would be 50% at the output. This would place a 7 V average voltage across the load. If  $V_{CC}$  then drops to 10 V, the IC would change the duty cycle to 70% and hence keep the average load voltage at 7 V.

Figure 1: Voltage Compensation

#### **5V Linear Regulator**

There is a 5V, 5mA linear regulator available at the  $V_{REG}$  lead for external use. This voltage acts as a reference for many internal and external functions. It has a drop out of approximately 1.5V at room temperature and does not require an external capacitor for stability.

#### **Current Sense and Timer**

The IC differentially monitors the load current on a cycle by cycle basis at the I<sub>SENSE+</sub> and I<sub>SENSE-</sub> leads. The differen-

tial voltage across these two leads is amplified internally and compared to the voltage at the  $I_{ADJ}$  lead. The gain,  $A_V$ , is set internally and externally by the following equation:

$$A_V = \frac{V_{I(ADJ)}}{I_{SENSE+} - I_{SENSE-}} = \frac{37000}{1000 + R_{CS}}$$

The current limit ( $I_{LIM}$ ) is set by the external current sense resistor ( $R_{SENSE}$ ) placed across the  $I_{SENSE+}$  and  $I_{SENSE-}$  terminals and the voltage at the  $I_{ADI}$  lead.

$$I_{LIM} = \frac{(1000 + R_{CS})}{37000} \times \frac{V_{I(ADJ)}}{R_{SENSE}}$$

The  $R_{CS}$  resistors and  $C_{CS}$  components form a differential low pass filter which filters out high frequency noise generated by the switching of the external MOSFET and the associated lead noise.  $R_{CS}$  also forms an error term in the gain of the  $I_{LIM}$  equation because the  $I_{SENSE+}$  and  $I_{SENSE-}$  leads are low impedance inputs thereby creating a good current sensing amplifier. Both leads source  $50\mu A$  while the chip is in run mode.  $R_{CS}$  should be much less than 1000  $\Omega$  to minimize error in the  $I_{LIM}$  equation.  $I_{ADJ}$  should be biased between 1V and 4V.

When the current through the external MOSFET exceeds  $I_{LIM}$ , an internal latch is set and the output pulls the gate of the MOSFET low for the remainder of the oscillator cycle (fault mode). At the start of the next cycle, the latch is reset and the IC reverts back to run mode until another fault occurs. If a number of faults occur in a given period of time, the IC "times out" and disables the MOSFET for a long period of time to let it cool off. This is accomplished by charging the C<sub>FLT</sub> capacitor each time an over current condition occurs. If a cycle goes by with no overcurrent fault occurring, an even smaller amount of charge will be removed from C<sub>FLT</sub>. If enough faults occur together, eventually C<sub>FLT</sub> will charge up to 2.4V and the fault latch will be set. The fault latch will not be reset until the  $C_{FLT}$  discharges to 0.6V. This action will continue indefinitely if the fault persists.

The off time and on time are set by the following:

Off Time =

$$C_{FLT} \times \frac{2.4V - 0.6V}{4.5\mu A}$$

On Time =

$$C_{FLT} \times \frac{2.4V - 0.6V}{I_{AVG}}$$

where:

$$I_{AVG} = (295.5\mu\text{A} \times \text{DC}) - [4.5\mu\text{A} \times (1 - \text{DC})]$$

$$I_{AVG} = (300\mu\text{A} \times \text{DC}) - 4.5\mu\text{A}$$

$$DC = PWM \text{ Duty Cycle}$$

### Sleep State

This device will enter into a low current mode ( $<275\mu$ A) when CTL lead is brought to less than 0.5V. All functions are disabled in this mode, except for the regulator.

#### Inhibit

When the inhibit voltage is greater than 2.5V the internal latch is set and the external MOSFET will be turned off for the remainder of the oscillator cycle. The latch is then reset at the start of the next cycle.

## Overvoltage Shutdown

The IC will disable the output during an overvoltage event. This is a real time fault event and does not set the internal latch and therefore is independent of the oscillator timing (i.e. asynchronous). There is no undervoltage lock-out. The device will shutdown gracefully once it runs out of headroom.

### **Reverse Battery**

The CS7054 will not survive a reverse battery condition. Therefore, a series diode is required between the battery and the  $V_{\rm CC}$  lead.

## **Load Dump**

$V_{CC}$  is internally clamped to 30V. It is recommended that a 51 $\Omega$  resistor, (R<sub>S</sub>) is placed in series with  $V_{CC}$  to limit the current flow into the IC in the event of a 40V peak transient condition.

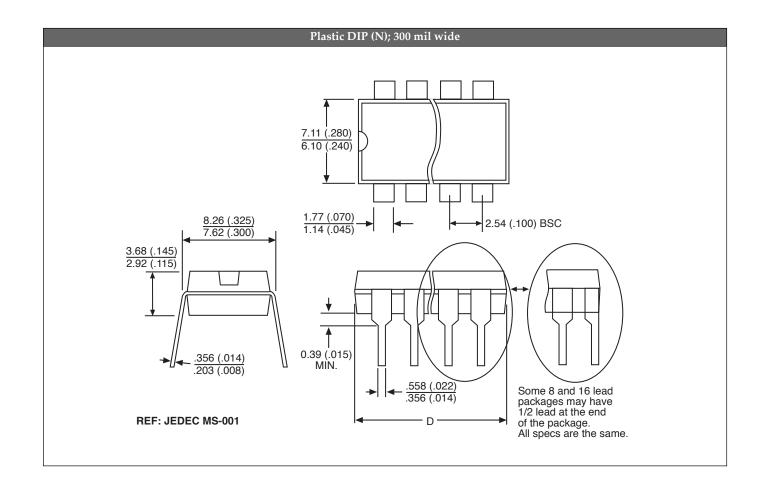

## **Package Specification**

## PACKAGE DIMENSIONS IN mm (INCHES)

|            |            |       | D    |      |

|------------|------------|-------|------|------|

| Lead Count | Metric Eng |       | lish |      |

|            | Max        | Min   | Max  | Min  |

| 14L PDIP   | 19.69      | 18.67 | .775 | .735 |

| PACKAGE THERMAL DATA |      |             |      |  |

|----------------------|------|-------------|------|--|

| Thermal              | Data | 14L<br>PDIP |      |  |

| $R_{\Theta JC}$      | typ  | 48          | °C/W |  |

| $R_{\Theta JA}$      | typ  | 85          | °C/W |  |

| Ordering Information |              |  |

|----------------------|--------------|--|

| Part Number          | Description  |  |

| CS7054YN14           | 14 Lead PDIP |  |

Cherry Semiconductor Corporation reserves the right to make changes to the specifications without notice. Please contact Cherry Semiconductor Corporation for the latest available information.