## Features

- Servo Processing Unit (SPU), Using Dedicated 16-bit Instruction Cycle AVR<sup>®</sup> RISC Cores (3), Giving 120 MIPS Maximum Processing Power with 40 MHz SYSCLK

- SPU Includes 17 x 17 Single-clock Cycle MAC

- On-chip Debugger Monitor for Program Development (OCDM)

- 8K Words Program RAM

- 4K Bytes Data RAM

- On-chip Clock Frequency Synthesizer with Output Clock Buffers for AT78C1501 Controller

- On-chip S/H and WCS Timing State Machine (TSM) for Conversion of Focus, Tracking and SUM Signals

- 10-bit 1.2 µsec ADC with six-channel MUX

- Synchronized ADC Conversions with SPU Interrupt Service Routine

- Three Fast 10-bit 500 nsec (rise time) DACs for Servo Loops and Adjustments

- Three 8-bit DACs for Offset Adjustment and Spin Loop

- Bandgap ADC and DAC Midpoint Reference Outputs

- SPU Implemented Spindle Speed Control

- Spindle Interface Logic and Hardware Support for Both CAV and CLV Spindle Control Modes

- Eight General Purpose I/O Pins

- SPU Servo Control of Focus, Fine Track, Coarse Track and Tray Load Motors

- High-speed Track Counter for Accurate High-speed Track Counts (1.4 MHz when used with AT78C1503 Read Channel)

- Lower Power Operations with 3.3V Core and 5V Tolerant I/Os

- 8-bit Data and 14-bit Address Controller/Microprocessor Interface

- 3-pin Universal Serial Port Interface to Program Read Channel and Power Devices

- Power Management

- On-chip UART to Access OCDM Unit

## Description

The Atmel AT78C1502 high-performance servo controller fully integrates all of the control and demodulation functions for DVD and CD, optical/mechanical systems. Packaged in 128-lead TQFP and fabricated in 0.35 micron CMOS, the device operates on a 3.3V logic/analog supply and provides 5V tolerance for digital I/O. An AVR-based Servo Processing Unit (SPU) embedded in the device provides programmable control of spindle speed, coarse and fine tracking, focus, sled, draw motor and tilt. The three parallel programmable AVR microcontrollers in the SPU are the heart of the system, offering a range of servo sample rates. With only a 40 MHz system clock, 120 MIPS of processing power is provided. Real-time notch filters can also be calculated. Fast 10-bit DACs provide real-time control of servo loops and other system adjustments. A universal serial port and many general purpose I/Os are provided.

AVR0 is the master AVR of the three microcontrolloers, communicating with AVR1, AVR2 and the ARMTDMI in the AT78C1501 interface controller and to the AT78C1503 read channel. An On-Chip Debugger Monitor (OCDM) is offered to enable programmers to easily observe the effect of changes to code on each AVR.

System-level evaluation boards are available with development code in both C and native code for basic operation of all servos. Simple changes to the code allow any mechadeck to be interfaced to the AT78C1502.

# AT78C1502

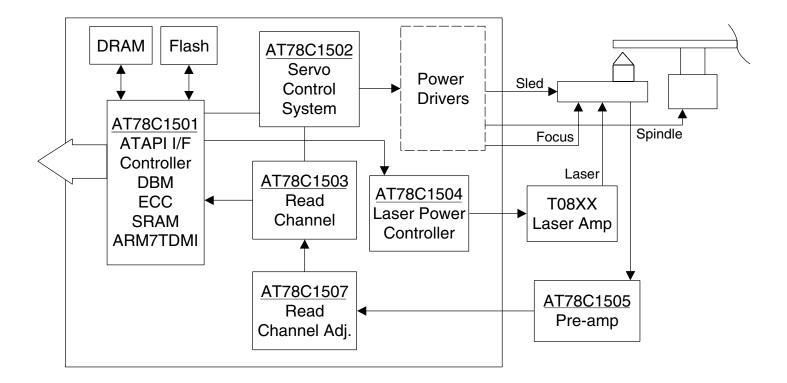

#### Figure 1. DVD System Block Diagram

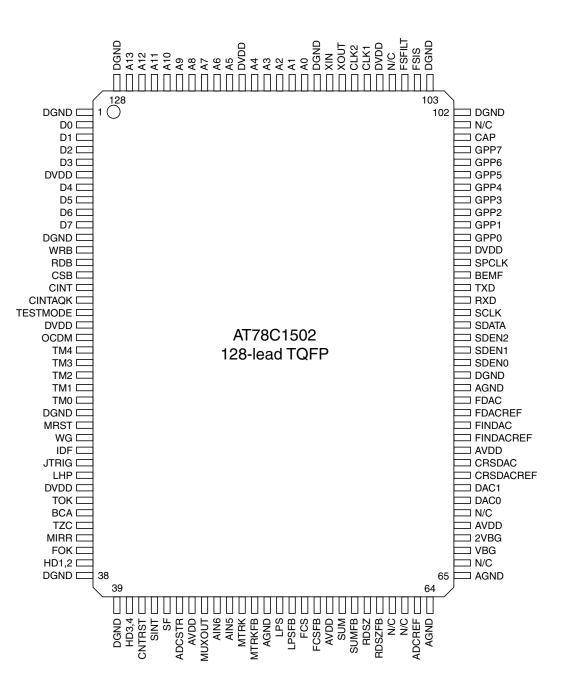

Figure 2. Pin-out

# External Pin Definition

P = Power or ground, B = Bidirectional, I = Digital Input, O = Digital Output.

AI = Analog Input, AO = Analog Output.

#### Table 1. External Pin Definition

| 1DGNDPDigital Ground2D0BData Bus3D1BData Bus4D2BData Bus5D3BData Bus6DVDDPDigital VDD7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Select Input14CSBIChip Select Input15CINTACKOController Interrupt Acknowledge16DVDDPDigital VDD17TMODEITest Mode Select Input18OVDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24GRNDISel Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIIset Mode Select Input/MUX Output28IDFIUP bigital Ground29JTRIGIUP bigital Ground29 <t< th=""><th>Pin #</th><th>Symbol</th><th>Туре</th><th>Description</th></t<> | Pin # | Symbol    | Туре | Description                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------|----------------------------------------|

| 3D1BData Bus4D2BData Bus5D3BData Bus6DVDDPDigital VDD7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Read Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input - Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27VGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJum Trigger Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Controller                                                                         | 1     | DGND      | Р    | Digital Ground                         |

| 4D2BData Bus5D3BData Bus6DVDDPDigital VDD7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Read Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input - Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output21TM2/MUX2ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27VGIVirite Gate Input from Controller28IDFIU/D Field Input from Controller29JTRIGIJum Trigger Input from Controller31DVDDPDigital Power32TOKITrack OK Input fr         | 2     | D0        | В    | Data Bus                               |

| 5D3BData Bus6DVDDPDigital VDD7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input/MUX Output27WGIWrite Gate Input from Controller28IDFIUrite Gate Input from Controller29JTRIGIJum Trigger Input from Controller29JTRIGILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                   | 3     | D1        | В    | Data Bus                               |

| 6DVDDPDigital VDD7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output23TM1/MUX3ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMater Reset Input/MUX Output27WGIWrite Gate Input from Controller28IDFIVirb Field Input from Controller29JTRIGIJum Trigger Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                        | 4     | D2        | В    | Data Bus                               |

| 7D4BData Bus8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input - Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGILuser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                | 5     | D3        | В    | Data Bus                               |

| 8D5BData Bus9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select18DVDDPDigital VDD19OCDM_ENABITest Mode Select20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power31DVDDPDigital Power32TOKITrack OK Input from Controller                                                                                                     | 6     | DVDD      | Р    | Digital VDD                            |

| 9D6BData Bus10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input - Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGILaser High Power Input from Controller30LHPILaser High Power31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                         | 7     | D4        | В    | Data Bus                               |

| 10D7BData Bus11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select Input/MUX Output21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFIJump Trigger Input from Controller29JTRIGILaser High Power Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                     | 8     | D5        | В    | Data Bus                               |

| 11DGNDPDigital Ground12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFIJump Trigger Input from Controller29JTRIGILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                               | 9     | D6        | В    | Data Bus                               |

| 12WRBIChip Write Select13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFIJDF Ield Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                | 10    | D7        | В    | Data Bus                               |

| 13RDBIChip Read Select14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVite Gate Input from Controller28IDFIJUP Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                       | 11    | DGND      | Р    | Digital Ground                         |

| 14CSBIChip Select Input15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                | 12    | WRB       | I    | Chip Write Select                      |

| 15CINTIInterrupt Input from Controller16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                              | 13    | RDB       | I    | Chip Read Select                       |

| 16CINTACKOController Interrupt Acknowledge17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                    | 14    | CSB       | I    | Chip Select Input                      |

| 17TMODEITest Mode Select Input – Active-low18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGILaser High Power Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                   | 15    | CINT      | I    | Interrupt Input from Controller        |

| 18DVDDPDigital VDD19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                         | 16    | CINTACK   | 0    | Controller Interrupt Acknowledge       |

| 19OCDM_ENABIOn-chip Debug/Monitor Mode20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIWrite Gate Input from Controller28IDFIJUP Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                           | 17    | TMODE     | I    | Test Mode Select Input – Active-low    |

| 20TM4/MUX4ITest Mode Select21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                          | 18    | DVDD      | Р    | Digital VDD                            |

| 21TM3/MUX3ITest Mode Select Input/MUX Output22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGILaser High Power Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                 | 19    | OCDM_ENAB | I    | On-chip Debug/Monitor Mode             |

| 22TM2/MUX2ITest Mode Select Input/MUX Output23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIVrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                 | 20    | TM4/MUX4  | I    | Test Mode Select                       |

| 23TM1/MUX1ITest Mode Select Input/MUX Output24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21    | TM3/MUX3  | I    | Test Mode Select Input/MUX Output      |

| 24TM0/MUX0ITest Mode Select Input/MUX Output25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22    | TM2/MUX2  | I    | Test Mode Select Input/MUX Output      |

| 25DGNDPDigital Ground26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23    | TM1/MUX1  | I    | Test Mode Select Input/MUX Output      |

| 26MRSTIMaster Reset Input27WGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24    | TM0/MUX0  | I    | Test Mode Select Input/MUX Output      |

| 27WGIWrite Gate Input from Controller28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25    | DGND      | Р    | Digital Ground                         |

| 28IDFII/D Field Input from Controller29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26    | MRST      | I    | Master Reset Input                     |

| 29JTRIGIJump Trigger Input from Controller30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27    | WG        | I    | Write Gate Input from Controller       |

| 30LHPILaser High Power Input from Controller31DVDDPDigital Power32TOKITrack OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28    | IDF       | I    | I/D Field Input from Controller        |

| 31     DVDD     P     Digital Power       32     TOK     I     Track OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29    | JTRIG     | I    | Jump Trigger Input from Controller     |

| 32 TOK I Track OK Input from Read Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30    | LHP       | I    | Laser High Power Input from Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31    | DVDD      | Р    | Digital Power                          |

| 33 BCA I Burst Cutting Area (Defect Flag Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32    | ТОК       | I    | Track OK Input from Read Channel       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33    | BCA       | I    | Burst Cutting Area (Defect Flag Input) |

| Pin # | Symbol  | Туре | Description                           |  |

|-------|---------|------|---------------------------------------|--|

| 34    | TZC     | I    | Track Zero Crossing from Read Channel |  |

| 35    | MIRR    | I    | Mirror Input from Read Channel        |  |

| 36    | FOK     | I    | Focus OK Signal from Read Channel     |  |

| 37    | HD1,2   | I    | Header 1, 2 Input from Read Channel   |  |

| 38    | DGND    | Р    | Digital Ground                        |  |

| 39    | DGND    | Р    | Digital Ground                        |  |

| 40    | HD3,4   | I    | Header 3, 4 Input from Read Channel   |  |

| 41    | CNTRST  | I    | TSM Counter Reset Signal              |  |

| 42    | SINT    | 0    | Servo Interrupt Output to Controller  |  |

| 43    | SF      | 0    | Servo Fault Output to Controller      |  |

| 44    | ADCSTR  | 0    | ADC Strobe Output from TSM            |  |

| 45    | AVDD    | Р    | Analog VDD                            |  |

| 46    | MUX_OUT | AO   | Analog MUX Output                     |  |

| 47    | AIN6    | AI   | Analog Input to MUX                   |  |

| 48    | AIN5    | AI   | Analog Input to MUX                   |  |

| 49    | MTRK    | AI   | MUXed Track Track/Hold Input          |  |

| 50    | MTRKFB  | AI   | MUXed Track Filter Input              |  |

| 51    | AGND    | Р    | Analog Ground                         |  |

| 52    | LPS     | AI   | Lens Position Sensor Track/Hold Input |  |

| 53    | LPS     | AI   | Lens Position Sensor Filter Input     |  |

| 54    | FCS     | AI   | Focus Error Signal Track/Hold Input   |  |

| 55    | FCSF    | AI   | Focus Error Signal Filter Input       |  |

| 56    | AVDD    | Р    | Analog VDD                            |  |

| 57    | SUM     | AI   | Slow Sum Track/Hold Input             |  |

| 58    | SUMF    | AI   | Slow Sum Input Filter                 |  |

| 59    | RDSZ    | AI   | Read Size Input                       |  |

| 60    | RDSZF   | AI   | Read Size Input Filter                |  |

| 61    | N/C     |      | No Connect                            |  |

| 62    | N/C     |      | No Connect                            |  |

| 63    | ADCREF  | AI   | Reference I/P for ADC                 |  |

| 64    | AGND    | Р    | Analog GND                            |  |

| 65    | AGND    | Р    | Analog GND                            |  |

| 66    | N/C     |      | No Connect                            |  |

| 67    | VBG     | AO   | Bandgap Output Voltage                |  |

| 68    | 2VBG    | AO   | 2*Bandgap Output Voltage              |  |

| 69    | AVDD    | Р    | Analog VDD                            |  |

. -

| Table 1. External Pin Definition (Continued) | Table 1. | External Pin | Definition | (Continued) |

|----------------------------------------------|----------|--------------|------------|-------------|

|----------------------------------------------|----------|--------------|------------|-------------|

| Pin # | Symbol    | Туре | Description                  |  |

|-------|-----------|------|------------------------------|--|

| 70    | N/C       |      | No Connect                   |  |

| 71    | DAC0      | AO   | 8-bit Offset DAC Output      |  |

| 72    | DAC1      | AO   | 8-bit Offset DAC Output      |  |

| 73    | CRSDAC    | AO   | 10-bit Coarse Tracking DAC   |  |

| 74    | CRSDACREF | AI   | Coarse DAC Ref Input         |  |

| 75    | AVDD      | Р    | Analog VDD                   |  |

| 76    | FINDAC    | AO   | 10-bit Fine Tracking DAC     |  |

| 77    | FINDACREF | AI   | Fine DAC Ref Input           |  |

| 78    | FDAC      | AO   | 10-bit Focus DAC             |  |

| 79    | FDACREF   | AI   | Focus DAC Ref Input          |  |

| 80    | AGND      | Р    | Analog GND                   |  |

| 81    | DGND      | Р    | Digital GND                  |  |

| 82    | SDEN0     | 0    | Serial Data Enable #0        |  |

| 83    | SDEN1     | 0    | Serial Data Enable #1        |  |

| 84    | SDEN2     | 0    | Serial Data Enable #2        |  |

| 85    | SDATA     | В    | Serial Data                  |  |

| 86    | SCLK      | 0    | Serial CLK                   |  |

| 87    | RXD       | I    | UART Receive Data Input      |  |

| 88    | TXD       | 0    | UART Transmit Data Output    |  |

| 89    | BEMF      | I    | Back EMF Zero Crossing Input |  |

| 90    | SPCLK     | 0    | Spin Pseudo Register Output  |  |

| 91    | DVDD      | Р    | Digital VDD                  |  |

| 92    | GPP0      | В    | General Purpose I/O Port Bit |  |

| 93    | GPP1      | В    | General Purpose I/O Port Bit |  |

| 94    | GPP2      | В    | General Purpose I/O Port Bit |  |

| 95    | GPP3      | В    | General Purpose I/O Port Bit |  |

| 96    | GPP4      | В    | General Purpose I/O Port Bit |  |

| 97    | GPP5      | В    | General Purpose I/O Port Bit |  |

| 98    | GPP6      | В    | General Purpose I/O Port Bit |  |

| 99    | GPP7      | В    | General Purpose I/O Port Bit |  |

| 100   | САР       | I    | External Event Capture       |  |

| 101   | N/C       |      | No Connect                   |  |

| 102   | DGND      | Р    | Digital Ground               |  |

| 103   | DGND      | Р    | Digital Ground               |  |

| 104   | FSIS      | I    | Frequency Synthesizer Iset   |  |

| 105   | FSFILT    | I    | Frequency Synthesizer Filter |  |

# AT78C1502

| Pin # | Symbol | Туре | Description               |

|-------|--------|------|---------------------------|

| 106   | N/C    |      | No Connect                |

| 107   | DVDD   | Р    | Digital VDD               |

| 108   | CLK1   | 0    | Clock 1 Output            |

| 109   | CLK2   | 0    | Clock 1 Output            |

| 110   | XOUT   | 0    | Crystal Out Connection    |

| 111   | XIN    | I    | Crystal Input/Clock Input |

| 112   | DGND   | Р    | Digital Ground            |

| 113   | A0     | I    | Address Bus Input         |

| 114   | A1     | I    | Address Bus Input         |

| 115   | A2     | I    | Address Bus Input         |

| 116   | A3     | I    | Address Bus Input         |

| 117   | A4     | I    | Address Bus Input         |

| 118   | DVDD   | Р    | Digital VDD               |

| 119   | A5     | I    | Address Bus Input         |

| 120   | A6     | I    | Address Bus Input         |

| 121   | A7     | I    | Address Bus Input         |

| 122   | A8     | I    | Address Bus Input         |

| 123   | A9     | I    | Address Bus Input         |

| 124   | A10    | I    | Address Bus Input         |

| 125   | A11    | I    | Address Bus Input         |

| 126   | A12    | I    | Address Bus Input         |

| 127   | A13    | I    | Address Bus Input         |

| 128   | DGND   | Р    | Digital GND               |

Table 1. External Pin Definition (Continued)

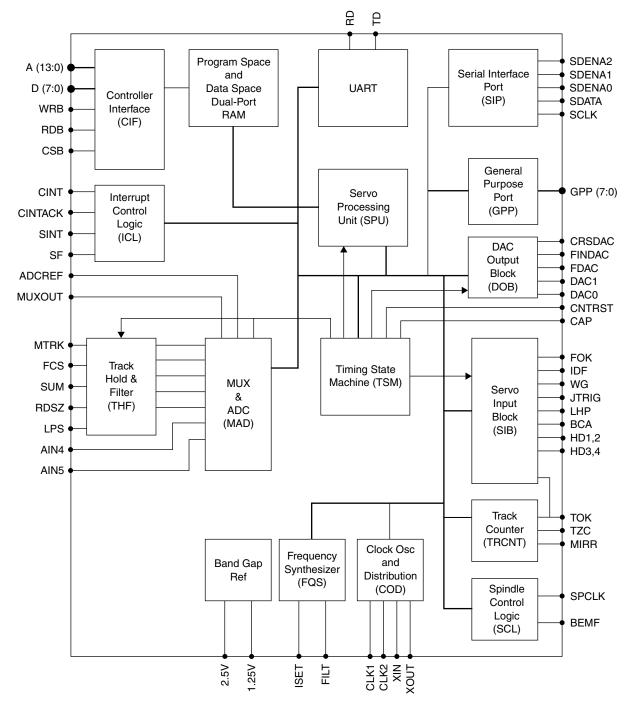

#### Figure 3. Block Diagram

#### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

## Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.

Printed on recycled paper.

2050A-DVD-07/02