#### POWER OPERATIONAL AMPLIFIER

# **MP230**

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

# **FEATURES**

- LOW COST

- HIGH VOLTAGE 100 VOLTS

- HIGH OUTPUT CURRENT 30 AMPS

- 210 WATT DISSIPATION CAPABILITY

# **APPLICATIONS**

- MOTOR DRIVE

- MAGNETIC DEFLECTION

- PROGRAMMABLE POWER SUPPLIES

- INDUSTRIAL AUDIO AMPLIFIER

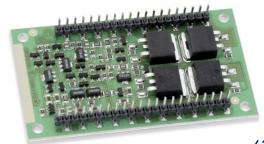

## **DESCRIPTION**

The MP230 operational amplifier is a surface mount constructed component that provides a cost effective solution in many industrial applications. The MP230 offers outstanding performance that rivals many much more expensive hybrid components yet has a footprint of only 4.7 sq in. The MP230 has many optional features such as four-wire current limit sensing, a shutdown control and external compensation. In addition, the class A/B output stage biasing can be turned off for lower quiescent current with class C operation in applications where crossover distortion is less important such as when driving motors, for example. A boost voltage feature biases the output stage for close linear swings to the supply rail for extra efficient operation. The MP230 is built on a thermally conductive but electrically insulating substrate that can be mounted to a heat sink.

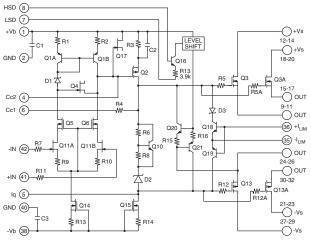

## **EQUIVALENT CIRCUIT DIAGRAM**

42-PIN DIP PACKAGE TYPE FC

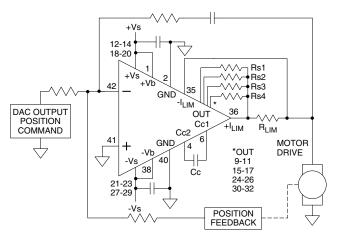

#### TYPICAL APPLICATION

# **MOTOR POSITION CONTROL**

The MOSFET output stage of the MP230 provides superior SOA performance compared to bipolar output stages where secondary breakdown is a concern. The extended SOA is ideal in motor drive applications where the back EMF of the motor may impose simultaneously both high voltage and high current across the output stage transistors. In the figure above a mechanical to electrical feedback position converter allows the MP230 to drive the motor in either direction to a set point determined by the DAC voltage.

# **EXTERNAL CONNECTIONS**

ABSOLUTE MAXIMUM RATINGS **MP230 SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

SUPPLY VOLTAGE,  $+V_S$  to  $-V_S$ SUPPLY VOLTAGE, +V<sub>B</sub> (BOOST) SUPPLY VOLTAGE, -V<sub>B</sub> (BOOST) OUTPUT CURRENT, peak POWER DISSIPATION, internal, DC INPUT VOLTAGE TEMPERATURE, pin solder, 10s TEMPERATURE, junction<sup>2</sup> TEMPERATURE RANGE, storage OPERATING TEMPERATURE, case

100V  $+V_{S} + 15V^{6}$  $-V_{S} - 15V^{6}$ 40A, within SOA 210W  $+V_B$  to  $-V_B$ 225°C. 175°C. -40 to 105°C.

-40 to 85°C.

## **SPECIFICATIONS**

| PARAMETER                                                                                                                                   | TEST CONDITIONS <sup>1</sup>                                                                          | MIN                                                                                                  | TYP                                        | MAX                                                | UNITS                             |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|-----------------------------------|

| INPUT OFFSET VOLTAGE OFFSET VOLTAGE vs. temperature OFFSET VOLTAGE vs. supply BIAS CURRENT, initial <sup>3</sup> BIAS CURRENT vs. supply    | Full temperature range                                                                                |                                                                                                      | 1<br>20                                    | 5<br>50<br>20<br>100<br>0.1                        | mV<br>μV/°C<br>μV/V<br>pA<br>pA/V |

| OFFSET CURRENT, initial INPUT IMPEDANCE, DC INPUT CAPACITANCE COMMON MODE VOLTAGE RANGE COMMON MODE VOLTAGE RANGE COMMON MODE REJECTION, DC |                                                                                                       | 92                                                                                                   | 100<br>4                                   | 50<br>+V <sub>S</sub> - 13<br>-V <sub>S</sub> + 13 | pA<br>GΩ<br>pF<br>V<br>V<br>dB    |

| NOISE SHUTDOWN, active SHUTDOWN, inactive                                                                                                   | 100kHz bandwidth, 1kΩ R <sub>S</sub><br>HSD - LSD<br>HSD - LSD                                        | 4.5<br>-0.5                                                                                          | 5<br>5<br>0                                | 5.5<br>0.25                                        | μV RMS<br>V<br>V                  |

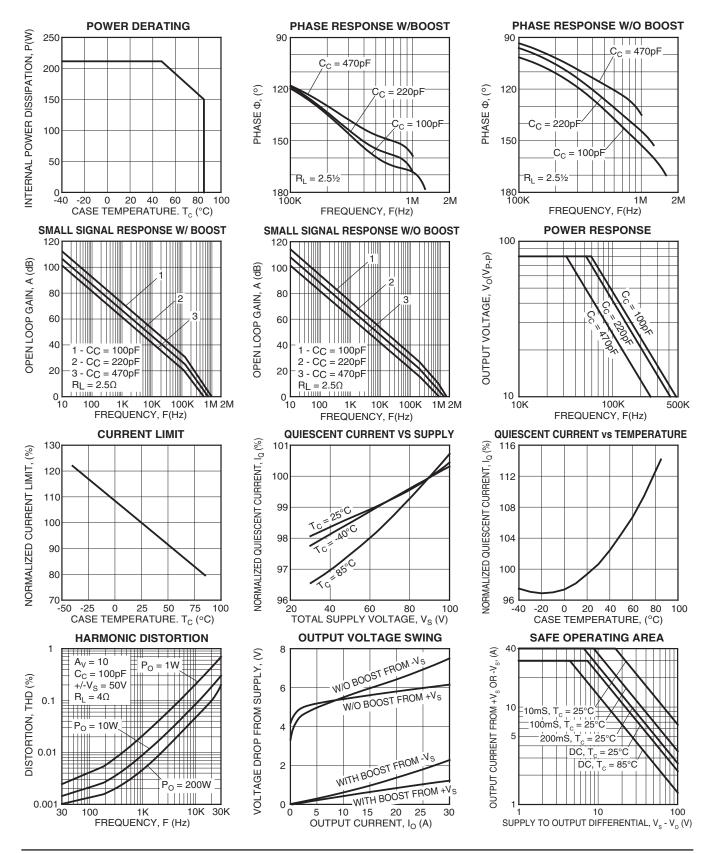

| GAIN<br>OPEN LOOP @ 15Hz<br>GAIN BANDWIDTH PRODUCT @ 1MHz<br>PHASE MARGIN                                                                   | $R_L = 1K\Omega$ , $C_C = 100pF$<br>$C_C = 100pF$<br>Full temperature range                           | 96<br>60                                                                                             | 2                                          |                                                    | dB<br>MHz                         |

| OUTPUT VOLTAGE SWING VOLTAGE SWING VOLTAGE SWING VOLTAGE SWING CURRENT, continuous, DC                                                      | $I_{O} = 30A$ $I_{O} = -30A$ $I_{O} = 30A, +V_{B} = +V_{S} +10V$ $I_{O} = -30A, -V_{B} = -V_{S} -10V$ | +V <sub>S</sub> - 10<br>-V <sub>S</sub> + 10<br>+V <sub>S</sub> - 1.5<br>-V <sub>S</sub> + 3.0<br>30 | +V <sub>S</sub> - 7<br>-V <sub>S</sub> + 8 |                                                    | V<br>V<br>V<br>V<br>A             |

| SLEW RATE, A $_{\rm V}$ = -10<br>SETTLING TIME, to 0.1%<br>RESISTANCE, open loop                                                            | $C_C = 100pF$<br>$A_V = -1, 10V \text{ Step, } C_C = 470pF$<br>DC, 10A Load                           | 12                                                                                                   | 15<br>2.5<br>0.1                           |                                                    | V/μS<br>μS<br>Ω                   |

| POWER SUPPLY VOLTAGE CURRENT, quiescent, total CURRENT, boost supply CURRENT, shutdown or class C quiescent                                 |                                                                                                       | ±15                                                                                                  | ±45<br>27<br>17<br>17                      | ±50<br>35                                          | V<br>mA<br>mA<br>mA               |

| THERMAL RESISTANCE, AC, junction to case <sup>5</sup> RESISTANCE, DC, junction to case RESISTANCE, junction to air TEMPERATURE RANGE, case  | Full temperature range, f ≥ 60Hz<br>Full temperature range, f < 60Hz<br>Full temperature range        | -40                                                                                                  |                                            | 0.6<br>0.7<br>14<br>85                             | °C/W<br>°C/W<br>°C                |

- NOTES: 1. Unless otherwise noted:  $T_c = 25^{\circ}$ C, compensation  $C_c = 470$ pF, DC input specifications are  $\pm$  value given, power supply voltage is typical rating. Amplifier operated without boost feature.

- 2. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTBF.

- 3. Doubles for every 10°C of case temperature increase.

- 4. +V<sub>S</sub> and -V<sub>S</sub> denote the + and output stage supply voltages. +V<sub>B</sub> and -V<sub>B</sub> denote the + and input stage supply voltages (boost voltages).

- Rating applies if the output current alternates between both output transistors at a rate faster than 60Hz.

- 6. Power supply voltages  $+V_B$  and  $-V_B$  must not be less than  $+V_S$  and  $-V_S$  respectively.

OPERATING CONSIDERATIONS MP230

#### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, power supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit, heat sink selection, Apex's complete Application Notes library, Technical Seminar Workbook and Evaluation Kits.

#### **GROUND PINS**

The MP230 has two ground pins (pins 2, 40). These pins provide a return for the internal capacitive bypassing of the small signal stages of the MP230. The two ground pins are not connected together on the substrate. Both of these pins are required to be connected to the system signal ground.

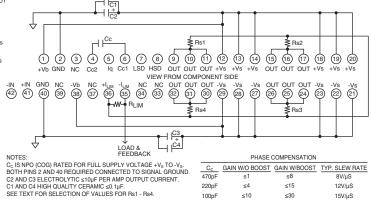

# BALANCING RESISTOR SELECTION (R<sub>S1</sub>-R<sub>S4</sub>)

The MP230 uses parallel sets of output transistors. To ensure that the load current is evenly shared among the transistors external balancing resistors  $R_{\rm S1}\text{-}R_{\rm S4}$  are required. To calculate the required value for each of the resistors use:  $R=4.5\ /\ l^2$  ,where I is the maximum expected output current. For example, with a maximum output current of 10A each balancing resistor should be 0.045 ohms. Each resistor dissipates 1.125W at the maximum current. Use a **non-inductive** 2W rated resistor. A ready source for such resistors is the IRC resistor series LR available from Mouser Electronics.

## **SAFE OPERATING AREA**

The MOSFET output stage of the MP230 is not limited by second breakdown considerations as in bipolar output stages. Only thermal considerations and current handling capabilities limit the SOA (see Safe Operating Area graph on previous page). The output stage is protected against transient flyback by the parasitic diodes of the output stage MOSFET structure. However, for protection against sustained high energy flyback external fast-recovery diodes must be used.

## **COMPENSATION**

The external compensation capacitor  $C_{\rm C}$  is connected to pins 4 and 6. Unity gain stability can be achieved with  $C_{\rm C}$  = 470pF for a minimum phase margin of 60 degrees. At higher gains more phase shift can usually be tolerated and  $C_{\rm C}$  can be reduced resulting in higher bandwidth and slew rate. Use the typical operating curves as a guide to select  $C_{\rm C}$ . A 100V NPO (COG) type capacitor is required. Boost operation requires more compensation or higher gains than with normal operation due to the increased capacitance of the output transistors when the output signal swings close to the supply rails.

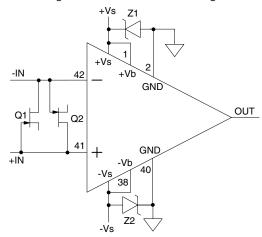

#### **OVERVOLTAGE PROTECTION**

Although the MP230 can withstand differential input voltages up to ±25V, in some applications additional external protection may be needed. 1N4148 signal diodes connected anti-parallel across the input pins is usually sufficient. In more demanding applications where bias current is important diode connected JFETs such as 2N4416 will be required. See Q1 and Q2 in Figure 1. In either case the differential input voltage will be

clamped to ±0.7V. This is sufficient overdrive to produce the maximum power bandwidth. Some applications will also need over-voltage protection devices connected to the power supply rails. Unidirectional zener diode transient suppressors are recommended. The zeners clamp transients to voltages within the power supply rating and also clamp power supply reversals to ground. Whether the zeners are used or not the system power supply should be evaluated for transient performance including power-on overshoot and power-off polarity reversals as well as line regulation. See Z1 and Z2 in Figure 1.

FIGURE 1: OVERVOLTAGE PROTECTION

#### POWER SUPPLY BYPASSING

Bypass capacitors to power supply terminals  $+V_S$  and  $-V_S$  must be connected physically close to the pins to prevent local parasitic oscillation in the output stage of the MP230. Use electrolytic capacitors at least  $10\mu F$  per output amp required. Bypass the electrolytic capacitors with high quality ceramic capacitors  $0.1\mu F$  or greater. In most applications power supply terminals  $+V_B$  and  $-V_B$  will be connected to  $+V_S$  and  $-V_S$  respectively. Although  $+V_B$  and  $-V_B$  are bypassed internally it is recommended to bypass  $+V_B$  and  $-V_B$  with  $0.1\mu F$  externally. Additionally, ground pins 2 and 40 must be connected to the system signal ground.

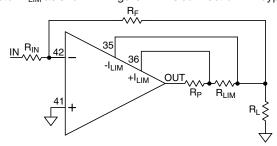

### **CURRENT LIMIT**

The two current limit sense lines are to be connected directly across the current limit sense resistor. For the current limit to work correctly pin 36 must be connected to the amplifier output side and pin 35 connected to the load side of the current limit resistor  $R_{LIM}$  as shown in Figure 2. This connection will bypass

FIGURE 2: 4 WIRE CURRENT LIMIT

MP230 OPERATING CONSIDERATIONS

any parasitic resistances RP, formed by socket and solder joints as well as internal amplifier losses. The current limiting resistor may not be placed anywhere in the output circuit except where shown in Figure 2. The value of the current limit resistor can be calculated as follows:  $R_{LIM} = .65/I_{LIMIT}$

# **BOOST OPERATION**

With the boost feature the small signal stages of the amplifier are operated at a higher supply voltages than the amplifier's high current output stage. +V $_{\rm B}$  (pin 1) and -V $_{\rm B}$  (pin 38) are connected to the small signal stages. An additional 10V on the +V $_{\rm B}$  and -V $_{\rm B}$  pin is sufficient to allow the small signal stages to drive the output stage into the triode region and improve the output voltage swing for extra efficient operation when required. When the boost feature is not needed +V $_{\rm S}$  and -V $_{\rm S}$  are connected to +V $_{\rm B}$  and -V $_{\rm B}$  respectively. +V $_{\rm B}$  and -V $_{\rm B}$  must not be operated at supply voltages less than +V $_{\rm S}$  and -V $_{\rm S}$  respectively.

#### **SHUTDOWN**

The output stage is turned off by applying a 5V level to HSD (pin 8) relative to LSD (pin 7). This is a non-latching circuit. As long as HSD remains high relative to LSD the output stage will be turned off. LSD will normally be tied to signal ground but LSD may float from -V $_{\rm B}$  to +V $_{\rm B}$  - 10V. Shutdown can be used to lower quiescent current for standby operation or as part of a load protection circuit.

#### **BIAS CLASS OPTION**

Normally pin 5 (Iq) is left open. But when pin 5 is connected to pin 6 (Cc1) the quiescent current in the output stage is disabled. This results in lower quiescent power, but also class C operation of the output stage and the resulting crossover distortion. In many applications, such as driving motors, the distortion may be unimportant and lower standby power dissipation is an advantage.