# 5616

## 2-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCK—PROGRAMMABLE

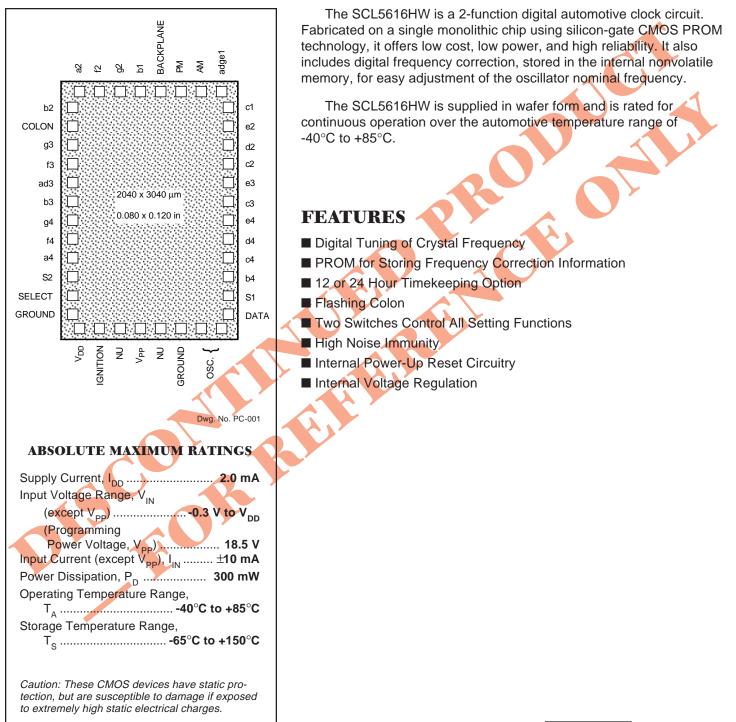

Always order by complete part number: SCL5616HW.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 1990, 1995, Allegro MicroSystems, Inc.

### **5616 2-FUNCTION, 4-DIGIT LCD AUTOMOTIVE CLOCK**

# **ELECTRICAL CHARACTERISTICS** at $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , in Typical Application (unless otherwise noted).

|                          |                   |                                                   | Limits   |           |      |       |

|--------------------------|-------------------|---------------------------------------------------|----------|-----------|------|-------|

| Characteristic           | Symbol            | Test Conditions                                   | Min.     | Тур.      | Max. | Units |

| Operating Voltage Range  | V <sub>DD</sub>   | T <sub>A</sub> = +25°C                            | 4.5      | —         |      | V     |

| Zener Voltage            | V <sub>DD</sub>   | I <sub>DD</sub> = 1.0 mA                          | 5.5      | _         | 6.8  | V     |

| Segment Output Current   | I <sub>OUT</sub>  | V <sub>DD</sub> = 5.0 V, V <sub>OUT</sub> = 4.8 V | -20      | _         |      | μA    |

|                          |                   | V <sub>DD</sub> = 5.0 V, V <sub>OUT</sub> = 0.2 V | 120      | _         |      | μA    |

| Backplane Output Current | I <sub>OUT</sub>  | V <sub>DD</sub> = 5.0 V, V <sub>OUT</sub> = 4.8 V | -80      | _         |      | μΑ    |

|                          |                   | V <sub>DD</sub> = 5.0 V, V <sub>OUT</sub> = 0.2 V | 240      | —         |      | μA    |

| LCD Drive Signal         | V <sub>DISP</sub> | V <sub>DD</sub> ≥5.0 V                            | 4.0      | _         |      | V     |

| Input Current            | I <sub>IN</sub>   | S1, S2, DATA, or SELECT                           | -55      | _         | -700 | μΑ    |

| Oscillator Frequency     | f <sub>osc</sub>  |                                                   | —        | 4.194 304 | —    | MHz   |

| Oscillator Starting Time | t <sub>osc</sub>  | V <sub>DD</sub> = Zener voltage                   | —        | _         | 200  | ms    |

| Oscillator Stability     | $\Delta f_{OSC}$  | $\Delta V_{DD} = \pm 100 \text{ mV}$              | —        | _         | ±1.0 | ррМ   |

| Backplane Frequency      | f <sub>BP</sub>   |                                                   | -        | 64        |      | Hz    |

| Switch Debounce Time     | t <sub>DB</sub>   |                                                   | 0        | _         | 62.5 | ms    |

| Osc. Feedback Resistance | R <sub>OSC</sub>  |                                                   | <b>—</b> | 16        | _    | MΩ    |

| Osc. Input Capacitance   | C <sub>OSCI</sub> |                                                   | —        | 15        |      | pF    |

| Osc. Output Capacitance  | C <sub>osco</sub> |                                                   | <u> </u> | 30        | _    | pF    |

| Supply Current           | I <sub>DD</sub>   | V <sub>DD</sub> = 5.0 V                           | —        | _         | 1.0  | mA    |

NOTE: Negative current is defined as coming out of (sourcing) the specified device terminal.

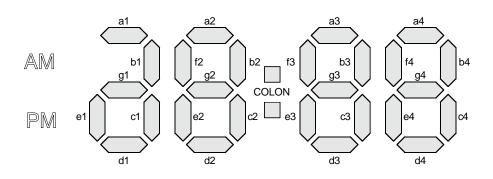

#### **DISPLAY FORMAT**

Dwg. No. OC-001

#### FUNCTIONAL DESCRIPTION DATA Logic Levels are V<sub>DD</sub> and Ground

Power-Up Reset. When power up occurs, the hours and minutes counters are reset, and the clock starts running:

#### Operation

12-Hour mode and counting starts from 1:00 AM

Programming Modes. Data is loaded by pulling DATA low (1 µs pulse duration) n times to set the desired bits for frequency correction into the data input register. This information is latched in the RAM, thus allowing the testing of the oscillator frequency adjustment without storing the selected pattern in the PROM cells. The data latched in the RAM is stored in the PROM cells when DATA is held low for a minimum of 10 ms.

The data stored in the data input register is cleared on any SELECT transition (low to high or high to low). It is also cleared when the program power voltage ( $V_{PP}$ ) is reduced from 18 V to  $V_{DD}$ . Clearing the data input register does not affect the data latched in the RAM.

| Program<br>V <sub>PP</sub> | DATA<br>V <sub>D</sub> | SELECT<br>V <sub>S</sub> | Operation                          |

|----------------------------|------------------------|--------------------------|------------------------------------|

| 18 V                       | Pulse                  | Ground                   | DATA load for frequency correction |

| 18 V                       | Ground                 | V <sub>DD</sub>          | DATA store                         |

| V <sub>DD</sub>            | $V_{DD}$               | Ground                   | Verify stored data                 |

#### **FREQUENCY CORRECTION**

#### FREQUENCY CORRECTION

SEGMENT OUTPUTS

Dwg. No. WC-001-1

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Frequency Correction. The on-chip oscillator circuit increases the crystal frequency approximately 40 ppm. This ensures that the typical crystal will operate within the tuning range. With  $V_s$  at ground, data pulses are then used to trim the internal clock frequency by 2 to 254 ppm to the required value. The quantity of data pulses needed (1 to 127) is

$$n = f_{BP} - 64$$

where  $\rm f_{_{BP}}$  is the measured frequency at BACKPLANE. Prior to trimming, it must be between 64.000 128 Hz and 64.016 256 Hz.

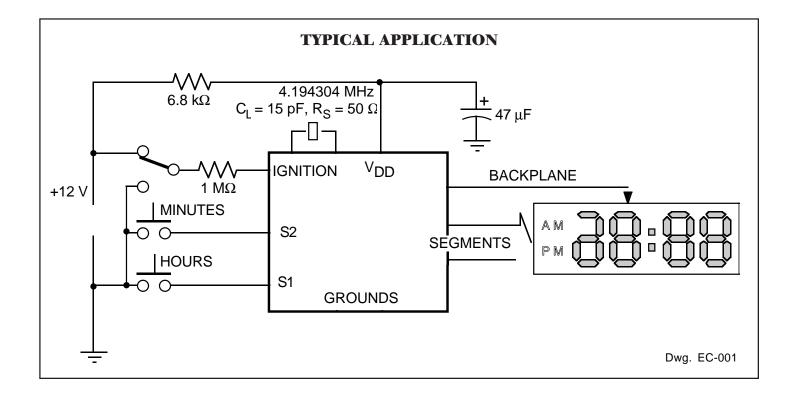

<code>Operating Modes</code>. The operating modes of the clock are controlled by the voltages applied to  $V_{\rm PP},$  SELECT, IGNITION, and switches S1 and S2.

| Program<br>V <sub>PP</sub> | SELECT<br>V <sub>S</sub> | S1     | S2     | IGNITION | Mode          |

|----------------------------|--------------------------|--------|--------|----------|---------------|

| V <sub>DD</sub>            | V <sub>DD</sub>          | Open   | Open   | Х        | Clock running |

| V <sub>DD</sub>            | V <sub>DD</sub>          | Ground | Ground | 12 V     | Diagnostic    |

| 18 V                       | Ground                   | Open   | Open   | Х        | Programming   |

X = Irrelevant, ground or 12 V

Clock Running Mode. During the clock running mode, setting functions are achieved by either momentary or continuous operation of switches S1 and S2, which are enabled by IGNITION. Hours or minutes are incremented on S1 or S2 (respectively) depression and continue at a 1 Hz rate while the switch is depressed.

| S1     | S2     | IGNITION | Operation                               |

|--------|--------|----------|-----------------------------------------|

| Open   | Open   | Х        | Clock running                           |

| Х      | Х      | Ground   | Setting disabled                        |

| Ground | Open   | 12 V     | Set hours                               |

| Open   | Ground | 12 V     | Set Minutes                             |

| Ground | Ground | 12 V     | Change counting sequence (12 to 24 hour |

|        |        |          | or 24 to 12 hour)                       |

X = Irrelevant, ground or 12 V for IGNITION, ground or open for S1 and S2

Diagnostic Mode. To enter the diagnostic mode, S1 and S2 are operated with IGNITION connected to 12 V. All segments are displayed for as long as S1 and S2 are depressed. On opening S1 and S2, the clock will leave the diagnostic mode and go through a power-up sequence. In the SCL5616HW, the counting sequence will change (from 12 hour to 24 hour or from 24 hour to 12 hour). To inhibit the power-up reset, hold the DATA input low (ground). The counting mode will change without resetting the hours or minutes counters. **Stored Data Verification.** In the verify mode, the complement value of the information stored in the PROM cells is brought out directly to the segment output terminals for easy verification of the stored data. If a bit is programmed (high), the appropriate segment output is turned ON (low). The segments represent the binary equivalent of the number of frequency correction data pulses entered.

| Frequency Selection Pulses | 64 | 32 | 16 | 8  | 4  | 2  | 1  |  |

|----------------------------|----|----|----|----|----|----|----|--|

| Segment                    | b4 | c4 | d4 | e4 | c3 | e3 | c2 |  |

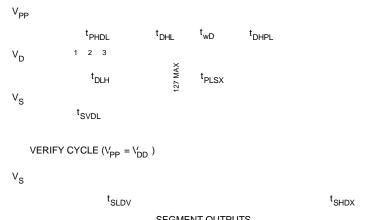

#### RECOMMENDED FLASH PROGRAMMING CHARACTERISTICS at T<sub>A</sub> = +25°C, Logic Levels are V<sub>DD</sub> and Ground (except PROGRAM High)

| Characteristic                    | Symbol            | Min. | Max. | Units |

|-----------------------------------|-------------------|------|------|-------|

| PROGRAM High (18 V) to DATA Low   | t <sub>PHDL</sub> | 1.0  |      | μs    |

| SELECT Valid to DATA Low          | t <sub>SVDL</sub> | 25   | —    | μs    |

| DATA Low to DATA High             | t <sub>DLH</sub>  | 1.0  | 1.5  | μs    |

| DATA High to DATA Low             | t <sub>DHL</sub>  | 1.0  | —    | μs    |

| DATA Store Pulse Duration         | t <sub>wD</sub>   | 10   |      | ms    |

| DATA High to PROGRAM Low          | t <sub>DHPL</sub> | 1.0  | —    | μs    |

| PROGRAM Low to SELECT Change      | t <sub>PLSX</sub> | 1.0  | _    | μs    |

| SELECT Low (Verify) to DATA Valid | t <sub>SLDV</sub> | —    | 1.0  | μs    |

| DATA Hold from End of Verify      | t <sub>SHDX</sub> | —    | 10   | ns    |

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000