# Lucent Technologies Bell Labs Innovations

# DNCM01 10/100 Ethernet MAC ASIC Macrocell

### Features

- Compliant with ISO 8802.3–1993, IEEE<sup>\*</sup> 802.3u– 1995, and IEEE 802.3x–1995 standards for media access control:

- Data transmission and reception rates of 10 Mbits/s at a clock speed of 2.5 MHz or 100 Mbits/s at a clock speed of 25 MHz.

- State machines for implementing the MII interface support standards-based connectivity to a variety of physical layer devices (PHYs).

- Transmits or receives at full- or half-duplex.

- Supports flow control.

- Supports both Level 1 and Level 2 VLAN frame recognition.

- Extensive network management signals are provided.

- Transmit and receive functions can be asynchronously reset with no clocks present.

- Supports full internal scan test methodology.

- Designed using Verilog<sup>†</sup> HDL.

- Suitable for Lucent Technologies' 0.5 μm and 0.35 μm CMOS technology (3 V or 5 V operation).

- A kit part and evaluation board is planned for evaluating the macrocell:

- The kit part provides a CPU interface for registered access to configuration and status signals, management counters, and the MII management interface.

- All configuration and status signals also go to pins to facilitate prototyping ASIC logic around the macrocell.

- Companion macrocells planned:

- 10 Mbits/s and 100 Mbits/s transceivers.

- Autonegotiation.

- Content addressable memory (CAM).

- \* *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

- <sup>†</sup> *Verilog* is a registered trademark of Cadence Design Systems, Inc.

# Description

The DNCM01 is an 802.3u–1993 compliant macrocell capable of both 10 Mbits/s and 100 Mbits/s data operation. The MAC interfaces with a transceiver through a media independent interface (MII). The transmit and receive clocks are 2.5 MHz or 25 MHz, depending on which speed the PHY is running. The DNCM01 supports half-duplex and full-duplex operation. The DNCM01 is capable of transmitting and receiving MAC control frames, including the PAUSE opcode. The DNCM01 allows full-duplex flow control using the PAUSE opcode. The DNCM01 supports both Level 1 and Level 2 VLAN tagging. The DNCM01 is able to increase the maximum legal byte count when frames are transmitted or received with Level 1 or Level 2 VLAN tags. All transmit and receive functions can be asynchronously reset with no clocks present. The DNCM01 can be used with full internal scan test methodology to ease test development time and increase fault coverage.

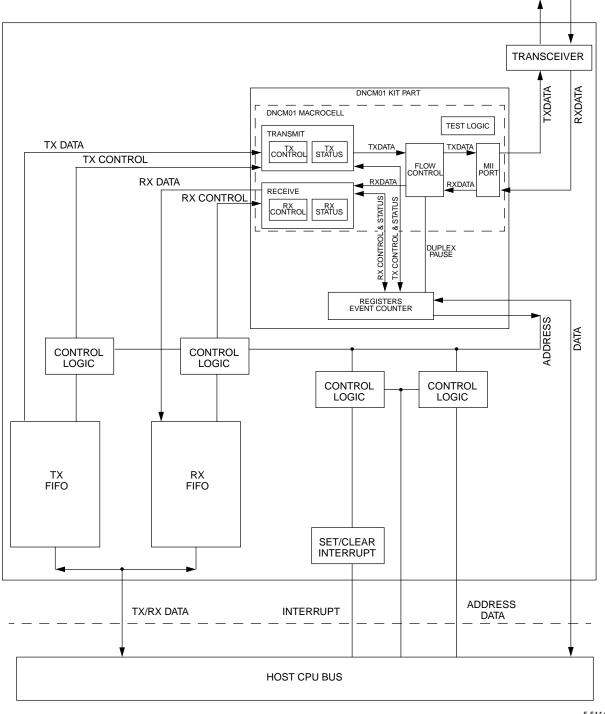

This data sheet also describes the kit part for evaluation of the DNCM01 macrocell. The kit part has a CPU interface providing access to registers that control transmit configuration and report transmit status and receive status. The kit part configuration signals are the logic OR of the configuration pins and configuration register bits. The kit part status signals are available as both register bits and output pins.

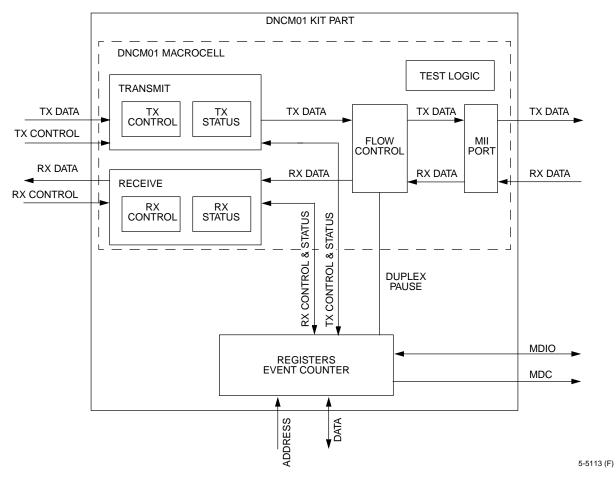

Figure 1 shows the DNCM01 block diagram.

Note: Advisories are issued as needed to update product information. When using this data sheet for design purposes, please contact your Lucent Technologies Microelectronics Group Account Manager to obtain the latest advisory on this product.

Description (continued)

Figure 1. DNCM01 (Shown in Dotted Lines) and DNCM01 Kit Part Block Diagram

# **Signal Information**

| Table 1. MI | I Signal | Descriptions | (16 | Signals) |

|-------------|----------|--------------|-----|----------|

|-------------|----------|--------------|-----|----------|

| Signal   | Туре | Description                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COL      | I    | <b>Collision (Active-High).</b> Used to indicate a collision between two stations. Assumed to be active a minimum of two TX_CLK cycles. COL is only sampled during half-duplex transmit operations when TXE is active, and during the first 64 bit times of interpacket gap time after any (normal or aborted) transmission if ISQE is active. |

| CRS      | I    | <b>Carrier Sense.</b> Asynchronously asserted by the physical layer when traffic is detected on the medium.                                                                                                                                                                                                                                    |

| RX_CLK   | I    | <b>Receive Clock.</b> 2.5 MHz or 25 MHz receive clock. RX_CLK is sourced by the physical layer device.                                                                                                                                                                                                                                         |

| RXD[3:0] | Ι    | <b>Receive Data.</b> 4-bit nibble containing received data. RXD is valid on the rising edge of RX_CLK.                                                                                                                                                                                                                                         |

| RX_DV    | I    | Receive Data Valid. Used to indicate that the data nibble on RXD has been decoded.                                                                                                                                                                                                                                                             |

| RX_ERR   | I    | <b>Receive Error.</b> RX_ERR will be asserted by the PHY when it has detected an error with the frame currently being received that the DNCM01 may not be able to detect.                                                                                                                                                                      |

| TX_CLK   | I    | <b>Transmit Clock.</b> 2.5 MHz or 25 MHz 50% duty cycle, continuously running. TX_CLK clocks all transmitter and timer logic. TX_CLK is sourced by the PHY.                                                                                                                                                                                    |

| TXD[3:0] | 0    | <b>Transmit Data.</b> 4-bit nibble with data to be transmitted. TXD is driven on the rising edge of TX_CLK.                                                                                                                                                                                                                                    |

| TX_ERR   | 0    | Transmit Error. The DNCM01 does not implement this function at this time.                                                                                                                                                                                                                                                                      |

| TX_EN    | 0    | Transmit Enable. Indicates that a transmission is in progress.                                                                                                                                                                                                                                                                                 |

#### Table 2. Kit Part CPU Interface Signal Descriptions (29 Signals)

| Signal      | Туре | Description                                                                                                                                                                                                                                                                                  |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDC         | 0    | Management Data Clock. 2.5 MHz (maximum) clock to exchange management data with a device on MDIO.                                                                                                                                                                                            |

| MDIO        | I/O  | Management Data. Bidirectional management data for external device.                                                                                                                                                                                                                          |

| RST         | I    | <b>Reset (Active-High).</b> Assumed to be asynchronous. Used to reset state machines, counters, and critical logic in the CPU interface.                                                                                                                                                     |

| CPUSTRB     | I    | <b>CPU Strobe (Active-Low).</b> During a write, this signal indicates that the data on CPUDB[7:0] bus is valid and can be latched into the MAC. During a read, this signal indicates that the MAC should drive CPUDB[7:0]. CPUAD[2:0] and CPUR/W are sampled on the falling edge of CPUSTRB. |

| CPUR/W      | Ι    | <b>CPU Read/Write.</b> Indicates which direction the CPU data bus is in for the current register or counter access. This signal should be driven high when reading a register/ counter and low when writing a register.                                                                      |

| CPURDY      | 0    | <b>CPU Ready (Active-Low).</b> This signal indicates that the MAC has latched data during a write cycle and has placed valid data onto the bus during a read cycle. An external 1 k $\Omega$ pull-up resistor is required.                                                                   |

| CPUDB[15:0] | I    | <b>CPU Data Bus.</b> This data bus is used by the CPU to write and read registers and to read counters inside the DNCM01.                                                                                                                                                                    |

| CPUAD[4:0]  | I    | <b>CPU Address Bus.</b> The address bus is used by the CPU to indicate which register/ counter is being read or written.                                                                                                                                                                     |

| HCLK        | I    | Host Clock. Clock for the DNCM01, supplied by the host.                                                                                                                                                                                                                                      |

| SELPLL      | Ι    | Select PLL. Selects the divisor of the host clock for the MDC clock of the MII inter-<br>face.<br>High—high-speed HCLK, MDC = HCLK/32<br>Low—low-speed HCLK, MDC = HCLK/16                                                                                                                   |

## Table 3. TX Control Signal Descriptions (31 Signals)

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |  |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| TXRST      | Ι    | Transmit Reset (Active-High). Assumed to be asynchronous. Used to reset state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |  |

|            |      | machines and critical logic in the transmitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |

| INVCRC     | Ι    | <b>Invert CRC (Active-High).</b> Used to invert the polarity of the 32-bit CRC polarity of the 32-bit CRC polarity of the sector of t |               |  |

| APNDCRC    | I    | Append CRC (Active-High). Used to control if a 32-bit CRC polynomial is the end of transmitted packet. If high, the CRC is appended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | appended to   |  |

| RETRY[1:0] | I    | <b>Retry.</b> Used to control the total number of attempts (initial + retries after co<br>MAC makes to transmit a packet. The total attempts follow the table below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |  |

|            |      | RETRY1 RETRY0 Attempts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |  |

|            |      | 0 0 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |  |

|            |      | 0 1 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |  |

|            |      | 1 0 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |  |

|            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |

| BSEL       | -    | Backoff Select (Active-High). Used to control whether the binary backoff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | algorithm is  |  |

| DOLL       | •    | used during collision handling. If BSEL is high, the backoff algorithm is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |  |

|            |      | transmitter jams for 32 TX_CLK cycles and attempts to retransmit after 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |

|            |      | mal IFG). If low, the transmitter follows the normal binary backoff algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |  |

|            |      | collision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ioliowing a   |  |

| DEFER      | I    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | attempt if it |  |

| DEFER      | I    | <b>Defer (Active-High).</b> Used to force the transmitter to abort a transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |  |

|            |      | has deferred for more than 24,288 TX_CLK cycles. Deferring starts when the is ready to transmit, but is prevented from doing so because CRS is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |  |

|            |      | not cumulative. If the transmitter defers for 10,000 bit times, then transmits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |  |

|            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |

|            |      | backs off, and then has to defer again after completion of backoff, the defe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |  |

|            |      | resets to 0 and restarts. If DEFER is low, the transmitter defers indefinitely.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |

| MFDUP      | I    | MAC Full Duplex (Active-High). Used to control half- or full-duplex operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |  |

|            |      | MFDUP is low, the COL input is monitored and the binary backoff algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |

|            |      | if collisions occur during transmission. When MFDUP is low and CRS is as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |  |

|            |      | the MAC's own packet is being transmitted, the receiver is not enabled since                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |  |

|            |      | packet is the MAC's own transmitted packet. When MFDUP is high, all pac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | kets are      |  |

|            |      | received regardless of the status of TXE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |

| TXREQ      | I    | Transmit Request (Active-High). Used to request a packet transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TXREQ is a    |  |

|            |      | handshake signal and should be held high until TXACK is activated by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | transmitter.  |  |

|            |      | TXREQ should not be activated until TXEOP is returned by the transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |  |