# ACT–PD1M16 Fast Page Mode 16 Megabit Plastic Monolithic DRAM

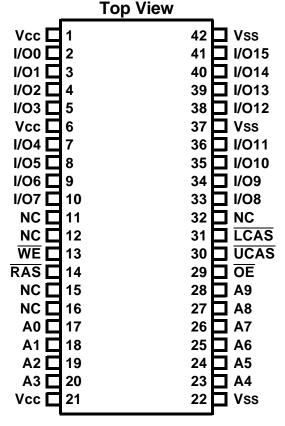

Pin Configuration

#### Pin Description

| <b>A</b> 0-9 | Address Inputs                             |

|--------------|--------------------------------------------|

| I/O0-15      | Data Input / Output                        |

| WE           | Read/Write Enable                          |

| OE           | Output Enable                              |

| RAS          | Row Address Strobe                         |

| UCAS         | Upper Byte Control / Column Address Strobe |

| LCAS         | Lower Byte Control / Column Address Strobe |

| Vcc          | +5.0V Power Supply                         |

| Vss          | Ground                                     |

| NC           | Not Connected                              |

### **Features**

- Fast Access Time (tRAC): 70ns

- Power Supply: 5.0V ± 0.5V

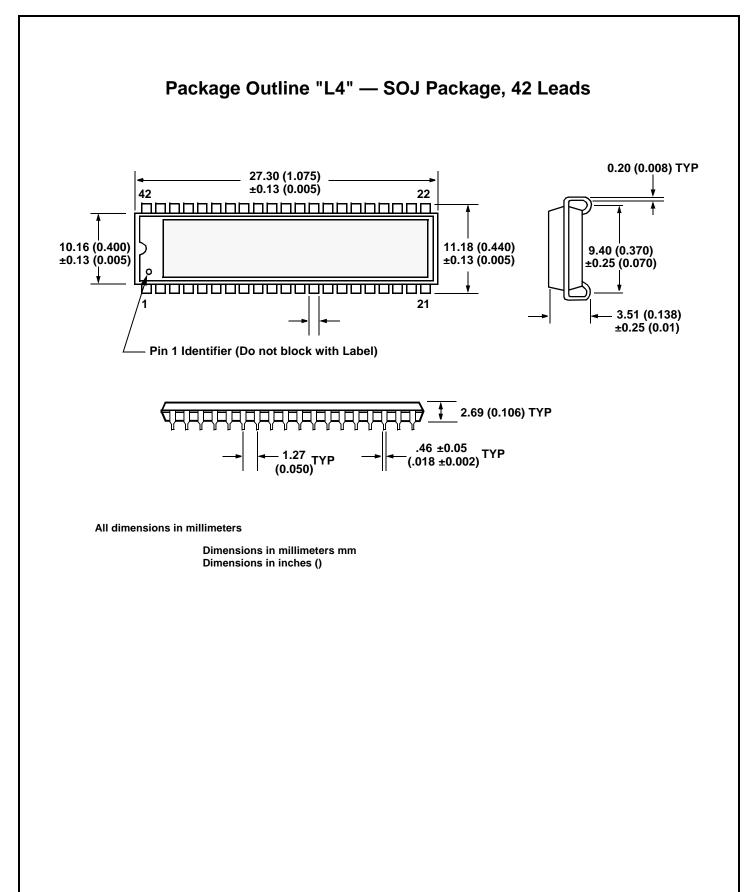

- Packaging

- 42 Lead Plastic Surface-Mount SOJ (L4)

- Industrial and Military Temperature Ranges

- Three-State Unlatched Output

- Fast Page Mode

- RAS-Only Refresh

- xCAS Before RAS Refresh

- Hidden Refresh

- 1024 Cycle Refresh in 16ms

- Low Power Dissipation

- Long Refresh Period Option

### Absolute Maximum Ratings

| Symbol           | Parameter                    | MINIMUM | MAXIMUM | Units |

|------------------|------------------------------|---------|---------|-------|

| Τ <sub>C</sub>   | Case Operating Temp.         | -55     | +125    | °C    |

| T <sub>STG</sub> | Storage Temperature          | -55     | +150    | °C    |

| I <sub>OS</sub>  | Short Circuit Output Current | -       | 50      | mA    |

| P <sub>T</sub>   | Power Dissipated             | -       | 1       | W     |

| V <sub>CC</sub>  | Supply Voltage Range         | -1.0    | +7.0    | V     |

| V <sub>T</sub>   | Voltage Range on any Pin*    | -1.0    | +7.0    | V     |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

\* All voltage values are with respect to Vss.

#### **Recommended Operating Conditions**

| Symbol          | Parameter              | Minimum | Maximum | Units |

|-----------------|------------------------|---------|---------|-------|

| V <sub>CC</sub> | Power Supply Voltage   | +4.5    | +5.5    | V     |

| V <sub>IH</sub> | Input High Voltage     | +2.4    | -       | V     |

| V <sub>IL</sub> | Input Low Voltage      | -       | +0.8    | V     |

| T <sub>CM</sub> | Operating Temp. (Mil)  | -55     | +125    | °C    |

| T <sub>CI</sub> | Operating Temp. (Ind.) | -40     | +85     | °C    |

### Capacitance

#### $(V_{IN} = 0V, f = 1MHz, Tc = 25^{\circ}C)$

| Symbol             | Parameter                          | Maximum | Units |

|--------------------|------------------------------------|---------|-------|

| C <sub>I(A)</sub>  | A <sub>0-9</sub> Input Capacitance | 10      | pF    |

| C <sub>I(RC)</sub> | RAS and CAS Input Capacitance      | 10      | pF    |

| C <sub>I(OE)</sub> | OE Input Capacitance               | 10      | pF    |

| C <sub>I(WE)</sub> | WE Input Capacitance               | 10      | pF    |

| C <sub>O</sub>     | Output Capacitance                 | 15      | pF    |

These parameters are guaranteed by design but not tested.

### **DC Characteristics**

| Parameter                                  | Sym              | Conditions                                      | Min | Max | Units |

|--------------------------------------------|------------------|-------------------------------------------------|-----|-----|-------|

| Output Low Voltage                         | V <sub>OL</sub>  | I <sub>OL</sub> = 4.2 mA                        | -   | 0.4 | V     |

| Output High Voltage                        | V <sub>OH</sub>  | I <sub>OH</sub> = -5 mA                         | 2.4 |     | V     |

| Input Leakage Current                      | ١L               | $V_{I} = 0$ to +6.5V, All others 0V to $V_{CC}$ | -10 | +10 | μA    |

| Output Leakage Current                     | Ι <sub>Ο</sub>   | $V_0 = 0$ to $V_{CC}$ , $\overline{CAS}$ high   | -10 | +10 | μA    |

| Read or Write Cycle Current <sup>1,2</sup> | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5V, minimum cycle           |     | 190 | mA    |

#### (VCC = 5.0V, VSS = 0V, TCI or TCM)

### **DC Characteristics (continued)**

(VCC = 5.0V, VSS = 0V, TCI or TCM)

| Parameter S                       |                  | Conditions                                                               | Min | Max | Units |

|-----------------------------------|------------------|--------------------------------------------------------------------------|-----|-----|-------|

| Ctandky Cymraet                   |                  | VIH = 2.4V (TTL), After 1 memory cycle,<br>RAS and $\overline{CAS}$ high | -   | 2   | mA    |

| Standby Current                   | I <sub>CC3</sub> | VIH = Vcc - 0.05V (CMOS), After 1 memory cycle, RAS and CAS high         | -   | 1   | mA    |

| Average Page Current <sup>2</sup> | I <sub>CC4</sub> | RAS low, CAS cycling                                                     | -   | 100 | mA    |

1. Measured with a maximum of one address change while  $\overline{RAS} = VIL$ .

2. Measured with a maximum of one address change while  $\overline{CAS} = VIH$ .

### AC Characteristics\*

(VCC = 5.0V ±10%, VSS= 0V, TCI or TCM)

| Parameter                                              | Sym  | Min | Max | Units |

|--------------------------------------------------------|------|-----|-----|-------|

| Access Time from Column-Address                        | tAA  | -   | 35  | ns    |

| CAS Low Access Time from CAS                           | tCAC | -   | 20  | ns    |

| Column Access Time from CAS Precharge                  | tCPA | -   | 40  | ns    |

| Access Time from RAS                                   | tRAC | -   | 70  | ns    |

| OE Access Time                                         | tOEA | -   | 20  | ns    |

| Output Buffer Turn-off Delay <sup>1</sup>              | tOFF | 0   | 15  | ns    |

| Output Buffer Turn-off Delay Time from OE <sup>1</sup> | tOEZ | 0   | 15  | ns    |

\* Valid data is presented at the outputs after all access times are satisfied but can go from the high-impedance state to an invalid-data state prior to the specified access times as the outputs are driven when  $\overline{CAS}$  goes low. 1. tOFF and tOEZ are specified when the outputs are no longer driven. The outputs are disabled by bringing either  $\overline{OE}$  or  $\overline{CAS}$  high.

#### **AC Characteristics**

(VCC = 5.0V, VSS = 0V, TCI or TCM)

| Parameter                                                 | Sym   | Min | Max     | Units |

|-----------------------------------------------------------|-------|-----|---------|-------|

| Cycle Time, Read or Write Random <sup>1</sup>             | tRC   | 130 | -       | ns    |

| Cycle Time, Fast Page Mode Read or Write <sup>1,2</sup>   | tPC   | 45  | -       | ns    |

| Cycle Time, Fast Page Mode Read-Modify-Write <sup>1</sup> | tPRWC | 90  | -       | ns    |

| Pulse Duration, RAS Low Fast Page Mode <sup>3</sup>       | tRASP | 70  | 200,000 | ns    |

| Pulse Duration, RAS Low Nonpage Mode <sup>3</sup>         | tras  | 70  | 10,000  | ns    |

| Pulse Duration, CAS Low <sup>4</sup>                      | tCAS  | 20  | 10,000  | ns    |

| Pulse Duration, CAS High Precharge Time                   | tCP   | 10  | -       | ns    |

| Pulse Duration, RAS High Precharge Time                   | tRP   | 50  | -       | ns    |

| Pulse Duration, WE Low                                    | tWP   | 15  | -       | ns    |

| Setup Time, Column Address before CAS Low                 | tASC  | 0   | -       | ns    |

| Setup Time, Row Address before RAS Low                    | tasr  | 0   | -       | ns    |

| Setup Time, Data <sup>5</sup>                             | tDS   | 0   | -       | ns    |

| Setup Time, WE High before CAS Low                        | tRCS  | 0   | -       | ns    |

| Setup Time, WE Low before CAS High                        | tCWL  | 20  | -       | ns    |

| Setup Time, WE Low before RAS High                        | tRWL  | 20  | -       | ns    |

# AC Characteristics (continued) (Vcc = 5.0V, Vss = 0V, Tcl or TcM)

| Parameter                                                                                | Sym  | Min | Max | Units |

|------------------------------------------------------------------------------------------|------|-----|-----|-------|

| Setup Time, $\overline{WE}$ Low before $\overline{CAS}$ Low (early-write operation only) | twcs | 0   | -   | ns    |

| Hold Time, Column Address after CAS Low                                                  | tCAH | 15  | -   | ns    |

| Hold Time, Data <sup>5</sup>                                                             | tDH  | 15  | -   | ns    |

| Hold Time, Row Address after RAS Low                                                     | tRAH | 10  | -   | ns    |

| Hold Time, WE High after CAS High <sup>6</sup>                                           | tRCH | 0   | -   | ns    |

| Hold Time, WE High after RAS High <sup>6</sup>                                           | tRRH | 0   | -   | ns    |

1. All cycle times assume tT= 5ns, reference to VIH (min) and VIL (max).

2. To assume tPC min, tASC should be  $\geq$  tCP.

3. In read-write cycle, tRWD and tRWL must be observed.

4. In read-write cycle, tCWD and tCWL must be observed.

5. Referenced to the later of  $\overline{xCAS}$  or  $\overline{WE}$  in write operations.

6. Either tRRH or tRCH must be satisfied for a read cycle.

#### **AC Characteristics**

(VCC = 5.0V, VSS = 0V, TCI or TCM)

| Parameter                                                         | Sym   | Min | Max | Units |

|-------------------------------------------------------------------|-------|-----|-----|-------|

| WE Low before CAS Low Hold Time (early-write operation only)      | tWCH  | 15  | -   | ns    |

| OE Command Hold Time                                              | tOEH  | 15  | -   | ns    |

| RAS Referenced to OE Hold Time                                    | tROH  | 10  | -   | ns    |

| RAS from CAS Precharge (Fast Page Mode)                           | tRHCP | 40  | -   | ns    |

| Column Address to WE Low Delay Time (read-write operation only)   | tAWD  | 60  | -   | ns    |

| RAS Low to CAS High Delay Time (CBR refresh only)                 | tCHR  | 15  | -   | ns    |

| CAS High to RAS Low Delay Time (CAS to RAS Precharge Time)        | tCRP  | 5   | -   | ns    |

| RAS Low to CAS High Delay Time (CAS Hold Time)                    | tCSH  | 70  | -   | ns    |

| CAS Low to RAS Low Delay Time (CAS Set-up Time)                   | tCSR  | 5   | -   | ns    |

| CAS Low to WE Low Delay Time (read-write operation only)          | tCWD  | 45  | -   | ns    |

| OE to Data Delay Time                                             | tOED  | 15  | -   | ns    |

| RAS Low to Column Address Delay Time <sup>1</sup>                 | tRAD  | 15  | 35  | ns    |

| Column Address to RAS High Delay Time                             | tRAL  | 35  | -   | ns    |

| RAS Low to CAS Low Delay Time <sup>1</sup>                        | tRCD  | 20  | 50  | ns    |

| RAS High to CAS Low Precharge Time                                | tRPC  | 5   | -   | ns    |

| CAS Low to RAS High Delay Time (RAS Hold Time)                    | tRSH  | 20  | -   | ns    |

| RAS Low to WE Low Delay Time (read-write operation only)          | tRWD  | 95  | -   | ns    |

| WE Low after CAS Precharge Delay Time (read-write operation only) | tCWD  | 65  | -   | ns    |

| Refresh Time Interval                                             | tREF  |     | 16  | ms    |

| Transition time <sup>2</sup>                                      | tτ    | 3   | 50  | ns    |

1. The maximum value is specified only to assure access time

2. Transition times (rise and fall) for  $\overline{RAS}$  and  $\overline{xCAS}$  are to be a minimum of 3ns and a maximum of 30ns.

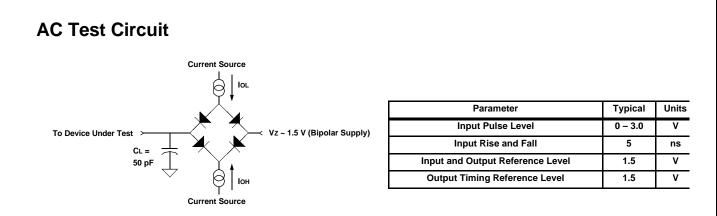

Notes: 1) Vz is programmable from -2V to +7V.

2) IOL and IOH programmable from 0 to 16 mA.

3) Tester Impedance  $ZO = 75\Omega$ .

4) Vz is typically the midpoint of VOH and VoL.

5) IOL and IOH are adjusted to simulate a typical resistance load circuit.

6) ATE Tester includes jig capacitance.

# **OPERATIONS**

### DUAL CAS

Two  $\overline{CAS}$  pins ( $\overline{LCAS}$  and  $\overline{UCAS}$ ) are provided to give independent control of the 16 data-I/O pins (I/O0-15), with LCAS corresponding to I/O0-7 and UCAS corresponding to I/O8-15. For read or write cycles, the column address is latched on the first  $\overline{xCAS}$  falling edge. Each  $\overline{xCAS}$  going low enables its corresponding I/Ox pin with data associated with the column address latched on the first falling  $\overline{xCAS}$  edge. All address setup and hold parameters are referenced to the first falling  $\overline{xCAS}$  edge. The delay time from xCAS low to valid data out (see parameter tCAC) is measured form each individual  $\overline{xCAS}$  to its corresponding I/Ox pin.

In order to latch in a new column address, both  $\overline{xCAS}$  pins must be brought high. The column-precharge time (see parameter tCP) is measured from the last  $\overline{xCAS}$  rising edge to the first  $\overline{xCAS}$  falling edge of the new cycle. Keeping <u>a</u> column address valid while toggling  $\overline{xCAS}$  requires a minimum setup time, tCLCH. During tCLCH at least one  $\overline{xCAS}$ must be brought low before the other  $\overline{xCAS}$  is taken high.

For early-write cycles, the data is latched on the first xCAS falling edge. Only the I/Os that have the corresponding xCAS low are written into. Each xCAS must meet tCAS minimum in order to ensure writing into the storage cell. To latch a new address and new data, all xCAS pins must be high and meet tCP.

### PAGE MODE

Page-mode operation allows faster memory access by keeping the same row address while selecting random column addresses. The time for row-address setup and hold and address multiplex is eliminated. The maximum number of columns that can be accessed is determined by the maximum  $\overrightarrow{RAS}$  low time and the  $\overrightarrow{xCAS}$  page-mode cycle time used. With minimum  $\overrightarrow{xCAS}$  page-cycle time, all columns can be accessed without intervening  $\overrightarrow{RAS}$  cycles.

Unlike conventional page-mode DRAMs, the column address buff-ers in this device are activated on the falling edge of RAS. The buffers act as transparent or flow-through latches while  $\overline{xCAS}$  is high. The falling edge of the first  $\overline{xCAS}$  latches the column addresses. This feature allows the devices to operate at a higher data bandwidth than conventional page-mode parts because data retrieval begins as soon as the column address is valid rather than when  $\overline{xCAS}$  transitions low. This performance improvement is referred to as enhanced page mode. A valid column address may be presented immediately after tRAH (row-address hold time) has been satisfied, usually well in advance of the falling edge of  $\overline{xCAS}$ . In this case, data is obtained after tCAC maximum (access time from  $\overline{xCAS}$ low) if tAA maximum (access time from column address) has been satisfied. In the event that column addresses for the next page cycle are valid at the time  $\overline{xCAS}$  goes high, minimum access time for the next cycle is determined by tCPA (access time from rising edge of the last  $\overline{xCAS}$ ).

### ADDRESS: A0-9

Twenty address bits are required to decode 1 of 1048576 storage cell locations. For the ACTPD1M16, 10 row-address bits are set up on A0 through A9 and latched onto the chip by RAS. Ten, column-address bits are set up on A0 through A9 and latched onto the chip by the first xCAS. All addresses must be stable on or before the falling edge of RAS and xCAS. RAS is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder. xCAS is used as a chip select, activating its correspond-ing output buffer and latching the address bits into the column-address buffers.

### WRITE ENABLE (WE)

The read or write mode is selected through  $\overline{WE}$ . A logic high on  $\overline{WE}$  selects the read mode and a logic low selects the write mode. The data inputs are disabled when the read mode is selected. When  $\overline{WE}$  goes low prior to  $\overline{xCAS}$  (early write), data out remains in the high-impedance state for the entire cycle, permitting a write operation with  $\overline{OE}$  grounded.

### DATA IN (I/O0-15)

Data written during write is а or read-modify-write cycle. Depending on the mode of operation, the falling edge of  $\overline{xCAS}$  or WE strobes data into the on-chip data latch. In an early-write cycle,  $\overline{WE}$  is brought low prior to  $\overline{xCAS}$  and the data is strobed in by the first occurring xCAS with setup and hold times referenced to this signal. In a delayed-write or read-modify-write cycle,  $\overline{xCAS}$  is already low and the data is strobed in by  $\overline{WE}$  with setup and hold times referenced to this signal. In a delaved-write or read-modify-write cycle. OE must be high to bring the output buffers to the high-impedance state prior to impressing data on the I/O lines.

### DATA OUT (I/O0-15)

Data out is the same polarity as data in. The output is in the high-impedance (floating) state until xCAS and OE are brought low. In a read cycle, the output becomes valid after the access time interval tCAC (which begins with the negative transition of xCAS) as long as tRAC and tAA are satisfied.

## OUTPUT ENABLE (OE)\*

$\overline{OE}$  controls the impedance of the output buffers. When  $\overline{OE}$  is high, the buffers remain in the high-impedance state. Bringing  $\overline{OE}$  low during a normal cycle activates the output buffers, putting them in the low-impedance state. It is necessary for both RAS and xCAS to be brought low for the output butters to go into the low-impedance state, and they remain in the low-impedance state until either  $\overline{OE}$  or  $\overline{xCAS}$  is brought high.

\*Output Enable can be held low during write cycles.

## RAS-ONLY REFRESH

A refresh operation must be performed at least once every 16ms (128ms for long refresh periods) to retain data. This can be achieved by strobing each of the 1024 rows (A0-9). A normal read or write cycle refreshes all bits in each row that is selected. A RAS-only operation can be used by holding both  $\overline{xCAS}$  at the high (inactive) level, conserving power as the output buffers high-impedance remain in the state. Externally generated addresses must be used for a RAS-only refresh.

### HIDDEN REFRESH

Hidden refresh can be performed while maintaining valid data at the output pin. This is accomplished by holding xCAS at VIL after a read operation and cycling RAS after a specified precharge period, similar to a RAS-only refresh cycle. The external address is ignored and the refresh address is generated internally.

# xCAS-BEFORE-RAS(xCBR)REFRESH

**x**CBR refresh is utilized by bringing at least one xCAS low earlier than RAS (see parameter tCSR) and holding it low after RAS fails (see parameter tCHR). For succesive xCBR refresh cycles, xCAS can remain low while cycling RAS. The external address is ignored and the refresh address is generated internally.

### POWER UP

To achieve proper device operation, an initial pause of 200 $\mu$ s followed by a minimum of eight initialization cycles is required after power up to full Vcc level. These eight initialization cycles must include at least one refresh (RAS-only or xCBR) cycle.

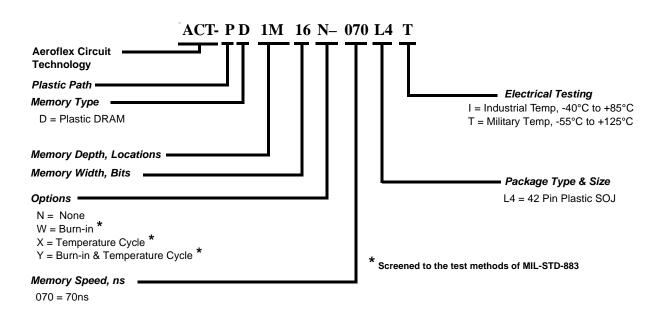

### **Ordering Information (Typical)**

| Model Number       | Options              | Speed | Package     |

|--------------------|----------------------|-------|-------------|

| ACT-PD1M16N-070L4I | None                 | 70ns  | 42 Lead SOJ |

| ACT-PD1M16W-070L4I | Burn-in              | 70ns  | 42 Lead SOJ |

| ACT-PD1M16X–070L4I | Temp Cycle           | 70ns  | 42 Lead SOJ |

| ACT-PD1M16Y-070L4I | Temp Cycle & Burn-in | 70ns  | 42 Lead SOJ |

| ACT-PD1M16N-070L4T | None                 | 70ns  | 42 Lead SOJ |

| ACT-PD1M16W-070L4T | Burn-in              | 70ns  | 42 Lead SOJ |

| ACT-PD1M16X-070L4T | Temp Cycle           | 70ns  | 42 Lead SOJ |

| ACT-PD1M16Y-070L4T | Temp Cycle & Burn-in | 70ns  | 42 Lead SOJ |

### Part Number Breakdown

#### Aeroflex Circuit Technology 35 South Service Road Plainview New York 11830

Telephone: (516) 694-6700 FAX: (516) 694-6715 Toll Free Inquiries: 1-(800) 843-1553