# 50 MHz to 4 GHz TruPwr™ Detector

### PRELIMINARY TECHNICAL DATA

ADL5501

#### **FEATURES**

True rms response

Excellent temperature stability

Up to 30 dB input dynamic range at 4 GHz

50 Ω input impedance

1.25 V rms, +15 dBm, maximum input

Single-supply operation: 2.7 V to 5.5 V

Low power: 3 mW at 3 V supply

RoHS Compliant

#### **APPLICATIONS**

Measurement of CDMA, CDMA2000, W-CDMA, and QPSK/QAM-based OFDM, and other complex modulation waveforms

RF transmitter or receiver power measurement

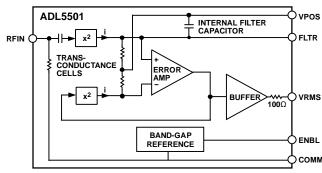

#### **FUNCTIONAL BLOCK DIAGRAM**

Fiaure 1.

#### **GENERAL DESCRIPTION**

The ADL5501 is a mean-responding power detector for use in high frequency receiver and transmitter signal chains from 50 MHz to 4 GHz. It is easy to apply, requiring only a single supply between 2.7 V and 5.5 V and a power supply decoupling capacitor. The input is internally ac-coupled and has a nominal input impedance of 50  $\Omega$ . The output is a linear-responding dc voltage with a conversion gain of 6.6 V/V rms at 900 MHz.

The ADL5501 is intended for true power measurement of simple and complex waveforms. The device is particularly useful for measuring high crest factor (high peak-to-rms ratio) signals, such as CDMA, CDMA2000, W-CDMA, and QPSK/QAM-based OFDM waveforms. The on-chip modulation filter provides adequate averaging for most waveforms. The on-chip, 100  $\Omega$  series resistance at the output

combined with an external shunt capacitor creates a low-pass filter response that reduces the residual ripple in the dc output voltage. For more complex waveforms, an external capacitor at the FLTR pin can be used for supplementary signal demodulation.

The ADL5501 offers excellent temperature stability across a 30 dB range and near 0 dB measurement error across temperature over the top portion of the dynamic range. In addition to its temperature stability, the ADL5501 offers low process variations which further reduces calibration complexity.

The ADL5501 operates from  $-40^{\circ}$ C to  $+85^{\circ}$ C and is available in a 6-lead, 2.0 mm  $\times$  2.1 mm SC-70 package. It is fabricated on a proprietary high  $f_T$  silicon bipolar process.

## ADL5501

### TARGET SPECIFICATIONS

$T_A$  = 25°C,  $V_S$  = 3.0 V,  $C_{FLTR}$  = Open,  $C_{OUT}$  = 100 nF, unless otherwise noted.

Table 1.

| Parameter                     | Condition                                             | Min | Тур      | Max  | Unit    |

|-------------------------------|-------------------------------------------------------|-----|----------|------|---------|

| FREQUENCY RANGE               | (Input RFIN)                                          | 50  |          | 4000 | MHz     |

| RMS CONVERSION (f = 100 MHz)  | (Input RFIN to output VRMS)                           |     |          |      |         |

| Input Impedance               |                                                       |     | 77  4.7  |      | Ω  pF   |

| Input Return Loss             |                                                       |     | 12.5     |      | dB      |

| Dynamic Range <sup>1</sup>    | CW input, $-40$ °C $< T_A < +85$ °C                   |     |          |      |         |

| ±1 dB Error <sup>2</sup>      | $V_S = 3 V$                                           |     | TBD      |      | dB      |

|                               | $V_S = 5 V$                                           |     | 30       |      | dB      |

| Conversion Gain               | $VOUT = (Gain \times V_{IN}) + Intercept$             | TBD | 7.4      | TBD  | V/V rms |

| Output Intercept <sup>3</sup> |                                                       | TBD | 0.03     | TBD  | V       |

| Output Voltage—High Power In  | $P_{IN} = +5 \text{ dBm}, 400 \text{ mV rms}$         |     | 3.06     |      | V       |

| Output Voltage—Low Power In   | $P_{IN} = -21 \text{ dBm}, 20 \text{ mV rms}$         |     | 0.17     |      | V       |

| Temperature Sensitivity       | $P_{IN} = -5 \text{ dBm}$                             |     |          |      |         |

|                               | $25^{\circ}C \leq T_A \leq 85^{\circ}C$               |     | 0.0026   |      | dB/°C   |

|                               | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+25$ °C        |     | -0.0023  |      | dB/°C   |

| RMS CONVERSION (f = 900 MHz)  | (Input RFIN to output VRMS)                           |     |          |      |         |

| Input Impedance               |                                                       |     | 40  0.7  |      | Ω  pF   |

| Input Return Loss             |                                                       |     | 16.5     |      | dB      |

| Dynamic Range                 | CW input, -40°C < T <sub>A</sub> < +85°C              |     |          |      |         |

| ±1 dB Error                   | $V_S = 3 V$                                           |     | TBD      |      | dB      |

|                               | $V_S = 5 V$                                           |     | 26       |      | dB      |

| Conversion Gain               | $VOUT = (Gain \times V_{IN}) + Intercept$             |     | 6.6      |      | V/V rms |

| Output Intercept              |                                                       |     | 0.03     |      | V       |

| Output Voltage—High Power In  | $P_{IN} = +5 \text{ dBm}, 400 \text{ mV rms}$         |     | 2.69     |      | V       |

| Output Voltage—Low Power In   | $P_{IN} = -21 \text{ dBm}, 20 \text{ mV rms}$         |     | 0.15     |      | V       |

| Temperature Sensitivity       | $P_{IN} = -5 \text{ dBm}$                             |     |          |      |         |

| •                             | 25°C ≤T <sub>A</sub> ≤ 85°C                           |     | 0.0039   |      | dB/°C   |

|                               | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+25$ °C        |     | -0.0046  |      | dB/°C   |

| RMS CONVERSION (f = 1900 MHz) | (Input RFIN to output VRMS)                           |     |          |      |         |

| Input Impedance               | (                                                     |     | 64  -0.5 |      | Ω  pF   |

| Input Return Loss             |                                                       |     | 13.5     |      | dB      |

| Dynamic Range                 | CW input, -40°C < T <sub>A</sub> < +85°C              |     |          |      |         |

| ±1 dB Error                   | V <sub>S</sub> = 3 V                                  |     | TBD      |      | dB      |

|                               | $V_S = 5 \text{ V}$                                   |     | 33       |      | dB      |

| Conversion Gain               | $VOUT = (Gain \times V_{IN}) + Intercept$             |     | 5.7      |      | V/V rms |

| Output Intercept              | (11.00)                                               |     | 0.02     |      | V V     |

| Output Voltage—High Power In  | $P_{IN} = +5 \text{ dBm}, 400 \text{ mV rms}$         |     | 2.36     |      | V       |

| Output Voltage—Low Power In   | $P_{IN} = -21$ dBm, 20 mV rms                         |     | 0.13     |      | V       |

| Temperature Sensitivity       | $P_{IN} = -5 \text{ dBm}$                             |     |          |      |         |

|                               | 25°C ≤ T <sub>A</sub> ≤ 85°C                          |     | 0.0049   |      | dB/°C   |

|                               | $-40^{\circ}\text{C} \le T_A \le +25^{\circ}\text{C}$ |     | -0.0076  |      | dB/°C   |

| Parameter                                  | Condition                                                                         | Min  | Тур       | Max       | Unit    |

|--------------------------------------------|-----------------------------------------------------------------------------------|------|-----------|-----------|---------|

| RMS CONVERSION (f = 2350 MHz)              | (Input RFIN to output VRMS)                                                       |      |           |           |         |

| Input Impedance                            |                                                                                   |      | 83  -0.06 |           | Ω  pF   |

| Input Return Loss                          |                                                                                   |      | 12        |           | dB      |

| Dynamic Range                              | CW input, $-40$ °C $<$ T <sub>A</sub> $<$ $+85$ °C                                |      |           |           |         |

| ±1 dB Error                                | $V_S = 3 V$                                                                       |      | TBD       |           | dB      |

|                                            | $V_S = 5 V$                                                                       |      | 32        |           | dB      |

| Conversion Gain                            | $VOUT = (Gain \times V_{IN}) + Intercept$                                         |      | 5.1       |           | V/V rms |

| Output Intercept                           |                                                                                   |      | 0.02      |           | V       |

| Output Voltage—High Power In               | $P_{IN} = +5 \text{ dBm}, 400 \text{ mV rms}$                                     |      | 2.11      |           | V       |

| Output Voltage—Low Power In                | $P_{IN} = -21 \text{ dBm, } 20 \text{ mV rms}$                                    |      | 0.12      |           | V       |

| Temperature Sensitivity                    | $P_{IN} = -5 \text{ dBm}$                                                         |      |           |           |         |

|                                            | 25°C ≤ T <sub>A</sub> ≤ 85°C                                                      |      | 0.0051    |           | dB/°C   |

|                                            | -40°C ≤ T <sub>A</sub> ≤ +25°C                                                    |      | -0.0142   |           | dB/°C   |

| OUTPUT OFFSET                              | No signal at RFIN                                                                 |      | 50        | TBD       | mV      |

| ENABLE INTERFACE                           | (Pin ENBL)                                                                        |      |           |           |         |

| Logic Level to Enable Power, HI Condition  | $2.7 \le V_S \le 5.5 \text{ V}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$  | 1.8  |           | $V_{POS}$ | V       |

| Input Current when HI                      | $2.7 \text{ V at ENBL}$ , $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ |      | 0.2       | TBD       | μΑ      |

| Logic Level to Disable Power, LO Condition | $2.7 \le V_S \le 5.5 \text{ V}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$  | -0.5 |           | 0.8       | V       |

| Power-Up Response Time⁴                    | $C_{FLTR} = C_{OUT} = Open, 0 dBm at RFIN$                                        |      | 5         |           | μs      |

|                                            | C <sub>FLTR</sub> = 100nF, C <sub>OUT</sub> = Open, 0 dBm at RFIN                 |      | TBD       |           | μs      |

| POWER SUPPLY                               |                                                                                   |      |           |           |         |

| Operating Range                            | -40°C < T <sub>A</sub> < +85°C                                                    | 2.7  |           | 5.5       | V       |

| Quiescent Current                          | No signal at RFIN, ENBL Input HI <sup>5</sup>                                     |      | 1.0       |           | mA      |

| Total Supply Current when Disabled         | No signal at RFIN, ENBL Input LO                                                  |      | <1        | TBD       | μΑ      |

<sup>&</sup>lt;sup>1</sup> The available output swing, and hence the dynamic range, is altered by the supply voltage; see TDB.

<sup>2</sup> Error referred to best-fit line at 25°C

<sup>3</sup> Calculated using linear regression.

<sup>4</sup> The response time is measured from 10%–90% of settling level; see TDB.

<sup>5</sup> Supply current is input level dependant; see TBD.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                        | Rating          |

|----------------------------------|-----------------|

| Supply Voltage V <sub>S</sub>    | 5.5 V           |

| VRMS                             | 0 V, Vs         |

| RFIN                             | 1.25 V rms      |

| Equivalent Power, re 50 $\Omega$ | 15 dBm          |

| Internal Power Dissipation       | TBD mW          |

| θ <sub>JA</sub> (SC-70)          | TBD°C/W         |

| Maximum Junction Temperature     | 125℃            |

| Operating Temperature Range      | −40°C to +85°C  |

| Storage Temperature Range        | −65°C to +150°C |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

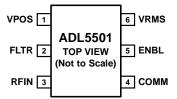

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. 6-Lead SC-70 Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                       |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VPOS     | Supply Voltage Pin. Operational range 2.7 V to 5.5 V.                                                                                                                                                                                                                                             |

| 2       | FLTR     | Modulation Filter Pin. Connection for an External Capacitor to lower the corner frequency of the modulation filter. Capacitor is connected between FLTR and $V_5$ . The on-chip filter is approximately TBD pF. For simple waveforms, no further filtering of the demodulated signal is required. |

| 3       | RFIN     | Signal Input Pin. Internally ac-coupled after internal termination resistance. Nominal 50 $\Omega$ input impedance.                                                                                                                                                                               |

| 4       | COMM     | Device Ground Pin.                                                                                                                                                                                                                                                                                |

| 5       | ENBL     | Enable Pin. Connect Pin to $V_S$ for Normal Operation. Connect pin to ground for disable mode for a supply current less than 1 $\mu$ A.                                                                                                                                                           |

| 6       | VRMS     | Output Pin. Rail-to-rail voltage output with limited 3 mA current drive capability. The output has an internal $100 \Omega$ series resistance. High resistive loads are recommended to preserve output swing.                                                                                     |

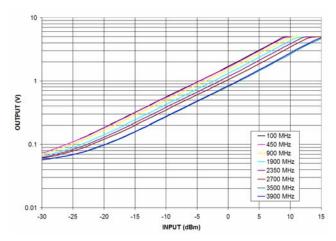

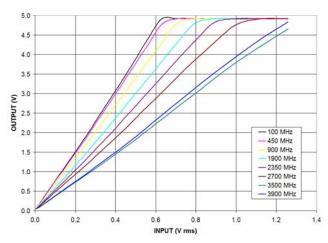

### TYPICAL PERFORMANCE CHARACTERISTICS

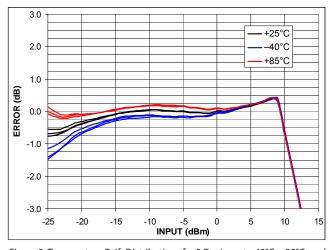

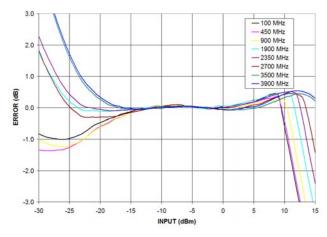

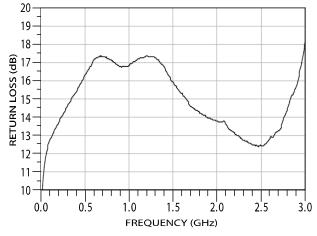

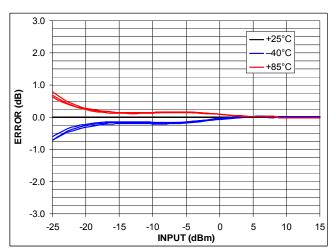

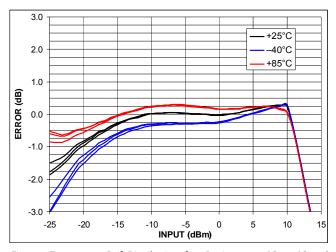

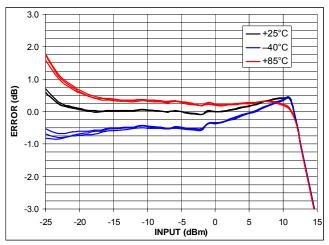

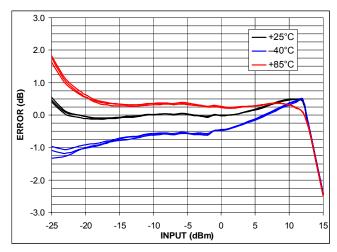

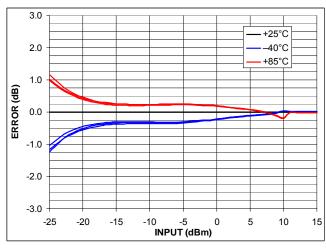

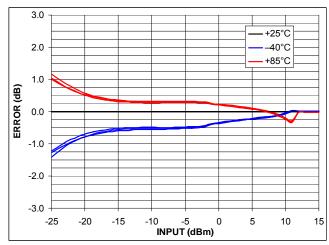

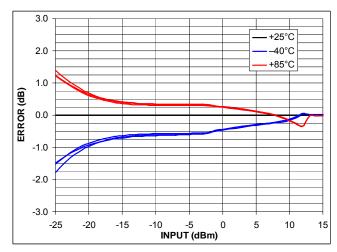

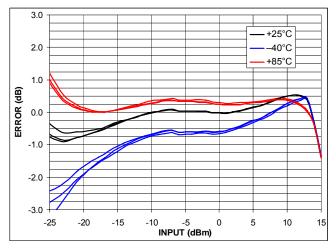

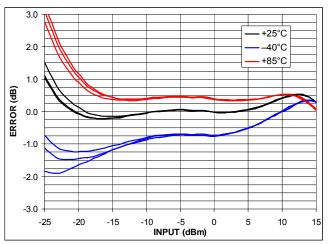

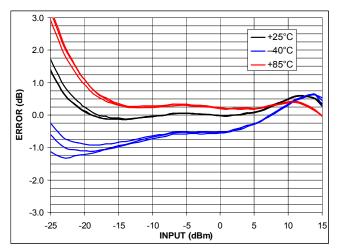

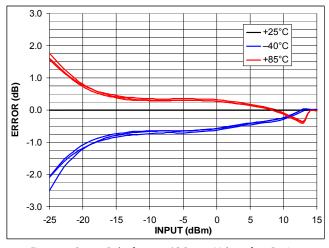

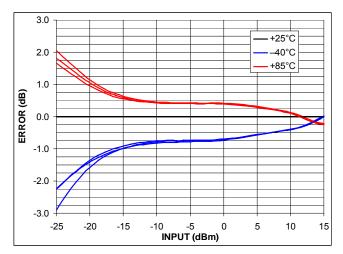

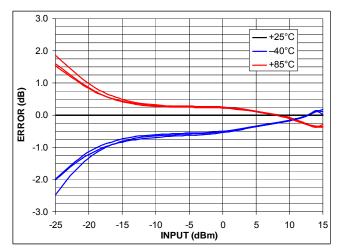

$T_A = 25^{\circ}\text{C}$ ,  $V_S = 5.0 \text{ V}$ ,  $C_{\text{FLTR}} = \text{Open}$ ,  $C_{\text{OUT}} = 100 \text{ nF}$ ,  $C_{\text{Olors}}$ :  $black = +25^{\circ}\text{C}$ ,  $blue = -40^{\circ}\text{C}$ ,  $red = +85^{\circ}\text{C}$ , unless otherwise noted.

Figure 3. Output vs. Input Level, Frequencies 100 MHz, 450 MHz, 900 MHz, 1900 MHz, 2350 MHz, 2700 MHz, 3500 MHz, and 3900 MHz, Supply 5.0 V

Figure 4. Output vs. Input Level (Linear Scale), Freq 100 MHz, 450 MHz, 900 MHz, 1900 MHz, 2350 MHz, 2700 MHz, 3500 MHz, and 3900 MHz, Supply 5.0 V

Figure 5. Temperature Drift Distributions for 3 Devices at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C vs.  $+25^{\circ}$ C Linear Reference, Frequency 100 MHz, Supply 5.0 V

Figure 6. Linearity Error vs. Input Level, Freq 100 MHz, 450 MHz, 900 MHz, 1900 MHz, 2350 MHz, 2700 MHz, 3500 MHz, and 3900 MHz, Supply 5.0 V

Figure 7. Return Loss vs. Frequency

Figure 8. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 100 MHz, Supply 5.0 V

Figure 9. Temperature Drift Distributions for 3 Devices at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C vs.  $+25^{\circ}$ C Linear Reference, Frequency 900 MHz, Supply 5.0 V

Figure 10. Temperature Drift Distributions for 3 Devices at −40°C, +25°C, and +85°C vs. +25°C Linear Reference, Frequency 1900 MHz, Supply 5.0 V

Figure 11. Temperature Drift Distributions for 3 Devices at -40°C, +25°C, and +85°C vs. +25°C Linear Reference, Frequency 2350 MHz, Supply 5.0 V

Figure 12. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 900 MHz, Supply 5.0 V

Figure 13. Output Delta from +25°C Output Voltage for 3 Devices at -40°C and +85°C, Frequency 1900 MHz, Supply 5.0 V

Figure 14. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 2350 MHz, Supply 5.0 V

Figure 15. Temperature Drift Distributions for 3 Devices at −40°C, +25°C, and +85°C vs. +25°C Linear Reference, Frequency 2700 MHz, Supply 5.0 V

Figure 16. Temperature Drift Distributions for 3 Devices at −40°C, +25°C, and +85°C vs. +25°C Linear Reference, Frequency 3500 MHz, Supply 5.0 V

Figure 17. Temperature Drift Distributions for 3 Devices at −40°C, +25°C, and +85°C vs. +25°C Linear Reference, Frequency 3900 MHz, Supply 5.0 V

Figure 18. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 2700 MHz, Supply 5.0 V

Figure 19. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 3500 MHz, Supply 5.0 V

Figure 20. Output Delta from  $+25^{\circ}$ C Output Voltage for 3 Devices at  $-40^{\circ}$ C and  $+85^{\circ}$ C, Frequency 3900 MHz, Supply 5.0 V

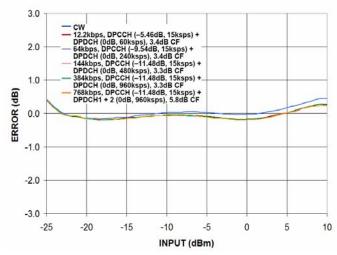

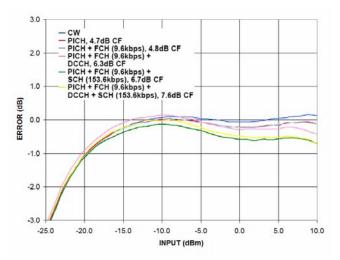

Figure 21. Error from CW Linear Reference vs. Input with Various WCDMA Up Link Waveforms at 1900 MHz,  $C_{FLTR} = Open$ ,  $C_{OUT} = 100$  nF

Figure 22. Error from CW Linear Reference vs. Input with Various CDMA2000 Reverse Link Waveforms at 900 MHz,  $C_{FLTR}=1$  nF,  $C_{OUT}=100$  nF

#### **EVALUATION BOARD**

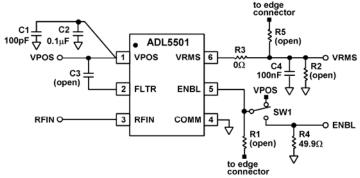

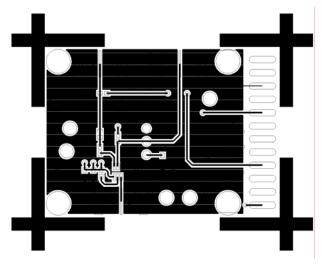

Figure 23 shows the schematic of the ADL5501 evaluation board. The layout and silkscreen of the evaluation board layers are shown in Figure 24 to Figure 27. The board is powered by a single supply in the 2.7 V to 5.5 V range. The power supply is decoupled by 100 pF and 0.1  $\mu F$  capacitors. Table 4 details the various configuration options of the evaluation board.

Problems caused by impedance mismatch can arise using the evaluation board to examine the ADL5501 performance. One way to reduce these problems is to put a coaxial 3 dB attenuator on the RFIN SMA connector. Mismatches at the source, cable, and cable interconnection, as well as those occurring on the evaluation board, can cause these problems.

A simple (and common) example of such a problem is triple travel due to mismatch at both the source and the evaluation

board. Here the signal from the source reaches the evaluation board and mismatch causes a reflection. When that reflection reaches the source mismatch, it causes a new reflection, which travels back to the evaluation board, adding to the original signal incident at the board. The resultant voltage varies with both cable length and frequency dependence on the relative phase of the initial and reflected signals. Placing the 3 dB pad at the input of the board improves the match at the board and thus reduces the sensitivity to mismatches at the source. When such precautions are taken, measurements are less sensitive to cable length and other fixture issues. In an actual application when the distance between ADL5501 and source is short and well-defined, this 3 dB attenuator is not needed.

Figure 23. Evaluation Board Schematic

**Table 4. Evaluation Board Configuration Options**

| Component  | omponent Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

| VPOS, GND  | Ground and Supply Vector Pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Not Applicable                                                                  |  |

| C1, C2     | Power Supply Decoupling. The nominal supply decoupling of 0.01 μF and 100 pF.                                                                                                                                                                                                                                                                                                                                                                                                          | C1 = 0.1 $\mu$ F (Size 0402)<br>C2 = 100 $\mu$ F (Size 0402)                    |  |

| C3         | Filter Capacitor. The internal averaging capacitor can be augmented by placing additional capacitance in C3.                                                                                                                                                                                                                                                                                                                                                                           | C3 = Open (Size 0402)                                                           |  |

| R2, R3, C4 | Output Filtering. The combination of the internal $100\Omega$ output resistance and C4 produce a low-pass filter to reduce output ripple. The output can also be scaled down using the resistor divider pads, R3 and R8. In addition, resistors and capacitors can be placed in C4 and R8 to load test VRMS.                                                                                                                                                                           | R2 = Open (Size 0402)<br>R3 = 0 $\Omega$ (Size 0402)<br>C4 = 100 nF (Size 0402) |  |

| R4, SW1    | Device Enable. When the switch is set towards the "SW1" label, the ENBL pin is connected to VPOS and the ADL5501 is in operating mode. In the opposite switch position, the ENBL pin is grounded (through the 49.9 $\Omega$ resistor) putting the device in power-down mode. While in this switch position, the ENBL pin can be driven by a signal generator via the SMA labeled ENBL. In this case, R4 serves as a termination resistor for generators requiring a 50 $\Omega$ match. | R4 = 49.9 $\Omega$ (Size 0402)<br>SW1 = towards "SW1"<br>label                  |  |

| R1, R5     | Alternate Interface. R6 allows VOUT to be accessible from the edge connector, which is only used for characterization.                                                                                                                                                                                                                                                                                                                                                                 | R1 = Open (Size 0402)<br>R5 = Open (Size 0402)                                  |  |

Figure 24. Layout of Component Side

Figure 26. Silkscreen of Component Side

Figure 25. Layout of Circuit Side

Figure 27. Silkscreen of Circuit Side

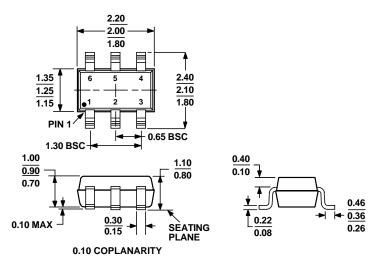

## **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MO-203-AB

Figure 28. 6-Lead Thin Shrink Small Outline Transistor Package [SC-70] (KS-6) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                           | Temperature<br>Range | Package Description           | Package<br>Outline | Branding | Ordering Quantity |

|---------------------------------|----------------------|-------------------------------|--------------------|----------|-------------------|

| ADL5501AKSZ-<br>R7 <sup>1</sup> | -40°C to +85°C       | 6-Lead SC-70, 7"Tape and Reel | KS-6               | Q0Z      | 3,000             |

| ADL5501AKSZ-R2 <sup>1</sup>     | -40°C to +85°C       | 6-Lead SC-70, 7"Tape and Reel | KS-6               | Q0Z      | 250               |

| ADL5501-EVAL                    |                      | Evaluation Board              |                    |          |                   |

$<sup>^{1}</sup>$  Z = Pb-free part.

## **NOTES**