## **Revision History**

### **Revision 1 ( Dec. 2001 )**

1.Fister release.

### Revision 2 (Apr. 2002)

- 1. Changed module current specification.

- 2. Add Performance range.

- 3. Changed AC Characteristics.

- 4. Changed typo size on module PCB in package dimensions.

#### **Double Data Rate SDRAM**

#### 4M x 16 Bit x 4 Banks

#### **General Description**

The ADD8616A8A are four-bank Double Data Rate(DDR) Synchronous DRAMs organized as 4,194,304 words x 16 bits x 4 banks,

Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle.

Data outputs occur at both rising edges of CK and /CK.

Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth high performance memory system applications

#### **Features**

- 2.5V for VDDQ power supply

- · SSTL\_2 interface

- MRS Cycle with address key programs

- -CAS Latency (2, 2.5)

- -Burst Length (2,4 &8)

- -Burst Type (sequential & Interleave)

- 4 banks operation

- Differential clock input (CK, /CK) operation

- · Double data rate interface

- · Auto & Self refresh

- · 8192 refresh cycle

- · DQM for masking

- · Package:66-pins 400 mil TSOP-Type II

#### **Ordering Information.**

| Part No.        | Frequency             | Interface | Package             |  |

|-----------------|-----------------------|-----------|---------------------|--|

| VDD8608A8A-75BA | 133Mhz(7.5ns /CL=2)   | 0071 0    | 400mil Comin TOODU  |  |

| ADD8616A8A-75B  | 133Mhz(7.5ns /CL=2.5) | SSTL_2    | 400mil 66pin TSOPII |  |

#### **Pin Assignment**

| VDD             | ᅥ      | 1 🔾 | 66  | Ь | Vss       |

|-----------------|--------|-----|-----|---|-----------|

| DQ <sub>0</sub> | ㅁ      | 2   | 65  | Ь | DQ7       |

| VDDQ            | ㅁ      | 3   | 64  | Þ | VssQ      |

| NC              | ㅁ      | 4   | 63  | Þ | NC        |

| DQ1             | $\Box$ | 5   | 62  | 巨 | DQ6       |

| Vssq            | $\Box$ | 6   | 61  | Þ | VDDQ      |

| NC              | $\Box$ | 7   | 60  | Þ | NC        |

| DQ2             | $\Box$ | 8   | 59  | 口 | DQ5       |

| VDDQ            |        | 9   | 58  | Þ | Vssq      |

| NC              |        | 10  | 57  | Þ | NC        |

| DQ3             |        | 1 1 | 56  | 尸 | DQ4       |

| Vssq            |        | 12  | 55  | 尸 | VDDQ      |

| NC              |        | 13  | 54  | 口 | NC        |

| NC              |        | 14  | 53  | 尸 | NC        |

| VDDQ            |        | 15  | 52  | 尸 | Vssq      |

| NC              |        | 16  | 5 1 | P | DQS       |

| NC              |        | 17  | 50  | 尸 | NC        |

| $V_{DD}$        |        | 18  | 49  | 口 | $V_{REF}$ |

| NC              |        | 19  | 48  | 口 | Vss       |

| NC              |        | 20  | 47  | 口 | DM        |

| WE              |        | 21  | 46  | 口 | CK        |

| CAS             |        | 22  | 45  | 尸 | CK        |

| RAS             |        | 23  | 44  | 尸 | CKE       |

| cs              |        | 24  | 43  | 尸 | NC        |

| NC              |        | 25  | 42  | 尸 | NC        |

| BAO             |        | 26  | 41  | 尸 | A11       |

| BA1             |        | 27  | 40  | 尸 | A9        |

| 410/AP          |        | 28  | 39  | P | 8A        |

| A0              |        | 29  | 38  | 尸 | A7        |

| A1              |        | 30  | 37  | 尸 | A 6       |

| A2              |        | 31  | 36  | P | A5        |

| A3              |        | 32  | 35  | P | A4        |

| VDD             |        | 33  | 34  | P | $V_{SS}$  |

|                 |        |     |     | J |           |

66-pin plastic TSOP II 400 mil

# Pin Description

| PIN       | NAME                     | FUNCTION                                                              |

|-----------|--------------------------|-----------------------------------------------------------------------|

| CK, /CK   | System Clock             | Differential clock input.                                             |

| CKE       | Clock Enable             | Masks system clock to freeze operation from the next clock cycle. CKE |

|           |                          | should be enabled at least on cycle prior new command. Disable input  |

|           |                          | buffers for power down in standby                                     |

| /CS       | Chip Select              | Disables or Enables device operation by masking or enabling all input |

|           |                          | except CK, CKE and DQ                                                 |

| A0~A12    | Address                  | Row / Column address are multiplexed on the same pins.                |

|           |                          | Row address : A0~A12                                                  |

|           |                          | Column address : A0~A9                                                |

| BS0~BS1   | Banks Select             | Selects bank to be activated during row address latch time.           |

|           |                          | Selects bank for read / write during column address latch time.       |

| DQ0~DQ15  | Data                     | Data inputs / outputs are multiplexed on the same pins.               |

| /RAS      | Row Address Strobe       | Latches row addresses on the positive edge of the CLK with /RAS low   |

| /CAS      | Column Address Strobe    | Latches Column addresses on the positive edge of the CLK with /CAS    |

|           |                          | low                                                                   |

| /WE       | Write Enable             | Enables write operation and row recharge.                             |

| VDD/VSS   | Power Supply/Ground      | Power and Ground for the input buffers and the core logic.            |

| VDDQ/VSSQ | Data Output Power/Ground | Power supply for output buffers.                                      |

| VREF      | Reference Voltage        | Reference voltage for inputs for SSTL interface.                      |

| NC        | No Connection            | This pin is recommended to be left No Connection on the device.       |

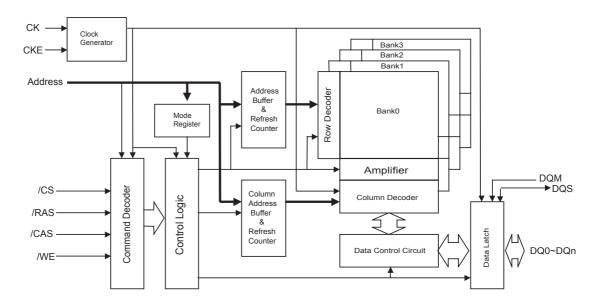

## **Block Diagram**

### **Absolute Maximum Ratings**

| Parameter                             | Symbol    | Value              | Unit                   |

|---------------------------------------|-----------|--------------------|------------------------|

| Voltage on any pin relative to Vss    | VIN, Vout | -0.3 ~ VDDQ+0.3    | V                      |

| Voltage on VDD supply relative to Vss | VDD, VDDQ | -0.3 ~ 3.6         | V                      |

| Storage temperature                   | Тѕтс      | -55 ~ <b>+</b> 150 | $^{\circ}\!\mathbb{C}$ |

| Power dissipation                     | Po        | 1                  | W                      |

| Short circuit current                 | Іоит      | 50                 | mA                     |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATING are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

### **DC Operating Condition**

Voltage referenced to Vss = 0V, TA = 0 to 70  $^{\circ}$ C

| Parameter                           | Symbol          | Min        | Max        | Unit | Note |

|-------------------------------------|-----------------|------------|------------|------|------|

| Supply voltage                      | V <sub>DD</sub> | 2.3        | 2.7        | V    |      |

| Supply voltage                      | VDDQ            | 2.3        | VDD        |      | 1    |

| Input logic high voltage            | ViH             | VREF+0.15  | VDDQ+0.3   | V    |      |

| Input logic low voltage             | VIL             | -0.3       | VREF-0.15  | V    | 2    |

| Differential Clock DC Input voltage | Vick            | -0.3       | VDDQ+0.3   | V    |      |

| Input Differential CLK&/CLK voltage | VID             | 0.7        | VDDQ+0.6   | V    |      |

| Input leakage current               | lıL             | -5         | 5          | uA   | 3    |

| Output leakage current              | lol             | -5         | 5          | uA   | 4    |

| Reference Voltage                   | VREF            | 0.49* VDDQ | 0.51* VDDQ | V    |      |

| Termination Voltage                 | VTT             | VREF-0.04  | VREF+0.04  | V    | 5    |

Note: 1. VDDQ must not exceed the level of VDDQ.

3.Any input  $0V \le V_{IN} \le 3.6V$ , all other pins are not under test = 0V.

4.Dout is disabled, 0V  $\,\leq\,\,$  Vout  $\,\leq\,\,$  2.7V.

5. VREF is expected to be equal to  $0.5^*$  VDDQ of the transmitting device, and to track variations in the DC level of the same. Peak to peak noise on VREF may not exceed  $\pm 2\%$  of the DC value.

### **AC Test Condition**

Voltage referenced to Vss = 0V, Ta = 0 to 70  $\,^{\circ}\!\mathbb{C}$

| Parameter                                     | Symbol | Value     | Unit | Note |

|-----------------------------------------------|--------|-----------|------|------|

| AC input high level voltage                   | VIH    | VREF+0.31 | V    |      |

| AC input low level voltage                    | VIL    | VREF-0.31 | V    |      |

| Input Reference Voltage                       | VREF   | 0.5xVddq  | V    |      |

| Termination Voltage                           | VTT    | 0.5xVDDQ  | V    |      |

| Input Signal Peak to Peak Swing               | Vswing | 1.0       | V    |      |

| Input Difference Voltage. CLK and /CLK Inputs | VID    | 1.5       | V    |      |

## Capacitance

TA=25°C, f-=1Mhz

| Parameter                       | Pin                          | Symbol | Min | Max | Unit |

|---------------------------------|------------------------------|--------|-----|-----|------|

| Input capacitance               | CK, /CK                      | CI1    | 2   | 3.0 | pF   |

|                                 | A0~A12,BS0,BS1,CKE,/CS,/RAS, | CI2    | 2   | 3.0 | pF   |

|                                 | /CAS,/WE,DQM                 |        |     |     |      |

| Data input / output capacitance | DQM                          | CI/O   | 4   | 5   | pF   |

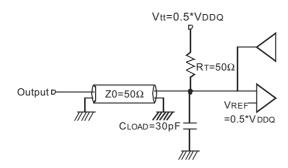

## **Output load circuit**

Output Load Circuit (SSTL\_2)

### **DC Characteristics II**

| Parameter             | Symbol   | Test condition                  | Speed       | Unit  | Note  |  |

|-----------------------|----------|---------------------------------|-------------|-------|-------|--|

| raiailletei           | Syllibol | rest condition                  | -75BA/ -75B | Offic | 14010 |  |

| Operating Current     | IDD1     | Burst length=2, One bank active | 110         | mA    | 1     |  |

| operating current     | 1001     | Trc=tRC(min),IouT=0mA           |             | 117.  | •     |  |

| Precharge standby     |          |                                 |             |       |       |  |

| current in power      | IDD2P    | CKE≦Vı∟(max), tCK=min           | 20          | mA    |       |  |

| down mode             |          |                                 |             |       |       |  |

|                       |          |                                 |             |       |       |  |

| Precharge standby     |          | CKE≧Vıн(min), /CS≧Vıн(min),     |             |       |       |  |

| current in Non power  | IDD2N    | tCK= tCK min input signals are  | mA          |       |       |  |

| down mode             |          | changed one time during 2clks.  |             |       |       |  |

| Active standby        |          |                                 |             |       |       |  |

| current in power      | IDD3P    | CKE≦Vı∟(max), tCK= tCK min      | 20          | mA    |       |  |

| down mode             |          | , ,                             |             |       |       |  |

|                       |          | OVE > Marketin) (OO > Marketin) |             |       |       |  |

| Active standby        | IDDON    | CKE ≥ VIH(min), /CS ≥ VIH(min), | 0.5         |       |       |  |

|                       | IDD3N    | tCK=min input signals are       | 65          | mA    |       |  |

| down mode             |          | changed one time during 2clks.  |             |       |       |  |

| Burst mode operating  |          | tcκ≧tcκ(min),louτ=0 mA          | 455         | A     |       |  |

| current               | IDD4R    | All banks active                | 155         | mA    | 1     |  |

| Auto refresh current  | IDD5     | tRRC≧tRRC(min), All banks       | 190         | mA    | 2     |  |

| Auto refresii current | טטטו     | active                          | 190         | IIIA  | ۷     |  |

| Self refresh current  | IDD6     | CKE≦0.2V                        | 3           | mA    |       |  |

**Note:** 1. IDD1 and IDD4 depend on output loading and cycle rates. Specified values are measured with the output open.

2. Min. of tRRC is shown at AC characteristics.

### **AC Characteristics**

| Parameter                              |                        | 0      | -75   | БВА  | -7:   | l lmit |     |

|----------------------------------------|------------------------|--------|-------|------|-------|--------|-----|

| '                                      | Symbol                 | Min    | Max   | Min  | Max   | Unit   |     |

| System clock                           | /CAS Latency = 2.5     | tCK2.5 | 7.5   | 12   | 7.5   | 12     |     |

| Cycle time                             | /CAS Latency = 2       | tCK2   | 7.5   | 12   | 10    | 12     | ns  |

| Clock high puls                        | e width                | tCHW   | 0.45  | 0.55 | 0.45  | 0.55   | CLK |

| Clock low pulse                        | e width                | tCLW   | 0.45  | 0.55 | 0.45  | 0.55   | CLK |

| Access time for                        | rm CK to /CK           | tAC    | -0.75 | 0.75 | -0.75 | 0.75   | ns  |

| Data strobe ed                         | ge to clock edge       | tDQSCK | -0.75 | 0.75 | -0.75 | 0.75   | ns  |

| Clock to first ris                     | sing edge of DQS delay | tDQSS  | 0.75  | 1.25 | 0.75  | 1.25   | CLK |

| /RAS cycle time                        | е                      | tRC    | 65    | -    | 65    | -      | ns  |

| /RAS to /CAS o                         | delay                  | tRCD   | 20    | -    | 20    | -      | ns  |

| /RAS active tim                        | ne                     | tRAS   | 45    | 120K | 45    | 120K   | ns  |

| /RAS precharge                         | e time                 | tRP    | 20    | -    | 20    | -      | ns  |

| /RAS to /RAS t                         | oank active delay      | tRRD   | 15    | -    | 15    | -      | ns  |

| /CAS to /CAS o                         | delay                  | tCCD   | 1     | -    | 1     | -      | CLK |

| Data-in setup ti                       | me (to DQS)            | tDS    | 0.5   | -    | 0.5   | -      | ns  |

| Data-in hold tim                       | ne (to DQS)            | tDH    | 0.5   | -    | 0.5   | -      | ns  |

| DQS Falling Ed                         | lge to CLK Setup Time  | tDSS   | 0.2   | -    | 0.2   | -      | CLK |

| DQS Falling Ed                         | ge Hold Time from CLK  | tDSH   | 0.2   | -    | 0.2   | -      | CLK |

| Input setup time                       | е                      | tIS    | 0.9   | -    | 0.9   | -      | ns  |

| Input hold time                        |                        | tIH    | 0.9   | -    | 0.9   | -      | ns  |

| DQS-in high lev                        | vel width              | tDSH   | 0.35  | -    | 0.35  | -      | CLK |

| DQS-in low leve                        | el width               | tDSL   | 0.35  | -    | 0.35  | -      | CLK |

| Clock to DQS write preamble setup time |                        | tWPRES | 0     | -    | 0     | -      | ns  |

| Write preamble                         |                        | tWPST  | 0.4   | 06   | 0.4   | 06     | CLK |

| Data strobe ed                         | tDQSQ                  |        | 0.5   |      | 0.5   | ns     |     |

| Mode register s                        | set cycle time         | tMRD   | 15    |      | 15    |        |     |

| DQS read prea                          | mble                   | tRPRE  | 0.9   | 1.1  | 0.9   | 1.1    | CLK |

### **Command Truth-Table**

| SYM.  | Command                   |          |   | CKEn-1 | CKEn | /CS      | /RAS | /CAS | /WE | DM | ADDR   | A10/AP | BS       |

|-------|---------------------------|----------|---|--------|------|----------|------|------|-----|----|--------|--------|----------|

| MRS   | Mode Register Set         |          |   | Н      | Х    | L        | L    | L    | L   | Х  | CA     | CA     | L        |

| NOP   | No Operation              |          |   | Н      | Х    | L        | Н    | Н    | Н   | Х  |        | Х      |          |

| ACT   | Bank Active               |          |   | Н      | Х    | L        | L    | Н    | Н   | Х  |        | V      | V        |

| READ  | Read                      |          |   | H      | Х    | L        | н    | L    | I   | Х  | V      | L      | <b>V</b> |

| READA | Read with Auto P          | recharge |   |        | ^    | <u> </u> | П    | L    | Е   | ^  | V      | Н      | V        |

| WRIT  | Write                     |          |   | Н      | Х    | L        | Н    | L    | ٦   | Х  | \<br>\ | L      | <        |

| WRITA | Write with Auto Precharge |          |   | 11     | ^    | _        | "    | L    | ı   | ^  | V      | Н      | V        |

| PREA  | Precharge All Bank        |          |   | Н      | Х    | L        | L    | Н    | L   | Х  | х      | н      | Х        |

| BST   | Burst Stop                |          |   | Н      | Х    | L        | Н    | Н    | L   | Х  | х х    |        |          |

| AREF  | Auto Refresh              |          |   | Н      | Н    | L        | L    | L    | Н   | Х  | х х    |        |          |

| SELF  |                           | Entry    | Н | L      | L    | L        | L    | Н    | Х   |    |        |        |          |

| SELEX | Self Refresh              | Exit     | L | Н      | Н    | Х        | Х    | Х    | Х   |    |        | Χ      |          |

|       |                           | EXIL     | L |        | L    | Н        | Н    | Н    | ^   |    |        |        |          |

| PD    |                           | Cata     | Н | L      | Н    | Х        | Х    | Χ    | Х   |    |        |        |          |

|       | Precharge                 | Entry    | П | _      | L    | Н        | Н    | Н    | ^   |    | ×      |        |          |

|       | Power down                |          |   |        | Н    | Х        | Х    | Х    |     |    |        |        |          |

| PDEX  |                           | Exit     | L | Н      | L    | Н        | Н    | Х    | Х   |    |        |        |          |

| WDE   | Data write                | Enable   | Н | Х      | х    | х        | х    | Х    | L   | X  |        |        |          |

| WDD   | Data Wille                | Disable  | Н | Х      | Х    | Х        | Х    | Х    | Ι   |    | ^      |        |          |

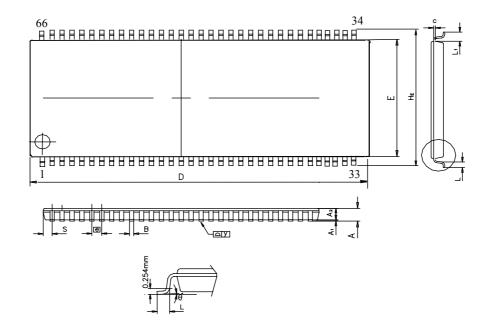

# **Package Information**

| SYMBOL         | MILLIMETER |           |       | INCH      |        |        |  |  |

|----------------|------------|-----------|-------|-----------|--------|--------|--|--|

| STWIDOL        | MIN.       | NOM.      | MAX.  | MIN.      | NOM.   | MAX.   |  |  |

| Α              |            |           | 1.20  |           |        | 0.047  |  |  |

| A1             | 0.05       |           | 0.15  | 0.002     |        | 0.006  |  |  |

| A2             | 0.95       | 1.00      | 1.05  | 0.037     | 0.039  | 0.041  |  |  |

| В              | 0.17       | 0.24      | 0.32  | 0.007     | 0.009  | 0.013  |  |  |

| С              | 0.09       | 0.145     | 0.2   | 0.004     | 0.0006 | 0.008  |  |  |

| D              |            | 22.62 BSC |       | 0.891 BSC |        |        |  |  |

| H <sub>E</sub> | 11.74      | 11.76     | 11.78 | 0.462     | 0.463  | 0.464  |  |  |

| Е              | 10.15      | 10.16     | 10.17 | 0.3996    | 0.400  | 0.4004 |  |  |

| е              | 0.65 BSC   |           |       | 0.026     |        |        |  |  |

| L              | 0.40       | 0.50      | 0.60  | 0.016     | 0.020  | 0.024  |  |  |

| L1             | 0.80 REF   |           |       | 0.031 REF |        |        |  |  |

| S              | 0.71 REF   |           |       | 0.028 REF |        |        |  |  |

| θ              | 0 °        | -         | 8 °   | 0 °       | -      | 8°     |  |  |

400mil 66pin TSOP II Package