Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1

LTC1771

s

Very Low Standby Current: 10

µ

A

s

Available in Space-Saving 8-Lead MSOP Package

s

High Output Currents

s

Wide V

IN

Range: 2.8V to 20V Operation

s

V

OUT

Range: 1.23V to 18V

s

High Efficiency: Over 93% Possible

s

±

2% Output Accuracy

s

Very Low Dropout Operation: 100% Duty Cycle

s

Current Mode Operation for Excellent Line and

Load Transient Response

s

Defeatable Burst Mode

TM

Operation

s

Short-Circuit Protected

s

Optional Programmable Soft-Start

s

Micropower Shutdown: I

Q

= 2

µ

A

The LTC

®

1771 is a high efficiency current mode step-

down DC/DC controller that draws as little as 10

µ

A DC

supply current to regulate the output at no load while

maintaining high efficiency for loads up to several amps.

The LTC1771 drives an external P-channel power MOSFET

using a current mode, constant off-time architecture. An

external sense resistor is used to program the operating

current level. Current mode control provides short-circuit

protection, excellent transient response and controlled

start-up behavior. Burst Mode operation enables the

LTC1771 to maintain high efficiency down to extremely

low currents. Shutdown mode further reduces the supply

current to a mere 2

µ

A. For low noise applications, Burst

Mode operation can be easily disabled with the MODE pin.

Wide input supply range of 2.8V to 18V (20V maximum)

and 100% duty cycle operation for low dropout make the

LTC1771 ideal for a wide variety of battery-powered appli-

cations where maximizing battery life is important.

The LTC1771's availability in both 8-lead MSOP and SO

packages provides for a minimum area solution.

s

Cellular Telephones and Wireless Modems

s

1- to 4-Cell Lithium-Ion-Powered Applications

s

Portable Instruments

s

Battery-Powered Equipment

s

Battery Chargers

s

Scanners

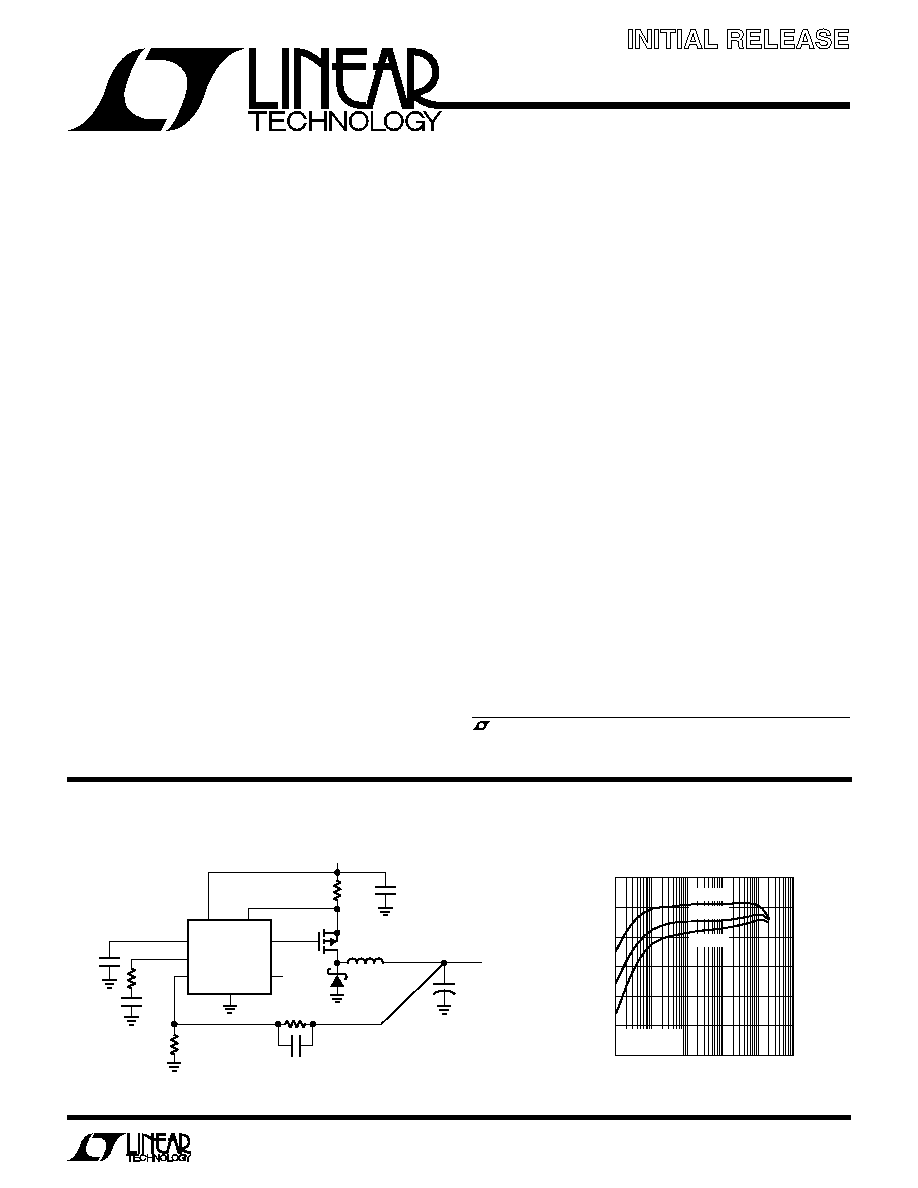

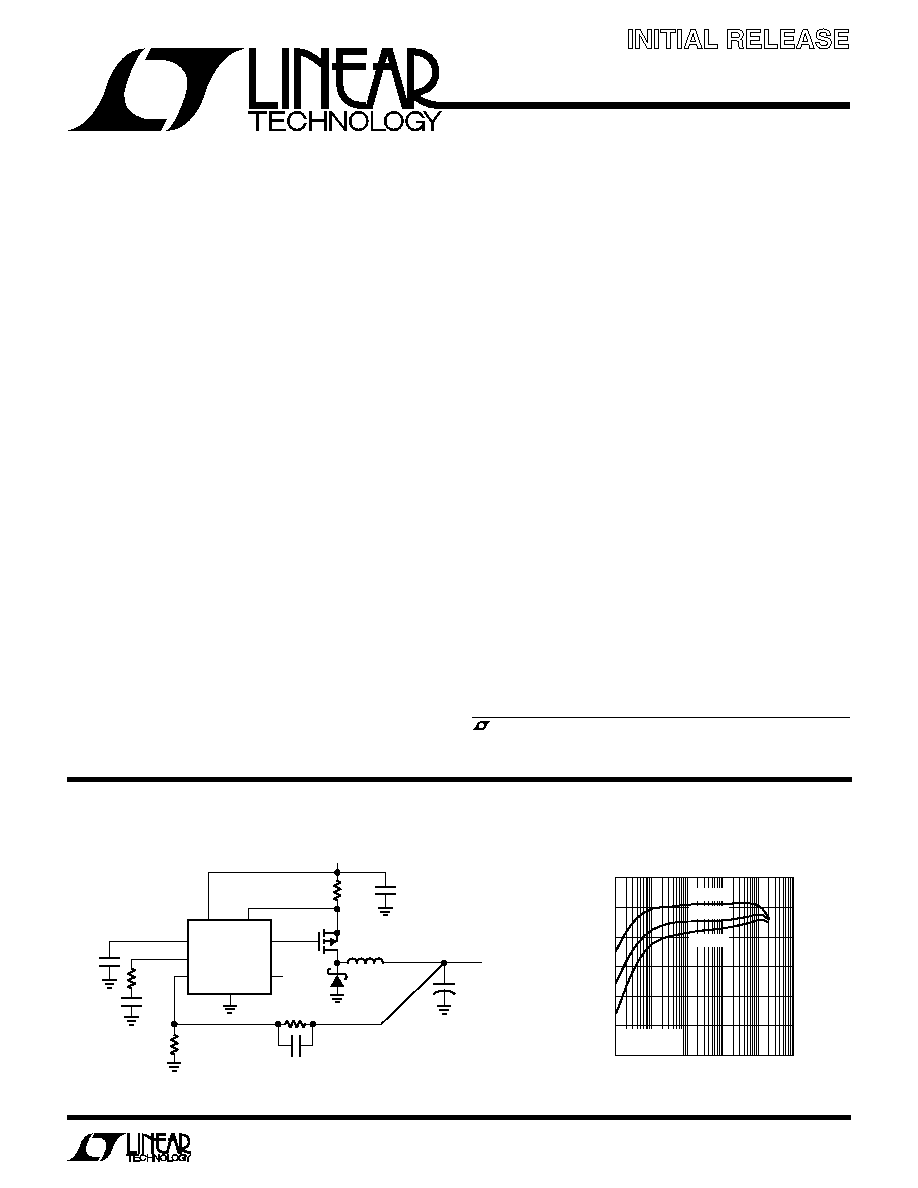

Figure 1. High Efficiency Step-Down Converter

Low Quiescent Current

High Efficiency Step-Down

DC/DC Controller

February 2000

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode is a trademark of Linear Technology Corporation.

RUN/SS

I

TH

V

FB

V

IN

V

IN

V

IN

4.5V TO 18V

R

C

10k

R

SENSE

0.05

R2

1.64M

1%

R1

1M

1%

M1

Si6447DQ

UPS5817

L1

15

µ

H

C

C

22OpF

5pF

10

µ

F

25V

CER

C

OUT

150

µ

F

6.3V

V

OUT

3.3V

2A

1771 F01

C

SS

0.01

µ

F

PGATE

MODE

LTC1771

GND

SENSE

+

LTC1771 Efficiency

LOAD CURRENT (mA)

EFFICIENCY (%)

100

90

80

70

60

50

40

0.1

1

100

1000

10000

1771 F01b

10

V

IN

= 5V

V

IN

= 10V

V

IN

= 15V

V

OUT

= 3.3V

R

SENSE

= 0.05

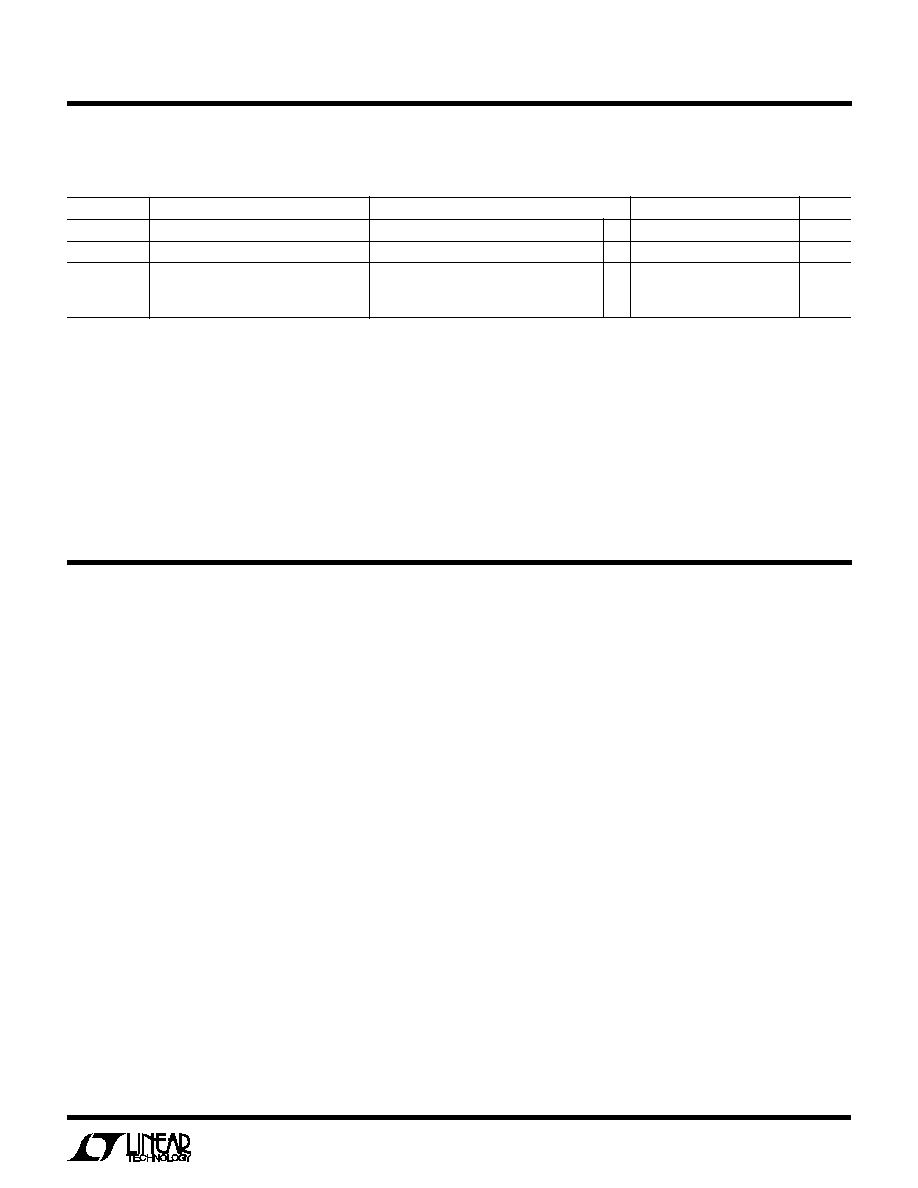

Final Electrical Specifications

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-

tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

FEATURES

DESCRIPTIO

U

APPLICATIO S

U

TYPICAL APPLICATIO

U

2

LTC1771

The

q

denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25

°

C.

V

IN

= 10V, V

RUN

= open unless otherwise specified.

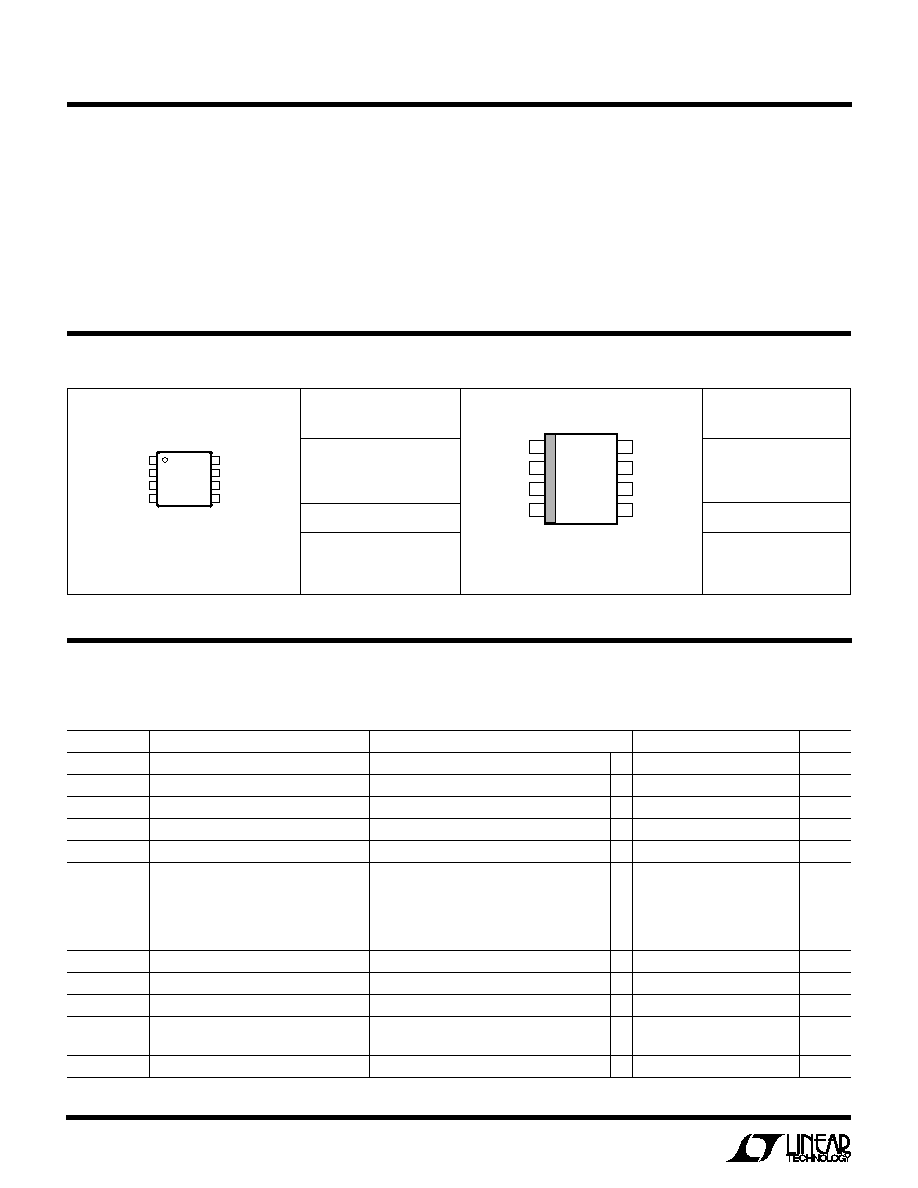

LTC1771EMS8

T

JMAX

= 125

°

C,

JA

= 150

°

C/ W

ORDER PART

NUMBER

Input Supply Voltage (V

IN

)........................ 0.3V to 20V

Peak Driver Output Current < 10

µ

s (PGATE) ............. 1A

RUN/SS Voltage ........................... 0.3V to (V

IN

+ 0.3V)

MODE Voltage .......................................... 0.3V to 20V

I

TH

, V

FB

Voltage .......................................... 0.3V to 5V

SENSE Voltage (V

IN

> 12V)... (V

IN

12V) to (V

IN

+ 0.3V)

SENSE Voltage (V

IN

12V) .......... 0.3V to (V

IN

+ 0.3V)

(Note 1)

Consult factory for Military grade parts.

Junction Temperature (Note 2) ............................ 125

°

C

Operating Temperature Range (Note 3)

LTC1771E ......................................... 40

°

C to 85

°

C

LTC1771I ......................................... 40

°

C to 85

°

C

Storage Temperature Range ................. 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec).................. 300

°

C

LTC1771ES8

LTC1771IS8

ORDER PART

NUMBER

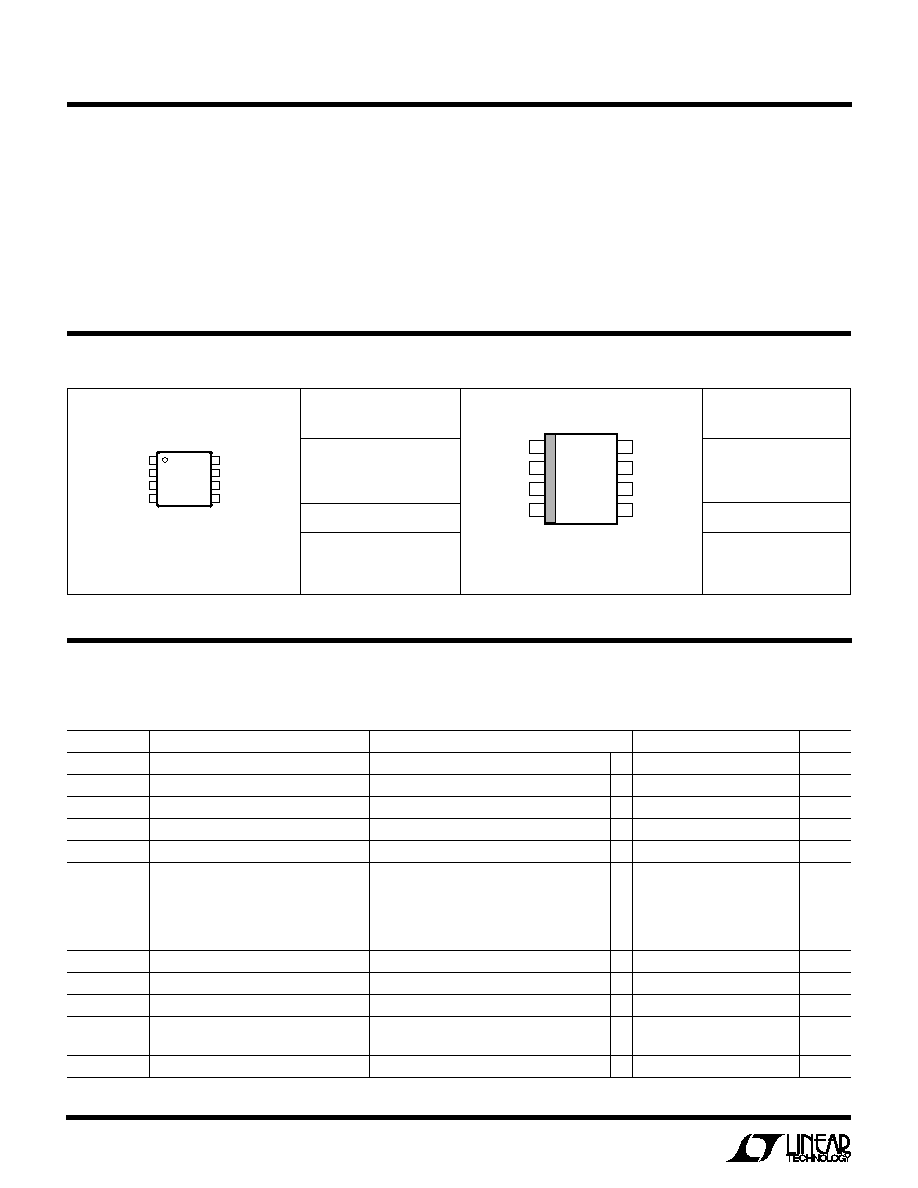

RUN/SS

I

TH

V

FB

GND

1

2

3

4

8

7

6

5

MODE

SENSE

V

IN

PGATE

TOP VIEW

MS8 PACKAGE

8-LEAD PLASTIC MSOP

MS8 PART MARKING

TOP VIEW

MODE

SENSE

V

IN

PGATE

RUN/SS

I

TH

V

FB

GND

S8 PACKAGE

8-LEAD PLASTIC SO

1

2

3

4

8

7

6

5

T

JMAX

= 125

°

C,

JA

= 110

°

C/ W

S8 PART MARKING

1771

1771I

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

FB

Feedback Voltage

(Note 5)

q

1.205

1.230

1.255

V

I

FB

Feedback Current

(Note 5)

q

1

10

nA

I

SUPPLY

No-Load Supply Current

V

IN

= 10V, I

LOAD

= 0 (Note 6)

10

µ

A

V

LINEREG

Reference Voltage Line Regulation

V

IN

= 5V to 15V (Note 5)

q

0.003

0.03

%/V

V

LOADREG

Output Voltage Load Regulation

I

TH

= 0.5V to 2V, Burst Disabled (Note 5)

q

0.25

1

%

I

Q

Input DC Supply Current

(Note 4)

Active Mode (PGATE = 0V)

V

IN

= 2.8V to 18V

150

235

µ

A

Sleep Mode (Note 6)

V

IN

= 2.8V to 18V, V

FB

= 1.5V

9

15

µ

A

Shutdown

V

IN

= 2.8V to 18V, V

RUN

= 0V

2

6

µ

A

Short Circuit

V

IN

= 2.8V to 18V, V

FB

= 0V

175

275

µ

A

V

SENSE(MAX)

Maximum Current Sense Threshold

V

FB

= V

REF

20mV

q

110

140

180

mV

V

SENSE(MIN)

Minimum Current Sense Threshold

V

FB

= V

REF

+ 10mV, Burst Disabled

25

mV

V

SENSE(SLEEP)

Sleep Current Sense Threshold

I

TH

= 1V

50

mV

t

OFF

Switch Off Time

V

FB

at Regulated Value

3.5

µ

s

V

FB

= 0V

70

µ

s

V

MODE

Mode Pin Threshold

V

MODE

Rising

q

0.5

1.3

2

V

LTKD

ABSOLUTE AXI U RATI GS

W

W

W

U

PACKAGE/ORDER I FOR ATIO

U

U

W

ELECTRICAL CHARACTERISTICS

3

LTC1771

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: T

J

is calculated from the ambient temperature T

A

and power

dissipation P

D

according to the following formulas:

LTC1771S8: T

J

= T

A

+ (P

D

)(110

°

C/W)

LTC1771MS8: T

J

= T

A

+ (P

D

)(150

°

C/W)

Note 3: The LTC1771E is guaranteed to meet performance specifications

from 0

°

C to 70

°

C. Specifications over the 40

°

C to 85

°

C operating

temperature range are assured by design, characterization and correlation

with statistical process controls. The LTC1771I is guaranteed and tested

over the 40

°

C to 85

°

C operating temperature range.

The

q

denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25

°

C.

V

IN

= 10V, V

RUN

= open unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

RUN/SS

RUN/SS Pin Threshold

V

RUN/SS

Rising

q

0.5

1.0

2

V

I

RUN

Source Current

V

RUN

= 0V, V

IN

= 2.8V to 18V

0.3

1

3

µ

A

PGATE t

r

, t

f

PGATE Transition Time (Note 7)

Rise Time

C

LOAD

= 2000pF

80

ns

Fall Time

C

LOAD

= 2000pF

90

ns

Note 4: Dynamic supply current is higher due to the gate charge being

delivered at the switching frequency. See Applications Information.

Note 5: The LTC1771 is tested in a feedback loop that servos V

FB

to the

balance point for the error amplifier (V

ITH

= 1.23V).

Note 6: No-load supply current consists of sleep mode current (9

µ

A

typical) plus a small switching component necessary to overcome

Schottky diode leakage and feedback resistor current.

Note 7: t

r

and t

f

measured at 10% to 90% levels.

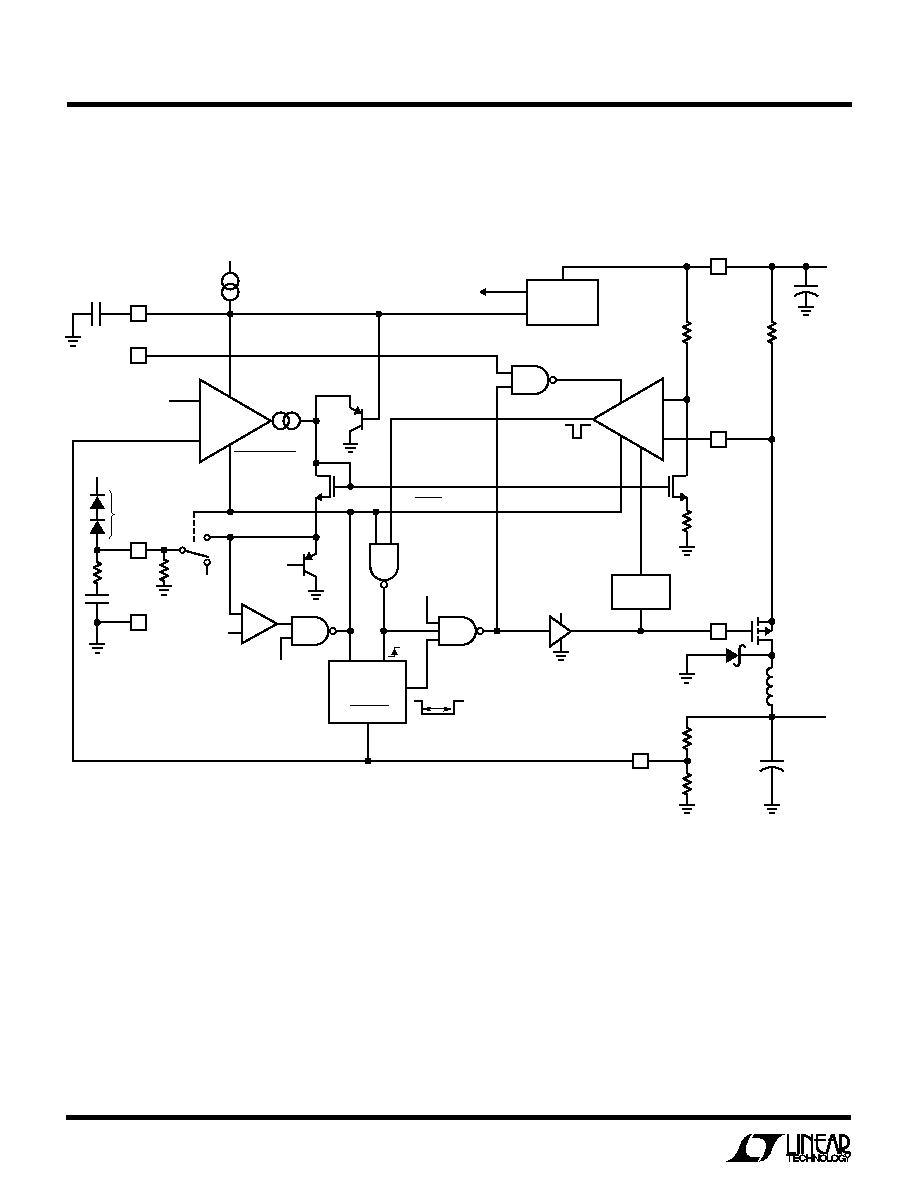

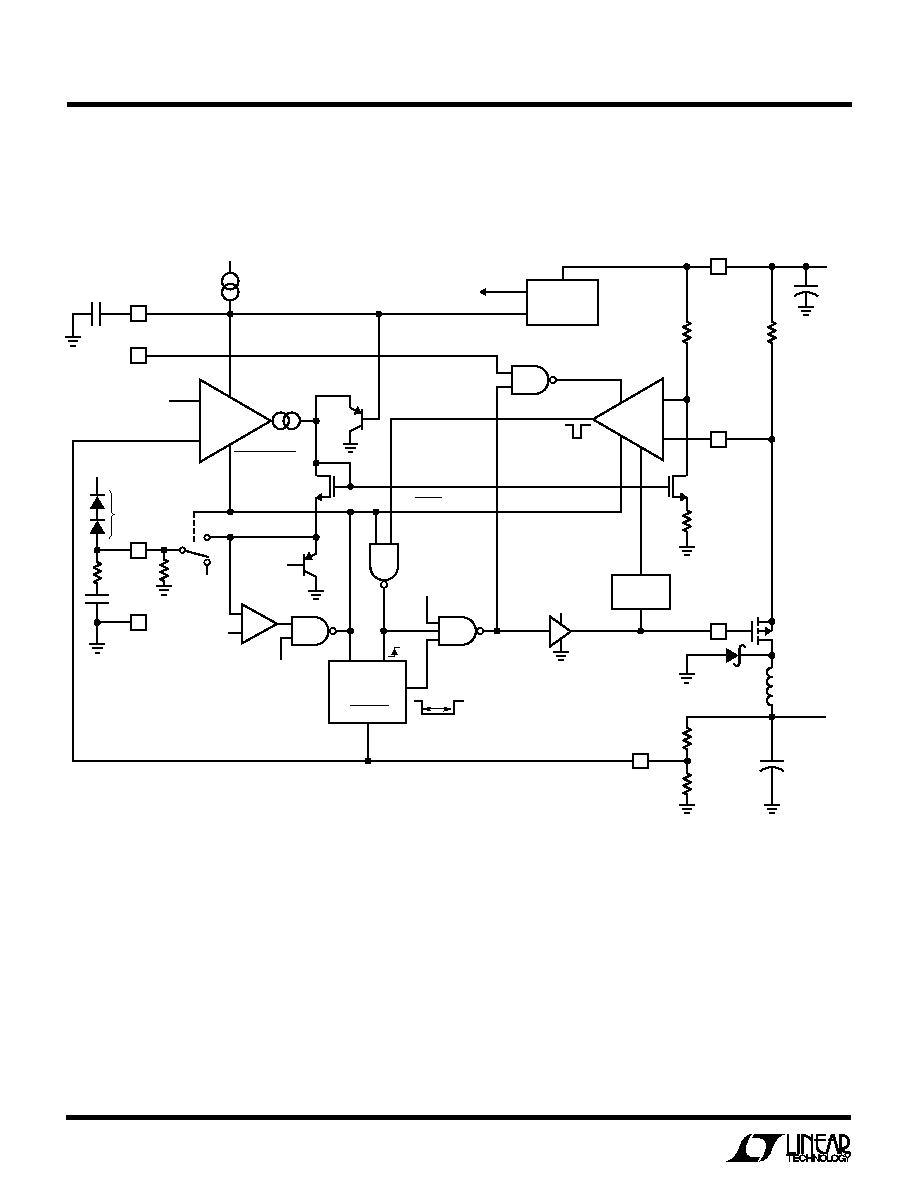

RUN/SS (Pin 1): The voltage level on this pin controls

shutdown/run mode (ground = shutdown, open/high =

run). Connecting an external capacitor to this pin provides

soft-start.

I

TH

(Pin 2): Error Amplifier Compensation Point. The

current comparator threshold increases with this control

voltage. Nominal voltage range for this pin is 0V to 3V.

V

FB

(Pin 3): Feedback of Output Voltage for Comparison

to Internal 1.23V Reference. An external resistive divider

across the output is returned to this pin.

GND (Pin 4): Ground Pin.

PGATE (Pin 5): High Current Gate Driver for External

P-Channel MOSFET Switch. Voltage swing is from ground

to V

IN

.

V

IN

(Pin 6): Main Input Voltage Supply Pin.

SENSE (Pin 7): Current Sense Input for Monitoring Switch

Current. Maximum switch current and Burst Mode

threshold is programmed with an external resistor be-

tween SENSE and V

IN

.

MODE (Pin 8): Burst Mode Enable/Disable Pin. Connect-

ing this pin to V

IN

(or above 2V) enables Burst Mode

operation, while connecting this pin to ground disables

Burst Mode operation. Do not leave floating.

ELECTRICAL CHARACTERISTICS

U

U

U

PI FU CTIO S

4

LTC1771

+

EA

+

C

ON

ON

+

C

SS

RUN/SS

V

IN

V

OUT

V

IN

1

MODE

MODE

READY

SLEEP

READY

250k

22k

R

SENSE

1.23V

1V

1V

2V

1

µ

A

(BURST ENABLE)

10% CURRENT

10% CURRENT

SOFT-START

8

V

IN

V

IN

V

OUT

L

C

IN

+

C

OUT

6

SENSE

7

SW

3.5

µ

s

1771 BD

5

V

FB

3

I

TH

R

C

C

C

*

*

OPTIONAL FOR FOLDBACK

CURRENT LIMITING

2

GND

4

+

B

ON TRIGGER

1.23V

REFERENCE

BLANKING

1-SHOT

STRETCH

FU

N

CTIO

N

AL BLOCK DIAGRA

U

U

W

5

LTC1771

(Refer to Functional Block Diagram)

Main Control Loop

The LTC1771 uses a constant off-time, current mode

step-down architecture. During normal operation, the

P-channel MOSFET is turned on at the beginning of each

cycle and turned off when the current comparator C

triggers the 1-shot timer. The external MOSFET switch

stays off for the 3.5

µ

s 1-shot duration and then turns back

on again to begin a new cycle. The peak inductor current

at which C triggers the 1-shot is controlled by the voltage

on Pin 3 (I

TH

), the output of the error amplifier EA. An

external resistive divider connected between V

OUT

and

ground allows EA to receive an output feedback voltage

V

FB

. When the load current increases, it causes a slight

decrease in V

FB

relative to the 1.23V reference, which in

turn causes the I

TH

voltage to increase until the average

inductor current matches the new load current.

The main control loop is shut down by pulling Pin 1

(RUN/SS) low. Releasing RUN/SS allows an internal 1

µ

A

current source to charge soft-start capacitor C

SS

. When

C

SS

reaches 1V, the main control loop is enabled with the

I

TH

voltage clamped at approximately 40% of its maxi-

mum value. As C

SS

continues to charge, I

TH

is gradually

released allowing normal operation to resume.

Burst Mode Operation

The LTC1771 provides outstanding low current efficiency

and ultralow no-load supply current by using Burst Mode

operation when the MODE pin is pulled above 2V. During

Burst Mode operation, short burst cycles of normal switch-

ing are followed by a longer idle period with the switch off

and the load current is supplied by the output capacitor.

During this idle period, only the minimum required cir-

cuitry--1.23V reference and error amp--are left on, and

the supply current is reduced to 9

µ

A. At no load, the output

capacitor is still discharged very slowly by leakage current

in the Schottky diode and feedback resistor current result-

ing in very low frequency burst cycles that add a few more

microamps to the supply current.

Burst Mode operation is provided by clamping the mini-

mum I

TH

voltage at 1V which represents about 25% of

maximum load current. If the load falls below this level, i.e.

the I

TH

voltage tries to fall below 1V, the burst comparator

B switches state signaling the LTC1771 to enter sleep

mode. During this time, EA is reduced to 10% of its normal

operating current and the external compensation capaci-

tor is disconnected and clamped to 1V so that the EA can

drive its output with the lower available current. As the load

discharges the output capacitor, the internal I

TH

voltage

increases. When it exceeds 1V the burst comparator exits

sleep mode, reconnects the external compensation com-

ponents to the error amplifier output, and returns EA to full

power along with the other necessary circuitry. This

scheme (patent pending) allows the EA to be reduced to

such a low operating current during sleep mode without

adding unacceptable delay to wake up the LTC1771 due to

the compensation capacitor on I

TH

required for stability in

normal operation.

Burst Mode operation can be disabled by pulling the

MODE pin to ground. In this mode of operation, the burst

comparator B is disabled and the I

TH

voltage allowed to go

all the way to 0V. The load can now be reduced to about 1%

of maximum load before the loop skips cycles to maintain

regulation. This mode provides a low noise output spec-

trum, useful for reducing both audio and RF interference,

at the expense of reduced efficiency at light loads.

Off-Time

The off-time duration is 3.5

µ

s when the feedback voltage

is close to the reference voltage; however, as the feedback

voltage drops, the off-time lengthens and reaches a maxi-

mum value of about 70

µ

s when V

FB

is zero. This ensures

that the inductor current has enough time to decay when

the reverse voltage across the inductor is low such as

during short circuit, thus protecting the MOSFET and

inductor.

OPERATIO

U