DS07-16306-3E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-bit Proprietary Microcontrollers

CMOS

FR30 Family MB91150 Series

MB91F155A/MB91155/MB91154

s

s

s

s

DESCRIPTION

The MB91F155A/MB91155/MB91154 is a single-chip microcontroller using a RISC-CPU (FR 30 series) as its

core. It contains peripheral I/O resources suitable for audio, MD and so on which are required to operate at low

power consumption.

s

s

s

s

FEATURES

1.

CPU

· 32-bit RISC (FR30) , load/store architecture, 5-stage pipeline

· General-purpose registers : 32 bits

×

16

· 16-bit fixed-length instructions (basic instructions) , 1 instruction/ 1 cycle

· Memory-to-memory transfer, bit processing, barrel shift processing : Optimized for embedded applications

· Function entrance/exit instructions, and multiple load/store instructions of register contents, instruction systems

supporting high level languages

· Register interlock functions, efficient assembly language description

· Branch instructions with delay slots : Reduced overhead time in branching executions

· Internal multiplier/supported at instruction level

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

· Interrupt (PC and PS saving) : 6 cycles, 16 priority levels

(Continued)

s

s

s

s

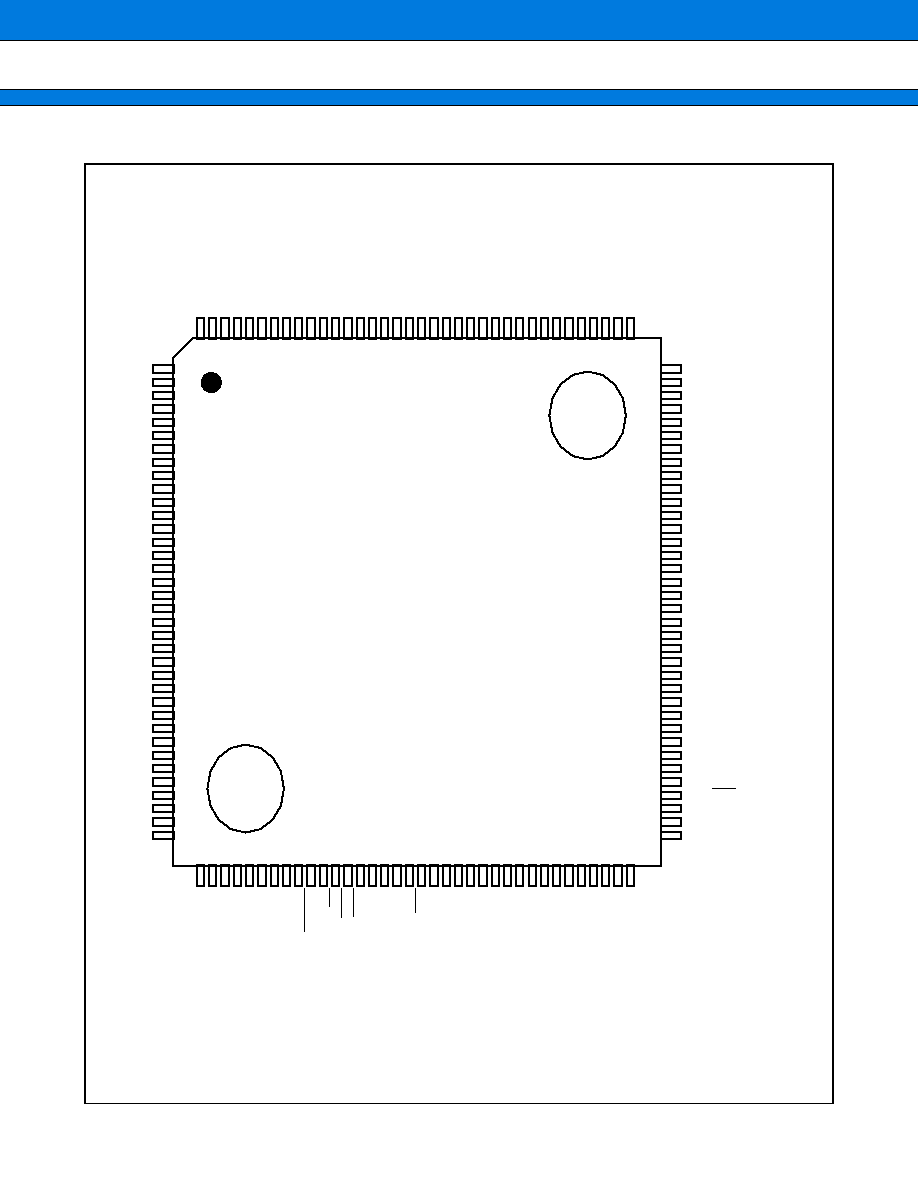

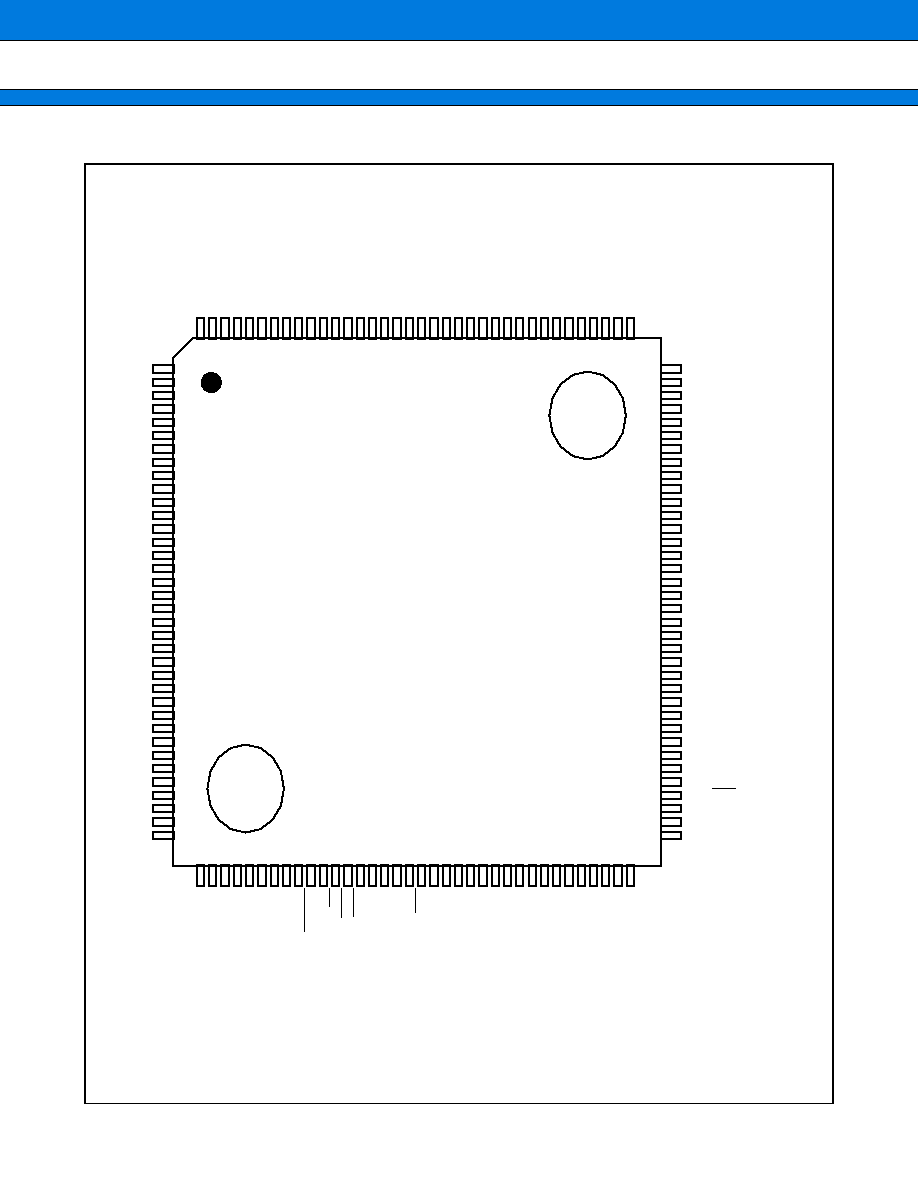

PACKAGE

144-pin plastic LQFP

144-pin plastic LQFP

(FPT-144P-M08)

(FPT-144P-M01)

MB91F155A/MB91155/MB91154

2

2.

Bus Interface

· 16-bit address output, 8/16-bit data input and output

· Basic bus cycle : 2-clock cycle

· Support for interface for various types of memory

· Unused data/address pins can be configured us input/output ports

· Support for little endian mode

3.

Internal ROM

MB91F155A

FLASH products : 510 Kbytes

MB91155

Mask product : 510 Kbytes

MB91154

Mask product : 384 Kbytes

4.

Internal RAM

Mask, FLASH products : 2 Kbytes

5.

Internal Data RAM

MB91F155, MB91155

FLASH, Mask products : 32 Kbytes

MB91154

FLASH, Mask product : 20 Kbytes

6.

DMAC

DMAC in descriptor format for placing transfer parameters on to the main memory.

Capable of transferring a maximum of eight internal and external factors combined.

Three channels for external factors

7.

Bit Search Module

Searches in one cycle for the position of the bit that changes from the MSB in one word to the initial I/O.

8.

Timers

· 16-bit OCU

×

8 channels, ICU

×

4 channels, Free-run timer

×

1 channel

· 8/16-bit up/down timer/counter (8-bit

×

2 channels or 16-bit

×

1 channel)

· 16-bit PPG timer

×

6 channels. The output pulse cycle and duty can be varied as desired

· 16-bit reload timer

×

4 channels

9.

D/A Converter

· 8-bit

×

3 channels

10. A/D Converter (Sequential Comparison Type)

· 10-bit

×

8 channels

· Sequential conversion method (conversion time : 5.0

µ

s@33 MHz)

· Single conversion or scan conversion can be selected, and one-shot or continuous or stop conversion mode

can be set respectively.

· Conversion starting function by hardware/software.

(Continued)

MB91F155A/MB91155/MB91154

3

(Continued)

11. Serial I/O

· UART

×

4 channels. Any of them is capable of serial transfer in sync with clock attached with the LSB/MSB

switching function.

· Serial data output and serial clock output are selectable by push-pull/open drain software.

· A 16-bit timer (U-timer) is contained as a dedicated baud rate generator allowing any baud rate to be generated.

12. I

2

C Bus Interface

· One channel master/slave send and receive

· Arbitration and clock synchronization functions

(The product is licensed with the Philips I

2

C patent to support those customers who intend to use this product

in an I

2

C system in compliance with the standard I

2

C specification stipulated by Philips.)

13. Clock Switching Function

· Gear function : Operating clock ratios to the basic clock can be set independently for the CPU and peripherals

from four types, 1 : 1, 1 : 2, 1 : 4 or 1 : 8.

14. Clock Function (Calendar Macro)

· Internal 32 kHz clock function

· It is possible to perform the clock function (oscillation frequency: 32 kHz) even in a stop mode. (The oscillation

does not suspend during a stop mode.)

15. Interrupt Controller

External interrupt input (16 channels in total) :

· Allows the rising edge/falling edge/H level/L level to be set.

Internal interrupt factors :

· Interrupt by resources and delay interrupt

16. Others

· Reset cause : Power on reset/watchdog timer/software reset/external reset

· Low power consumption mode : Sleep/stop

· Package : 144-pin LQFP

· CMOS technology (0.35

µ

m)

· Power supply voltage : 3.15 V to 3.6 V

· MB91F155 is to be MB91F155A.

MB91F155A/MB91155/MB91154

4

s

s

s

s

PIN ASSIGNMENT

(TOP VIEW)

(FPT-144P-M08)

(FPT-144P-M01 : MB91F155A only)

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

V

SS

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

P37/D31

P40/A00

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

V

SS

V

CC

P50/A08

P51/A09

P52/A10

P53/A11

P54/A12

P55/A13

P56/A14

P57/A15

P60/A16

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

P61/A17

P62/A18

P63/A19

P64/A20

P65/A21

P66/A22

P67/A23

V

SS

P80/RDY

P81/BGRNT

P82/BRQ

P83/RD

P84/WR0

P85/WR1

P86/CLK

MD2

MD1

MD0

RST

V

CC

X1

X0

V

SS

PC0/INT0

PC1/INT1

PC2/INT2

PC3/INT3

PC4/INT4/CS0

PC5/INT5/CS1

PC6/INT6/CS2

PC7/INT7/CS3

V

CC

PD0/AIN0/INT8/TRG0

PD1/BIN0/INT9/TRG1

PD2/AIN1/INT10/TRG2

PD3/BIN1/INT11/TRG3

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

PH5/SCK1/TO1

PI0/SIN2

PI1/SOT2

PI2/SCK2/TO2

PI3/SIN3

PI4/SOT3

PI5/SCK3/TO3

V

SS

PJ0/SCL

PJ1/SDA

V

SS

V

CC

PG5/PPG5

PG4/PPG4

PG3/PPG3

PG2/PPG2

PG1/PPG1

PG0/PPG0

PF4

PF3/IN3

PF2/IN2

PF1/IN1

PF0/IN0

PE7/OC7

PE6/OC6

PE5/OC5

PE4/OC4

PE3/OC3

PE2/OC2

PE1/OC1

PE0/OC0

V

CC

PD7/ATG/INT15

PD6/DEOP2/INT14

PD5/ZIN1/INT13/TRG5

PD4/ZIN0/INT12/TRG4

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

V

SS

X1A

X0A

TEST

V

CC

PK7/AN7

PK6/AN6

PK5/AN5

PK4/AN4

PK3/AN3

PK2/AN2

PK1/AN1

PK0/AN0

AV

SS

AVRL

AVRH

AV

CC

DAVC

DAVS

DA0

DA1

DA2

V

CC

PL7/DACK2

PL6/DREQ2

PL5/DEOP1

PL4/DACK1

PL3/DREQ1

PL2/DEOP0

PL1/DACK0

PL0/DREQ0

PH0/SIN0

PH1/SOT0

PH2/SCK0/TO0

PH3/SIN1

PH4/SOT1

MB91F155A/MB91155/MB91154

5

s

s

s

s

PIN DESCRIPTION

(Continued)

Pin No.

Pin name

Circuit

type

Function

1

2

3

4

5

6

7

8

D16/P20

D17/P21

D18/P22

D19/P23

D20/P24

D21/P25

D22/P26

D23/P27

C

Bit 16 to bit 23 of external data bus

These pins are enabled only in 16-bit external bus mode.

These pins are available as ports in single-chip and 8-bit external bus

modes.

10

11

12

13

14

15

16

17

D24/P30

D25/P31

D26/P32

D27/P33

D28P34

D29/P35

D30/P36

D31/P37

C

Bit 24 to bit 31 of external data bus

These pins are available as ports in single-chip mode.

18

19

20

21

22

23

24

25

28

29

30

31

32

33

34

35

A00/P40

A01/P41

A02/P42

A03/P43

A04/P44

A05/P45

A06/P46

A07/P47

A08/P50

A09/P51

A10/P52

A11/P53

A12/P54

A13/P55

A14/P56

A15/P57

F

Bit 0 to bit 15 of external address bus

These pins are enabled in external bus mode.

These pins are available as ports in single-chip mode.

36

37

38

39

40

41

42

43

A16/P60

A17/P61

A18/P62

A19/P63

A20/P64

A21/P65

A22/P66

A23/P67

O

Bit 16 to bit 23 of external address bus

These pins are available as ports when the address bus is not in use.

45

RDY/P80

C

External RDY input

This function is enabled when external RDY input is allowed.

Input "0" when the bus cycle being executed does not end.

This pin is available as a port when external RDY input is not in use.

MB91F155A/MB91155/MB91154

6

(Continued)

Pin No.

Pin name

Circuit

type

Function

46

BGRNT/P81

F

External bus release acceptance output

This function is enabled when external bus release acceptance output is

allowed.

Output "L" upon releasing of the external bus.

This pin is available as a port when external bus release acceptance out-

put is not allowed.

47

BRQ/P82

C

External bus release request input

This function is enabled when external bus release request input is al-

lowed.

Input "1" when the release of the external bus is desired.

This pin is available as a port when external bus release request input is

not in use.

48

RD/P83

F

External bus read strobe output

This function is enabled when external bus read strobe output is allowed.

This pin is available as a port when external bus read strobe output is not

allowed.

49

WR0/P84

F

External bus write strobe output

This function is enabled in external bus mode.

This pin is available as a port in single chip mode.

50

WR1/P85

F

External bus write strobe output

This function is enabled in external bus mode when the bus width is 16

bits.

This pin is available as a port in single chip mode or when the external bus

width is 8 bits.

51

CLK/P86

F

System clock output

The pin outputs the same clock as the external bus operating frequency.

The pin is available as a port when it is not used to output the clock.

52

53

54

MD2

MD1

MD0

G

Mode pins

To use these pins, connect them directly to either V

CC

or V

SS

.

Use these pins to set the basic MCU operating mode.

55

RST

B

External reset input

57

58

X1

X0

A

High-speed clock oscillation pins (16.5 MHz)

60

61

62

63

INT0/PC0

INT1/PC1

INT2/PC2

INT3/PC3

H

External interrupt request input 0-3

Since this input is used more or less continuously when the corresponding

external interrupt is allowed, output by the port needs to be stopped ex-

cept when it is performed deliberately.

Since this port is allowed to input also in standby mode, it can be used to

reset the standby state.

These pins are available as ports when external interrupt request input is

not in use.

MB91F155A/MB91155/MB91154

7

(Continued)

Pin No.

Pin name

Circuit

type

Function

64

65

66

67

INT4/PC4/CS0

INT5/PC5/CS1

INT6/PC6/CS2

INT7/PC7/CS3

H

These pins also serve as the chip select output and external inter-

rupt request input 4-7.

When the chip select output is not allowed, these pins are available

as external interrupt requests or ports.

Since this input is used more or less continuously when the corre-

sponding external interrupt is allowed, output by the port needs to

be stopped except when it is performed deliberately.

Since this port is also allowed to input in standby mode, the port can

be used to reset the standby state.

These pins are available as ports when external interrupt request

input and chip select output are not in use.

69

70

71

72

73

74

PD0/AIN0/INT8/TRG0

PD1/BIN0/INT9/TRG1

PD2/AIN1/INT10/TRG2

PD3/BIN1/INT11/TRG3

PD4/ZIN0/INT12/TRG4

PD5/ZIN1/INT13/TRG5

H

External interrupt request input 8-13

Since this input is used more or less continuously when the corre-

sponding external interrupt is allowed, output by the port needs to

be stopped except when it is performed deliberately.

[AIN, BIN] Up/down timer input.

[TRG] PPG external trigger input.

Since this input is used more or less continuously while input is al-

lowed, output by the port needs to be stopped except when it is per-

formed deliberately.

These pins are available as ports when the external interrupt re-

quest input, up timer counter input, and PPG external trigger input

are not in use.

75

PD6/DEOP2/INT14

H

External interrupt request input 14

Since this input is used more or less continuously when the corre-

sponding external interrupt is allowed, output by the port needs to

be stopped except when it is performed deliberately.

[DEOP2] DMA external transfer end output.

This function is enabled when DMAC external transfer end output

is allowed.

This pin is available as a port when it is not in use as the external

interrupt request input or DMA external transfer end output.

76

PD7/ATG/INT15

H

External interrupt request input 15

Since this input is used more or less continuously when the corre-

sponding external interrupt is allowed, output by the port needs to

be stopped except when it is performed deliberately.

[ATG] A/D converter external trigger input.

Since this input is used more or less continuously when selected as

an A/D activation factor, output by the port needs to be stopped ex-

cept when it is performed deliberately.

This pin is available as a port when it is not in use as the external

interrupt request input or A/D converter external trigger input.

MB91F155A/MB91155/MB91154

8

(Continued)

Pin No.

Pin name

Circuit

type

Function

78

79

80

81

82

83

84

85

PE0/OC0

PE1/OC1

PE2/OC2

PE3/OC3

PE4/OC4

PE5/OC5

PE6/OC6

PE7/OC7

F

Output compare output

These pins are available as ports when output compare output is not al-

lowed.

86

87

88

89

PF0/IN0

PF1/IN1

PF2/IN2

PF3/IN3

F

Input capture input

This function is enabled when the input capture operation is input.

These pins are available as ports when input capture input is not in use.

90

PF4

F

General purpose I/O port

91

92

93

94

95

96

PG0/PPG0

PG1/PPG1

PG2/PPG2

PG3/PPG3

PG4/PPG4

PG5/PPG5

F

PPG timer output

This function is enabled when PPG timer output is allowed.

These pins are available as ports when PPG timer output is not allowed.

99

PJ1/SDA

Q

I

2

C interface I/O pin

This function is enabled when the I

2

C interface is allowed to operate.

While the I

2

C interface is in operation, keep the port output set to Hi-Z.

This pin is available as a port when the I

2

C interface is not in use.

100

PJ0/SCL

Q

I

2

C interface I/O pin

This function is enabled when the I

2

C interface is allowed to operate.

While the I

2

C interface is in operation, keep the port output set to Hi-Z.

This pin is available as a port when the I

2

C interface is not in use.

102

PI5/SCK3/TO3

P

UART3 clock I/O, Reload timer 3 output

When UART3 clock output is not allowed, reload timer 3 can be output by

allowing it.

This pin is available as a port when neither UART3 clock output nor reload

timer output is allowed.

103

PI4/SOT3

P

UART3 data output

This function is enabled when UART3 data output is allowed.

This pin is available as a port when UART3 clock output is not allowed.

104

PI3/SIN3

P

UART3 data input

Since this input is used more or less continuously while UART3 is en-

gaged in input operations, output by the port needs to be stopped except

when it is performed deliberately.

This pin is available as a port when UART3 output data input is not in use.

MB91F155A/MB91155/MB91154

9

(Continued)

Pin No.

Pin name

Circuit

type

Function

105

PI2/SCK2/TO2

P

UART2 clock I/O, Reload timer 2 output

When UART2 clock output is not allowed, reload timer 2 can be output by

allowing it.

This pin is available as a port when neither UART2 clock output nor reload

timer output is allowed.

106

PI1/SOT2

P

UART2 data output

This function is enabled when UART2 data output is allowed.

This pin is available as a port when UART2 clock output is not allowed.

107

PI0/SIN2

P

UART2 data input

Since this input is used more or less continuously while UART2 is en-

gaged in input operations, output by the port needs to be stopped except

when it is performed deliberately.

This pin is available as a port when UART2 data input is not in use.

108

PH5/SCK1/TO1

P

UART1 clock I/O, Reload timer 1 output

When UART1 clock output is not allowed, reload timer 1 can be output by

allowing it.

This pin is available as a port when neither UART1 clock output nor reload

timer output is allowed.

109

PH4/SOT1

P

UART1 data output

This function is enabled when UART1 data output is allowed.

This pin is available as a port when UART1 clock output is not allowed.

110

PH3/SIN1

P

UART1 data input

Since this input is used more or less continuously while UART1 is en-

gaged in input operations, output by the port needs to be stopped except

when it is performed deliberately.

This pin is available as a port when UART1 data input is not in use.

111

PH2/SCK0/TO0

P

UART0 clock I/O, Reload timer 0 output

When UART0 clock output is not allowed, reload timer 0 can be output by

allowing it.

This pin is available as a port when neither UART0 clock output nor reload

timer output is allowed.

112

PH1/SOT0

P

UART0 data output

This function is enabled when UART0 data output is allowed.

This pin is available as a port when UART0 clock output is not allowed.

113

PH0/SIN0

P

UART0 data input

Since this input is used more or less continuously while UART0 is en-

gaged in input operations, output by the port needs to be stopped except

when it is performed deliberately.

This pin is available as a port when UART0 data input is not in use.

114

DREQ0/PL0

F

DMA external transfer request input

Since this input is used more or less continuously when selected as a

DMAC transfer factor, output by the port needs to be stopped except when

it is performed deliberately.

This pin is available as a port when DMA external transfer request input is

not in use.

MB91F155A/MB91155/MB91154

10

(Continued)

Pin No.

Pin name

Circuit

type

Function

115

DACK0/PL1

F

DMA external transfer request acceptance output

This function is enabled when the DMAC external transfer request accep-

tance is allowed to be output.

This pin is available as a port when the DMAC transfer request accep-

tance is not allowed to be output.

116

DEOP0/PL2

F

DMA external transfer end output

This function is enabled when the end of DMAC external transfer is al-

lowed to be output.

117

DREQ1/PL3

F

DMA external transfer request input

Since this input is used more or less continuously when selected as a

DMAC transfer factor, output by the port needs to be stopped except when

it is performed deliberately.

This pin is available as a port when DMA external transfer request input is

not in use.

118

DACK1/PL4

F

DMA external transfer request acceptance output

This function is enabled when the DMAC external transfer request accep-

tance is allowed to be output.

This pin is available as a port when DMAC transfer request acceptance

output is not allowed.

119

DEOP1/PL5

F

DMA external transfer end output

This function is enabled when the end of DMAC external transfer is al-

lowed to be output.

120

DREQ2/PL6

F

DMA external transfer request input

Since this input is used more or less continuously when selected as a

DMAC transfer factor, output by the port needs to be stopped except when

it is performed deliberately.

This pin is available as a port when DMA external transfer request input is

not in use.

121

DACK2/PL7

F

DMA external transfer request acceptance output

This function is enabled when the DMAC external transfer request accep-

tance is allowed to be output.

This pin is available as a port when DMAC transfer request acceptance

output is not allowed.

123

124

125

DA2

DA1

DA0

D/A converter output

This function is enabled when D/A converter output is allowed.

126

DAVS

Power supply pin for the D/A converter

127

DAVC

Power supply pin for the D/A converter

128

AV

CC

Vcc power supply for the A/D converter

129

AVRH

A/D converter reference voltage (high potential side)

Be sure to turn on/off this pin with potential higher than AVRH applied to

V

CC

.

130

AVRL

A/D converter reference voltage (low potential side)

131

AV

SS

V

SS

power supply for the A/D converter

MB91F155A/MB91155/MB91154

11

(Continued)

Note : On the majority of pins listed above, the I/O port and the resource I/O are multiplexed, such as XXXX/Pxx.

When the port and the resource output compete against each other on these pins, priority is given to the

resource.

Pin No.

Pin name

Circuit

type

Function

132

133

134

135

136

137

138

139

AN0/PK0

AN1/PK1

AN2/PK2

AN3/PK3

AN4/PK4

AN5/PK5

AN6/PK6

AN7/PK7

N

A/D converter analog input

These pins are enabled when the AIC register is designated for analog

input.

These pins are available as ports when A/D converter analog input is

not in use.

141

TEST

G

The TEST pin must be connected to the power supply (V

CC

)

142

143

X0A

X1A

K

Low-speed clock (32 kHz) oscillation pin

27, 56, 68,

77, 97,

122, 140

V

CC

Power supply pin (V

CC

) for digital circuit

Always power supply pin (V

CC

) must be connected to the power

supply

9, 26, 44,

59, 98,

101, 144

V

SS

Earth level (V

SS

) for digital circuit

Always power supply pin (V

SS

) must be connected to the power

supply

MB91F155A/MB91155/MB91154

12

s

s

s

s

I/O CIRCUIT TYPE

(Continued)

Type

Circuit

Remarks

A

· High-speed oscillation circuit

(16.5 MHz)

Oscillation feedback resistor

=

approx. 1 M

B

· CMOS hysteresis input pin

CMOS hysteresis input

(standby control not attached)

Pullup resistor

C

· CMOS level I/O pin

CMOS level output

CMOS level input

(attached with standby control)

I

OL

=

4 mA

F

· CMOS hysteresis I/O pin

CMOS level output

CMOS hysteresis input

(attached with standby control)

I

OL

=

4 mA

X1

X0

Xout

Standby control signal

Digital input

Pout

Nout

CMOS input

Standby control

R

Pout

Nout

Hysteresis input

Standby control

R

MB91F155A/MB91155/MB91154

13

(Continued)

Type

Circuit

Remarks

G

· CMOS level input pin

CMOS level input

(standby control not attached)

H

· CMOS hysteresis I/O pin with pul-

lup control

CMOS level output

CMOS level input

(standby control not attached)

Pullup resistance

=

approx. 50 k

(Typ.)

I

OL

=

4 mA

K

· Clock oscillation circuit (32 kHz)

N

· Analog/CMOS level I/O pin.

CMOS level output

CMOS level input

(attached with standby control)

Analog input (Analog input is en-

abled when AIC's corresponding

bit is set to "1.")

I

OL

=

4 mA

R

Digital input

R

R

Pout

Pullup control

Hysteresis input

Nout

X1A

X0A

Xout

Pout

Nout

CMOS input

Standby control

Analog input

R

MB91F155A/MB91155/MB91154

14

(Continued)

Type

Circuit

Remarks

O

· CMOS hysteresis I/O pin

with pullup control

CMOS level output

CMOS hysteresis input

(attached with standby control)

Pullup resistance

=

approx. 50 k

(Typ.)

I

OL

=

4 mA

P

· CMOS hysteresis I/O pin

with pullup control.

CMOS level output

(attached with open drain con-

trol)

CMOS hysteresis input

(attached with standby control)

Pullup resistance

=

approx. 50 k

(Typ.)

I

OL

=

4 mA

Q

· Open drain I/O pin

· 5 V tolerance of voltage

· CMOS hysteresis input

(attached with standby control)

I

OL

=

15 mA

Pout

Pullup control

Hysteresis input

Standby control

Nout

R

R

Nout

Pullup control

Open drain control

Hysteresis input

Standby control

R

R

Nout

Hysteresis input

Standby control

R

MB91F155A/MB91155/MB91154

15

s

s

s

s

HANDLING DEVICES

1.

Preventing Latchup

In CMOS ICs, applying voltage higher than V

CC

or lower than V

SS

to input/output pin or applying voltage over

rating across V

CC

and V

SS

may cause latchup.

This phenomenon rapidly increases the power supply current, which may result in thermal breakdown of the

device. Make sure to prevent the voltage from exceeding the maximum rating.

2.

Treatment of Pins

· Treatment of unused pins

Unused pins left open may cause malfunctions. Make sure to connect them to pull-up or pull-down resistors.

· Treatment of open pins

Be sure to use open pins in open state.

· Treatment of output pins

Shortcircuiting an output pin with the power supply or with another output pin or connecting a large-capacity

load may causes a flow of large current. If this conditions continues for a lengthy period of time, the device

deteriorates. Take great care not to exceed the absolute maximum ratings.

· Mode pins (MD0-MD2)

These pins should be used directly connected to either V

CC

or V

SS

. In order to prevent noise from causing

accidental entry into test mode, keep the pattern length as short as possible between each mode pin and V

CC

or V

SS

on the board and connect them with low impedance.

· Power supply pins

When there are several V

CC

and V

SS

pins, each of them is equipotentially connected to its counterpart inside

of the device, minimizing the risk of malfunctions such as latch up. To further reduce the risk of malfunctions,

to prevent EMI radiation, to prevent strobe signal malfunction resulting from creeping-up of ground level and

to observe the total output current standard, connect all V

CC

and V

SS

pins to the power supply or GND.

It is preferred to connect V

CC

and V

SS

of MB91F155/MB91154 to power supply with minimal impedance possible.

It is also recommended to connect a ceramic capacitor as a bypass capacitor of about 0.1

µ

F between V

CC

and

V

SS

at a position as close as possible to MB91F155/MB91154.

· Crystal oscillator circuit

Noises around X0, X1, X0A, and X1A pins may cause malfunctions of MB91F155/MB91154. In designing the

PC board, layout X0, X1 (X0A, X1A) and crystal oscillator (or ceramic oscillator) and bypass capacitor for

grounding as close as possible.

It is strongly recommended to design PC board so that X0, X1, X0A, and X1A pins are surrounded by grounding

area for stable operation.

The MB91F155A, MB91155 and MB91154 devices do not contain a feedback resistor. To use the clock function,

you need to connect an external resistor.

3.

Precautions

· External Reset Input

It takes at least 5 machine cycle to input "L" level to the RST pin and to ensure inner reset operation properly.

· External Clocks

When using an external clock, normally, a clock of which the phase is opposite to that of X0 must be supplied

to the X0 and X1 pins simultaneously. However, when using the clock along with STOP (oscillation stopped)

X0A

X1A

MB91F155A/MB91155/MB91154

MB91F155A/MB91155/MB91154

16

mode, the X1 pin stops when "H" is input in STOP mode. To prevent one output from competing against another,

an external resistor of about 1 k

should be provided.

The following figure shows an example usage of an external clock.

Figure 2.1 An example usage of an external clock

4.

Care During Powering Up

· When powering up

When turning on the power supply, never fail to start from setting the RST pin to "L" level. And after the power

supply voltage goes to V

CC

level, at least after ensuring the time for 5 machine cycle, then set to "H" level.

· Source oscillation input

At turning on the power supply, never fail to input the clock before cancellation of the oscillation stabilizing

waiting.

· Power on resetting

When powering up or when turning the power back on after the supply voltage drops below the operation

assurance range, be sure to reset the power.

· Power on sequence

Turn on the power in the order of V

CC

, AV

CC

and AVRH. The power should be disconnected in inverse order.

· Even when an AD converter is not in use, connect AV

CC

to the V

CC

level and AV

SS

to the V

SS

level.

· Even when a DA converter is not in use, connect DAVC to the V

CC

level and DAVS to the V

SS

level.

5.

When the Clock Function (Calendar Macro) Is Not in Use

Not using the clock function, the clock oscillation pin must be configured as shown below.

X0

X1

MB91F155A/MB91155/MB91154

X0A

X1A

MB91F155A/MB91155/MB91154

OPEN

This product type does not allow the clock crystal oscillator to be stopped with software.

MB91F155A/MB91155/MB91154

17

s

s

s

s

BLOCK DIAGRAM

· MB91F155A, MB91155

FR30 CPU Core

I - Bus

D - Bus

I - Bus

D - Bus

C - Bus

External

Bus CTL

UART 4 ch

UTIMER 4 ch

16 bit

Reload Timer

RAM

2 KB

ROM

510 KB

Clock

Control

Interrupt

Controller

8 bit

Up/Down

Counter

External

Interrupt

2 ch

1 ch

4 ch

16 bit

Free RUN Timer

1 ch

16 bit

Input Capture

4 ch

16 bit

Output Compare

10 bit 8 input

A/D converter

8 bit 3 output

D/A converter

I

2

C Interface

8 ch

16 bit PPG

6 ch

16 ch

Calendar

Data RAM

DMAC 8 ch

Bit Search

32 KB

D - Bus

R - Bus

P

O

R

T

D

8

( )

P

O

R

T

L

8

( )

P

O

R

T

6

/

5

/

4

24

P

O

R

T

3

/

2

16

M

O

D

E

4

( )

(

)

(

)

P

O

R

T

8

7( )

P

O

R

T

C

8

( )

PD7/INT15/ATG (I)

PD6/INT14/DEOP2

PD5/INT13/ZIN1

PD4/INT12/ZIN0

PD3/INT11/BIN1

PD2/INT10/AIN1

PD1/INT9/BIN0 (I)

PD0/INT8/AIN0 (I)

PC7/INT7/CS3

PC6/INT6/CS2

PC5/INT5/CS1

PC4/INT4/CS0

PC3/INT3

PC2/INT2

PC1/INT1

PC0/INT0 (I)

A/D

DMAC

Up/Down

Counter

External

Interrupt

OSC

(2)

OSC

(2)

P

O

R

T

K

8

P

O

R

T

E

8

P

O

R

T

I

6

P

O

R

T

F

5

P

O

R

T

J

2

D

A

3

( )

( )

( )

P

O

R

T

H

6( )

P

O

R

T

G

6( )

( )

( )

( )

PE7/OC7

PE6/OC6

PE5/OC5

PE4/OC4

PE3/OC3

PE2/OC2

PE1/OC1

PE0/OC0

PL7/DACK2

PL6/DREQ2

PL5/DEOP1

PL4/DACK1

PL3/DREQ1

PL2/DEOP0 (O)

PL1/DACK0 (O)

PL0/DREQ0 (I)

P86/CLK (O)

P85/WR1 (O)

P84/WR0

P83/RD (O)

P82/BRQ (I)

P81/BGRNT (O)

P80/RDY (I)

P67/A23 (O)

P60/A16

P57/A15

P50/A8

P47/A7

P40/A0

P37/D31 (IO)

P30/D24

P27/D23

P20/D16

PG5/PPG5

PG4/PPG4

PG3/PPG3

PG2/PPG2

PG1/PPG1

PG0/PPG0

PF4

PF3/IN3

PF2/IN2

PF1/IN1

PF0/IN0

DA2

DA1

DA0

X0A

X1A

X0 (I)

X1 (I)

PH0/SIN0

PH1/SOT0

PH2/SCK0/TO0

PH3/SIN1

PH4/SOT1

PH5/SCK1/TO1

PI0/SIN2

PI1/SOT2

PI2/SCK2/TO2

PI3/SIN3

PI4/SOT3

PI5/SCK3/TO3

PK0/AN0

PK1/AN1

PK2/AN2

PK3/AN3

PK4/AN4

PK5/AN5

PK6/AN6

PK7/AN7

PJ0/SCL

PJ1/SDA

UART

TOX:

Reload

Timer

PPG

Input

Capture

Clock

Clock

DMAC

Bus

Control

Address

DATA

Output

Compare

A/D

I

2

C

MD1

MD2

RST

MD0

MB91F155A/MB91155/MB91154

18

· MB91154

FR30 CPU Core

I - Bus

D - Bus

I - Bus

D - Bus

C - Bus

External

Bus CTL

UART 4 ch

UTIMER 4 ch

16 bit

Reload Timer

RAM

2 KB

ROM

384 KB

Clock

Control

Interrupt

Controller

8 bit

Up/Down

Counter

External

Interrupt

2 ch

1 ch

4 ch

16 bit

Free RUN Timer

1 ch

16 bit

Input Capture

4 ch

16 bit

Output Compare

10 bit 8 input

A/D converter

8 bit 3 output

D/A converter

I

2

C Interface

8 ch

16 bit PPG

6 ch

16 ch

Calendar

Data RAM

DMAC 8 ch

Bit Search

20 KB

D - Bus

R - Bus

P

O

R

T

D

8

( )

P

O

R

T

L

8

( )

P

O

R

T

6

/

5

/

4

24

P

O

R

T

3

/

2

16

M

O

D

E

4

( )

(

)

(

)

P

O

R

T

8

7( )

P

O

R

T

C

8

( )

PD7/INT15/ATG (I)

PD6/INT14/DEOP2

PD5/INT13/ZIN1

PD4/INT12/ZIN0

PD3/INT11/BIN1

PD2/INT10/AIN1

PD1/INT9/BIN0 (I)

PD0/INT8/AIN0 (I)

PC7/INT7/CS3

PC6/INT6/CS2

PC5/INT5/CS1

PC4/INT4/CS0

PC3/INT3

PC2/INT2

PC1/INT1

PC0/INT0 (I)

A/D

DMAC

Up/Down

Counter

External

Interrupt

OSC

(2)

OSC

(2)

P

O

R

T

K

8

P

O

R

T

E

8

P

O

R

T

I

6

P

O

R

T

F

5

P

O

R

T

J

2

D

A

3

( )

( )

( )

P

O

R

T

H

6( )

P

O

R

T

G

6( )

(

)

( )

( )

PE7/OC7

PE6/OC6

PE5/OC5

PE4/OC4

PE3/OC3

PE2/OC2

PE1/OC1

PE0/OC0

PL7/DACK2

PL6/DREQ2

PL5/DEOP1

PL4/DACK1

PL3/DREQ1

PL2/DEOP0 (O)

PL1/DACK0 (O)

PL0/DREQ0 (I)

P86/CLK (O)

P85/WR1 (O)

P84/WR0

P83/RD (O)

P82/BRQ (I)

P81/BGRNT (O)

P80/RDY (I)

P67/A23 (O)

P60/A16

P57/A15

P50/A8

P47/A7

P40/A0

P37/D31 (IO)

P30/D24

P27/D23

P20/D16

PG5/PPG5

PG4/PPG4

PG3/PPG3

PG2/PPG2

PG1/PPG1

PG0/PPG0

PF4

PF3/IN3

PF2/IN2

PF1/IN1

PF0/IN0

DA2

DA1

DA0

X0A

X1A

X0 (I)

X1 (I)

PH0/SIN0

PH1/SOT0

PH2/SCK0/TO0

PH3/SIN1

PH4/SOT1

PH5/SCK1/TO1

PI0/SIN2

PI1/SOT2

PI2/SCK2/TO2

PI3/SIN3

PI4/SOT3

PI5/SCK3/TO3

PK0/AN0

PK1/AN1

PK2/AN2

PK3/AN3

PK4/AN4

PK5/AN5

PK6/AN6

PK7/AN7

PJ0/SCL

PJ1/SDA

UART

TOX:

Reload

Timer

PPG

Input

Capture

Clock

Clock

DMAC

Bus

Control

Address

DATA

Output

Compare

A/D

I

2

C

MD1

MD2

RST

MD0

MB91F155A/MB91155/MB91154

19

s

s

s

s

CPU CORE

1.

Memory Space

The FR family has a logical address space of 4 Gbytes (2

32

bytes) and the CPU linearly accesses the memory

space.

· Direct addressing area

The following area in the address space is used for I/O.

This area is called direct addressing area and an operand address can be specified directly in an instruction.

The direct addressing area varies with the data size to be accessed as follows :

2.

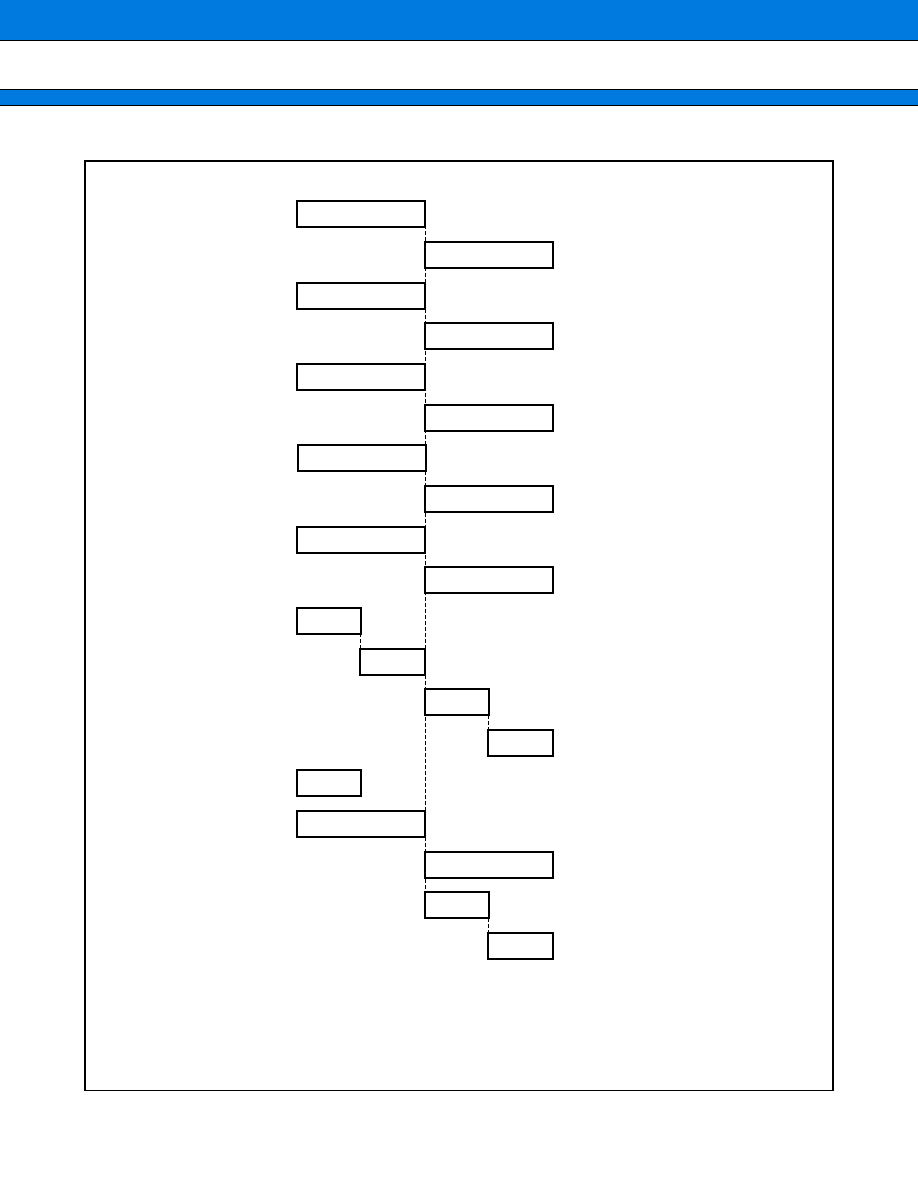

Memory Map

byte data access :

0-0FF

H

half word data access : 0-1FF

H

word data access :

0-3FF

H

· MB91F155, MB91155 Memory Space

Note : External areas are not accessible in single-chip mode.

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 9000

H

0001 0000

H

FFFF FFFF

H

0001 0000

H

Direct

addressing

area

See "

s

I/O MAP"

0008 0000

H

0008 0800

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I/O

I/O

I/O

External ROM-

external bus mode

Internal ROM-

external bus mode

Single-chip mode

I/O

Not accessible

Not accessible

Not accessible

32 KB

internal RAM

32 KB

internal RAM

32 KB

internal RAM

Not accessible

External area

Not accessible

Not accessible

External area

Not accessible

2 KB internal RAM

2 KB internal RAM

510 KB

internal ROM

510 KB

internal ROM

External area

Not accessible

MB91F155A/MB91155/MB91154

20

· MB91154 Memory Space

Note : External areas are not accessible in single-chip mode.

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 6000

H

0001 0000

H

FFFF FFFF

H

0001 0000

H

Direct

addressing

area

See "

s

I/O MAP"

0008 0000

H

0008 0800

H

000A 0000

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I/O

I/O

I/O

External ROM-

external bus mode

Internal ROM-

external bus mode

Single-chip mode

I/O

Not accessible

Not accessible

Not accessible

Not accessible

External area

Not accessible

Not accessible

External area

Not accessible

Not accessible

Not accessible

384 KB

internal ROM

384 KB

internal ROM

External area

Not accessible

2 KB internal RAM

2 KB internal RAM

20 KB

internal RAM

20 KB

internal RAM

20 KB

internal RAM

MB91F155A/MB91155/MB91154

21

3.

Registers

The family of FR microcontrollers has two types of registers : the registers residing in the CPU which are dedicated

to applications and the general-purpose registers residing in the memory.

· Dedicated registers :

· Program status (PS)

The PS register holds program status and is further divided into three registers which are a Condition Code

Register (CCR) , a System condition Code Register (SCR) , and an Interrupt Level Mask register (ILM) .

Program counter (PC)

: A 32-bit register to indicate the location where an instructions is stored.

Program status (PS)

: A 32-bit register to store a register pointer or a condition code.

Tablebase register (TBR)

: Holds the vector table lead address used when EIT (exceptions/interrupt/

trap) is processed.

Return pointer (RP)

: Holds the address to return from a subroutine to.

System stack pointer (SSP) : Points to the system stack space.

User stack pointer (USP)

: Points to the user stack space.

Multiplication and division result register (MDH/MDL) : A 32-bit multiplication and division register.

PC

PS

TBR

RP

SSP

USP

MDH

MDL

Program counter

Program status

Tablebase register

Return pointer

System stack pointer

User stack pointer

Multiplication and division register

(Undefined)

(Undefined)

(Undefined)

(Undefined)

(Undefined)

XXXX XXXX

H

XXXX XXXX

H

XXXX XXXX

H

XXXX XXXX

H

XXXX XXXX

H

0000 0000

H

000F FC00

H

32 bit

Initial value

PS

ILM4 ILM3 ILM2

ILM

SCR

CCR

ILM1 ILM0

D1

D0

T

S

I

N

Z

V

C

0

1

2

3

4

5

6

7

8

9

10

16

17

18

19

20

31

MB91F155A/MB91155/MB91154

22

· Condition Code Register (CCR)

· System condition Code Register (SCR)

· Interrupt Level Mask register (ILM)

S flag

: Designates the stack pointer for use as R15.

I flag

: Controls enabling and disabling of user interrupt requests.

N flag

: Indicates the sign when arithmetic operation results are considered to be an integer represented

by 2's complement.

Z flag

: Indicates if arithmetic results were "0."

V flag

: Considers the operand used for an arithmetic operation to be an integer represented by 2's com-

plement and indicates if the operation resulted in an overflow.

C flag

: Indicates whether or not an arithmetic operation resulted in a carry or a borrow from the most sig-

nificant bit.

T flag

: Designates whether or not to enable step trace trap.

ILM4 to ILM0

: Holds an interrupt level mask value to be used for level masking.

An interrupt request is accepted only if the corresponding interrupt level among interrupt

requests input to the CPU is higher than the value indicated by the ILM register.

ILM4

ILM3

ILM2

ILM1

ILM0

Interrupt level

High-Low

0

0

0

0

0

0

Higher

0

1

0

0

0

15

1

1

1

1

1

31

Lower

MB91F155A/MB91155/MB91154

23

s

s

s

s

GENERAL-PURPOSE REGISTERS

General-purpose registers are CPU registers R0 through R15 and used as accumulators during various oper-

ations and as memory access pointers (fields indicating addresses) .

Of the 16 general-purpose registers, the following registers are assumed for specific applications. For this reason,

some instructions are enhanced.

R13 : Virtual accumulator (AC)

R14 : Frame pointer (FP)

R15 : Stack pointer (SP)

Initial values to which R0 through R14 are reset are not defined. The initial value of R15 is 0000 0000

H

(the SSP

value) .

· Register Bank Configuration

R0

R1

R12

R13

R14

R15

AC (Accumulator)

FP (Frame Pointer)

SP (Stack Pointer)

XXXX XXXX

H

Initial value

XXXX XXXX

H

0000 0000

H

32 bit

MB91F155A/MB91155/MB91154

24

s

s

s

s

SETTING MODE

1.

Mode Pins

As shown in Table 1 three pins, MD2, 1, and 0 are used to indicate an operation.

Table 1 Mode pins and set modes

2.

Mode Data

The data which the CPU writes to "0000 07FF

H

" after reset is called mode data.

It is the mode register (MODR) that exists at "0000 07FF

H

." Once a mode is set in this register, operations will

take place in that mode. The mode register can be written only once after reset.

The mode specified in the register is enabled immediately after it is written.

[bits 7 and 6] : M1, M0

These are bus mode setting bits. Specify the bus mode to be set to after writing to the mode register.

[bits 5 to 0] :

These bits are reserved for the system.

Mode pin

Mode name

Reset vector

access area

External data

bus width

MD2

MD1

MD0

0

0

0

External vector mode 0

External

8 bits

External ROM bus mode

0

0

1

External vector mode 1

External

16 bits

0

1

0

External vector mode 2

External

32 bits

Not available on this

product type

0

1

1

External vector mode

Internal

(Mode register) Single-chip mode

1

Not available

M1

M0

Function

Remarks

0

0

Single-chip mode

0

1

Internal ROM-external bus mode

1

0

External ROM-external bus mode

1

1

Setting not allowed

"0" should be written to these bits at all times.

MODR

Initial value Access

Address : 0000 07FF

H

XXXXXXXX

W

W : Write only, X : Undefined

M1

M0

Bus mode setting bits

MB91F155A/MB91155/MB91154

25

[Precautions When Writing to the MODR]

Before writing to the MODR, be sure to set AMD0 through 5 and determine the bus width in each CS (Chip

Select) area.

The MODR does not have bus width setting bits.

The bus width value set with mode pins MD2 through 0 is enabled before writing to the MODR and the bus width

value set with BW1 and 0 of AMD0 through 5 is enabled after writing to the MODR.

For example, the external reset vector is normally executed with area 0 (the area where CS0 is active) and the

bus width at that time is determined by pins MD 2 through 0. Suppose that the bus width is set to 32 or 16 bits

in MD2 though 0 but no value is specified in AMD 0. If the MODR is written in this state, area 0 then switches

to 8-bit bus mode and operates the bus since the initial bus width in AMD0 is set to 8 bits. This causes a

malfunction.

In order to prevent this type of problem, AMD0 through 5 must always be set before writing to the MODR.

Writing to the MODR.

AMD0 to AMD5 BW1, 0

Designated bus width : MD2,1,0

RST (Reset)

MB91F155A/MB91155/MB91154

26

s

s

s

s

I/O MAP

(Continued)

Address

Register

Block

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000000

H

PDR3 (R/W)

XXXXXXXX

PDR2 (R/W)

XXXXXXXX

Port Data Register

000004

H

PDR6 (R/W)

XXXXXXXX

PDR5 (R/W)

XXXXXXXX

PDR4 (R/W)

XXXXXXXX

000008

H

PDR8 (R/W)

- XXXXXXX

00000C

H

000010

H

PDRF (R/W)

- - - XXXXX

PDRE (R/W)

XXXXXXXX

PDRD (R/W)

XXXXXXXX

PDRC (R/W)

XXXXXXXX

000014

H

PDRJ (R/W)

- - - - - - 11

PDRI (R/W)

- - XXXXXX

PDRH (R/W)

- - XXXXXX

PDRG (R/W)

- - XXXXXX

000018

H

PDRL (R/W)

XXXXXXXX

PDRK (R/W)

XXXXXXXX

00001C

H

SSR0 (R, R/W)

00001000

SIDR0/SODR0

(R, W)

XXXXXXXX

SCR0 (R/W, W)

00000100

SMR0 (R/W)

00000 - 00

UART0

000020

H

SSR1 (R, R/W)

00001000

SIDR1/SODR1

(R, W)

XXXXXXXX

SCR1 (R/W, W)

00000100

SMR1 (R/W)

00000 - 00

UART1

000024

H

SSR2 (R, R/W)

00001000

SIDR2/SODR2

(R, W)

XXXXXXXX

SCR2 (R/W, W)

00000100

SMR2 (R/W)

00000 - 00

UART2

000028

H

SSR3 (R, R/W)

00001000

SIDR3/SODR3

(R, W)

XXXXXXXX

SCR3 (R/W, W)

00000100

SMR3 (R/W)

00000 - 00

UART3

00002C

H

TMRLR0 (W)

XXXXXXXX XXXXXXXX

TMR0 (R)

XXXXXXXX XXXXXXXX

Reload Timer 0

000030

H

TMCSR0 (R/W)

- - - - 0000 00000000

000034

H

TMRLR1 (W)

XXXXXXXX XXXXXXXX

TMR1 (R)

XXXXXXXX XXXXXXXX

Reload Timer 1

000038

H

TMCSR1 (R/W)

- - - - 0000 00000000

00003C

H

TMRLR2 (W)

XXXXXXXX XXXXXXXX

TMR2 (R)

XXXXXXXX XXXXXXXX

Reload Timer 2

000040

H

TMCSR2 (R/W)

- - - - 0000 00000000

MB91F155A/MB91155/MB91154

27

(Continued)

Address

Register

Block

000044

H

TMRLR3 (W)

XXXXXXXX XXXXXXXX

TMR3 (R)

XXXXXXXX XXXXXXXX

Reload Timer 3

000048

H

TMCSR3 (R/W)

- - - - 0000 00000000

00004C

H

CDCR1 (R/W)

0 - - - 0000

CDCR0 (R/W)

0 - - - 0000

Communications

prescaler 1

000050

H

CDCR3 (R/W)

0 - - - 0000

CDCR2 (R/W)

0 - - - 0000

000054

H

to

000058

H

Reserved

00005C

H

RCR1 (W)

00000000

RCR0 (W)

00000000

UDCR1 (R)

00000000

UDCR0 (R)

00000000

8/16 bit U/D Counter

000060

H

CCRH0 (R/W)

00000000

CCRL0 (R/W, W)

- 000X000

CSR0 (R/W, R)

00000000

000064

H

CCRH1 (R/W)

- 0000000

CCRL1 (R/W, W)

- 000X000

CSR1 (R/W, R)

00000000

000068

H

IPCP1 (R)

XXXXXXXX XXXXXXXX

IPCP0 (R)

XXXXXXXX XXXXXXXX

16 bit ICU

00006C

H

IPCP3 (R)

XXXXXXXX XXXXXXXX

IPCP2 (R)

XXXXXXXX XXXXXXXX

000070

H

ICS23 (R/W)

00000000

ICS01 (R/W)

00000000

000074

H

OCCP1 (R/W)

XXXXXXXX XXXXXXXX

OCCP0 (R/W)

XXXXXXXX XXXXXXXX

16 bit OCU

000078

H

OCCP3 (R/W)

XXXXXXXX XXXXXXXX

OCCP2 (R/W)

XXXXXXXX XXXXXXXX

00007C

H

OCCP5 (R/W)

XXXXXXXX XXXXXXXX

OCCP4 (R/W)

XXXXXXXX XXXXXXXX

000080

H

OCCP7 (R/W)

XXXXXXXX XXXXXXXX

OCCP6 (R/W)

XXXXXXXX XXXXXXXX

000084

H

OCS2, 3 (R/W)

XXX00000 0000XX00

OCS0, 1 (R/W)

XXX00000 0000XX00

000088

H

OCS6, 7 (R/W)

XXX00000 0000XX00

OCS4, 5 (R/W)

XXX00000 0000XX00

00008C

H

TCDT (R/W)

00000000 00000000

TCCS (R/W)

0 - - - - - - - 00000000

16 bit Freerun Timer

000090

H

STPR0 (R/W)

0000 - - - -

STPR1 (R/W)

00000000

STPR2 (R/W)

000000 - -

Stop Register 0, 1, 2

000094

H

GCN1 (R/W)

00110010 00010000

GCN2 (R/W)

00000000

PPG ctl

MB91F155A/MB91155/MB91154

28

(Continued)

Address

Register

Block

000098

H

PTMR0 (R)

11111111 11111111

PCSR0 (W)

XXXXXXXX XXXXXXXX

PPG0

00009C

H

PDUT0 (W)

XXXXXXXX XXXXXXXX

PCNH0 (R/W)

0000000 -

PCNL0 (R/W)

00000000

0000A0

H

PTMR1 (R)

11111111 11111111

PCSR1 (W)

XXXXXXXX XXXXXXXX

PPG1

0000A4

H

PDUT1 (W)

XXXXXXXX XXXXXXXX

PCNH1 (R/W)

0000000 -

PCNL1 (R/W)

00000000

0000A8

H

PTMR2 (R)

11111111 11111111

PCSR2 (W)

XXXXXXXX XXXXXXXX

PPG2

0000AC

H

PDUT2 (W)

XXXXXXXX XXXXXXXX

PCNH2 (R/W)

0000000 -

PCNL2 (R/W)

00000000

0000B0

H

PTMR3 (R)

11111111 11111111

PCSR3 (W)

XXXXXXXX XXXXXXXX

PPG3

0000B4

H

PDUT3 (W)

XXXXXXXX XXXXXXXX

PCNH3 (R/W)

0000000 -

PCNL3 (R/W)

00000000

0000B8

H

PTMR4 (R)

11111111 11111111

PCSR4 (W)

XXXXXXXX XXXXXXXX

PPG4

0000BC

H

PDUT4 (W)

XXXXXXXX XXXXXXXX

PCNH4 (R/W)

0000000 -

PCNL4 (R/W)

00000000

0000C0

H

PTMR5 (R)

11111111 11111111

PCSR5 (W)

XXXXXXXX XXXXXXXX

PPG5

0000C4

H

PDUT5 (W)

XXXXXXXX XXXXXXXX

PCNH5 (R/W)

0000000 -

PCNL5 (R/W)

00000000

0000C8

H

EIRR0 (R/W)

00000000

ENIR0 (R/W)

00000000

EIRR1 (R/W)

00000000

ENIR1 (R/W)

00000000

Ext int

0000CC

H

ELVR0 (R/W)

00000000 00000000

ELVR1 (R/W)

00000000 00000000

0000D0

H

to

0000D8

H

Reserved

0000DC

H

DACR2 (R/W)

- - - - - - - 0

DACR1 (R/W)

- - - - - - - 0

DACR0 (R/W)

- - - - - - - 0

D/A Converter

0000E0

H

DADR2 (R/W)

XXXXXXXX

DADR1 (R/W)

XXXXXXXX

DADR0 (R/W)

XXXXXXXX

0000E4

H

ADCR (R, W)

00101- XX XXXXXXXX

ADCS1 (R/W, W)

00000000

ADCS0 (R/W)

00000000

A/D Converter

(Sequential type)

0000E8

H

AICK (R/W)

00000000

Analog Input Control

0000EC

H

to

0000F0

H

Reserved

MB91F155A/MB91155/MB91154

29

(Continued)

Address

Register

Block

0000F4

H

PCRI (R/W)

- - 000000

PCRH (R/W)

- - 000000

PCRD (R/W)

00000000

PCRC (R/W)

00000000

Pull Up Control

0000F8

H

OCRI (R/W)

- - 000000

OCRH (R/W)

- - 000000

Opendrain Control

0000FC

H

DDRF (R/W)

- - - 00000

DDRE (R/W)

00000000

DDRD (R/W)

00000000

DDRC (R/W)

00000000

Data Direction

Register

000100

H

DDRI (R/W)

- 0000000

DDRH (R/W)

- - 000000

DDRG (R/W)

- - 000000

000104

H

DDRL (R/W)

00000000

DDRK (R/W)

00000000

000108

H

to

00011C

H

Reserved

000120

H

IBCR (R/W)

00000000

IBSR (R)

00000000

IADR (R/W)

- XXXXXXX

ICCR (R/W)

- - 0XXXXX

I

2

C Interface

000124

H

IDAR (R/W)

XXXXXXXX

000128

H

to

0001FC

H

Reserved

000200

H

DPDP (R/W)

- - - - - - - - - - - - - - - - - - - - - - - - - 0000000

DMAC

000204

H

DACSR (R/W)

00000000 00000000 00000000 00000000

000208

H

DATCR (R/W)

XXXXXXXX XXXX0000 XXXX0000 XXXX0000

00020C

H

Reserved

000210

H

CAC (R/W)

00000000

CA1 (R/W)

- - XXXXXX

CA2 (R/W)

- - XXXXXX

CA3 (R/W)

- - - XXXXX

Calendar

000214

H

CA4 (R/W)

- - - XXXXX

CA5 (R/W)

- - - - - XXX

CA6 (R/W)

- - - - XXXX

CA7 (R/W)

- XXXXXXX

000218

H

Reserved

00021C

H

CAS (R/W)

0 - - - - - - 0

Calendar

000220

H

to

0003EC

H

Reserved

MB91F155A/MB91155/MB91154

30

(Continued)

Address

Register

Block

0003F0

H

BSD0 (W)

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

Bit Search Module

0003E4

H

BSD1 (R/W)

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003F8

H

BSDC (W)

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003FC

H

BSRR (R)

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

000400

H

ICR00 (R/W)

- - - - 1111

ICR01 (R/W)

- - - - 1111

ICR02 (R/W)

- - - - 1111

ICR03 (R/W)

- - - - 1111

Interrupt Control unit

000404

H

ICR04 (R/W)

- - - - 1111

ICR05 (R/W)

- - - - 1111

ICR06 (R/W)

- - - - 1111

ICR07 (R/W)

- - - - 1111

000408

H

ICR08 (R/W)

- - - - 1111

ICR09 (R/W)

- - - - 1111

ICR10 (R/W)

- - - - 1111

ICR11 (R/W)

- - - - 1111

00040C

H

ICR12 (R/W)

- - - - 1111

ICR13 (R/W)

- - - - 1111

ICR14 (R/W)

- - - - 1111

ICR15 (R/W)

- - - - 1111

000410

H

ICR16 (R/W)

- - - - 1111

ICR17 (R/W)

- - - - 1111

ICR18 (R/W)

- - - - 1111

ICR19 (R/W)

- - - - 1111

000414

H

ICR20 (R/W)

- - - - 1111

ICR21 (R/W)

- - - - 1111

ICR22 (R/W)

- - - - 1111

ICR23 (R/W)

- - - - 1111

000418

H

ICR24 (R/W)

- - - - 1111

ICR25 (R/W)

- - - - 1111

ICR26 (R/W)

- - - - 1111

ICR27 (R/W)

- - - - 1111

00041C

H

ICR28 (R/W)

- - - - 1111

ICR29 (R/W)

- - - - 1111

ICR30 (R/W)

- - - - 1111

ICR31 (R/W)

- - - - 1111

000420

H

ICR32 (R/W)

- - - - 1111

ICR33 (R/W)

- - - - 1111

ICR34 (R/W)

- - - - 1111

ICR35 (R/W)

- - - - 1111

000424

H

ICR36 (R/W)

- - - - 1111

ICR37 (R/W)

- - - - 1111

ICR38 (R/W)

- - - - 1111

ICR39 (R/W)

- - - - 1111

000428

H

ICR40 (R/W)

- - - - 1111

ICR41 (R/W)

- - - - 1111

ICR42 (R/W)

- - - - 1111

ICR43 (R/W)

- - - - 1111

00042C

H

ICR44 (R/W)

- - - - 1111

ICR45 (R/W)

- - - - 1111

ICR46 (R/W)

- - - - 1111

ICR47 (R/W)

- - - - 1111

000430

H

DICR (R/W)

- - - - - - - 0

HRCL (R/W)

- - - - 1111

Delay int

000434

H

to

00047C

H

Reserved

000480

H

RSRR/WTCR

(R, W)

1-XXX-00

STCR (R/W, W)

000111- -

PDRR (R/W)

- - - - 0000

CTBR (W)

XXXXXXXX

Clock Control unit

000484

H

GCR (R/W, R)

110011-1

WPR (W)

XXXXXXXX

MB91F155A/MB91155/MB91154

31

(Continued)

Address

Register

Block

000488

H

PTCR (R/W)

00XX0XXX

PLL Control

00048C

H

to

0005FC

H

Reserved

000600

H

DDR3 (W)

00000000

DDR2 (W)

00000000

Data Direction

Register

000604

H

DDR6 (W)

00000000

DDR5 (W)

00000000

DDR4 (W)

00000000

000608

H

DDR8 (W)

- 0000000

00060C

H

ASR1 (W)

00000000 00000001

AMR1 (W)

00000000 00000000

T-unit

000610

H

ASR2 (W)

00000000 00000010

AMR2 (W)

00000000 00000000

000614

H

ASR3 (W)

00000000 00000011

AMR3 (W)

00000000 00000000

000618

H

ASR4 (W)

00000000 00000100

AMR4 (W)

00000000 00000000

00061C

H

ASR5 (W)

00000000 00000101

AMR5 (W)

00000000 00000000

000620

H

AMD0 (R/W)

- - - 00111

AMD1 (R/W)

0 - - 00000

AMD32 (R/W)

00000000

AMD4 (R/W)

0 - - 00000

000624

H

AMD5 (R/W)

0 - - 00000

000628

H

EPCR0 (W)

- - - - 1100 -1111111

EPCR1 (W)

- - - - - - - - 11111111

00062C

H

Reserved

000630

H

PCR6 (R/W)

00000000

Pull Up Control

000634

H

to

0007BC

H

Reserved

0007C0

H

FLCR (R/W, R)

000XXXX0

FLASH Control

0007C4

H

FWTC (R/W, W)

- - - - - 000

0007C8

H

to

0007F8

H

Reserved

MB91F155A/MB91155/MB91154

32

(Continued)

Note : Do not execute RMW instructions on registers having a write-only bit.

RMW instructions (RMW : Read Modify Write)

Data is undefined in "Reserved" or (

) areas.

Address

Register

Block

0007FC

H

LER (W)

- - - - - 000

MODR (W)

XXXXXXXX

Little Endian

Register

Mode Register

AND

Rj, @Ri

OR

Rj, @Ri

EOR

Rj, @Ri

ANDH

Rj, @Ri

ORH

Rj, @Ri

EORH

Rj, @Ri

ANDB

Rj, @Ri

ORB

Rj, @Ri

EORB

Rj, @Ri

BANDL #u4, @Ri

BORL #u4, @Ri

BEORL #u4, @Ri

BANDH #u4, @Ri

BORH #u4, @Ri

BEORH #u4, @Ri

( ) :

Access

R/W : Read/Write enabled

R :

Read only

W :

Write only

:

Not in use

X :

Undefined

MB91F155A/MB91155/MB91154

33

s

s

s

s

INTERRUPT FACTORS AND ASSIGNMENT OF INTERRUPT VECTORS AND RESISTERS

(Continued)

Factor

Interrupt No.

Interrupt

level

Offset

Default TBR

address

Decimal

Hex.

Reset

0

00

3FC

H

000FFFFC

H

Reserved for the system

1

01

3F8

H

000FFFF8

H

Reserved for the system

2

02

3F4

H

000FFFF4

H

Reserved for the system

3

03

3F0

H

000FFFF0

H

Reserved for the system

4

04

3EC

H

000FFFEC

H

Reserved for the system

5

05

3E8

H

000FFFE8

H

Reserved for the system

6

06

3E4

H

000FFFE4

H

Reserved for the system

7

07

3E0

H

000FFFE0

H

Reserved for the system

8

08

3DC

H

000FFFDC

H

Reserved for the system

9

09

3D8

H

000FFFD8

H

Reserved for the system

10

0A

3D4

H

000FFFD4

H

Reserved for the system

11

0B

3D0

H

000FFFD0

H

Reserved for the system

12

0C

3CC

H

000FFFCC

H

Reserved for the system

13

0D

3C8

H

000FFFC8

H

Undefined instruction exception

14

0E

3C4

H

000FFFC4

H

Reserved for the system

15

0F

3C0

H

000FFFC0

H

External interrupt 0

16

10

ICR00

3BC

H

000FFFBC

H

External interrupt 1

17

11

ICR01

3B8

H

000FFFB8

H

External interrupt 2

18

12

ICR02

3B4

H

000FFFB4

H

External interrupt 3

19

13

ICR03

3B0

H

000FFFB0

H

External interrupt 4

20

14

ICR04

3AC

H

000FFFAC

H

External interrupt 5

21

15

ICR05

3A8

H

000FFFA8

H

External interrupt 6

22

16

ICR06

3A4

H

000FFFA4

H

External interrupt 7

23

17

ICR07

3A0

H

000FFFA0

H

External interrupts 8 - 15

24

18

ICR08

39C

H

000FFF9C

H

Reserved for the system

25

19

398

H

000FFF98

H

UART0 (receiving complete)

26

1A

ICR10

394

H

000FFF94

H

UART1 (receiving complete)

27

1B

ICR11

390

H

000FFF90

H

UART2 (receiving complete)

28

1C

ICR12

38C

H

000FFF8C

H

UART3 (receiving complete)

29

1D

ICR13

388

H

000FFF88

H

Reserved for the system

30

1E

384

H

000FFF84

H

UART0 (sending complete)

31

1F

ICR15

380

H

000FFF80

H

UART1 (sending complete)

32

20

ICR16

37C

H

000FFF7C

H

UART2 (sending complete)

33

21

ICR17

378

H

000FFF78

H

MB91F155A/MB91155/MB91154

34

(Continued)

Factor

Interrupt No.

Interrupt

level

Offset

Default TBR

address

Decimal

Hex.

UART3 (sending complete)

34

22

ICR18

374

H

000FFF74

H

I

2

C

35

23

ICR19

370

H

000FFF70

H

DMAC (End, Error)

36

24

ICR20

36C

H

000FFF6C

H

Reload timer 0

37

25

ICR21

368

H

000FFF68

H

Reload timer 1

38

26

ICR22

364

H

000FFF64

H

Reload timer 2

39

27

ICR23

360

H

000FFF60

H

Reload timer 3

40

28

ICR24

35C

H

000FFF5C

H

A/D (sequential type)

42

2A

ICR26

354

H

000FFF54

H

PPG0

43

2B

ICR27

350

H

000FFF50

H

PPG1

44

2C

ICR28

34C

H

000FFF4C

H

PPG2

45

2D

ICR29

348

H

000FFF48

H

PPG3

46

2E

ICR30

344

H

000FFF44

H

PPG4

47

2F

ICR31

340

H

000FFF40

H

PPG5

48

30

ICR32

33C

H

000FFF3C

H

U/Dcounter 0

(compare/underflow, overflow, up-down

inversion)

49

31

ICR33

338

H

000FFF38

H

U/Dcounter 1

(compare/underflow, overflow, up-down

inversion

50

32

ICR34

334

H

000FFF34

H

ICU0 (Read)

51

33

ICR35

330

H

000FFF30

H

ICU1 (Read)

52

34

ICR36

32C

H

000FFF2C

H

ICU2 (Read)

53

35

ICR37

328

H

000FFF28

H

ICU3 (Read)

54

36

ICR38

324

H

000FFF24

H

OCU0 (Match)

55

37

ICR39

320

H

000FFF20

H

OCU1 (Match)

56

38

ICR40

31C

H

000FFF1C

H

OCU2 (Match)

57

39

ICR41

318

H

000FFF18

H

OCU3 (Match)

58

3A

ICR42

314

H

000FFF14

OCU4/5 (Match)

59

3B

ICR43

310

H

000FFF10

H

OCU6/7 (Match)

60

3C

ICR44

30C

H

000FFF0C

H

Reserved for the system

61

3D

308

H

000FFF08

H

16-bit free-run timer

62

3E

ICR46

304

H

000FFF04

H

Delay interrupt factor bit

63

3F

ICR47

300

H

000FFF00

H

MB91F155A/MB91155/MB91154

35

(Continued)

* : REALOS/FR uses 0X40 and 0X41 interrupts for system codes.

Factor

Interrupt No.

Interrupt

level

Offset

Default TBR

address

Decimal

Hex.

Reserved for the system

(used by REALOS*)

64

40

2FC

H

000FFEFC

H

Reserved for the system

(used by REALOS*)

65

41

2F8

H

000FFEF8

H

Reserved for the system

66

42

2F4

H

000FFEF4

H

Reserved for the system

67

43

2F0

H

000FFEF0

H

Reserved for the system

68

44

2EC

H

000FFEEC

H

Reserved for the system

69

45

2E8

H

000FFEE8

H

Reserved for the system

70

46

2E4

H

000FFEE4

H

Reserved for the system

71

47

2E0

H

000FFEE0

H

Reserved for the system

72

48

2DC

H

000FFEDC

H

Reserved for the system

73

49

2D8

H

000FFED8

H

Reserved for the system

74

4A

2D4

H

000FFED4

H

Reserved for the system

75

4B

2D0

H

000FFED0

H

Reserved for the system

76

4C

2CC

H

000FFECC

H

Reserved for the system

77

4D

2C8

H

000FFEC8

H

Reserved for the system

78

4E

2C4

H

000FFEC4

H

Reserved for the system

79

4F

2C0

H

000FFEC0

H

Used with the INT instruction

80

to

255

50

to

FF

2BC

H

to

000

H

000FFEBC

H

to

000FFC00

H

MB91F155A/MB91155/MB91154

36

s

s

s

s

PERIPHERAL RESOURCES

1.

I/O Port

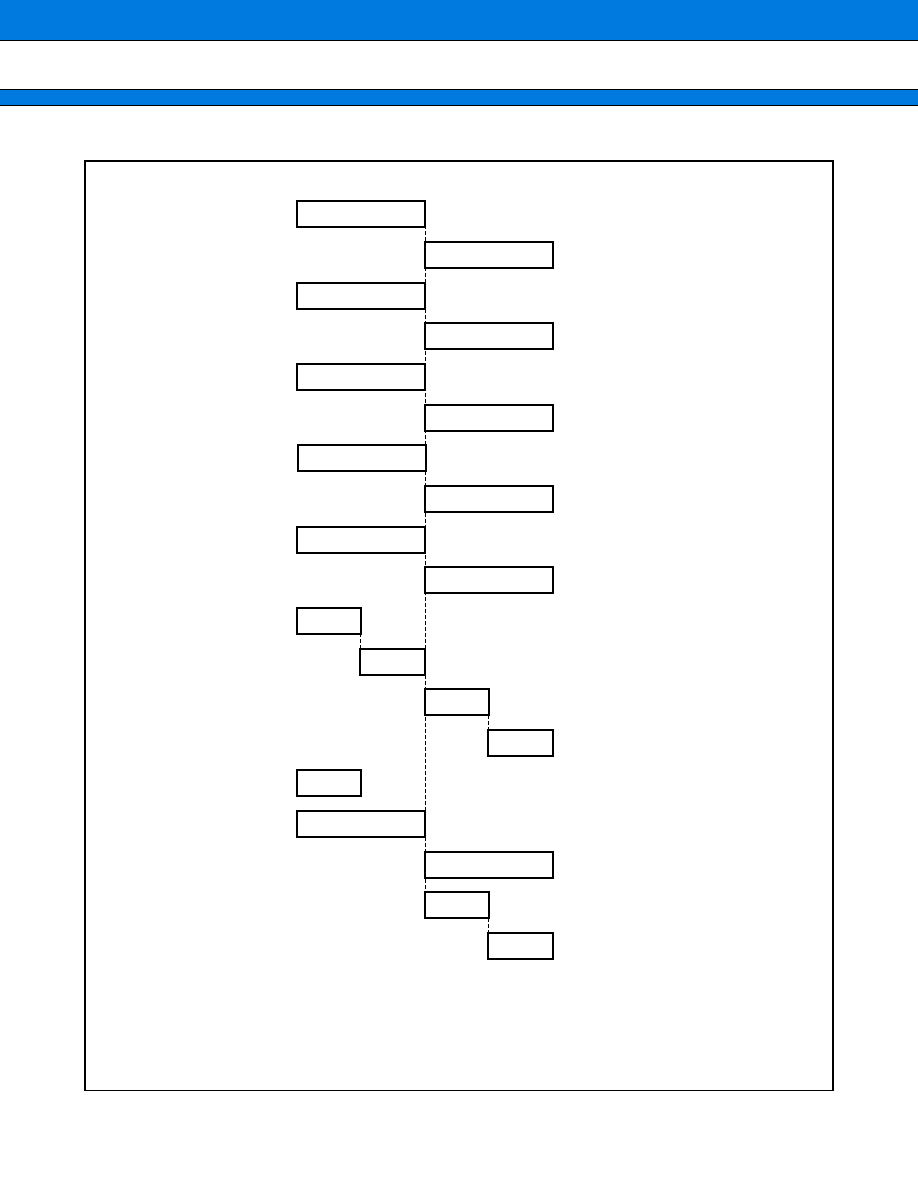

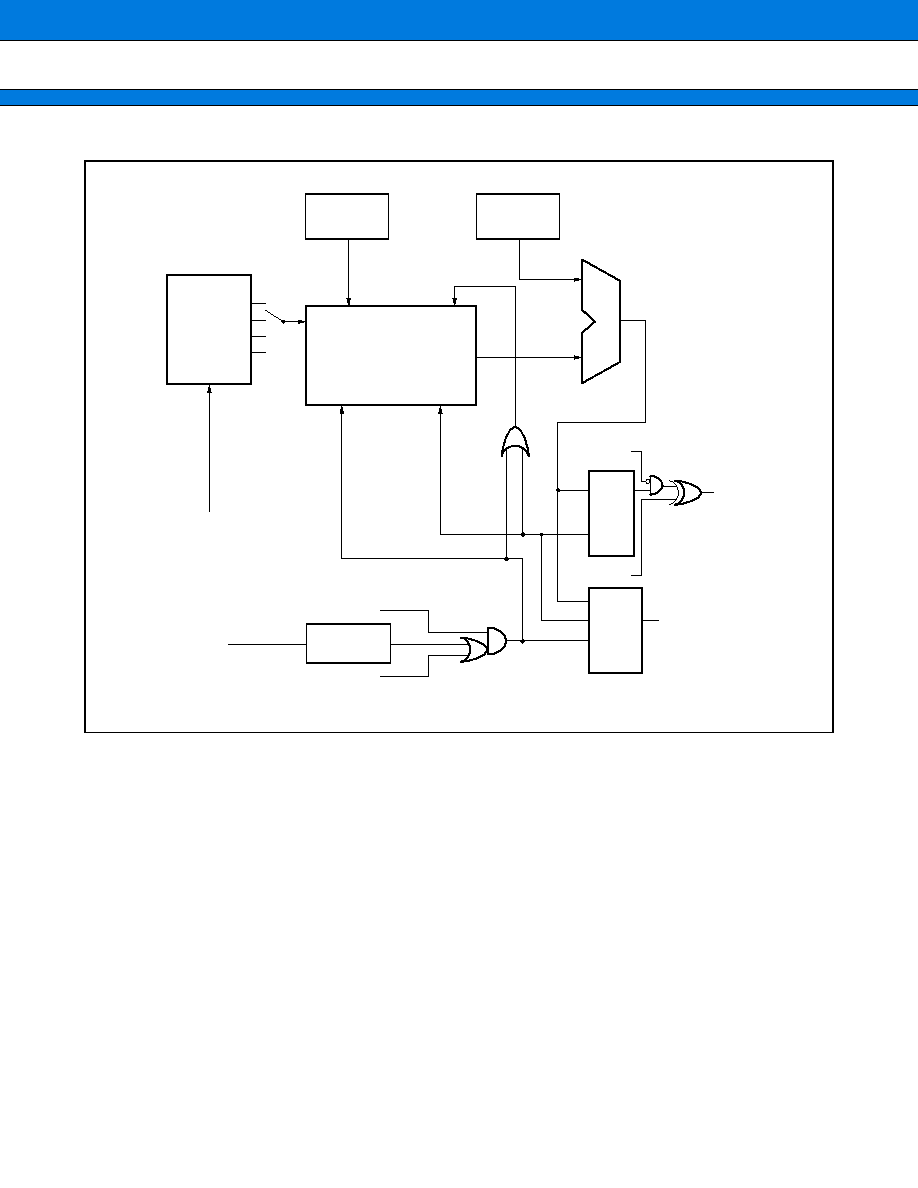

(1) Port Block Diagram

This LSI is available as an I/O port when the resource associated with each pin is set not to use a pin for input/

output.

The pin level is read from the port (PDR) when it is set for input. When the port is set for output, the value in the

data register is read. The same also applies to reload by read modify write.

When switching from input to output, output data is set in the data register beforehand. However, if a read modify

write instruction (such as bit set) is used at that time, keep in mind that it is the input data from the pin that is

read, not the latch value of the data register.

· Basic I/O Port

Figure PORT-1 Basic port block

The I/O port consists of the PDR (Port Data Register) and the DDR (Data Direction Register) .

Notes : AIC controls switching between the resource and port of the analog pin (A/D) .

AICK (Analog Input Control register on port-K)

The register controls whether port K should be used for analog input or as a general-purpose port.

0 : General-purpose port