aJ-80

TM

Real-time Low Power Java

TM

Processor

4/9/01

Page 1

Preliminary Data Sheet

Overview

The aJile Systems aJ-80 is a single-chip Java processor that powers networked smart sensors. aJile's

Java processor directly executes Java Virtual Machine

TM

(JVM) bytecodes, real-time Java threading

primitives and a number of extended bytecodes for embedded operations. The native JVM bytecode

implementation eliminates the typical interpreter or JIT software layers and provide the most optimal

Java performance in both memory requirements and execution time. In addition, Java threading prim-

itives (wait, yield, notify, monitor enter/exit) are implemented as extended bytecodes eliminating the

need for a the traditional RTOS. The result is extremely low executive overhead with thread to thread

context switch times of less than 1

µ

sec. The aJ-80 features on-chip memory and all the I/O functions

required for use in many real-time networked embedded applications. The powerful combination of di-

rect JVM bytecode execution, direct multithreading support, and fully protected multiple JVM environ-

ments is ideal for efficient, safe, and robust Java execution. The aJ-80 is ideally suited for real-time

networked smart sensors used in industrial control, automotive, home automation and consumer ap-

plications.

Features

JEM2 32-bit Direct Execution Java Processor

Core

·

Native JVM bytecode

·

Extended bytecodes for I/O and threading

support

·

IEEE-754 floating-point arithmetic

·

Writeable control store supports custom

extended bytecodes

Native Java Threading Support

·

Hard real-time, multi-threading kernel in

hardware

·

Threading operations are atomic including

true Java synchronization

·

Built-in deterministic scheduling queues

·

Directly supports the Real Time Specification

for Java (RTSJ)

·

Thread to thread yield in less than 1

µ

sec

·

Eliminates traditional RTOS layer

Multiple JVM Manager (MJM

TM

)

·

Support two independent JVM's

·

Brick wall time and space protection

·

Support external memory protection

Internal 48KB RAM

·

32KB dedicated data memory

·

16KB microcode memory

Memory Controller

·

8-bit interface

·

Six chip selects to support ROM, Flash,

SRAM, and peripheral devices

Dual 16550 compatible UARTs

·

128-byte FIFO on Rx and Tx

·

Support IrDA physical layer protocol

Three 16-bit Timers/Counters

·

Flexible count control and counter I/O

·

Pulse Width Modulation (PWM)

·

Waveform measurement

Serial Peripheral Interface (SPI)

·

Master/Slave operation

·

Four external chip selects

·

Programmable transfer length

General Purpose I/O Ports

·

Twenty-two I/O pins

·

I/O programmable on a per-bit basis

·

Flexible interrupt generation

Phase Locked Loop (PLL) and Power

Management

·

Transparent CPU power down when the "run

queue" is empty

·

Individual peripherals can be deactivated

when not in use

·

Global clock disable with external wake-up

pin

IEEE 1149.1 (JTAG) Interface

·

Boundary scan

·

Low-level debugger interface

·

JPDA Java Debugger Interface

Designed for ultra-low-power operation

·

Less than 1mW/MHz power consumption

·

Fully static operation up to 66 MHz

·

Implemented in 3.3V and 0.25

µ

m CMOS

process

·

Core operates at 2.5V

Housed in 100-lead QFP package

aJ-80

TM

Real-time Low Power Java

TM

Processor

4/9/01

Page 2

Preliminary Data Sheet

System Development Support

The aJ-80 processor, bundled with Sun's Java 2 Micro Edition (J2ME) Connected Limited Device Con-

figuration (CLDC) Java runtime system, optimizing application builder, debugging tools and evaluation

board provides a complete solution for implementing real-time networked embedded Java applica-

tions. Using commercial Java IDEs, application developers can create standalone real-time Java ap-

plications totally in Java with the performance and memory efficiency of systems programmed in C and

assembly.

An aJ-80 based system can be configured to execute in real-time and/or dynamic environments to sup-

port a wide range of applications. The dynamic runtime supports the CLDC Mobile Information Device

Profile (MIDP) to allow Java "MIDlets" to be downloaded and executed dynamically in separate JVM

environments. Multiple "MIDlets" can be run simultaneously under the control of the Java Applications

Manager (JAM) that maintains memory and execution time allocations. aJ-80 can also be configured

to execute both real-time and dynamic applications in deterministic time sliced schedule.

The primary components of the development and runtime environments are summarized as follows:

Optimizing Linker/Application Builder

·

GUI based application build configuration and control tool - JEM Builder

·

Utilizes standard JVM class files generated by commercial Java IDEs

·

Statically resolves class files and eliminates unused methods and fields

·

Performs bytecode optimizations

·

Performs method substitutions (method invokes replaced by extended bytecodes)

·

Builds boot tables, class initialization code, and assigns interrupt and trap handlers

·

Configures JVM's and memory layout

Java Runtime System

·

Java run-time environment based on a J2ME CLDC

·

Includes networking classes, storage classes, and Java communications API

·

Dynamic runtime includes the JAM (class loader, verifier, scheduler) and GC components

·

Device drivers for integrated peripherals and generic physical device interfacing in Java

Application Debugging Tools

·

Host-target communications via an IEEE 1149 (JTAG) interface using a simple inexpensive

IEEE-1284 cable

·

Host-based full featured low-level debugger - Charade (Target level debugger threads and

routines are not required)

·

Host-based JDI provided to interface to commercial JDI compliant source-level debuggers

aJ-80

TM

Real-time Low Power Java

TM

Processor

4/9/01

Page 4

Preliminary Data Sheet

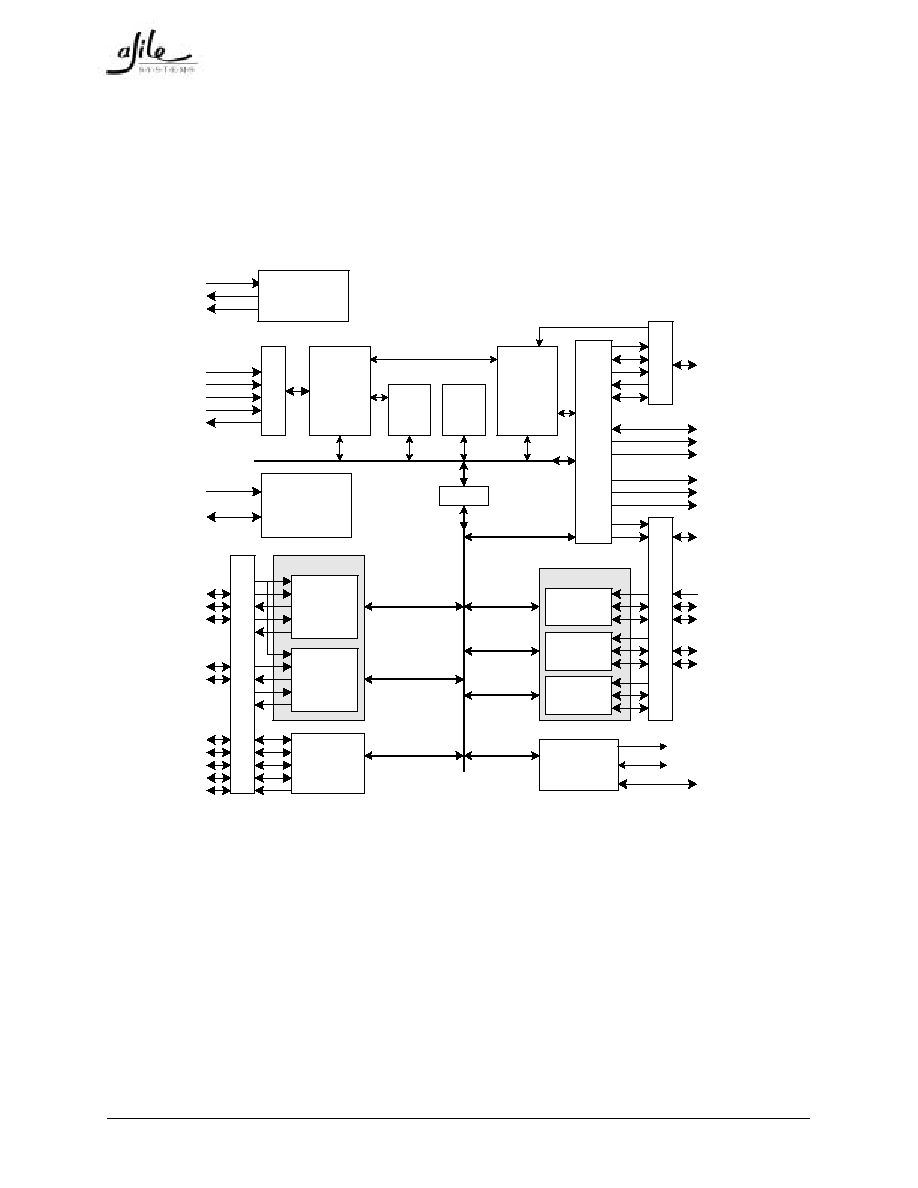

Figure 2: JEM2, Java Processing Core

Custom Instructions

The aJ-80 enables the use of custom microcode to implement new instructions. The new instructions

can significantly increase the performance of frequently used algorithms. The power of custom instruc-

tions is reflected in the threading instructions of the JEM2. For example, the yield instruction results in

a thread-to-thread switch of one microsecond while a typical RTOS written in a high level language that

may take several milliseconds.

For an example of where a custom instruction could be used consider the square root method in ja-

va.lang.Math. This method could be implemented with microcode and initiated via an instruction. When

processing a class file, the aJile tools will replace invokes of java.lang.Math.sqrt with the custom sqrt

instruction. The performance advantage of a custom instruction varies from 5X for simple algorithms

to 50X for complex algorithms.

Multiple JVM Manager (MJM)

The multiple JVM feature of the aJ-80 allows up to two independent Java applications to execute with

a deterministic, time-sliced schedule and with full memory protection. Within its bounded execution in-

terval and memory space, each JVM environment can employ its own multi-threading and memory uti-

lization policies without threat of intervention by faulty or malicious applications.

Processor

Bus

ADDRESS

Register

File

32-bit

ALU

Mux

Mux

Shifter

Shifter

Mux

Data Reg

Parser

Mux

Mux

Microinstruction Register

MicroPC

Stack

Vector

Test Interface

Instr. Reg

Put/Pull

ROM

Power

Management

DATA

ROM Control Store

ByteCodes

Floating Point

Debugger Control

RAM Control Store

Real-Time Kernel

Multiple JVM Control

Custom Instructions

Mux

JVM Interrupt

Timer Interrupts

Test Interrupts

Mux