1

* This specification are subject to be changed without notice.

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

8.16.2001

Preliminary

GENERAL DESCRIPTION

EM73A89B is an advanced single chip CMOS 4-bit micro-controller. It contains 16K-byte ROM, 1012-nibble

RAM, 4-bit ALU, 13-level subroutine nesting, 22-stage time base, two 12-bit timer/counters for the kernel

function, and one high speed conter. EM73A89B also equipped with 6 interrupt sources, 3~7 I/O ports (including

1 input port and 2~7 bidirection ports), LCD display (64x16 or 64x32), built-in watch-dog-timer and speech

synthesizer.

It's low power consumption and high speed feature are further strengten with DUAL, SLOW, IDLE and STOP

operation mode for optimized power saving.

FEATURES

Operation voltage

: 2.2V to 3.6V.

Clock source

: Dual clock system. Low-frequency oscillator is 32KHz. Crystal oscillator or RC

oscillator by mask option and high-frequency oscillator is a built-in internal

oscillator.

Instruction set

: 107 powerful instructions.

Instruction cycle time

: 0.85µs for 9.2M or 1.7µs for 4.6M Hz selected by mask option(high speed clock).

122µs for 32768 Hz (low speed clock, frequency double).

ROM capacity

: 16K x 8 bits.

RAM capacity

: 1012 x 4 bits.

Input port

: 1 port (P0.0-P0.3), IDLE/STOP releasing function is available by mask option.

(each input pin has a pull-up and pull-down resistor available by mask option).

Bidirection port

: 2~7 ports (P1, P2, P4, P5, P6, P7, P8). IDLE/STOP release function for P8(0..

3) is available by mask option. P1, P2, P5, P6, P7 are shared with LCD pins.

Built-in watch-dog-timer counter : It is available by mask option.

12-bit timer/counter

: Two 12-bit timer/counters are programmable for timer, event counter and pulse

width measurement mode.

Built-in time base counter : 22 stages.

Subroutine nesting

: Up to 13 levels.

Interrupt

: External interrupt . . . . . . 2 input interrupt sources.

Internal interrupt . . . . . . 2 timer overflow interrupts, 1 time base interrupt.

1 speech/HTC interrupt.

High speed counter

: The high speed counter includes one 8-bit high speed counter and a resistor to

frequency oscillator. It has resistor to frequrncy oscillation mode, melody mode

and auto load timer mode.

LCD driver

: 64x32 or 64x16 dots, 1/32 or 1/16 duty, 1/5 bias by mask option.

Speech synthesizer

: 992K speech data ROM (use as 992K nibbles data ROM).

PWM or current D/A

: Output selection by mask option.

Power saving function

: SLOW, IDLE, STOP operation modes.

Package type

: Chip form 126 pins.

2

* This specification are subject to be changed without notice.

8.16.2001

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

Preliminar

y

Symbol

Pin-type

Function

V

DD,

V

DD2

Power supply (+)

V

SS

Power supply (-)

RESET

RESET-A

System reset input signal, low active

mask option :

none

pull-up

CLK

OSC-G

Capacitor connecting pin for internal high frequency oscillator.

LXIN

OSC-B/OSC-H Crystal/Resistor connecting pin for low speed clock source.

LXOUT

OSC-B

Crystal connecting pin for low speed clock source.

P0(0..3)/WAKEUP0..3

INPUT-B

4-bit input port with IDLE/STOP releasing function

mask option :

wakeup enable, pull-up

wakeup enable, none

wakeup disable, pull-up

wakeup disable, pull-down

wakeup disable, none

P4.0(RX),P4.2(RY),

I/O-X1

3-bit bidirection I/O pins or RF oscillation input pins.

P4.3(RZ)

mask option :

open-drain (apply to RF oscillation)

high current push-pull

normal current push-pull

low current push-pull

P4.1

I/O-Q1

1-bit bidirection I/O pin.

mask option :

open-drain

high current push-pull

normal current push-pull

low current push-pull

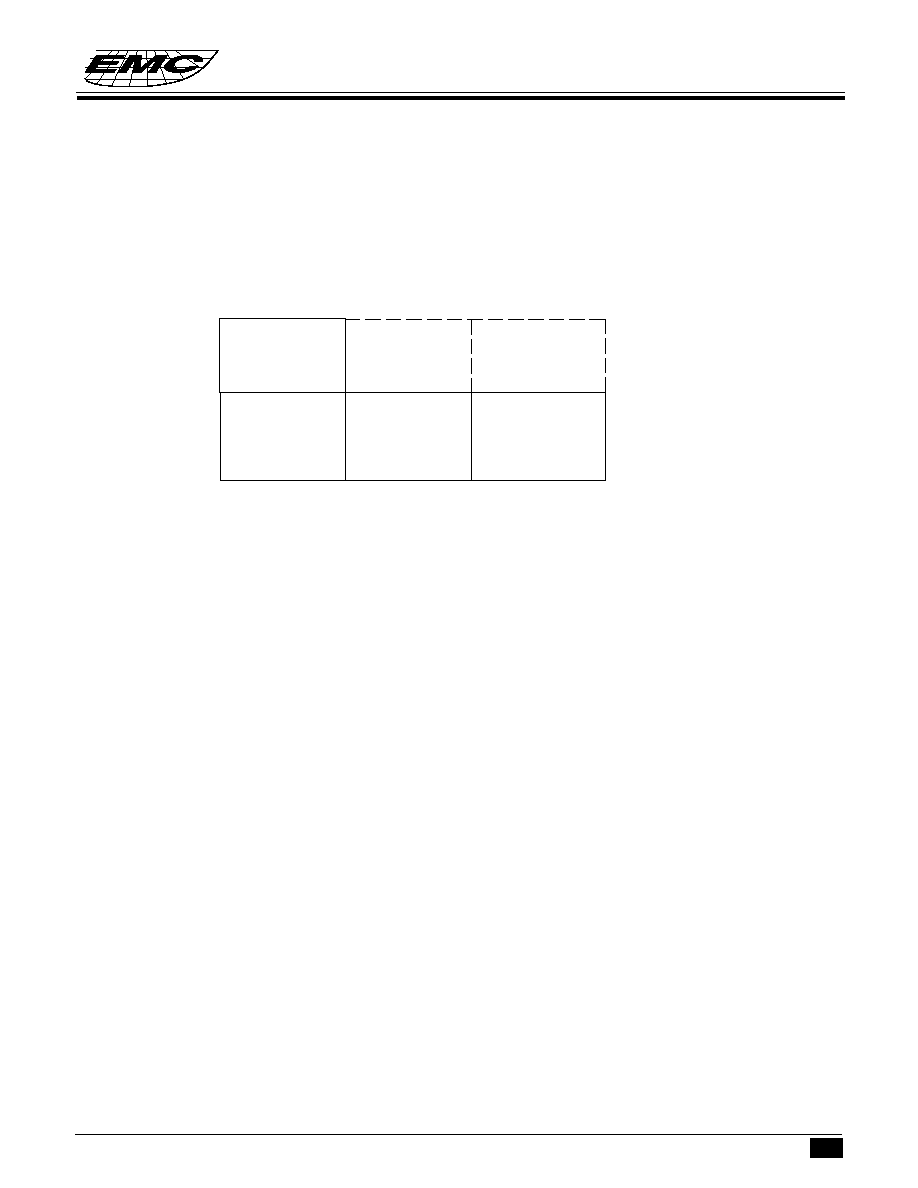

FUNCTION BLOCK DIAGRAM

PIN DESCRIPTIONS

Interrupt

Control

Time

Base

Timer/Counter

(TA,TB)

System Control

Instruction Decoder

Instruction Register

ROM

PC

Data Bus

Reset

Control

Clock

Generator

Timing

Generator

Clock Mode

Control

Data pointer

ACC

ALU

Flag

Z

C

S

Stack pointer

Stack

RAM

HR

LR

I/O Control

P0.0/WAKEUP0

P0.1/WAKEUP1

P0.2/WAKEUP2

P0.3/WAKEUP3

P8.0(INT1)/WAKEUPA

P8.1(TRGB)/WAKEUPB

P8.2(INT0)/WAKEUPC

P8.3(TRGA)/WAKEUPD

RESET

CLK

LXOUT

Speech

synthesizer

LCD Driver

LXIN

HTC

BZ1/VO

BZ2

P4.0(RX)

P4.1

P4.2(RY)

P4.3(RZ)

VC1~VC4,

VA,VB

VR1~VR4

P1/SESG60~63

P2,5,6,7/COM16~31

or SEG44~59

SEG0~43

COM0~15

3

* This specification are subject to be changed without notice.

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

8.16.2001

Preliminary

Symbol

Pin-type

Function

P8.0(INT1)/WAKEUPA I/O-X1

2-bit bidirection I/O port with external interrupt sources input and IDLE

P8.2(INT0)/WAKEUPC

/STOP releasing function

mask option :

wakeup enable, normal current push-pull

wakeup ensable, low current push-pull

wakeup disable, high current push-pull

wakeup disable, normal current push-pull

wakeup disable, low current push-pull

wakeup disable, open drain

P8.1(TRGB)/WAKEUPB I/O-X1

2-bit bidirection I/O port with time/counter A,B external input and IDLE

P8.3(TRGA)/WAKEUPD

/STOP releasing function

mask option :

wakeup enable, normal current push-pull

wakeup ensable, low current push-pull

wakeup disable, high current push-pull

wakeup disable, normal current push-pull

wakeup disable, low current push-pull

wakeup disable, open drain

VCA, VCB, V1~V6

LCD bias voltage pins

BZ1/VO

PWM or current D/A output pin for speech synthesizer by mask option

BZ2

PWM output pin for speech synthesizer

TEST

Tie Vss as package type, no connecting as COB type.

*16 COMMONS :

COM0~COM15

LCD common output pins

SEG0~SEG59

LCD segment output pins

P1(0..3)/SEG63..60

I/O-P

4-bit bidirection I/O pins with LCD segment pins

mask option :

LCD segment pin

push-pull

open-drain

P2(0..3),P5(0..3),

I/O-P

16-bit bidirection I/O pins

P6(0..3),P7(0..3)

mask option :

push-pull

open-drain

*32 COMMONS :

COM0~COM31

LCD common output pins

SEG0~SEG43

LCD segment output pins

P1(0..3)/SEG63..60,

I/O-P

16-bit bidirection I/O pins with LCD segment pins

P2(0..3)/SEG59..56,

mask option :

LCD segment pin

P5(0..3)/SEG55..52,

push-pull

P6(0..3)/SEG51..48,

open-drain

P7(0..3)/SEG47..44

4

* This specification are subject to be changed without notice.

8.16.2001

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

Preliminar

y

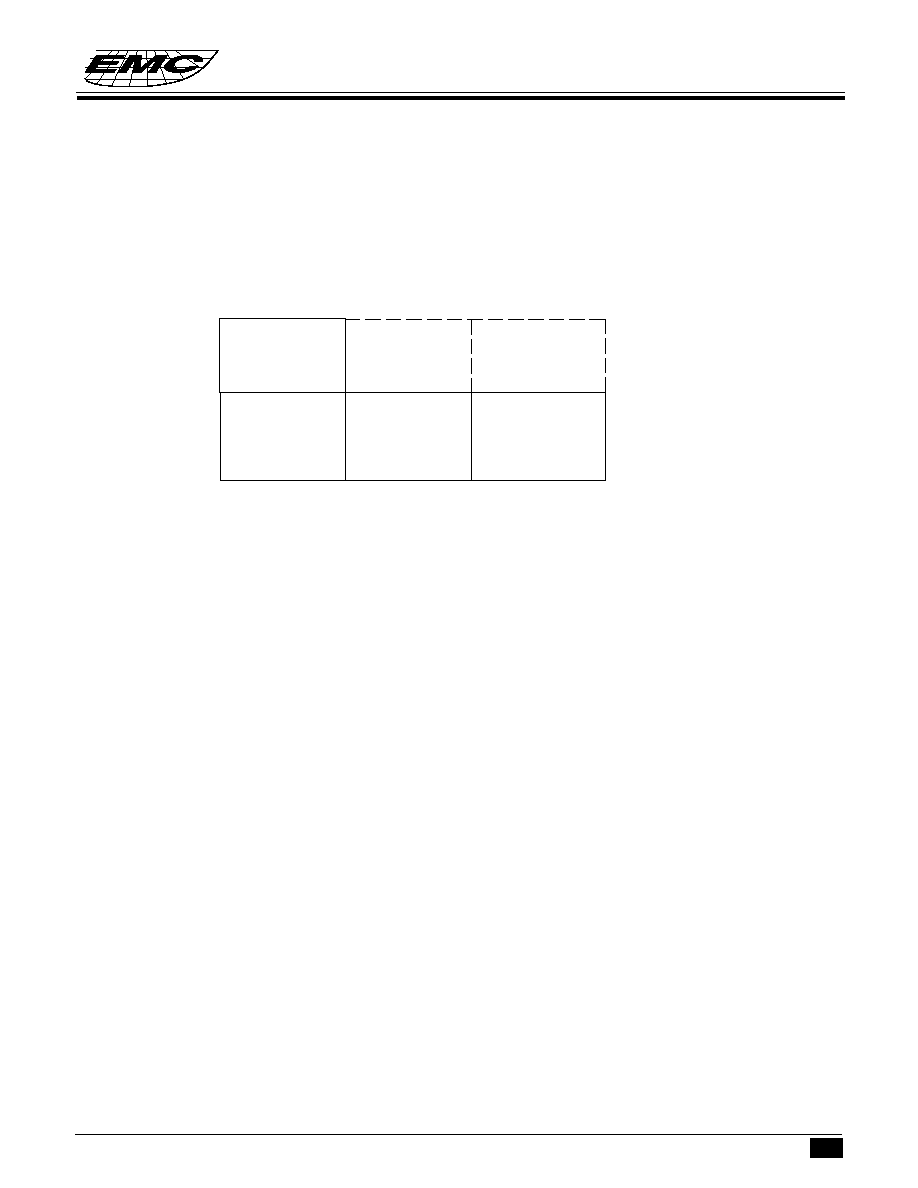

FUNCTION DESCRIPTIONS

PROGRAM ROM ( 16K X 8 bits )

16 K x 8 bits program ROM contains user's program and some fixed data.

The basic structure of the program ROM may be categorized into 5 partitions.

1. Address 0000h : Reset start address.

2. Address 0002h - 000Ch : 6 kinds of interrupt service routine entry addresses.

3. Address 000Eh - 0086h : SCALL subroutine entry address, only available at 000Eh, 0016h, 001Eh, 0026h, 002Eh,

0036h, 003Eh, 0046h, 004Eh, 0056h, 005Eh, 0066h, 006Eh, 0076h, 007Eh, 0086h.

4. Address 0000h - 07FFh : LCALL subroutine entry address.

5. Address 0000h - 1FFFh : Except used as above function, the other region can be used as user's program and

data region.

address Bank 0 :

.

.

.

SCALL, subroutine call entry address

Data table for

[LDAX],[LDAXI]

instruction

Subroutine call entry address

designated by [LCALL a]

instruction

Bank 1

Bank 2

Bank 3

Reset start address

INT0 ; interrupt service routine entry address

TRGA

TRGB

TBI

INT1

0000h

0002h

0004h

0006h

0008h

000Ah

000Ch

000Eh

0086h

07FFh

0800h

0FFFh

1000h

1FFFh

SPI or HTCI

5

* This specification are subject to be changed without notice.

EM73A89B

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

8.16.2001

Preliminary

User's program and fixed data are stored in the program ROM. User's program is executed using the PC value

to fetch an instruction code.

The 16Kx8 bits program ROM can be divided into 4 banks. There are 4Kx8 bits per bank.

The program ROM bank is selected by P3(1..0). The program counter is a 13-bit binary counter. The PC and

P3 are initialized to "0" during reset.

When P3(1..0)=00B or 11B, the bank0 and bank1 of program ROM will be selected. P3(1..0)=01B, the bank0

and bank2 will be selected. P3(1..0)=10B, the bank0 and bank3 will be selected.

P3=xx00B

Address

P3=xx11B

P3=xx01B

P3=xx10B

0000h

:

:

Bank0

Bank0

Bank0

0FFFh

1000h

:

:

Bank1

Bank2

Bank3

1FFFh

PROGRAM EXAMPLE:

BANK 0

START:

:

:

:

LDIA #00H

; set program ROM to bank1

OUTA P3

B

XA1

:

XA :

:

:

LDIA #01H

; set program ROM to bank2

OUTA P3

B

XB1

:

XB :

:

:

LDIA #02H

; set program ROM to bank3

OUTA P3

B

XC1

:

XC :

:

:

B

XD

XD :

:

:

:

; - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

BANK 1

XA1 :

:

:

B

XA

:

XA2 :

: