USE ULTRA37000TM FOR

ALL NEW DESIGNS

64-Macrocell MAX

®

EPLD

CY7C343

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

,

CA 95134

·

408-943-2600

Document #: 38-03015 Rev. *B

Revised April 22, 2004

Features

· 64 MAX

®

macrocells in four LABs

· Eightdedicated inputs, 24 bidirectional I/O pins

· Programmable interconnect array

· 0.8-micron double-metal CMOS EPROM technology

· Available in 44-pin HLCC, PLCC

· Lowest power MAX device

Functional Description

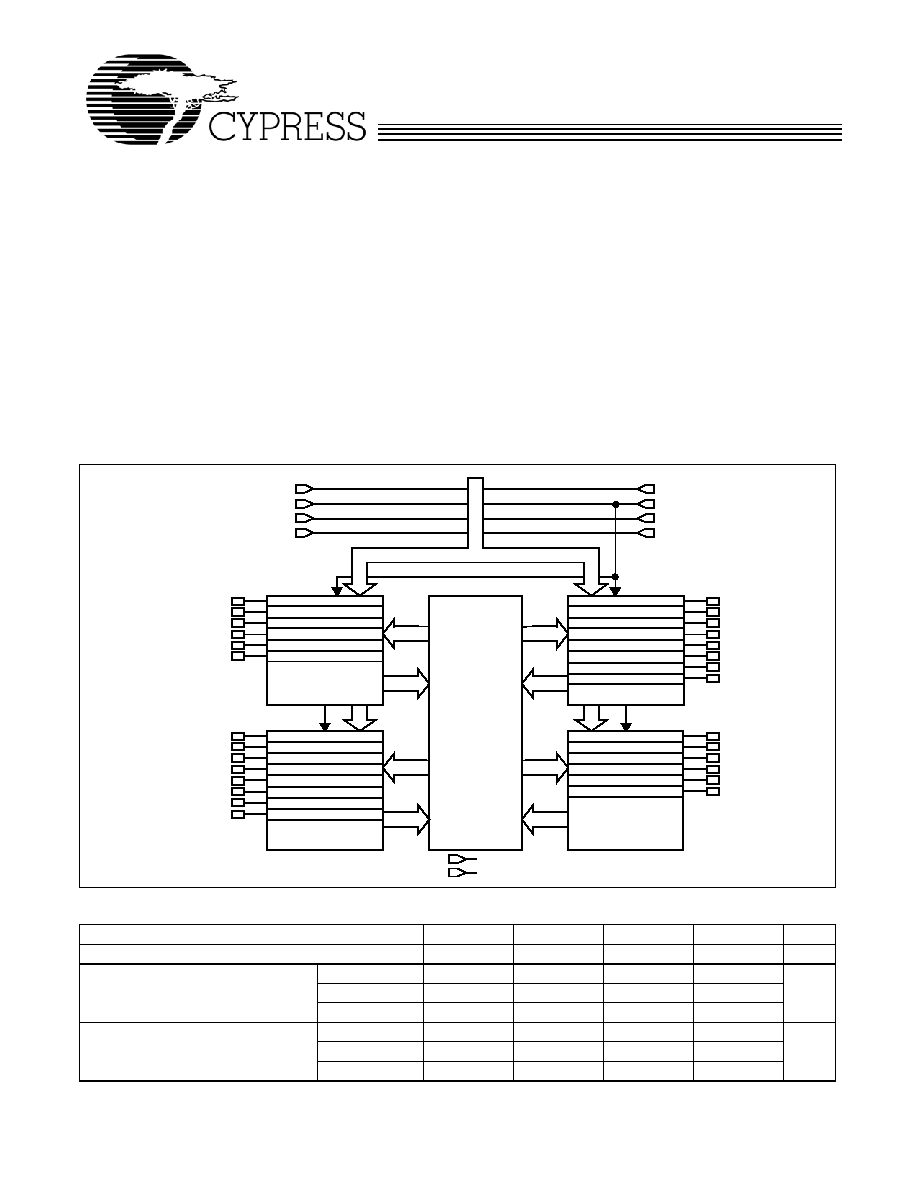

The CY7C343 is a high-performance, high-density erasable

programmable logic device, available in 44-pin PLCC and

HLCC packages.

The CY7C343 contains 64 highly flexible macrocells and 128

expander product terms. These resources are divided into four

Logic Array Blocks (LABs) connected through the Program-

mable Inter-connect Array (PIA). There are eight input pins,

one that doubles as a clock pin when needed. The CY7C343

also has 28 I/O pins, each connected to a macrocell (six for

LABs A and C, and eight for LABs B and D). The remaining 36

macrocells are used for embedded logic.

The CY7C343 is excellent for a wide range of both

synchronous and asynchronous applications.

MACROCELL 17

MACROCELL 18

MACROCELL 19

MACROCELL 20

MACROCELL 21

MACROCELL 22

MACROCELL 23

MACROCELL 24

MACROCELL 38

MACROCELL 37

MACROCELL 36

MACROCELL 35

MACROCELL 34

MACROCELL 33

9 INPUT

11 INPUT

12 INPUT

13 INPUT

P

I

A

MACROCELL1

MACROCELL2

MACROCELL3

MACROCELL4

MACROCELL5

MACROCELL6

MACROCELL 56

MACROCELL 55

MACROCELL 54

MACROCELL 53

MACROCELL 52

MACROCELL 51

MACROCELL 50

MACROCELL 49

MACROCELLS 716

MACROCELLS 5764

MACROCELLS 2532

MACROCELLS 3948

INPUT 35

INPUT/CLK 34

INPUT 33

INPUT 31

2

4

5

6

7

8

1

44

42

41

40

39

38

37

30

29

28

27

26

24

SYSTEM CLOCK

(3, 14, 25, 36)

(10, 21, 32, 43)

V

CC

GND

LAB A

LAB B

LAB D

LAB C

Logic Block Diagram

DEDICATED INPUTS

I/O PINS

15

16

17

18

19

20

22

23

I/O PINS

I/O PINS

I/O PINS

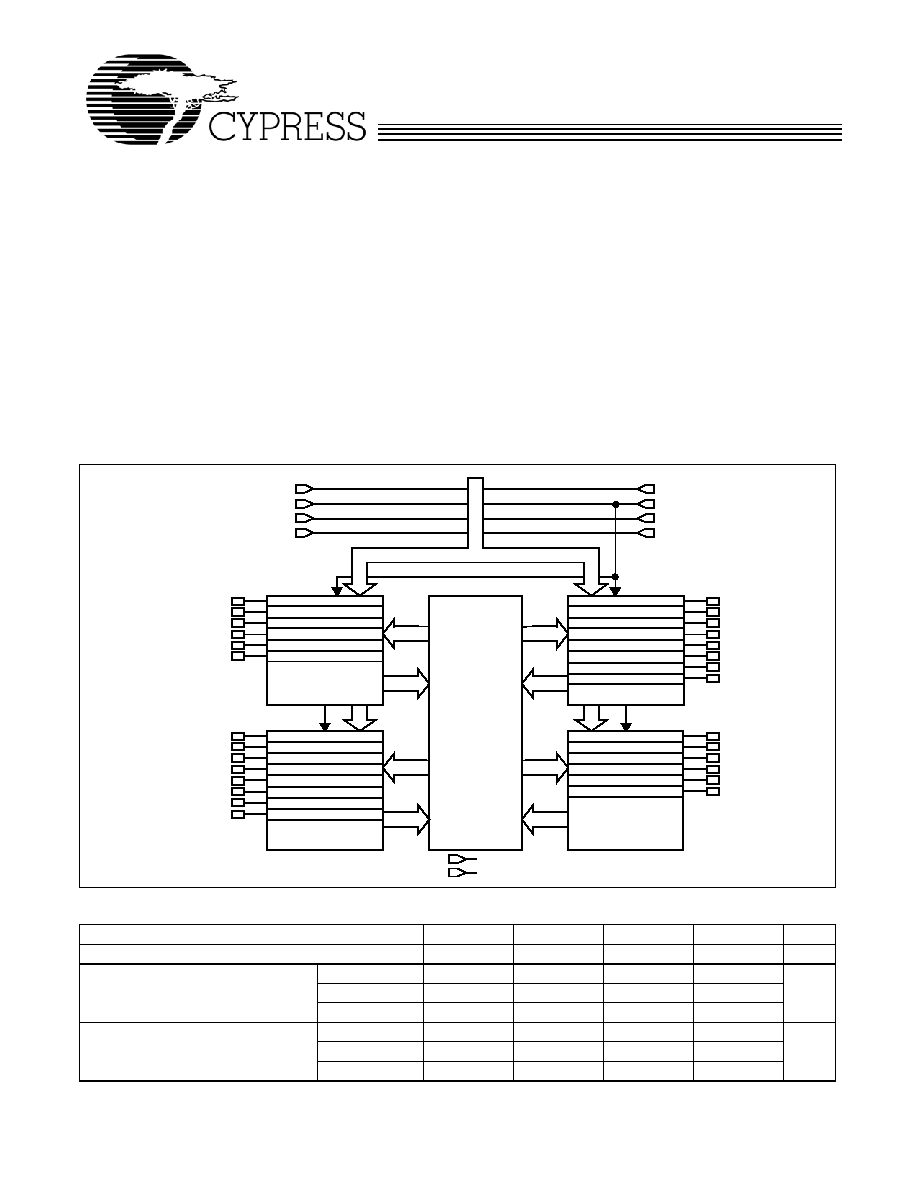

Selection Guide

7C343-20

7C343-25

7C343-30

7C343-35

Unit

Maximum Access Time

20

25

30

35

ns

Maximum Operating Current

Commercial

135

135

135

135

mA

Military

225

225

225

225

Industrial

225

225

225

225

Maximum Standby Current

Commercial

125

125

125

125

mA

Military

200

200

200

200

Industrial

200

200

200

200

USE ULTRA37000TM FOR

ALL NEW DESIGNS

CY7C343

Document #: 38-03015 Rev. *B

Page 3 of 19

Programmable Interconnect Array

The Programmable Interconnect Array (PIA) solves inter-

connect limitations by routing only the signals needed by each

logic array block. The inputs to the PIA are the outputs of every

macrocell within the device and the I/O pin feedback of every

pin on the device.

Unlike masked or programmable gate arrays, which induce

variable delay dependent on routing, the PIA has a fixed delay.

This eliminates undesired skews among logic signals, which

may cause glitches in internal or external logic. The fixed

delay, regardless of programmable interconnect array config-

uration, simplifies design by ensuring that internal signal

skews or races are avoided. The result is simpler design imple-

mentation, often in a single pass, without the multiple internal

logic placement and routing iterations required for a program-

mable gate array to achieve design timing objectives.

Timing Delays

Timing delays within the CY7C343 may be easily determined

using Warp

®

, Warp ProfessionalTM, or Warp EnterpriseTM

software. The CY7C343 has fixed internal delays, allowing the

user to determine the worst case timing delays for any design.

Design Recommendations

Operation of the devices described herein with conditions

above those listed under "Maximum Ratings" may cause

permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other

conditions above those indicated in the operational sections of

this data sheet is not implied. Exposure to absolute maximum

ratings conditions for extended periods of time may affect

device reliability. The CY7C343 contains circuitry to protect

device pins from high static voltages or electric fields;

however, normal precautions should be taken to avoid

applying any voltage higher than maximum rated voltages.

For proper operation, input and output pins must be

constrained to the range GND < (V

IN

or V

OUT

) < V

CC

. Unused

inputs must always be tied to an appropriate logic level (either

V

CC

or GND). Each set of V

CC

and GND pins must be

connected together directly at the device. Power supply

decoupling capacitors of at least 0.2

µ

F must be connected

between V

CC

and GND. For the most effective decoupling,

each V

CC

pin should be separately decoupled to GND, directly

at the device. Decoupling capacitors should have good

frequency response, such as monolithic ceramic types.

Timing Considerations

Unless otherwise stated, propagation delays do not include

expanders. When using expanders, add the maximum

expander delay t

EXP

to the overall delay. Similarly, there is an

additional t

PIA

delay for an input from an I/O pin when

compared to a signal from a straight input pin.

When calculating synchronous frequencies, use t

S1

if all inputs

are on the input pins. t

S2

should be used if data is applied at

an I/O pin. If t

S2

is greater than t

CO1

, 1/t

S2

becomes the limiting

frequency in the data path mode unless 1/(t

WH

+ t

WL

) is less

than 1/t

S2

.

When expander logic is used in the data path, add the appro-

priate maximum expander delay, t

EXP

to t

S1

. Determine which

of 1/(t

WH

+ t

WL

), 1/t

CO1

, or 1/(t

EXP

+ t

S1

) is the lowest

frequency. The lowest of these frequencies is the maximum

data path frequency for the synchronous configuration.

When calculating external asynchronous frequencies, use

t

AS1

if all inputs are on dedicated input pins. If any data is

applied to an I/O pin, t

AS2

must be used as the required set-up

time. If (t

AS2

+ t

AH

) is greater than t

ACO1

, 1/(t

AS2

+ t

AH

)

becomes the limiting frequency in the data path mode unless

1/(t

AWH

+ t

AH

) is less than 1/(t

AS2

+ t

AH

).

When expander logic is used in the data path, add the appro-

priate maximum expander delay, t

EXP

to t

AS1

. Determine

which of 1/(t

AWH

+ t

AWL

), 1/t

ACO1

, or 1/(t

EXP

+ t

AS1

) is the

lowest frequency. The lowest of these frequencies is the

maximum data path frequency for the asynchronous configu-

ration.

The parameter t

OH

indicates the system compatibility of this

device when driving other synchronous logic with positive

input hold times, which is controlled by the same synchronous

clock. If t

OH

is greater than the minimum required input hold

time of the subsequent synchronous logic, then the devices

are guaranteed to function properly with a common

synchronous clock under worst-case environmental and

supply voltage conditions.

The parameter t

AOH

indicates the system compatibility of this

device when driving subsequent registered logic with a

positive hold time and using the same clock as the CY7C343.

In general, if t

AOH

is greater than the minimum required input

hold time of the subsequent logic (synchronous or

asynchronous), then the devices are guaranteed to function

properly under worst-case environmental and supply voltage

conditions, provided the clock signal source is the same. This

also applies if expander logic is used in the clock signal path

of the driving device, but not for the driven device. This is due

to the expander logic in the second device's clock signal path

adding an additional delay (t

EXP

), causing the output data from

the preceding device to change prior to the arrival of the clock

signal at the following device's register.

USE ULTRA37000TM FOR

ALL NEW DESIGNS

CY7C343

Document #: 38-03015 Rev. *B

Page 5 of 19

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature ................................ 65

°

C to +150

°

C

Ambient Temperature with

Power Applied.................................................. 0

°

C to +70

°

C

Maximum Junction Temperature

(Under Bias).................................................................150

°

C

Supply Voltage to Ground Potential ...............2.0V to +7.0V

Maximum Power Dissipation...................................2500 mW

DC V

CC

or GND Current ............................................500 mA

DC Output Current, per Pin ......................25 mA to +25 mA

DC Input Voltage

[1]

.........................................3.0V to +7.0V

DC Program Voltage..................................................... 13.0V

Static Discharge Voltage........................................... > 1100V

(per MILSTD883, method 3015)

Notes:

1. Minimum DC input is 0.3V. During transitions, the inputs may undershoot to 2.0V for periods less than 20 ns.

2. The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

3. Typical values are for T

A

= 25°C and V

CC

= 5V.

4. Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V

OUT

= 0.5V has been chosen to avoid

test problems caused by tester ground degradation.

5. Guaranteed but not 100% tested.

6. Measured with device programmed as a 16-bit counter in each LAB. This parameter is tested periodically by sampling production material.

7. Part (a) in AC Test Load and Waveforms is used for all parameters except t

ER

and t

XZ

, which is used for part (b) in AC Test Load and Waveforms. All external

timing parameters are measured referenced to external pins of the device.

Operating Range

[2]

Range

Ambient Temperature

V

CC

Commercial

0

°

C to +70

°

C 5V

±

5%

Industrial

40

°

C to +85

°

C 5V

±

10%

Military

55

°

C to +125

°

C (Case)

5V

±

10%

Electrical Characteristics

Over the Operating Range

[3]

Parameter

Description

Test Conditions

Min.

Max.

Unit

V

OH

Output HIGH Voltage

V

CC

= Min., I

OH

= 4.0 mA

2.4

V

V

OL

Output LOW Voltage

V

CC

= Min., I

OL

= 8 mA

0.45

V

V

IH

Input HIGH Level

2.2

V

CC

+ 0.3

V

V

IL

Input LOW Level

0.3

0.8

V

I

IX

Input Current

GND < V

IN

< V

CC

10

+10

µ

A

I

OZ

Output Leakage Current

V

O

= V

CC

or GND

40

+40

µ

A

I

OS

Output Short Circuit Current

V

CC

= Max., V

OUT

= 0.5V

[4, 5]

30

90

mA

I

CC1

Power Supply Current (Standby)

V

I

= V

CC

or GND

(No Load)

Commercial

125

mA

Military/Industrial

200

mA

I

CC2

Power Supply Current

[6]

V

I

= V

CC

or GND (No

Load) f = 1.0 MHz

[5, 6]

Commercial

135

mA

Military/Industrial

225

mA

t

R

Recommended Input Rise Time

100

ns

t

F

Recommended Input Fall Time

100

ns

Capacitance

[7]

Parameter

Description

Test Conditions

Max.

Unit

C

IN

Input Capacitance

V

IN

= 2V, f = 1.0 MHz

10

pF

C

OUT

Output Capacitance

V

OUT

= 2.0V, f = 1.0 MHz

10

pF

AC Test Loads and Waveforms

[7]

3.0V

5V

OUTPUT

R1 464

R2

250

50 pF

INCLUDING

JIG AND

SCOPE

GND

90%

10%

90%

10%

< 6 ns

< 6 ns

5V

OUTPUT

R1 464

R2

250

5 pF

INCLUDING

JIG AND

SCOPE

(a)

(b)

OUTPUT

1.75V

Equivalent to:

THÉ VENIN EQUIVALENT (commercial/military)

ALL INPUT PULSES

163