Preliminary Data Sheet

August 2001

TAAD08JU2 Newport

T1/E1/J1/J2 ATM Processor

1 Features

s

System-on-a-chip integrated circuit supports low-

speed ATM access for next-generation wireless

base transmission station (BTS), base station con-

troller BSC), and remote access concentrator

(RAC) applications.

s

IC provides an integrated octal framer that sup-

ports T1/E1/J1/J2 formats.

s

Supports inverse multiplexing for ATM (IMA) over

selected group and link mappings ranging from

four two-link groups up to one eight-link group per

ATM Forum AF-PHY-0086.001.

s

Integrates an ATM adaptation layer 2 (AAL2) seg-

mentation and reassembly (SAR) function for sup-

port of low-speed data or voice traffic per ITU

I.363.2.

s

Provides AAL5 SAR functionality per ITU I.363.5.

s

Provides quality of service (QoS) connection iden-

tifier (CID) multiplexing per ITU I.366.1.

s

Enables ATM layer user network interface (UNI) or

IMA mode, selectable on a per-link basis for flexi-

ble transport of delay critical voice and data traffic.

s

Guarantees QoS for a variety of traffic types

(including delay-sensitive voice, real-time data,

non-real-time data, and signaling information)

through an advanced hierarchical three-level prior-

ity scheduler and per-VC queueing.

s

Supports 2047 AAL2 CIDs.

s

Supports 2048 high-speed data connections or vir-

tual circuits (VCs) via embedded context memory;

filters control cells and accepts control cells via a

host microprocessor interface.

s

Software package includes the following:

-- Software device manager source code (C-

based device manager ready-to-use with host

RTOS) and firmware for embedded controller

(executable binary).

-- User manual available for device manager soft-

ware.

s

Designed in 0.16 Ąm, low-power CMOS technol-

ogy.

2 Physical

s

3.3 V digital I/O compatibility; 1.5 V core power

s

520 enhanced ball-grid array (EBGA) package

s

Ł40

o

C to +85

o

C temperature range

3 Standards

ITU I.363.2

ITU I.366.1

ITU I.363.5

ITU I.432

ITU I.361

ITU I.371

ITU G.703

ITU G.704

ITU G.804

ITU G.732

ITU G.706

ITU I.610

ITU G.775

ITU G.733

ITU G.735

ITU G.965

ITU O.162

ANSI* T1.403

ANSI T1.231

ATM Forum af-phy-0086.001

ATM Forum af-phy-0029.000

ATM Forum af-phy-0039.000

ATM Forum Traffic Management 4.1

ETS 300.417-1-1

TR-NWT-000170

* ANSI is a registered trademark of American National Standards

Institute, Inc.

Table of Contents

2

Agere Systems Inc.

Preliminary Data Sheet

August 2001

T1/E1/J1/J2 ATM Processor

TAAD08JU2 Newport

Contents

Page

1

Features...........................................................................................................................................................1

2

Physical ...........................................................................................................................................................1

3

Standards ........................................................................................................................................................1

4

Description.....................................................................................................................................................16

5

Pin Definitions................................................................................................................................................17

6

Pin Description...............................................................................................................................................17

7

Package Pin Layout.......................................................................................................................................25

8

Block Diagram ...............................................................................................................................................31

9

Functional Overview ......................................................................................................................................32

9.1

Receive Direction Data Flow................................................................................................................32

9.1.1

PHY Layer...............................................................................................................................32

9.1.2

Low-Speed PHY Links ............................................................................................................32

9.1.3

Medium-Speed PHY Links ......................................................................................................33

9.1.4

High-Speed PHY Links ...........................................................................................................33

9.1.5

TC and IMA Layers .................................................................................................................33

9.1.6

ATM Layer...............................................................................................................................34

9.1.7

AAL Engine .............................................................................................................................34

9.1.8

Embedded Device Controller ..................................................................................................35

9.2

Transmit Direction Data Flow...............................................................................................................35

9.2.1

SSCS/AAL Layer Interaction...................................................................................................35

9.2.2

ATM Layer...............................................................................................................................35

9.2.3

IMA/TC Layer ..........................................................................................................................36

9.2.4

PHY Layer...............................................................................................................................36

10 Modes of Operation .......................................................................................................................................37

10.1 Interface Modes ...................................................................................................................................37

10.1.1 UTOPIA-2 Expansion Port Multiplexing Modes ......................................................................37

10.1.2 System Interface Port Multiplexing Modes..............................................................................38

10.1.3 Line Interface Modes...............................................................................................................38

10.2 Device Operating Modes......................................................................................................................38

10.2.1 Operating Mode 1: Internal Framer Mode...............................................................................39

10.2.2 Operating Mode 2: External PHY/TC Mode ............................................................................41

10.2.3 Operating Mode 3: SAR Slave Mode ......................................................................................42

10.2.4 Operating Mode Summary ......................................................................................................42

11 Applications ...................................................................................................................................................43

11.1 BTS Network Interface Termination .....................................................................................................43

11.2 VToA Trunking Application...................................................................................................................46

11.3 Low-Speed ATM Access......................................................................................................................47

11.4 AAL2 Crossconnect .............................................................................................................................47

12 Submodule Functional Description ................................................................................................................48

12.1 Embedded Device Controller (EDC) ....................................................................................................48

12.1.1 Introduction .............................................................................................................................48

12.1.2 Features ..................................................................................................................................48

12.1.3 EDC Functional Description ....................................................................................................48

12.1.4 Host Interface..........................................................................................................................48

12.1.5 Host Interface Signals and Timing ..........................................................................................49

12.1.6 Host Interactions .....................................................................................................................50

13 Framer Block .................................................................................................................................................53

13.1 Introduction ..........................................................................................................................................53

13.2 Features ...............................................................................................................................................53

13.3 Framer-to-Line Interface Unit Physical Interface..................................................................................54

13.3.1 Clocking Modes.......................................................................................................................54

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

Agere Systems Inc.

Lucent Technologies--Proprietary

3

Use pursuant to Company instructions

13.4 Frame Formats.....................................................................................................................................55

13.5 Transmit Framer Functions ..................................................................................................................56

13.6 DS1 Transparent Framing Format .......................................................................................................56

13.7 CEPT 2.048 Basic Frame Structure Transparent Framing Format......................................................57

13.8 Receive Framer Nonalignment Mode (DS1/E1)...................................................................................58

13.9 Loss of Frame Alignment Criteria.........................................................................................................58

13.9.1 Frame Bit Errors......................................................................................................................58

13.9.2 CRC Errors..............................................................................................................................58

13.10 Frame Alignment Criteria .....................................................................................................................58

13.11 Performance Monitoring Functional Integration Into Framer................................................................59

13.12 Performance Report Message .............................................................................................................62

13.13 ESF Data Link ......................................................................................................................................64

13.14 Facility Data Link..................................................................................................................................64

13.15 Receive Data Link Functional Description ...........................................................................................64

13.16 SLC-96 Superframe Receive Data Link ...............................................................................................65

13.17 DDS Receive Data Link Stack .............................................................................................................65

13.18 CEPT; CEPT CRC-4 (100 ms); CEPT CRC-4 (400 ms) Multiframe Sa Bits Receive Stack................65

13.19 Receive Data Link Stack Idle Modes ...................................................................................................65

13.20 Transmit Facility Data Link Functional Description ..............................................................................66

13.21 SLC-96 Superframe Transmit Data Link ..............................................................................................66

13.22 DDS Transmit Data Link Stack ............................................................................................................66

13.23 Transmit ESF Data Link Bit-Oriented Messages .................................................................................66

13.24 CEPT, CEPT Multiframe Transmit Data Link Sa Bits Stack.................................................................67

13.25 Transmit Data Link Stack Idle Modes ..................................................................................................68

13.26 SLC-96, DDS, or CEPT ESF Frame Alignment ...................................................................................68

13.27 Concentration Highway Interface (CHI) ...............................................................................................68

13.28 Transmit/Receive System Interface Features ......................................................................................68

13.29 Double NOTFAS System Time-Slot Mode...........................................................................................69

13.30 Transparent Mode................................................................................................................................69

13.31 Loopbacks............................................................................................................................................69

13.32 Nominal CHI Timing .............................................................................................................................70

13.33 CHI Timing with CHI Double Time-Slot Timing (CHIDTS) Mode Enabled ...........................................71

13.34 Clocking Scheme .................................................................................................................................71

14 Transmission Convergence (TC) Block .........................................................................................................72

14.1 Introduction ..........................................................................................................................................72

14.2 Features ...............................................................................................................................................72

14.3 TC--Receive Direction.........................................................................................................................73

14.4 TC--Transmit Direction........................................................................................................................73

14.4.1 HEC Generation/Checking......................................................................................................74

14.5 Cell Delineation ....................................................................................................................................74

14.6 Cell Payload Scrambling/Descrambling ...............................................................................................74

14.7 Cell Mapping ........................................................................................................................................74

14.8 Facility Maintenance ............................................................................................................................74

14.9 Cell Rate Decoupling ...........................................................................................................................74

14.10 Functionality .........................................................................................................................................75

15 Inverse Multiplexing for ATM (IMA) Block......................................................................................................76

15.1 Introduction ..........................................................................................................................................76

15.2 Features ...............................................................................................................................................77

15.3 Multi-PHY UTOPIA Slave Interface......................................................................................................78

15.4 Link Processor .....................................................................................................................................78

15.5 Group Processor ..................................................................................................................................79

15.6 Delay Compensation Buffer (DCB) ......................................................................................................80

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

4

Lucent Technologies--Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

15.7 Programming the DCB .........................................................................................................................87

15.7.1 Link Startup Guardband Field .................................................................................................87

15.7.2 Link Maximum Operational Delay ...........................................................................................87

15.8 Features Not Supported in IMA............................................................................................................87

16 ATM Port Controller (APC) Block ..................................................................................................................89

16.1 Introduction ..........................................................................................................................................89

16.2 Architecture ..........................................................................................................................................90

16.3 Features ...............................................................................................................................................91

16.4 Summary of Commands ......................................................................................................................92

16.5 Buffer Management..............................................................................................................................92

16.6 Scheduling ...........................................................................................................................................94

16.6.1 Ingress Scheduling..................................................................................................................94

16.6.2 Fabric Backpressure ...............................................................................................................95

16.6.3 Egress Scheduling ..................................................................................................................95

16.7 ABR Flow Control.................................................................................................................................95

16.8 Control Plane Functions.......................................................................................................................96

16.8.1 APC Support for Control Plane Functions...............................................................................96

16.9 Management Plane Functions .............................................................................................................96

16.9.1 Operation Administration and Maintenance (OAM) ................................................................96

16.10 Statistics Counters ...............................................................................................................................97

16.11 Ingress Enqueue Operations ...............................................................................................................97

16.11.1 Connection Look Up................................................................................................................98

16.11.2 OAM Processing .....................................................................................................................99

16.11.3 Policing....................................................................................................................................99

16.11.4 Buffer Thresholding...............................................................................................................100

16.11.5 Egress--APC VC Queueing Structure..................................................................................100

16.12 Connection Management ...................................................................................................................100

16.12.1 Connection Admission Control..............................................................................................100

16.12.1.1 CBR ......................................................................................................................100

16.12.1.2 rt-VBR ...................................................................................................................101

16.12.1.3 nrt-VBR .................................................................................................................101

16.12.1.4 ABR.......................................................................................................................101

16.12.1.5 UBR ......................................................................................................................101

17 ATM Adaption Layer (AAL) Block ................................................................................................................102

17.1 Introduction ........................................................................................................................................102

17.2 Features .............................................................................................................................................102

17.3 Definitions ..........................................................................................................................................104

17.4 Architecture ........................................................................................................................................105

17.4.1 Datapath Flows .....................................................................................................................105

17.4.2 Subblock Architecture ...........................................................................................................107

17.4.3 Subblock Definition ...............................................................................................................109

17.4.4 Subblock Flows .....................................................................................................................109

17.4.5 Address Translation ..............................................................................................................110

17.4.6 Queueing and Scheduling.....................................................................................................111

17.4.7 Modes ...................................................................................................................................111

17.4.8 User Data Types (UDT) and AAL Types...............................................................................111

17.4.9 UDT: ATM Cell ......................................................................................................................113

17.4.10 AAL Type: AAL0....................................................................................................................113

17.4.11 AAL Type: AAL2....................................................................................................................113

17.4.12 AAL2 Subtype: SPAAL2 (Single-Packet AAL2) ....................................................................114

17.4.13 CPS-AAL0.............................................................................................................................114

17.4.14 AAL Type: AAL5....................................................................................................................115

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

Agere Systems Inc.

Lucent Technologies--Proprietary

5

Use pursuant to Company instructions

17.4.15 UDT: Packet ATM (PATM)....................................................................................................115

17.4.16 UDT: HPF..............................................................................................................................116

17.4.17 AAL Type: NPAAL (No Particular AAL).................................................................................118

17.4.18 Nonuser Data Types: ESI Messages ....................................................................................118

17.4.18.1 ESI Message Format ............................................................................................118

17.4.18.2 ESI Violation Code................................................................................................119

17.4.18.3 ESI Packet Length ................................................................................................119

17.4.19 Service Types .......................................................................................................................119

17.4.20 CPS_SERVICE .....................................................................................................................120

17.4.21 SEG_AAL2_SSSAR_SERVICE............................................................................................121

17.4.22 SEG_AAL2_SSTED_SERVICE ............................................................................................121

17.4.23 SEG_AAL5_SERVICE ..........................................................................................................122

17.4.24 TRANSPARENT_SERVICE..................................................................................................122

17.4.25 REASS_AAL2_SSSAR_SERVICE .......................................................................................122

17.4.26 REASS_AAL2_SSTED_SERVICE .......................................................................................122

17.4.27 REASS_AAL5_SERVICE .....................................................................................................123

17.5 Provisioning........................................................................................................................................124

17.5.1 Some Notes on Terminology and Command Referencing....................................................124

17.5.2 System Interface ...................................................................................................................124

17.5.3 Port Table..............................................................................................................................125

17.5.4 MEMI Shared Memory ..........................................................................................................126

17.5.4.1 MEMI-SM Provisioning Constraints ......................................................................126

17.5.4.2 VC Table ...............................................................................................................127

17.5.4.3 AAL2 VC Table .....................................................................................................128

17.5.4.4 Connection Table..................................................................................................129

17.5.4.5 Level 0 Queue Descriptor .....................................................................................130

17.5.4.6 ICID Table.............................................................................................................131

17.5.5 SQASE Shared Memory .......................................................................................................131

17.6 Configuration......................................................................................................................................132

17.6.1 Connection and Channel Setup ............................................................................................132

17.6.1.1 AAL2 Data Flow (CPS/SSSAR/SSTED) ...............................................................134

17.6.1.2 CPS-AAL0 Data Flow ...........................................................................................135

17.6.1.3 AAL0/AAL5 Data Flow ..........................................................................................135

17.6.1.4 HPF Data Flow......................................................................................................135

17.6.2 Configuration for QoS ...........................................................................................................136

17.6.2.1 Packet Scheduling ................................................................................................136

17.6.2.2 IL1Q Scheduler Algorithm.....................................................................................136

17.6.3 Configuration for QoS ...........................................................................................................137

17.6.3.1 IL2Q Scheduler Algorithm.....................................................................................137

17.6.3.2 Latency Policing....................................................................................................137

17.6.3.3 Latency Sensitive Data Discard ............................................................................138

17.6.3.4 Internal Queue Housekeeping ..............................................................................138

17.6.3.5 Reference Clock Generation.................................................................................138

17.6.3.6 Latency Timer Enable/Disable Functions .............................................................139

17.6.3.7 Queue Length Policing..........................................................................................139

17.6.3.8 Connection Queue Length Policing ......................................................................139

17.6.3.9 Intra-Level 1 Queue and Level 1 Queue Length Policing .....................................140

17.6.3.10 Intra-Level 2 Queue Length Policing.....................................................................141

17.6.4 Configuration for Exceptions .................................................................................................142

17.7 Interface Timing Diagrams .................................................................................................................145

17.7.1 SIF UT2/UT2+ Interface ........................................................................................................145

17.7.2 Polling Algorithms For UTOPIA 2 and UT2+ Modes .............................................................153

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

6

Lucent Technologies--Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

17.7.2.1 Receive Interface Polling ......................................................................................153

17.7.2.2 Transmit Interface Polling .....................................................................................154

17.7.3 NIF ........................................................................................................................................155

17.7.4 ESI ........................................................................................................................................155

18 Firmware Flows ...........................................................................................................................................156

18.1 Software Architecture Overview.........................................................................................................156

18.2 Provisioning........................................................................................................................................157

18.2.1 PHY Layer Provisioning ........................................................................................................157

18.2.2 Link Provisioning ...................................................................................................................159

18.2.3 Connection Provisioning .......................................................................................................161

18.2.4 AAL2 Provisioning.................................................................................................................161

18.2.5 System Interface Provisioning...............................................................................................161

18.3 Operation ...........................................................................................................................................161

18.3.1 Management Plane Interaction via External Host .................................................................163

18.3.2 Provisioning of AAL2 Connection..........................................................................................163

18.4 Alarm Generation and Reporting .......................................................................................................164

18.4.1 Layer 1 (PHY) .......................................................................................................................166

18.4.2 ATMF Specifications .............................................................................................................166

18.4.3 E1/ATMF ...............................................................................................................................167

18.4.4 Layer 2 (TC) ..........................................................................................................................167

18.4.5 Layer 3 (ATM) .......................................................................................................................168

18.4.6 Layer 4 (AAL) ........................................................................................................................168

19 Embedded Device Controller (EDC) Firmware............................................................................................169

19.1 Firmware Architecture ........................................................................................................................170

19.2 Reset and Booting..............................................................................................................................171

19.3 Initialization ........................................................................................................................................171

20 Commands and Indications .........................................................................................................................172

21 Commands ..................................................................................................................................................172

21.1 Command Register Structure.............................................................................................................172

21.1.1 Command Sequences...........................................................................................................175

21.2 Global Commands .............................................................................................................................176

21.2.1 NPT_CMD_ECHO Command...............................................................................................176

21.2.2 NPT_ENABLE_PROCESSING Command ...........................................................................176

21.2.3 NPT_GLBCLK_RATE Command..........................................................................................176

21.3 PHY Layer Commands ......................................................................................................................176

21.3.1 NPT_PHY_CONFIG_GLOBALS Command .........................................................................177

21.3.2 NPT_PHY_CONFIG_LINK Command ..................................................................................184

21.3.3 NPT_PHY_ADD_LINK Command ........................................................................................191

21.3.4 NPT_PHY_DELETE_LINK Command ..................................................................................192

21.3.5 NPT_PHY_FRAMER__TEST_LINK Command....................................................................193

21.3.6 NPT_PHY_SEND_ALARMS Command ...............................................................................194

21.3.7 NPT_PHY_FRAMER_LOOPBACK Command .....................................................................194

21.3.8 NPT_PHY_CHI_LOOPBACK Command ..............................................................................195

21.3.9 NPT_PHY_IMA_CONFIG_GROUP Command ....................................................................196

21.3.10 NPT_PHY_IMA_DELETE_GROUP Command ....................................................................198

21.3.11 NPT_PHY_IMA_INHIBIT_LINK Command...........................................................................198

21.3.12 NPT_PHY_IMA_INHIBIT_GROUP Command......................................................................198

21.3.13 NPT_PHY_IMA_TEST_LINK Command ..............................................................................198

21.3.14 NPT_PHY_SET_STATS Command .....................................................................................199

21.3.15 NPT_PHY_SINGLE_STATS Command ...............................................................................199

21.3.16 NPT_PHY_GET_STATE.......................................................................................................199

21.3.17 NPT_PHY_READ_REG........................................................................................................200

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

Agere Systems Inc.

Lucent Technologies--Proprietary

7

Use pursuant to Company instructions

21.3.18 NPT_PHY_SET_LINK_ALARMS Command ........................................................................200

21.3.19 NPT_PHY_SET_GROUP_ALARMS Command ...................................................................202

21.3.20 NPT_PHY_FRAMER_BOM Command.................................................................................203

21.3.21 NPT_PHY_FRAMER_DL_THRESHOLDS Command..........................................................203

21.3.22 NPT_PHY_FRAMER_AUTOPRM Command.......................................................................204

21.3.23 NPT_PHY_FRAMER_DATA_LINK_MSG Command ...........................................................205

21.3.24 NPT_PHY_FRAMER_FDL_STACK Command ....................................................................205

21.4 ATM Layer Commands ......................................................................................................................207

21.4.1 APC Modes ...........................................................................................................................207

21.4.2 ATM Connection Tags ..........................................................................................................207

21.4.3 Calculation of Connection Buffer and Bandwidth Parameters ..............................................207

21.4.4 ATM Scheduling....................................................................................................................209

21.4.5 ATM-Layer OAM ...................................................................................................................212

21.4.6 APC Connection Defect States .............................................................................................215

21.4.7 NPT_ATM_INIT Command ...................................................................................................215

21.4.8 NPT_ATM_SCHED_INIT# Commands.................................................................................221

21.4.9 NPT_ATM_SCHED_CONFIG Command .............................................................................222

21.4.10 NPT_ATM_SET_ALARM_MASK Command ........................................................................224

21.4.11 NPT_ATM_SET_STATS_MASK Command .........................................................................224

21.4.12 NPT_ATM_ADD_CONN Command......................................................................................232

21.4.13 NPT_ATM_DELETE_UNI_CONN Command .......................................................................238

21.4.14 NPT_ATM_DELETE_BI_CONN Command..........................................................................239

21.4.15 NPT_ATM_SET_CONN_STATS Command.........................................................................241

21.4.16 NPT_ATM_SET_CONN_FAULT_STATE Command ...........................................................241

21.4.17 NPT_ATM_SET_CONN_OAM_CC Command.....................................................................242

21.4.18 NPT_ATM_ENABLE_CONN_OAM_PM Command .............................................................243

21.4.19 NPT_ATM_DISABLE_CONN_OAM_PM Command ............................................................243

21.4.20 NPT_ATM_INSERT_CELLS Command ...............................................................................244

21.4.21 NPT_ATM_GET_STATS Command.....................................................................................245

21.4.22 NPT_ATM_READ_APC Command ......................................................................................245

21.4.23 NPT_ATM_READ_DRAM Command ...................................................................................246

21.5 ATM Adaptation Layer Commands ....................................................................................................248

21.5.1 NPT_AAL_ADAPBLK_MEM_ALLC Command.....................................................................249

21.5.1.1 VC Table ...............................................................................................................249

21.5.1.2 AAL2 VC Table .....................................................................................................249

21.5.1.3 Connection Table..................................................................................................249

21.5.1.4 Level 0 Descriptors ...............................................................................................249

21.5.2 NPT_AAL_FREE_LIST_ALLC Command ............................................................................250

21.5.3 NPT_AAL_NIF_FREE_LIST_ALLC Command.....................................................................250

21.5.4 NPT_AAL_SIF_TRANSMIT_CONFIG Command.................................................................251

21.5.5 NPT_AAL_SIF_RECEIVE_CONFIG Command ...................................................................252

21.5.6 NPT_AAL_SIF_RECEIVE_PORT_CONTROL Command....................................................252

21.5.7 NPT_AAL_NIF_TRANSMIT_CONFIG Command ................................................................252

21.5.8 NPT_AAL_NIF_TRANSMIT_PORT_CONTROL Command.................................................253

21.5.9 NPT_AAL_NIF_RECEIVE_CONFIG Command ...................................................................254

21.5.10 NPT_AAL_SERVICE_COUNT Command ............................................................................254

21.5.11 NPT_AAL_CONN_QUE_LEN_POL Command ....................................................................254

21.5.12 NPT_AAL_QUE_LEN_POL_TAB Command........................................................................255

21.5.13 NPT_AAL_IL2_QUE_SHARE Command .............................................................................255

21.5.14 NPT_AAL_IL2_QUE_PRIVATE Command ..........................................................................256

21.5.15 NPT_AAL_L1_QUE_QOS Command...................................................................................257

21.5.16 NPT_AAL_IL1_QUE_POL_SCHED Command ....................................................................258

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

8

Lucent Technologies--Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

21.5.17 NPT_AAL_IDU_SDU_TABLE Command .............................................................................258

21.5.18 NPT_AAL_ADD_CONN Command ......................................................................................259

21.5.19 NPT_AAL_ADD_CHANNEL Command................................................................................262

21.5.20 NPT_AAL_RAS_TIMER Command ......................................................................................264

21.5.21 NPT_AAL_ENABLE Command ............................................................................................264

21.5.22 NPT_ AAL_DELETE_CHANNEL Command ........................................................................265

21.5.23 NPT_ AAL_DELETE_CONN Command ...............................................................................265

21.5.24 NPT_AAL_SET_STAT_MODE Command............................................................................267

21.5.25 NPT_AAL_SET_CONNCHAN_STATS Command ...............................................................267

21.5.26 NPT_AAL_ADD_STAT Command........................................................................................267

21.5.27 Block Exception Code ...........................................................................................................269

21.5.28 NPT_AAL_FREE_STAT Command......................................................................................271

21.5.29 NPT_AAL_GET_STAT Command ........................................................................................271

21.5.30 NPT_AAL_REPORT_ALL_STATS Command......................................................................272

21.5.31 NPT_AAL_INSERT_ALARMS Command.............................................................................272

21.5.32 NPT_AAL_INSERT_PACKETS Command...........................................................................273

22 Indications....................................................................................................................................................274

22.1 Indication Register Structure..............................................................................................................274

22.2 Indications of the Command-Complete Type.....................................................................................275

22.2.1 Global Command-Complete Indications ...............................................................................276

22.2.1.1 NPT_GLB_CLK_RATE_ERR Indication ...............................................................276

22.2.2 PHY Layer Command-Complete Indications ........................................................................276

22.2.3 ATM-Layer Command-Complete Indications ........................................................................283

22.3 Indications of the Data Type ..............................................................................................................290

22.3.1 Data Indications from the PHY Layer....................................................................................290

22.3.1.1 NPT_PHY_BOM_RCVD Indication.......................................................................290

22.3.1.2 NPT_PHY_BOM_SENT Indication .......................................................................291

22.3.1.3 NPT_PHY_FRAMER_DATA_LINK_RCVD Indication ..........................................291

22.3.1.4 NPT_PHY_FRAMER_DATA_LINK_SENT Indication...........................................292

22.3.1.5 NPT_PHY_FRAMER_FDL_STACK_RCVD Indication.........................................293

22.3.1.6 NPT_PHY_FRAMER_FDL_STACK_SENT Indication .........................................293

22.3.2 Data Indications from the ATM Layer....................................................................................293

22.3.2.1 NPT_ATM_DATA Indication .................................................................................296

22.3.3 Data Indications from the ATM Adaption Layer ....................................................................296

22.4 Indications of the Statistics Type........................................................................................................297

22.4.1 Statistics Indications from the PHY Layer .............................................................................297

22.4.2 Statistics Indications from the ATM Layer: Per-Connection Statistics ..................................301

22.4.2.1 NPT_ATM_CONN_STATS Indication...................................................................301

22.4.3 Statistics Indications from the ATM Layer: Global Statistics .................................................301

22.4.4 Statistics Indications from AAL Layer....................................................................................302

22.4.4.1 NPT_AAL_FLOW_STATS Indication....................................................................303

22.4.4.2 NPT_AAL_AAL2VC_STATS Indication ................................................................303

22.4.4.3 NPT_AAL_PROG_STATS Indication ...................................................................304

22.4.5 Indications of the Global Alarm Type ....................................................................................304

22.4.6 Alarm Indication from the Global Layer.................................................................................304

22.4.6.1 NPT_GLB_RDY Indication....................................................................................305

22.4.6.2 NPT_POLLING_TIMER Indication........................................................................305

22.4.7 Indications of the Alarm Type, Excluding Global Alarms ......................................................306

22.4.8 Alarm Indications from the PHY Layer ..................................................................................306

22.4.9 PHY Link Alarms ...................................................................................................................306

22.4.9.1 NPY_PHY_IMA_GROUP_ALARMS.....................................................................310

22.4.10 Alarm Indications from the AAL Layer...................................................................................310

Table of Contents

(continued)

Contents

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

Agere Systems Inc.

Lucent Technologies--Proprietary

9

Use pursuant to Company instructions

23 Absolute Maximum Ratings .........................................................................................................................311

24 Power Requirements ...................................................................................................................................311

25 Handling Precautions...................................................................................................................................311

26 Electrical Characteristics .............................................................................................................................312

26.1 Logical Interface Electrical Characteristics ........................................................................................312

27 Timing Characteristics .................................................................................................................................312

27.1 Input Clocks .......................................................................................................................................312

27.2 Host Interface Timing .........................................................................................................................313

27.3 Reset Timing ......................................................................................................................................315

27.4 Concentration Highway (CHI) Timing.................................................................................................316

27.5 Fabric Interface--Ports A and B ........................................................................................................317

27.6 Expansion UTOPIA2 Interface ...........................................................................................................318

27.6.1 Receive Interface Timing ......................................................................................................318

27.6.2 Transmit Interface Timing .....................................................................................................318

27.7 Enhanced Services Interface (ESI) ....................................................................................................319

27.8 JTAG ..................................................................................................................................................319

27.9 System Interface ................................................................................................................................319

27.9.1 Receive Interface Timing ......................................................................................................319

27.9.2 Transmit Interface Timing .....................................................................................................320

28 Referenced Documents ...............................................................................................................................321

29 Glossary.......................................................................................................................................................323

List of Figures

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

Figures

Page

10

Agere Systems Inc.

Figure 1.

Pin Configuration Diagram ................................................................................................................25

Figure 2.

Architecture of the Newport Device ...................................................................................................31

Figure 3.

Newport Interfaces ............................................................................................................................37

Figure 4.

Mode 1: Internal Framer Mode Operation .........................................................................................39

Figure 5.

Example of Sharing Span Line with TDM and ATM data ..................................................................40

Figure 6.

Mode 2: External PHY/TC Mode .......................................................................................................41

Figure 7.

Mode 3: SAR Slave Mode .................................................................................................................42

Figure 8.

BTS Application .................................................................................................................................43

Figure 9.

IMA Application..................................................................................................................................44

Figure 10. BTSs Require ADM Functions...........................................................................................................45

Figure 11. Gateway Controller............................................................................................................................45

Figure 12. Remote Access Concentrator Application .........................................................................................46

Figure 13. Edge/Access Switch Application .......................................................................................................46

Figure 14. AAL2 Cross-Connect.........................................................................................................................47

Figure 15. Stand-Alone AAL2 Cross-Connect ....................................................................................................47

Figure 16. Standard Host Interface Timing.........................................................................................................49

Figure 17. DS1 Transparent Frame Structure ....................................................................................................57

Figure 18. CEPT Transparent Frame Structure..................................................................................................57

Figure 19. System Loopbacks ............................................................................................................................69

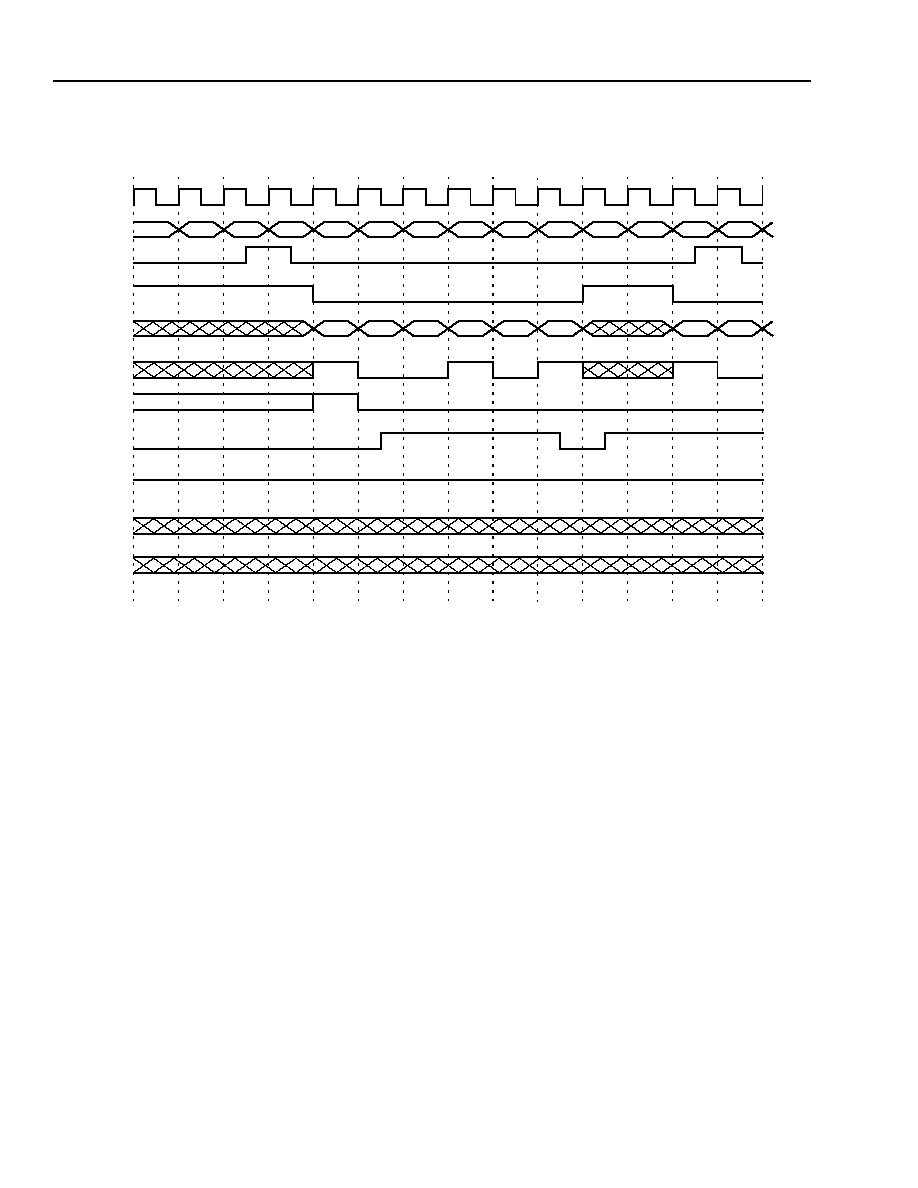

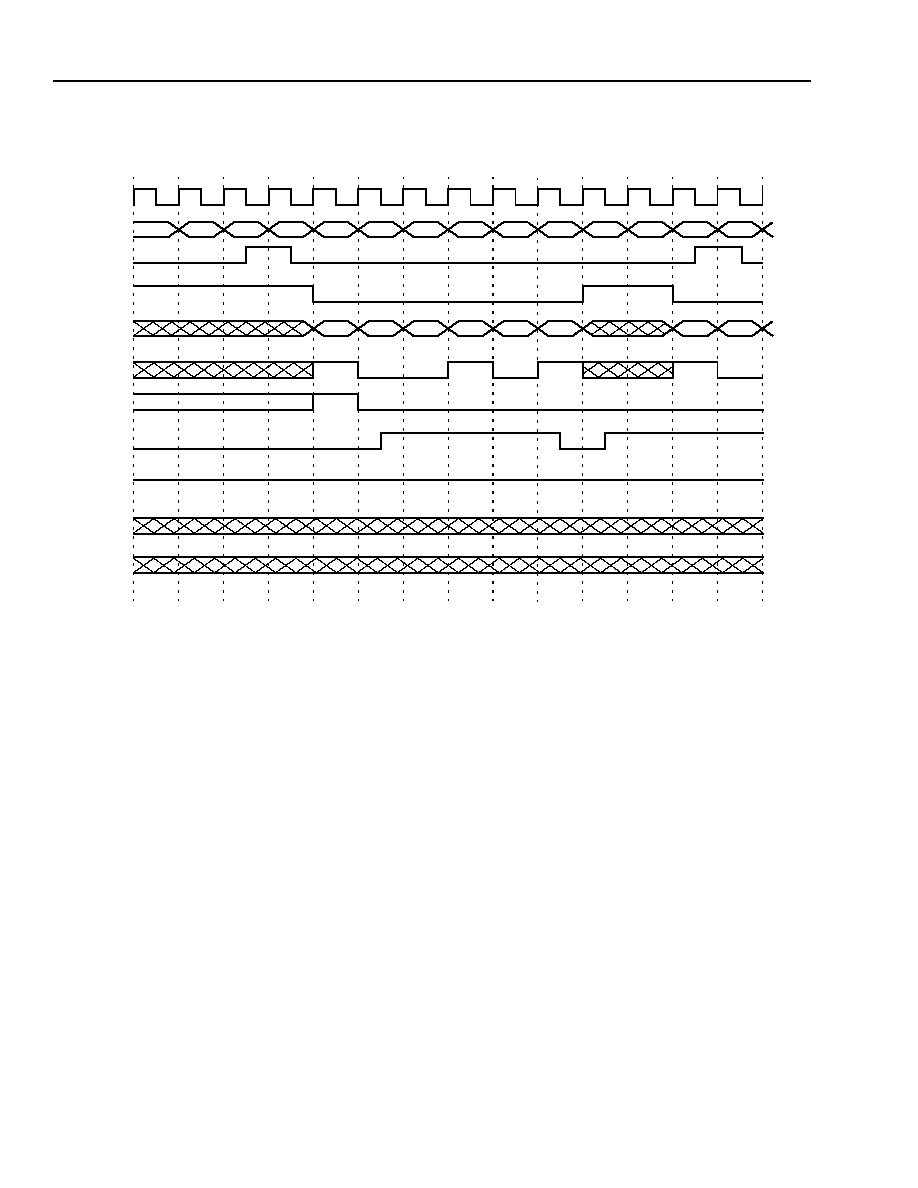

Figure 20. Nominal Concentration Highway Interface Timing ............................................................................70

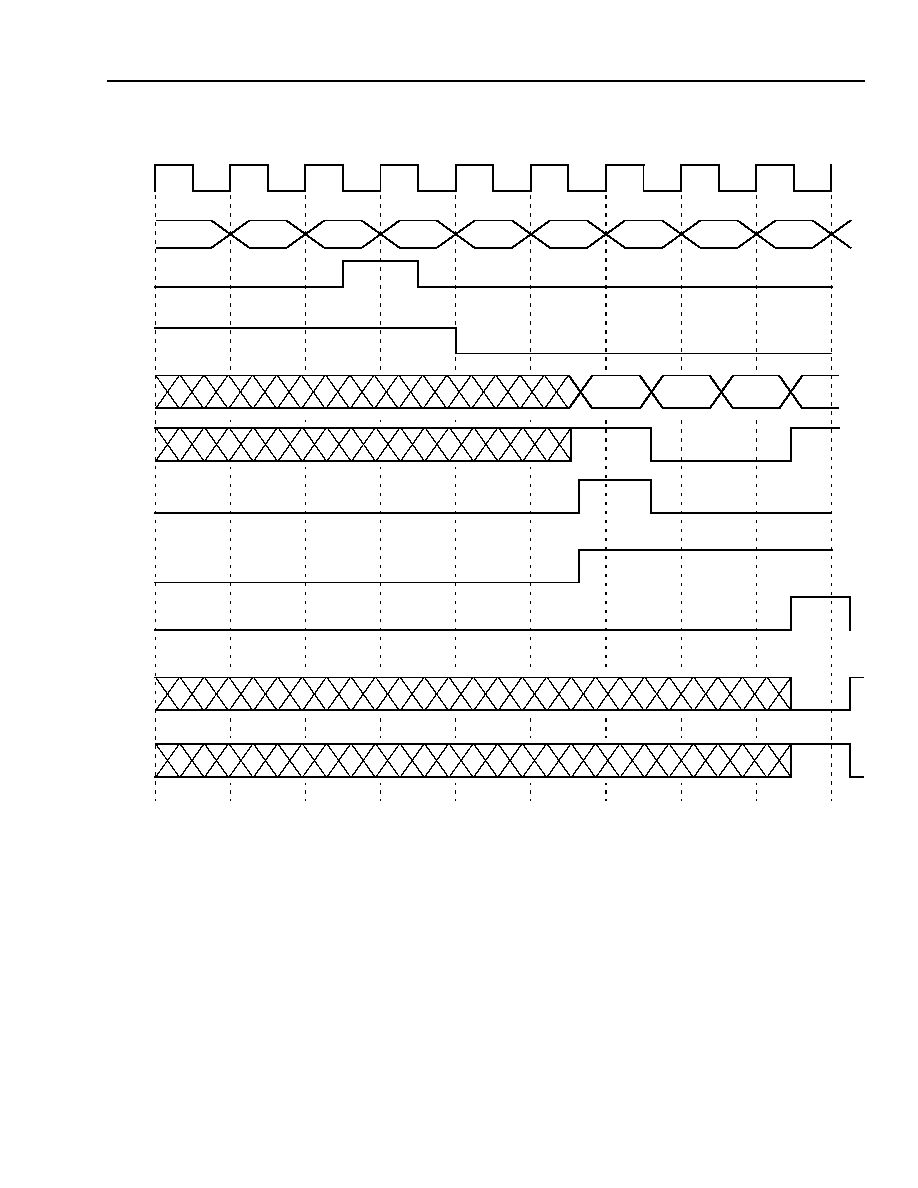

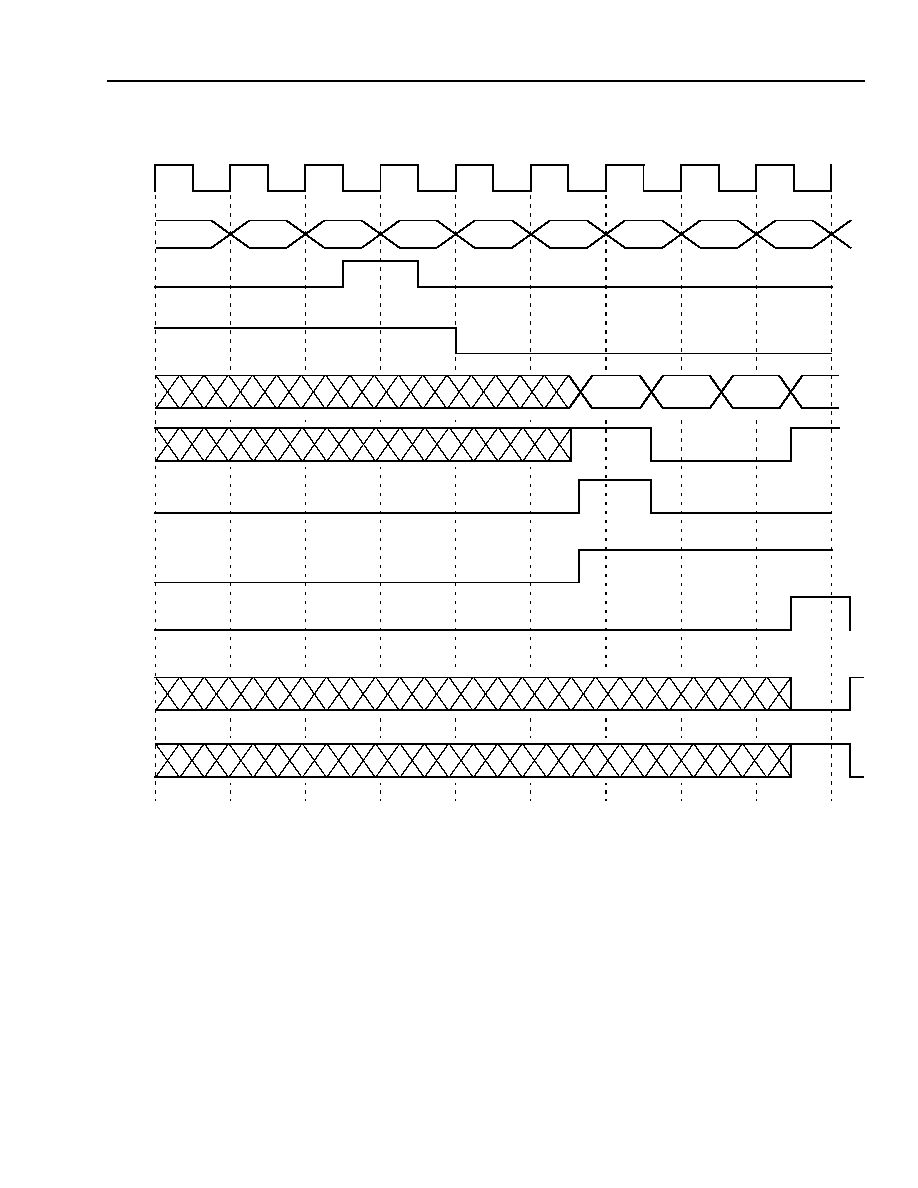

Figure 21. CHIDTS Mode Concentration Highway Interface Timing ..................................................................71

Figure 22. IMA Application..................................................................................................................................76

Figure 23. IMA High-Level Interconnect Block Diagram.....................................................................................77

Figure 24. Logical View of 3 Link Group's DCB Shortly after Starting to Receive Data from the Line ...............80

Figure 25. Logical View of 3-Link Group's DCB When It Starts Reading DCB...................................................81

Figure 26. Logical View of 3 Link Group's DCB after It Starts Reading DCB .....................................................82

Figure 27. DCB During Normal Operation ..........................................................................................................83

Figure 28. Starting to Add a Link to a Group ......................................................................................................84

Figure 29. Link Now Being Read ........................................................................................................................85

Figure 30. Effects of Link #3 and Link #4 Faults.................................................................................................86

Figure 31. APC Block Integrated Memory Configuration....................................................................................89

Figure 32. Switch Fabric Connections for Dual Newport Switch Mode ..............................................................90

Figure 33. AAL Engine Block Diagram .............................................................................................................102

Figure 34. SIF-to-NIF, NIF-to-SIF .....................................................................................................................105

Figure 35. SIF Loopback, NIF Loopback ..........................................................................................................105

Figure 36. NIF Adaptation Loopback ................................................................................................................106

Figure 37. Host-to-SIF, SIF-to-Host..................................................................................................................106

Figure 38. Host-to-NIF, NIF-to-Host .................................................................................................................107

Figure 39. SAR Subblock Diagram...................................................................................................................108

Figure 40. Logical View of the Enqueue (Left) and Dequeue (Right) Address Translation Procedure.............110

Figure 41. Simplified Diagram of SQASE Queueing Structure.........................................................................111

Figure 42. User Data Types and AAL Types at the Interfaces .........................................................................112

Figure 43. User Data Type (UDT) vs. AAL Type Mapping ...............................................................................112

Figure 44. SPAAL2 Data Format ......................................................................................................................114

Figure 45. CPS-AAL0 Data Format ..................................................................................................................115

Figure 46. PATM Format ..................................................................................................................................116

Figure 47. HPF Format .....................................................................................................................................117

Figure 48. Transferring an HPF Packet over the Host Interface Example........................................................120

Figure 49. Port Table ........................................................................................................................................125

Figure 50. VC Table..........................................................................................................................................127

Figure 51. AAL2 VC Table................................................................................................................................128

Figure 52. Connection Table ............................................................................................................................129

List of Figures

(continued)

Figure

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

T1/E1/J1/J2 ATM Processor

Agere Systems Inc.

Lucent Technologies--Proprietary

11

Use pursuant to Company instructions

Figure 53. SQASE Queueing Structure ............................................................................................................133

Figure 54. Connection Queue Length Policing .................................................................................................140

Figure 55. IL1Q/L1Q Length Policing ...............................................................................................................141

Figure 56. Intra-Level 2 Queue Length Policing ...............................................................................................142

Figure 57. UT2/UT2+ Header at the SIF Interface ...........................................................................................145

Figure 58. Cell Transmission on the SIF Interface ...........................................................................................146

Figure 59. Packet Transmission on the SIF Interface with No Stalls................................................................147

Figure 60. Packet Transmission on the SIF Interface with the PHY Stalling ....................................................148

Figure 61. Packet Transmission on the SIF Interface with the Master Stalling ................................................149

Figure 62. Reception of a Cell on the SIF Interface..........................................................................................150

Figure 63. Reception of a Packet on the SIF Interface with No Stalls ..............................................................151

Figure 64. Reception of a Packet on the SIF Interface with the PHY Stalling ..................................................152

Figure 65. Reception of a Packet on the SIF Interface with the Master Stalling...............................................153

Figure 66. ESI Functional Timing Diagram.......................................................................................................155

Figure 67. High-Level View of Software Architecture .......................................................................................156

Figure 68. Newport Internal Busing Scheme ....................................................................................................158

Figure 69. PHY Layer Provisioning...................................................................................................................159

Figure 70. IMA Group Link Failure....................................................................................................................165

Figure 71. ExH Processor, EDC, and Hardware Blocks...................................................................................170

Figure 72. Link Reference Numbers Used by the NPT_CONFIG_PHY_LINK Command ...............................185

Figure 73. Data Read from Newport.................................................................................................................313

Figure 74. Data Written to Newport ..................................................................................................................314

Figure 75. Power-On Reset ..............................................................................................................................315

Figure 76. Stable Reset ....................................................................................................................................315

Figure 77. CHI Transmit I/O Timing..................................................................................................................316

Figure 78. CHI Receive I/O Timing...................................................................................................................317

List of Tables

Table

Page

Preliminary Data Sheet

TAAD08JU2 Newport

August 2001

12

Agere Systems Inc.

Table 1.

Pin Definitions .................................................................................................................................. 17

Table 2.

Transmission Line Interface Signals (48 Signals) ............................................................................ 17

Table 3.

CHI Interface Signals (20 Signals) ................................................................................................... 18

Table 4.

UTOPIA 2 Expansion Interface Signals (52 Signals) ....................................................................... 18

Table 5.

System Interface Signals (63 Signals).............................................................................................. 19

Table 6.

Switch Fabric Interface Signals (50 Pins)......................................................................................... 21

Table 7.

APC External Statistics Interface Signals (18 Signals) .................................................................... 22

Table 8.

SAR External Statistics Interface Signals (18 Signals)..................................................................... 23

Table 9.

Host Interface Signals (49 Signals) .................................................................................................. 23

Table 10. JTAG Interface Pins (6 Signals) ...................................................................................................... 23

Table 11. Global/Miscellaneous Signal Pins (10 Signals) ................................................................................ 24

Table 12. Power Supply Pins (4 Analog Power Pins, 120 Digital Power Pins) ............................................... 24

Table 13. Signal-to-Ball Mapping ..................................................................................................................... 26

Table 14. Host Registers .................................................................................................................................. 50

Table 15. Frame Alignment Criteria.................................................................................................................. 59

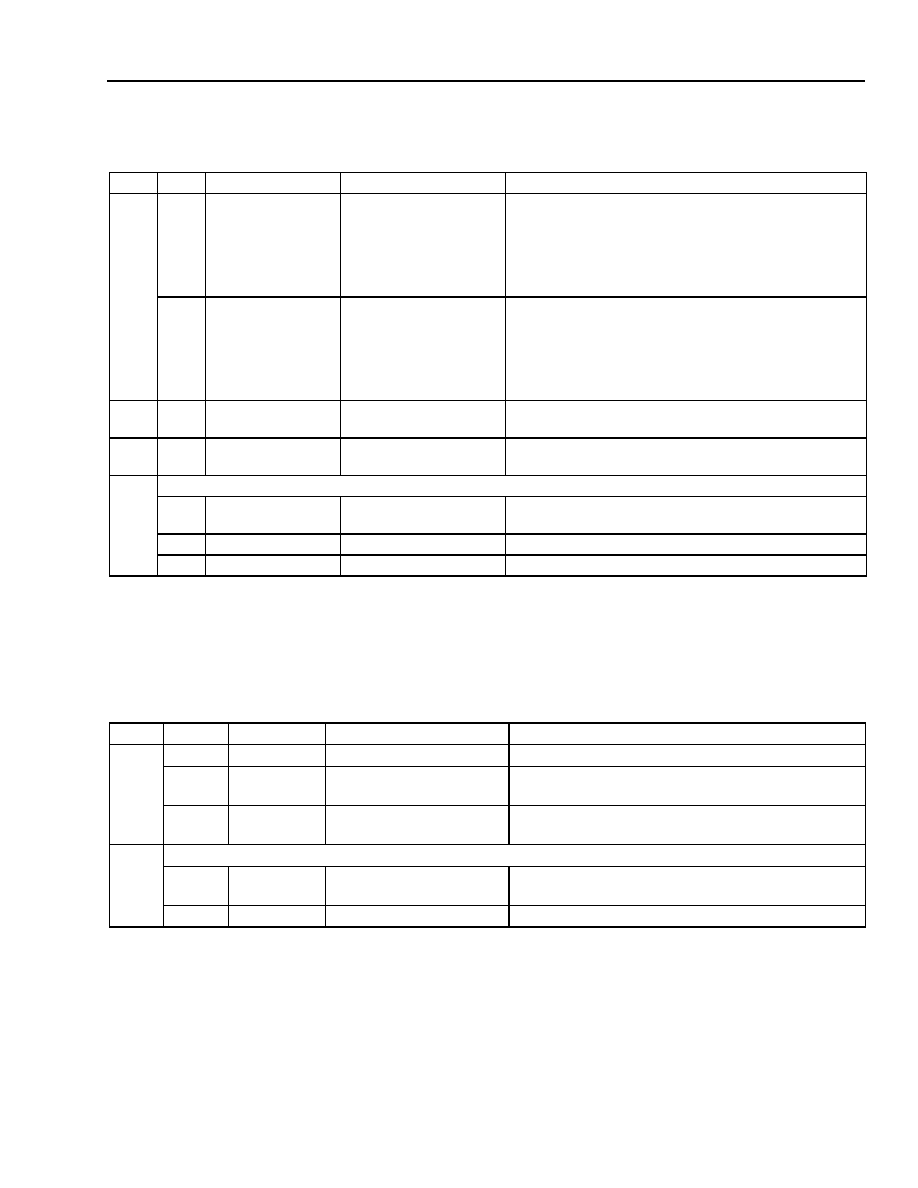

Table 16. Performance Monitor Functional Descriptions.................................................................................. 60

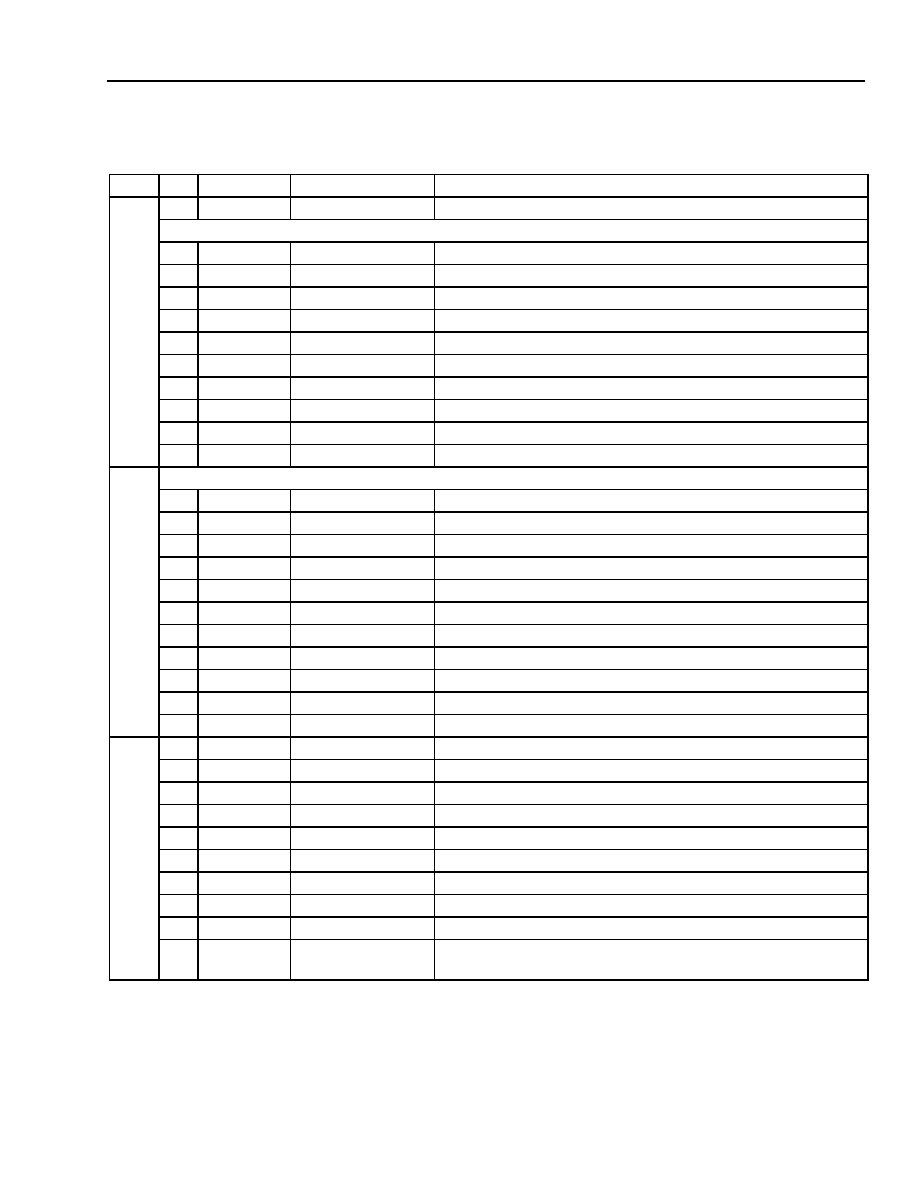

Table 17. Performance Report Message Format ............................................................................................. 62

Table 18. Performance Report Message Field Definition................................................................................. 63

Table 19. Shared Tx Stack Format for CEPT Frame ....................................................................................... 67

Table 20. Cell Headers of Idle, Unassigned, and Invalid Cells......................................................................... 75

Table 21. TC Functionality................................................................................................................................ 75

Table 22. Newport Exceptions to the IMA PICS Proforma ............................................................................... 87

Table 23. PATM Fields ................................................................................................................................... 116

Table 24. HPF Fields...................................................................................................................................... 117

Table 25. ESI Message Format (AALXDATA[15:0])....................................................................................... 118

Table 26. ESI Violation Codings..................................................................................................................... 119

Table 27. AAL Type vs. Service Type Compatibility....................................................................................... 120

Table 28. Transport of Congestion Indication and Loss Priority..................................................................... 123

Table 29. PortIndex to Enqueue Block Port Mapping..................................................................................... 125

Table 30. MEMI-SM Resources ..................................................................................................................... 126

Table 31. SQASE-SM Resources .................................................................................................................. 132

Table 32. IL1Q and IL2Q Scheduling ............................................................................................................. 136

Table 33. Example Stage One Divider Settings ............................................................................................. 138

Table 34. Example Stage Two Divider Settings ............................................................................................. 139

Table 35. Exceptions ...................................................................................................................................... 142

Table 36. Link Assignments for IMA Groups .................................................................................................. 160

Table 37. Link Assignment Register Set for IMA Group N ............................................................................. 160

Table 38. Link Assignment Register Set for IMA Group M............................................................................. 160

Table 39. Newport Operating Modes.............................................................................................................. 169

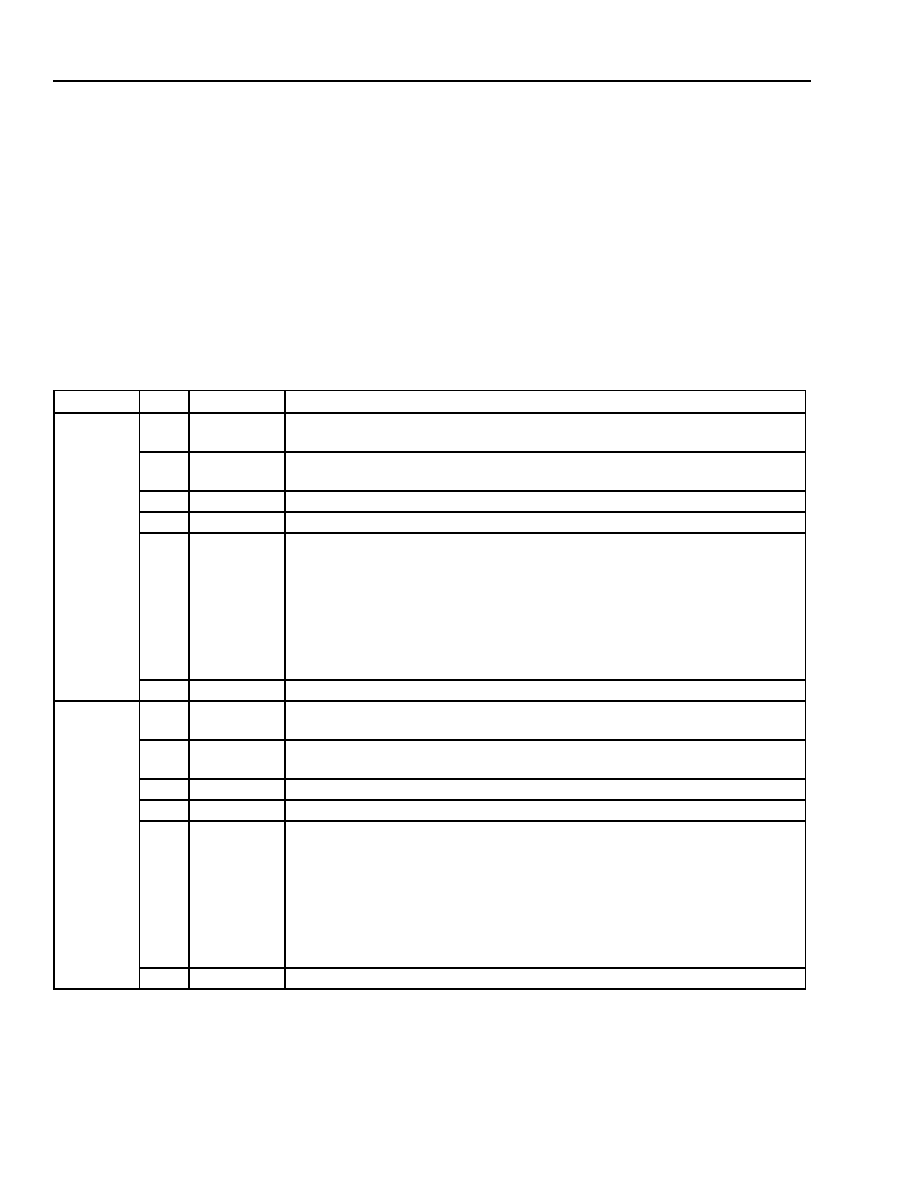

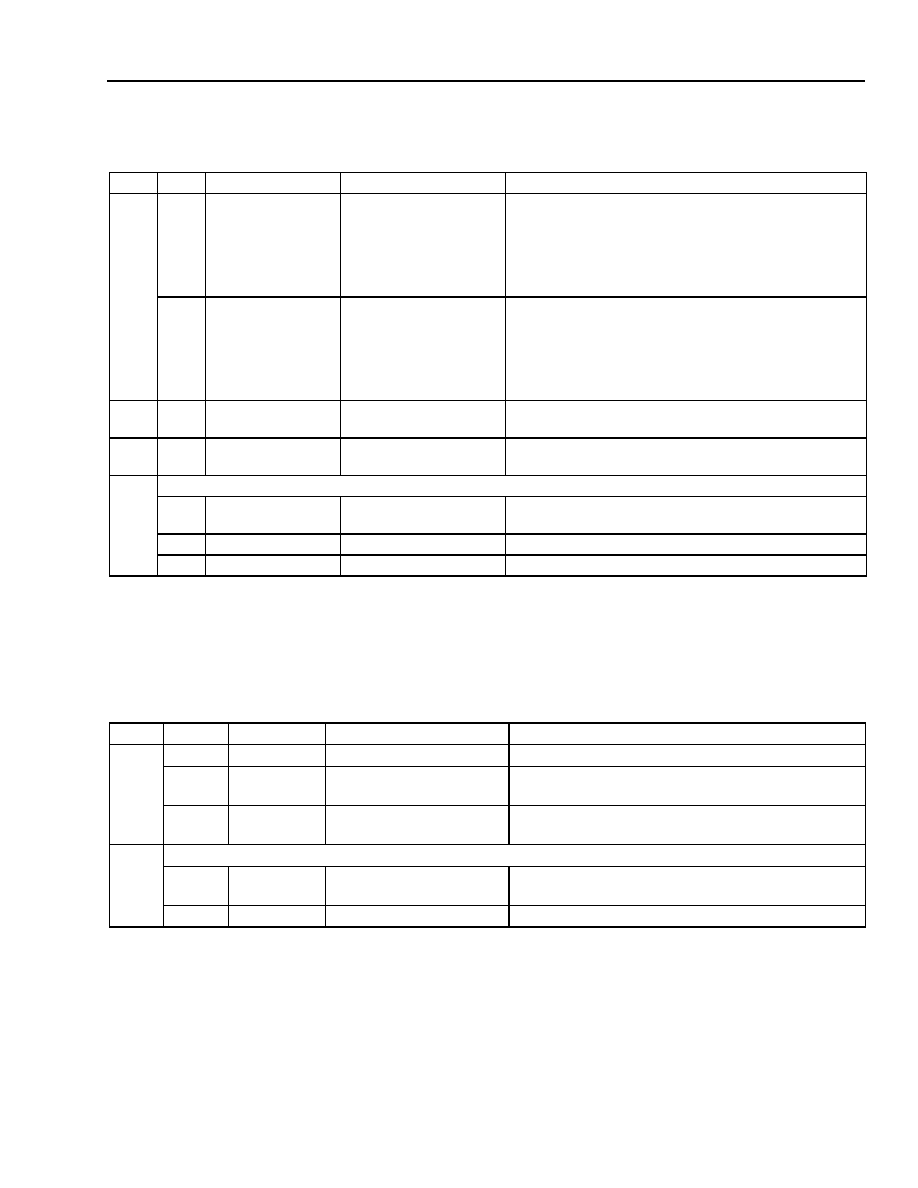

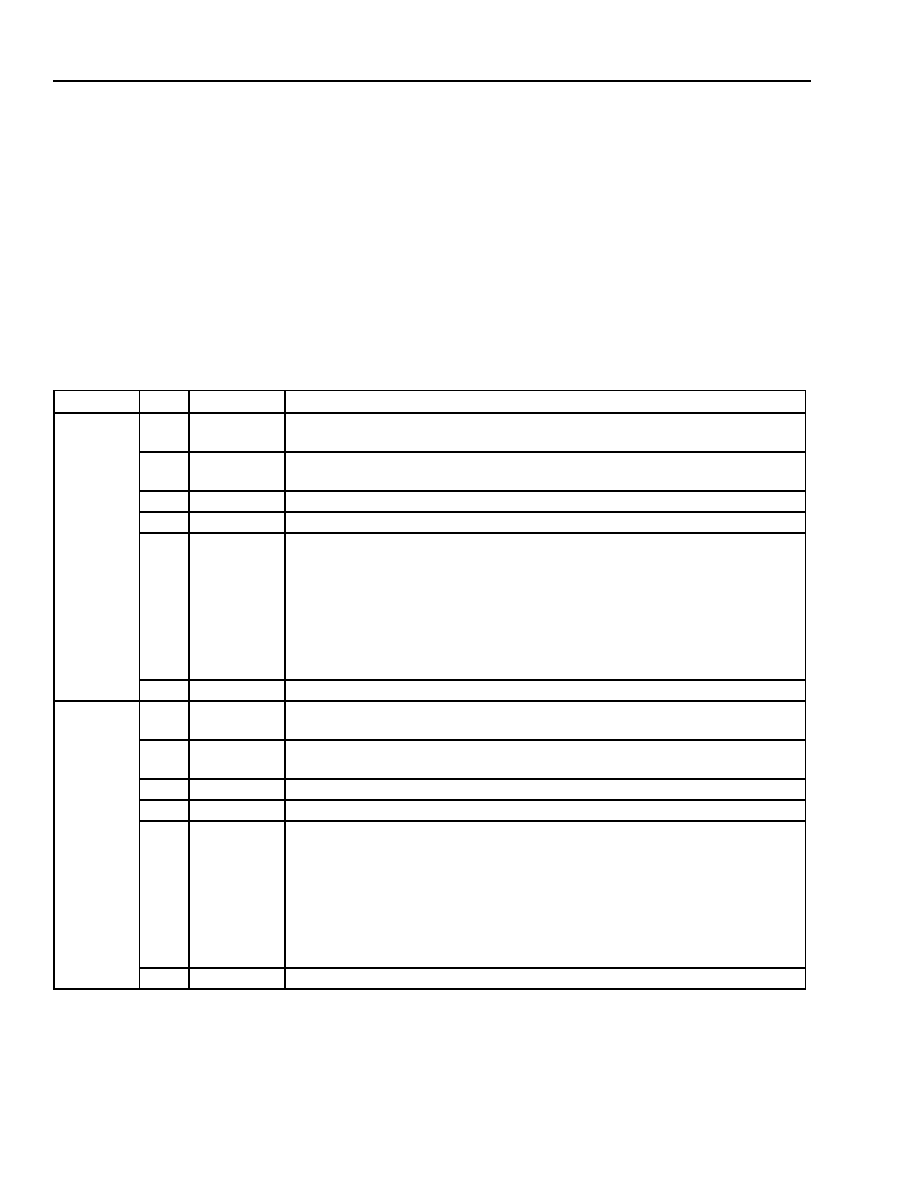

Table 40. Fields of the Command Register .................................................................................................... 172

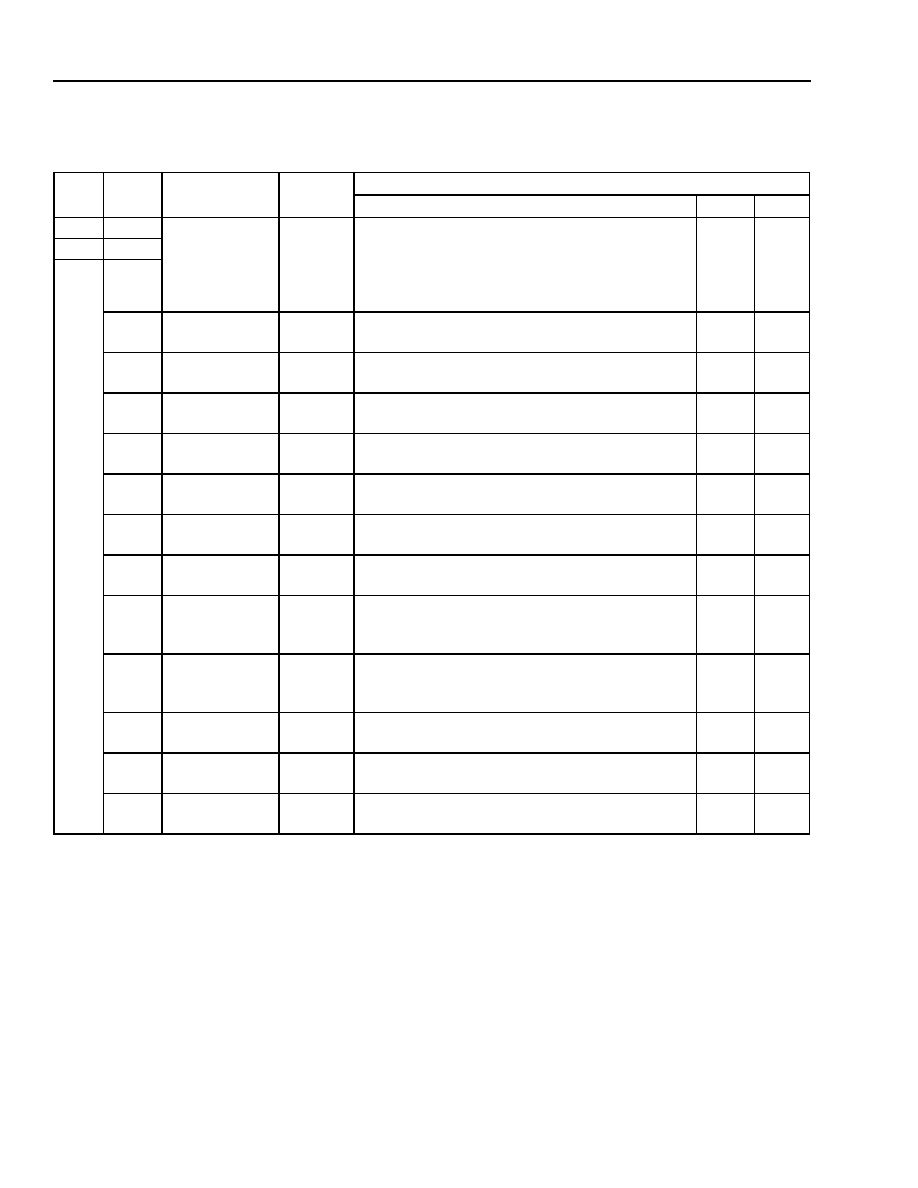

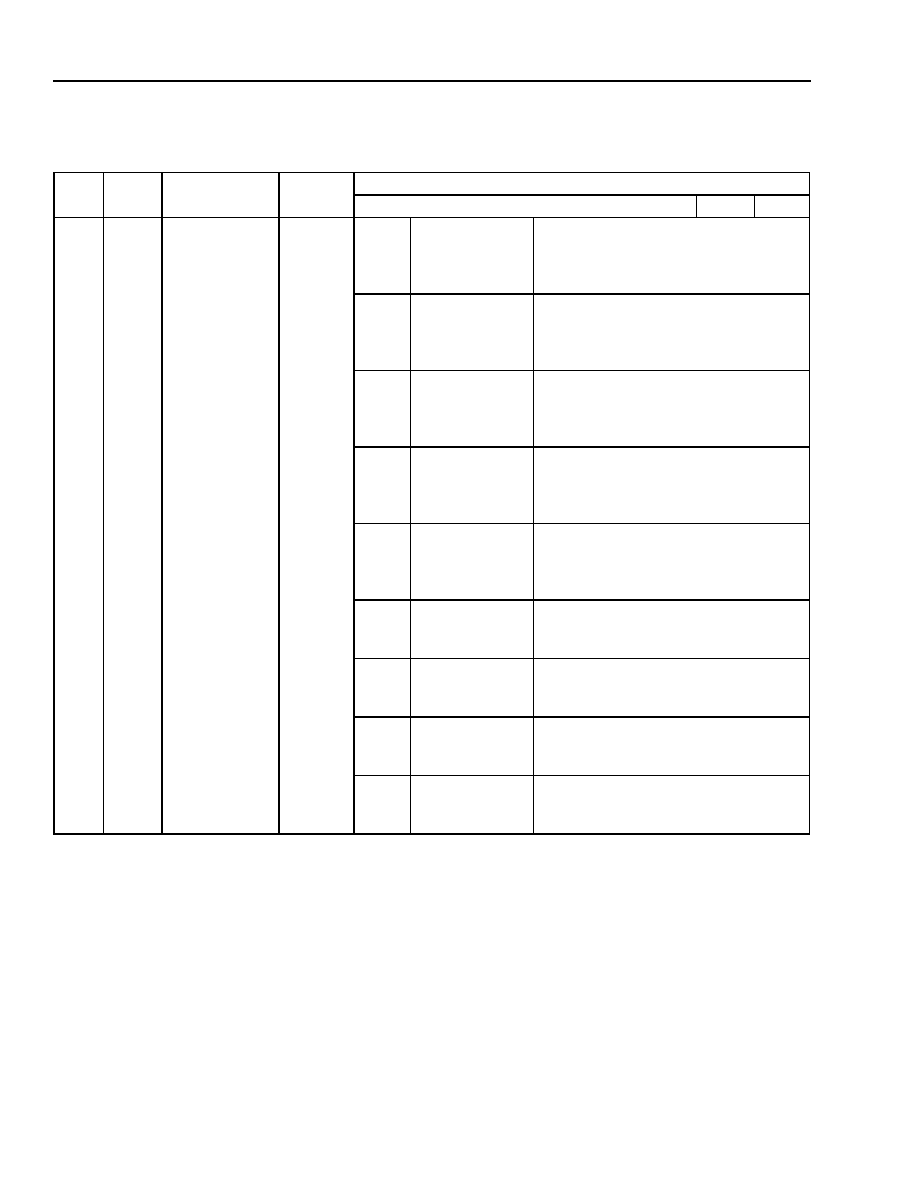

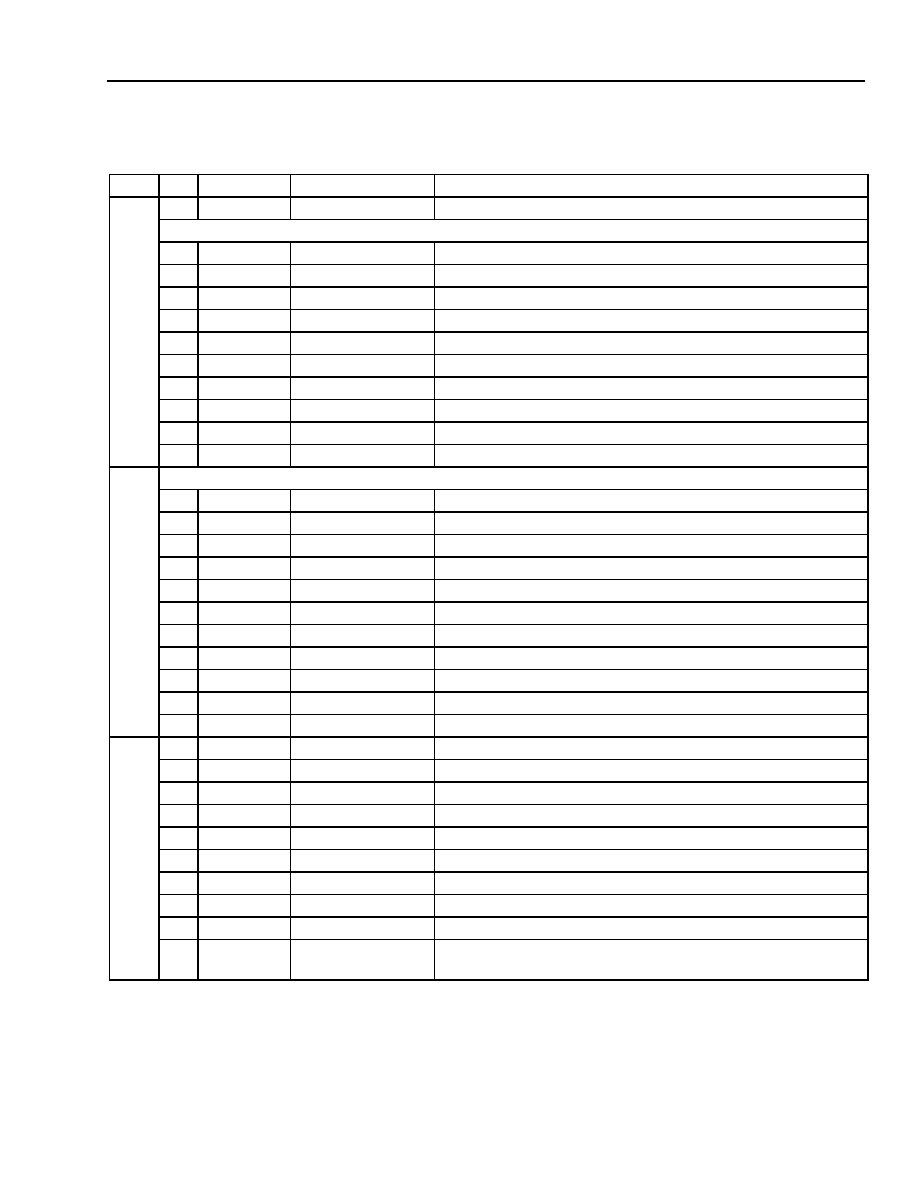

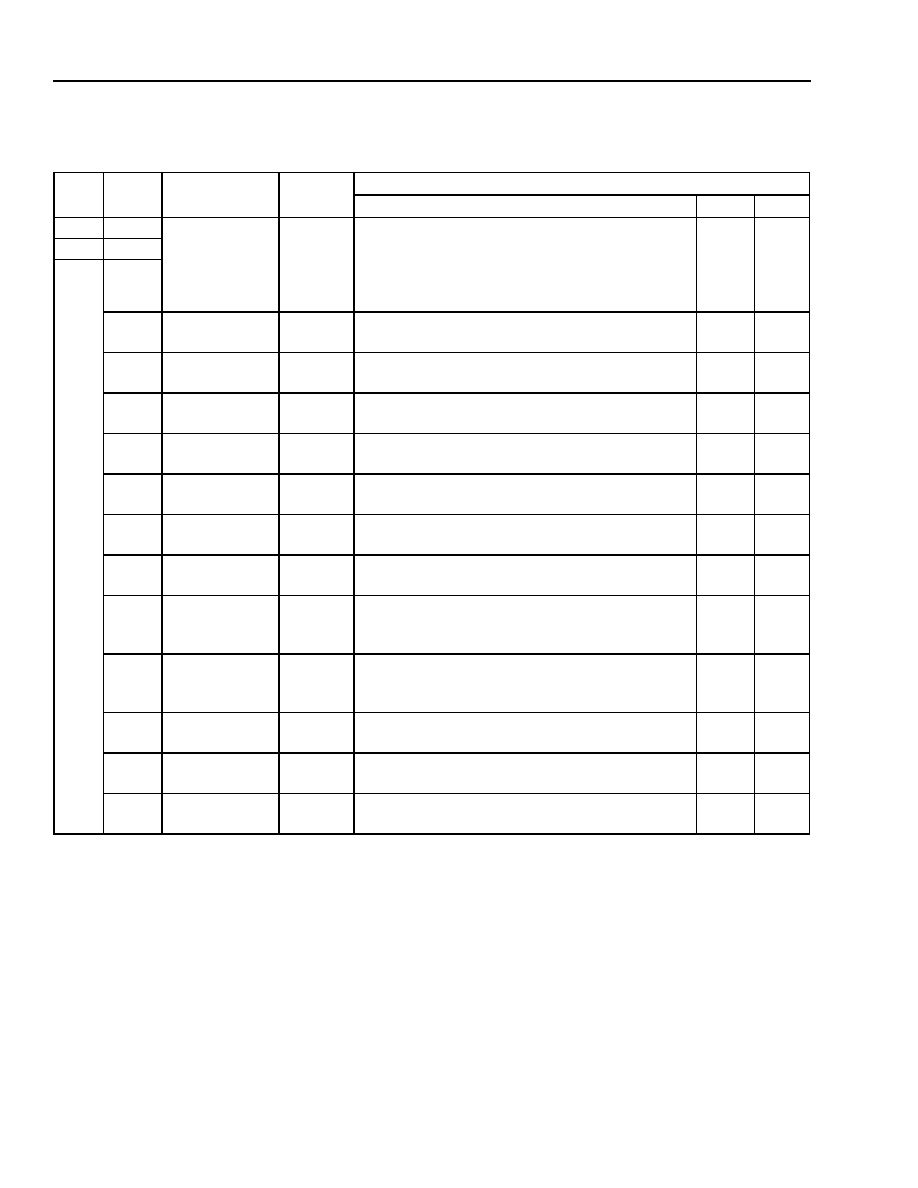

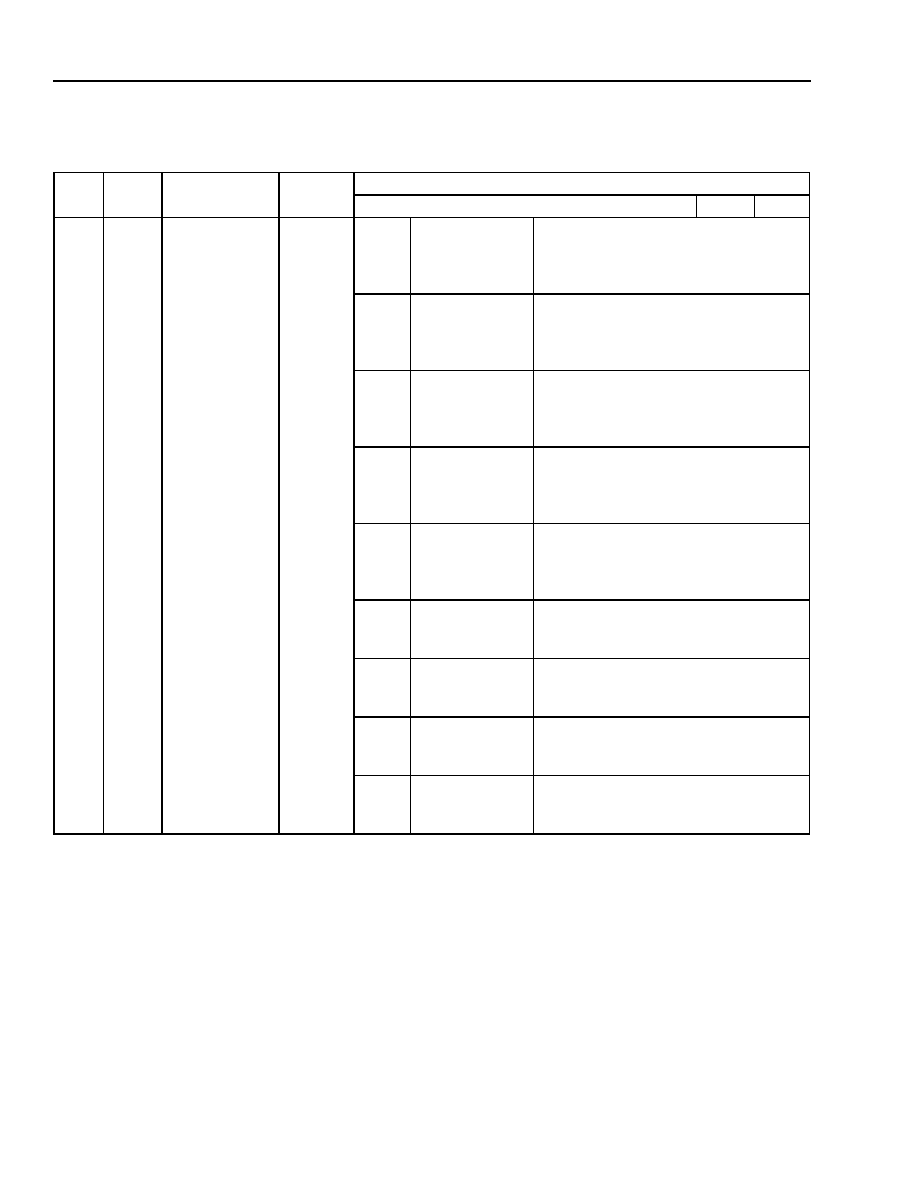

Table 41. Command List and Summary ......................................................................................................... 173

Table 42. Parameter List for the NPT_GLBCLK_RATE Command ............................................................... 176

Table 43. Parameter List for NPT_PHY_CONFIG_GLOBALS Command ..................................................... 178

Table 44. Parameter List for NPT_PHY_CONFIG_LINK Command.............................................................. 186

Table 45. Parameter List for NPT_PHY_ADD_LINK Command .................................................................... 191

Table 46. Parameter List for NPT_PHY_DELETE_LINK Command.............................................................. 192

Table 47. Parameter List for NPT_PHY_FRAMER_TEST_LINK Command ................................................. 193

Table 48. Parameter List for NPT_PHY_SEND_ALARMS Command ........................................................... 194

Table 49. Parameter List for NPT_PHY_SPAN_LINE_LOOPBACK Command ............................................ 195

Table 50. Parameter List for NPT_PHY_CHI_LOOPBACK Command.......................................................... 196

Table 51. Parameter List for NPT_PHY_IMA_CONFIG_GROUP Command ................................................ 197

Table 52. Parameter List for NPT_PHY_IMA_DELETE_GROUP Command ................................................ 198

List of Tables

(continued)

Table

Page

Agere Systems Inc.

Lucent Technologies--Proprietary

13

Use pursuant to Company instructions

Preliminary Data Sheet

TAAD08JU2 Newport

August 14, 2001

T1/E1/J1/J2 ATM Processor

Table 53. Parameter List for NPT_PHY_IMA_INHIBIT_LINK Command....................................................... 198

Table 54. Parameter List for NPT_PHY_IMA_INHIBIT_GROUP Command ................................................. 198