Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

ADMC401

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

® Analog Devices, Inc., 2000

REV. B

Single-Chip, DSP-Based

High Performance Motor Controller

FUNCTIONAL BLOCK DIAGRAM

ARITHMETIC UNITS

SHIFTER

MAC

ALU

MEMORY

SPORT 1

INTERVAL

TIMER

DM

RAM

1K

16

PM

ROM

2K 24

PM

RAM

2K 24

INTERRUPT

CONTROLLER

ENCODER

INTERFACE

8 CHANNEL

12-BIT ADC

26 MIPS DSP CORE

SERIAL PORTS

PROGRAM

SEQUENCER

DATA

ADDRESS

GENERATORS

DAG 1

DAG 2

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

PROGRAM MEMORY DATA

DATA MEMORY DATA

SPORT 0

WATCH-

DOG

TIMER

EVENT

CAPTURE

UNIT

DIGITAL

I/O

UNIT

EXTERNAL

ADDRESS

BUS

EXTERNAL

DATA

BUS

PRECISION

VOLTAGE

REFERENCE

16-BIT

PWM

GENERATION

POWER-

ON

RESET

MOTOR CONTROL

PERIPHERALS

2 CHANNEL

AUXILIARY

PWM

FEATURES

26 MIPS Fixed-Point DSP Core

Single Cycle Instruction Execution (38.5 ns)

ADSP-21xx Family Code Compatible

16-Bit Arithmetic and Logic Unit (ALU)

Single Cycle 16-Bit 16-Bit Multiply and Accumulate

Into 40-Bit Accumulator (MAC)

32-Bit Shifter (Logical and Arithmetic)

Multifunction Instructions

Single Cycle Context Switch

Zero Overhead Looping

Conditional Instruction Execution

Two Independent Data Address Generators

Memory Configuration

2K 24-Bit Internal Program Memory RAM

2K 24-Bit Internal Program Memory ROM

1K 16-Bit Internal Data Memory RAM

14-Bit Address Bus and 24-Bit Data Bus for External

Memory Expansion

High Resolution Multichannel ADC

12-Bit Pipeline Flash Analog-to-Digital Converter

Eight Dedicated Analog Inputs

Simultaneous Sampling Capability

All Eight Inputs Converted in <2 s

4.0 V p-p Input Voltage Range

PWM Synchronized or External Convert Start

Internal or External Voltage Reference

Out-of-Range Detection

Voltage Reference

Internal 2.0 V 2.0% Voltage Reference

Three-Phase 16-Bit PWM Generation Unit

Programmable Switching Frequency, Dead Time and

Minimum Pulsewidth

Edge Resolution of 38.5 ns

One or Two Updates per Switching Period

Hardware Polarity Control

Individual Enable/Disable of Each Output

High Frequency Chopping Mode

Dedicated Shutdown Pin (

PWMTRIP)

Additional Shutdown Pins in I/O System

High Output Sink and Source Capability (10 mA)

Incremental Encoder Interface Unit

Quadrature Rates to 17.3 MHz

Programmable Filtering of Encoder Inputs

Alternative Frequency and Direction Mode

Two Registration Inputs to Latch Count Value

Optional Hardware Reset of Counter

Single North Marker Mode

Count Error Monitor Function

Dedicated 16-Bit Loop Timer (Periodic Interrupts)

Companion Encoder Event (1/T) Timer

(Continued on Page 14)

RECOMMENDED OPERATING CONDITIONS

B Grade

Parameter

Min

Max

Unit

V

DD

Digital Supply Voltage

4.75

5.25

V

AV

DD

Analog Supply Voltage

4.75

5.25

V

T

AMB

Ambient Operating Temperature

Ł40

+85

░C

ELECTRICAL CHARACTERISTICS

Parameter

Test Conditions

Min

Max

Unit

V

IH

HI-Level Input Voltage

1, 2, 3

@ V

DD

= max

2.0

V

V

IL

LO-Level Input Voltage

1, 2, 3

@ V

DD

= min

0.8

V

V

OH

HI-Level Output Voltage

1, 3, 4, 5, 6

@ V

DD

= min, I

OH

= Ł1.0 mA

2.4

V

@ V

DD

= min, I

OH

= Ł0.1 mA

V

DD

Ł 0.3

V

V

OL

LO-Level Output Voltage

1, 3, 4, 5, 6

@ V

DD

= min, I

OL

= 2.0 mA

0.4

V

V

OH

HI-Level Output Voltage

5

@ V

DD

= min, I

OH

= Ł10.0 mA

2.4

V

V

OL

LO-Level Output Voltage

5

@ V

DD

= min, I

OL

= 10.0 mA

1.2

V

I

IH

HI-Level Input Current

7

@ V

DD

= max, V

IN

= V

DD

max

10

ĄA

I

IH

HI-Level Input Current

8

@ V

DD

= max, V

IN

= V

DD

max

100

ĄA

I

IH

HI-Level Input Current

9

@ V

DD

= max, V

IN

= V

DD

max

10

ĄA

I

IL

LO-Level Input Current

7

@ V

DD

= max, V

IN

= 0 V

10

ĄA

I

IL

LO-Level Input Current

8

@ V

DD

= max, V

IN

= 0 V

10

ĄA

I

IL

LO-Level Input Current

9

@ V

DD

= max, V

IN

= 0 V

100

ĄA

I

OZH

HI-Level Three-State Leakage Current

10

@ V

DD

= max, V

IN

= V

DD

max

10

ĄA

I

OZL

LO-Level Three-State Leakage Current

10

@ V

DD

= max, V

IN

= 0 V

10

ĄA

I

DD

Digital Supply Current (Idle)

11

@ V

DD

= max

40

mA

I

DD

Digital Supply Current (Dynamic)

12

@ V

DD

= max

110

mA

I

DD

Analog Supply Current

@ AV

DD

= max

60

mA

C

I

Input Pin Capacitance

13

V

IN

= 2.5 V, f

IN

= 1 MHz,

8

pF

T

AMB

= +25

░C

C

O

Output Pin Capacitance

13, 14

V

IN

= 2.5 V, f

IN

= 1 MHz,

8

pF

T

AMB

= +25

░C

NOTES

1

Bidirectional pins: D0ŁD23, RFS0, RFS1, TFS0, TFS1, SCLK0 and SCLK1, PIO0ŁPIO11.

2

Input only pins:

PWMTRIP, PWMPOL, PWMSR, RESET, EIA, EIB, EIZ, EIS, ETU0, ETU1, DR1A, DR1B, DR0, CLKIN, CONVST, MMAP, BMODE, BR

and

PWD.

3

Programmable I/O Pins (PIO0ŁPIO11).

4

Output pins: PWMSYNC, AUX0, AUX1, CLKOUT, DT0, DT1,

BG, BGH, PMS, DMS, BMS, RD, WR, PWDACK and A0ŁA13.

5

Output pins: AH, AL, BH, BL, CH and CL.

6

Although specified for TTL outputs, all ADMC401 outputs are CMOS-compatible and will drive to V

DD

Ł0.3 V and GND+0.3 V assuming no dc loads.

7

Input only pins

RESET, EIA, EIB, EIZ, EIS, ETU0, ETU1, DR1A, DR1B, DR0, CLKIN, CONVST, MMAP, BMODE, BR and PWD.

8

Input pins with internal pull-down PIO0ŁPIO11 and

PWMTRIP.

9

Input pins with internal pull-up, PWMPOL and

PWMSR.

10

Three-statable pins: A0ŁA13, D0ŁD23,

PMS, DMS, BMS, RD, WR, DT0, DT1, RFS0, RFS1, TFS0, TFS1, SCLK0, SCLK1.

11

Idle refers execution of the IDLE instruction. Deasserted pins are driven to V

DD

or GND. Current reflects device operation with CLKOUT disabled.

12

Current reflects device operating with no output loads.

13

Guaranteed but not tested.

14

Output Pin Capacitance is the capacitive load for any three-state output pin.

Specifications subject to change without notice.

(V

DD

= AV

DD

= 5 V 5%, GND = AGND = 0 V, T

AMB

= Ł40 C to +85 C,

CLKIN = 13 MHz, unless otherwise noted)

REV. B

Ł2Ł

ADMC401ŁSPECIFICATIONS

ANALOG-TO-DIGITAL CONVERTER

Parameter

Test Conditions

Min

Typ

Max

Unit

AC SPECIFICATIONS

SNR

Signal to Noise Ratio

f

IN

= 1.0 kHz

68

70

dB

SNRD

Signal to Noise and Distortion

f

IN

= 1.0 kHz

66

69

dB

THD

Total Harmonic Distortion

f

IN

= 1.0 kHz

Ł76

Ł70

dB

CTLK

Channel-Channel Crosstalk

f

IN

= 1.0 kHz

Ł89

Ł72

dB

CMRR

Common-Mode Rejection Ratio

Ł90

Ł72

dB

PSRR

Power Supply Rejection Ratio

0.025

0.1

% FSR

ACCURACY

INL

Integral Nonlinearity

▒0.6

▒1.5

LSB

DNL

Differential Nonlinearity

▒0.5

▒1.0

LSB

No Missing Codes

12

Bits Guaranteed

Zero Error

0.1

0.25

% FSR

Gain Error

1

0.4

1.0

% FSR

TEMPERATURE DRIFT

Zero Error

0.025

% FSR

Gain Error

1

0.025

% FSR

INPUT VOLTAGE

V

IN

Voltage Span

4.0

V p-p

C

IN

Input Capacitance

2

10

pF

CONVERSION TIME

t

CONV

Total Conversion Time

All 8 Channels

1.88

Ąs

NOTES

1

Excludes Internal Voltage Reference Error.

2

Analog Input Pins VIN0 to VIN7.

Typical values are neither tested nor guaranteed.

Specifications subject to change without notice.

VOLTAGE REFERENCE

Parameter

Test Conditions

Min

Typ

Max

Unit

V

REF

Output Voltage Reference

SENSE = REFCOM

1.96

2.0

2.04

V

Output Voltage Tolerance

1

SENSE = REFCOM

6

mV

Output Current

1.0

mA

Load Regulation

1.0 mA Load Current

0.3

1.5

mV

Power Supply Rejection Ratio

0.1

1.5

mV

Reference Input Resistance

8

k

NOTES

1

Relative tolerance due to temperature change, T

MIN

to T

MAX

.

Specifications subject to change without notice.

POWER-ON RESET

Parameter

Test Conditions

Min

Typ

Max

Unit

V

RST

Reset Threshold Voltage

3.25

4.0

V

V

HYST

Hysteresis Voltage

75

mV

Specifications subject to change without notice.

(V

DD

= AV

DD

= 5 V 5%, GND = AGND = 0 V, T

AMB

= Ł40 C to +85 C, CLKIN = 13 MHz,

VIN0 to VIN7 = 4.0 V p-p, V

REF

= 2.0 V, unless otherwise noted)

(V

DD

= AV

DD

= 5 V 5%, GND = AGND = 0 V, T

AMB

= Ł40 C to +85 C, CLKIN = 13 MHz, VIN0 to VIN7 =

4.0 V p-p, V

REF

= 2.0 V, unless otherwise noted)

(GND = AGND = 0 V, T

AMB

= Ł40 C to +85 C, CLKIN = 13 MHz, unless otherwise noted)

ADMC401

Ł3Ł

REV. B

REV. B

ADMC401

Ł4Ł

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . Ł0.3 V to +7 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . Ł0.3 V to V

DD

+ 0.3 V

Output Voltage Swing . . . . . . . . . . . . . . Ł0.3 V to V

DD

+ 0.3 V

Operating Temperature Range (Ambient) . . . . Ł40

░C to +85░C

Storage Temperature Range . . . . . . . . . . . . . Ł65

░C to +150░C

Lead Temperature (5 sec) . . . . . . . . . . . . . . . . . . . . . . +280

░C

*Stresses above those listed under absolute maximum ratings may cause permanent

damage to the device. These are stresses only; functional operation of the device

at these or any other conditions above those indicated in the operational section of

this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the ADMC401 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

ORDERING GUIDE

Temperature

Instruction

Package

Package

Model

Range

Rate

Description

Option

ADMC401BST

Ł40

░C to +85░C

26 MHz

144-Lead Plastic Thin Quad Flatpack (LQFP)

ST-144

ADMC401-ADVEVALKIT

Development Tool Kit

ADMC401-PB

Evaluation/Processor Board

Timing Parameters

GENERAL NOTES

Use the exact timing information given. Do not attempt to

derive parameters from the addition or subtraction of others.

While addition or subtraction would yield meaningful results for

an individual device, the values given in this data sheet reflect

statistical variations and worst cases. Consequently, you cannot

meaningfully add up parameters to derive longer times.

TIMING NOTES

Switching characteristics specify how the processor changes its

signals. You have no control over this timing; it is dependent on

the internal design. Timing requirements apply to signals that

are controlled outside the processor, such as the data input for a

read operation.

Timing requirements guarantee that the processor operates

correctly with another device. Switching characteristics tell you

what the device will do under a given circumstance. Also, use

the switching characteristics to ensure any timing requirement

of a device connected to the processor (such as memory) is

satisfied.

MEMORY REQUIREMENTS

This chart links common memory device specification names

and ADMC401 timing parameters for your convenience.

Common

Parameter

Memory Device

Name

Function

Specification Name

t

ASW

A0ŁA13,

DMS, PMS

Address Setup to

Setup before

WR Low

Write Start

t

AW

A0ŁA13,

DMS, PMS

Address Setup to

before

WR Deasserted

Write End

t

WRA

A0ŁA13,

DMS, PMS

Address Hold Time

Hold after

WR Deasserted

t

DW

Data Setup before

WR High Data Setup Time

t

DH

Data Hold after

WR High

Data Hold Time

t

RDD

RD Low to Data Valid

OE to Data Valid

t

AA

A0ŁA13,

DMS, PMS,

Address Access Time

BMS to Data Valid

ADMC401

Ł5Ł

REV. B

Parameter

Min

Max

Unit

Clock Signals

t

CK

is defined as 0.5t

CKI.

The ADMC401 uses an input clock

with a frequency equal to half the instruction rate; a 13 MHz

clock (which is equivalent to 76.9 ns) yields a 38.5 ns processor

cycle (equivalent to 26 MHz). t

CK

values within the range of

0.5t

CKI

period should be substituted for all relevant timing

parameters to obtain specification value.

Example: t

CKH

= 0.5t

CK

Ł 10 ns = 0.5 (38.5 ns) Ł 10 ns = 9.25 ns.

Timing Requirements:

t

CKI

CLKIN Period

76.9

150

ns

t

CKIL

CLKIN Width Low

20

ns

t

CKIH

CLKIN Width High

20

ns

Switching Characteristics:

t

CKL

CLKOUT Width Low

0.5t

CK

Ł 10

ns

t

CKH

CLKOUT Width High

0.5t

CK

Ł 10

ns

t

CKOH

CLKIN High to CLKOUT High

0

20

ns

Control Signals

Timing Requirement:

t

RSP

RESET Width Low

5t

CK

1

ns

PWM Shutdown Signals

Timing Requirements:

t

PWMTPW

PWMTRIP Width Low

t

CK

ns

t

PIOPWM

PIO Width Low

2t

CK

ns

ADC Signals

Timing Requirements:

t

CSI

Internal Convert Start Width High

2t

CK

ns

t

CSE

External Convert Start Width High

2t

CK

ns

NOTE

1

Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles assuming stable CLKIN (not including crystal

oscillator start-up time).

CLKIN

CLKOUT

t

CKOH

t

CKI

t

CKIH

t

CKIL

t

CKH

t

CKL

Figure 1. Clock Signals

REV. B

ADMC401

Ł6Ł

Parameter

Min

Max

Unit

Interrupts and Flags

Timing Requirements:

t

IFS

IRQx or FI Setup before CLKOUT Low

1, 2, 3

0.25t

CK

+ 15

ns

t

IFH

IRQx or FI Hold after CLKOUT High

1, 2, 3

0.25t

CK

ns

Switching Characteristics:

t

FOH

Flag Output Hold after CLKOUT Low

4

0.5t

CK

Ł 7

ns

t

FOD

Flag Output Delay from CLKOUT Low

4

0.5t

CK

+ 5

ns

NOTES

1

If

IRQx and FI inputs meet t

IFS

and t

IFH

setup/hold requirements, they will be recognized during the current clock cycle; otherwise the signals will be recognized on

the following cycle. (Refer to "Interrupt Controller Operation" in the Program Control chapter of the ADSP-2100 Family User's Manual, Third Edition for further

information on interrupt servicing.)

2

Edge-sensitive interrupts require pulsewidths greater than 10 ns; level-sensitive interrupts must be held low until serviced.

3

IRQx = IRQ0 and IRQ1.

4

Flag Output = FL1 and FO.

CLKOUT

FLAG

OUTPUTS

IRQx

FI

t

FOH

t

IFH

t

IFS

t

FOD

Figure 2. Interrupts and Flags

ADMC401

Ł7Ł

REV. B

Parameter

Min

Max

Unit

Bus Request/Grant

Timing Requirements:

t

BH

BR Hold after CLKOUT High

1

0.25t

CK

+2

ns

t

BS

BR Setup before CLKOUT Low

1

0.25t

CK

+ 17

ns

Switching Characteristics:

t

SD

CLKOUT High to

DMS, PMS, BMS,

0.25t

CK

+ 10

ns

RD, WR Disable

t

SDB

DMS, PMS, BMS, RD, WR

Disable to

BG Low

0

ns

t

SE

BG High to DMS, PMS, BMS,

RD, WR Enable

0

ns

t

SEC

DMS, PMS, BMS, RD, WR

Enable to CLKOUT High

0.25t

CK

Ł 7

ns

t

SDBH

DMS, PMS, BMS, RD, WR

Disable to

BGH Low

2

0

ns

t

SEH

BGH High to DMS, PMS, BMS,

RD, WR Enable

2

0

ns

NOTES

1

BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized

on the following cycle. Refer to the ADSP-2100 Family User's Manual, Third Edition for

BR/BG cycle relationships.

2

BGH is asserted when the bus is granted and the processor requires control of the bus to continue.

BR

CLKOUT

PMS, DMS

BMS, RD

WR

BG

CLKOUT

BGH

t

BH

t

BS

t

SD

t

SDB

t

SDBH

t

SEH

t

SE

t

SEC

Figure 3. Bus RequestŁBus Grant

REV. B

ADMC401

Ł8Ł

Parameter

Min

Max

Unit

Memory Read

Timing Requirements:

t

RDD

RD Low to Data Valid

0.5t

CK

Ł 11 + w

ns

t

AA

A0ŁA13,

PMS, DMS, BMS to Data Valid

0.75t

CK

Ł 12 + w

ns

t

RDH

Data Hold from

RD High

0

ns

Switching Characteristics:

t

RP

RD Pulsewidth

0.5t

CK

Ł 5 + w

ns

t

CRD

CLKOUT High to

RD Low

0.25t

CK

Ł 5

0.25t

CK

+ 7

ns

t

ASR

A0ŁA13,

PMS, DMS, BMS Setup before RD Low

0.25t

CK

Ł 6

ns

t

RDA

A0ŁA13,

PMS, DMS, BMS Hold after RD Deasserted

0.25t

CK

Ł 3

ns

t

RWR

RD High to RD or WR Low

0.5t

CK

Ł 5

ns

w = wait states

ū t

CK

.

CLKOUT

A0ŁA13

D

RD

WR

DMS, PMS

BMS

t

RWR

t

RP

t

ASR

t

CRD

t

AA

t

RDA

t

RDD

t

RDH

Figure 4. Memory Read

ADMC401

Ł9Ł

REV. B

Parameter

Min

Max

Unit

Memory Write

Switching Characteristics:

t

DW

Data Setup before

WR High

0.5t

CK

Ł 7 + w

ns

t

DH

Data Hold after

WR High

0.25t

CK

Ł 2

ns

t

WP

WR Pulsewidth

0.5t

CK

Ł 5 + w

ns

t

WDE

WR Low to Data Enabled

0

ns

t

ASW

A0ŁA13,

DMS, PMS Setup before WR Low

0.25t

CK

Ł 6

ns

t

DDR

Data Disable before

WR or RD Low

0.25t

CK

Ł 6

ns

t

CWR

CLKOUT High to

WR Low

0.25t

CK

Ł 5

0.25t

CK

+ 7

ns

t

AW

A0ŁA13,

DMS, PMS, Setup before WR Deasserted

0.75t

CK

Ł 9 + w

ns

t

WRA

A0ŁA13,

DMS, PMS Hold after WR Deasserted

0.25t

CK

Ł 3

ns

t

WWR

WR High to RD or WR Low

0.5t

CK

Ł 5

ns

w = wait states

ū t

CK

.

CLKOUT

A0ŁA13

D

WR

DMS, PMS

RD

t

WRA

t

WWR

t

WP

t

ASW

t

AW

t

DH

t

DDR

t

CWR

t

WDE

t

DW

Figure 5. Memory Write

REV. B

ADMC401

Ł10Ł

Parameter

Min

Max

Unit

Serial Ports

Timing Requirements:

t

SCK

SCLK Period

50

ns

t

SCS

DR/TFS/RFS Setup before SCLK Low

5

ns

t

SCH

DR/TFS/RFS Hold after SCLK Low

10

ns

t

SCP

SCLK

IN

Width

20

ns

Switching Characteristics:

t

CC

CLKOUT High to SCLK

OUT

0.25t

CK

0.25t

CK

+ 15

ns

t

SCDE

SCLK High to DT Enable

0

ns

t

SCDV

SCLK High to DT Valid

20

ns

t

RH

TFS/RFS

OUT

Hold after SCLK High

0

ns

t

RD

TFS/RFS

OUT

Delay from SCLK High

20

ns

t

SCDH

DT Hold after SCLK High

0

ns

t

TDE

TFS(Alt) to DT Enable

0

ns

t

TDV

TFS(Alt) to DT Valid

20

ns

t

SCDD

SCLK High to DT Disable

20

ns

t

RDV

RFS (Multichannel, Frame Delay Zero) to DT Valid

20

ns

CLKOUT

SCLK

TFS

RFS

DR

RFS

IN

TFS

IN

DT

alternate

frame mode

RFS

OUT

TFS

OUT

multichannel mode,

frame delay 0

(MFD = 0)

t

CC

t

CC

t

SCS

t

SCS

t

SCK

t

SCP

t

SCP

t

RD

t

RH

t

SCDV

t

SCDE

t

TDE

t

TDV

t

RDV

t

SCDH

t

SCDD

Figure 6. Serial Ports

ADMC401

Ł11Ł

REV. B

POWER DISSIPATION

To determine total power dissipation in a specific application,

the following equation should be applied for each output:

C

ū V

DD

2

ū f

C = load capacitance, f = output switching frequency.

Example:

In an application where external data memory is used and no

other outputs are active, power dissipation is calculated as

follows:

Assumptions:

Ę External data memory is accessed every cycle with 50% of the

address pins switching.

Ę External data memory writes occur every other cycle with

50% of the data pins switching.

Ę Each address and data pin has a 10 pF total load at the pin.

Ę The application operates at V

DD

= 5.0 V and t

CK

= 38.5 ns.

Total Power Dissipation = P

INT

+ (C

ū V

DD

2

ū f)

P

INT

= V

DD

ū (I

DD

Digital + I

DD

Analog)

(C

ū V

DD

2

ū f) is calculated for each output:

# of

Pins

C

V

DD

2

f

Address,

DMS

8

ū 10 pF ū 5

2

V

ū 26 MHz

= 52.00 mW

Data Output,

WR 9

ū 10 pF ū 5

2

V

ū 13 MHz

= 29.25 mW

RD

1

ū 10 pF ū 5

2

V

ū 13 MHz

=

3.25 mW

CLKOUT

1

ū 10 pF ū 5

2

V

ū 26 MHz

=

6.50 mW

91.00 mW

Total power dissipation for this example is P

INT

+ 91 mW.

TEST CONDITIONS

Output Disable Time

Output pins are considered to be disabled when they have

stopped driving and started a transition from the measured

output high or low voltage to a high impedance state. The out-

put disable time (t

DIS

) is the difference of t

MEASURED

and t

DECAY

,

as shown in the Output Enable/Disable diagram. The time is the

interval from when a reference signal reaches a high or low

voltage level to when the output voltages have changed by 0.5 V

from the measured output high or low voltage. The decay time,

t

DECAY

, is dependent on the capacitative load, C

L

, and the cur-

rent load, i

L

, on the output pin. It can be approximated by the

following equation:

t

C

V

I

DECAY

L

L

=

ū 0 5

.

from which

t

t

t

DIS

MEASURED

DECAY

=

-

is calculated. If multiple pins (such as the data bus) are dis-

abled, the measurement value is that of the last pin to stop

driving.

3.0V

1.5V

0.0V

2.0V

1.5V

0.3V

INPUT

OUTPUT

Figure 7. Voltage Reference Levels for AC Measure-

ments (Except Output Enable/Disable)

Output Enable Time

Output pins are considered to be enabled when that have made

a transition from a high-impedance state to when they start

driving. The output enable time (t

ENA

) is the interval from when

a reference signal reaches a high or low voltage level to when

the output has reached a specified high or low trip point, as

shown in the Output Enable/Disable diagram. If multiple pins

(such as the data bus) are enabled, the measurement value is

that of the first pin to start driving.

2.0V

1.0V

t

ENA

REFERENCE

SIGNAL

OUTPUT

t

DECAY

V

OH

(MEASURED)

OUTPUT STOPS

DRIVING

OUTPUT STARTS

DRIVING

t

DIS

t

MEASURED

V

OL

(MEASURED)

V

OH

(MEASURED) Ł 0.5V

V

OL

(MEASURED) +0.5V

HIGH-IMPEDANCE STATE. TEST CONDITIONS CAUSE

THIS VOLTAGE LEVEL TO BE APPROXIMATELY 1.5V.

V

OH

(MEASURED)

V

OL

(MEASURED)

Figure 8. Output Enable/Disable

TO

OUTPUT

PIN

50pF

+1.5V

I

OH

I

OL

Figure 9. Equivalent Device Loading for AC Measure-

ments (Including All Fixtures)

REV. B

ADMC401

Ł12Ł

PIN FUNCTION DESCRIPTION

Pin

Pin

Pin

Pin

Pin

Pin

Pin

Pin

No.

Name

No.

Name

No.

Name

No.

Name

1

A9

37

RFS1/

IRQ0/SROM

73

GND

109

CONVST

2

A8

38

TFS1/

IRQ1

74

D10

110

GND

3

A7

39

SCLK1

75

D9

111

VDD

4

A6

40

DR0

76

D8

112

GND

5

VDD

41

DT0

77

D7

113

AVDD

6

A5

42

RFS0

78

D6

114

AVSS

7

A4

43

TFS0

79

D5

115

VIN7

8

A3

44

SCLK0

80

D4

116

V

REF

9

GND

45

VDD

81

D3

117

VIN6

10

A2

46

GND

82

GND

118

REFCOM

11

A1

47

PWMTRIP

83

D2

119

VIN5

12

A0

48

PWMSYNC

84

D1

120

CAPT

13

PWD

49

CL

85

D0

121

VIN4

14

PWDACK

50

CH

86

P11

122

BSHAN

15

BR

51

VDD

87

P10

123

ASHAN

16

NC

52

GND

88

P9

124

VIN0

17

NC

53

BL

89

P8

125

CAPB

18

BMODE

54

BH

90

VDD

126

VIN1

19

MMAP

55

AL

91

GND

127

CML

20

VDD

56

AH

92

P7

128

VIN2

21

GND

57

BGH

93

P6

129

GAIN

22

PWMSR

58

D23

94

P5

130

VIN3

23

POR

59

D22

95

P4

131

SENSE

24

RESET

60

D21

96

P3

132

AVSS

25

GND

61

D20

97

P2

133

AVDD

26

GND

62

D19

98

GND

134

BMS

27

GND

63

GND

99

P1

135

PMS

28

PWMPOL

64

D18

100

P0

136

DMS

29

CLKIN

65

D17

101

AUX1

137

RD

30

XTAL

66

D16

102

AUX0

138

GND

31

CLKOUT

67

D15

103

ETU1

139

BG

32

VDD

68

D14

104

ETU0

140

WR

33

GND

69

D13

105

EIS

141

A13

34

DR1A/FI

70

D12

106

EIZ

142

A12

35

DRIB/FI

71

VDD

107

EIB

143

A11

36

DT1/FO

72

D11

108

EIA

144

A10

NC: These pins must be left unconnected

ADMC401

Ł13Ł

REV. B

PIN CONFIGURATION

A9

A8

A7

A6

VDD

A5

A4

A3

GND

A2

A1

A0

PWD

PWDACK

BR

NC

NC

BMODE

MMAP

VDD

GND

PWMSR

POR

RESET

GND

GND

GND

PWMPOL

CLKIN

XTAL

CLKOUT

VDD

GND

DR1A/F1

DR1B/FI

DT1/FO

P1

GND

P2

P3

P4

P5

P6

P7

GND

VDD

P8

P9

P10

P11

D0

D1

D2

GND

D3

D4

D5

D6

D7

D8

D9

D10

GND

EIA

EIB

EIZ

EIS

ETU0

ETU1

AUX0

AUX1

P0

D11

VDD

D12

D13

D14

D15

D16

D17

D18

GND

D19

D20

D21

D22

D23

BGH

AH

AL

BH

BL

GND

VDD

CH

CL

PWMSYNC

PWMTRIP

GND

VDD

SCLK0

TFS0

RFS0

DT0

DR0

SCLK1

TFS1/

IRQ1

RFS1/I

RQ0/SROM

CONVST

GND

VDD

GND

AVDD

AVSS

VIN7

V

REF

VIN6

REFCOM

VIN5

CAPT

VIN4

BSHAN

ASHAN

VIN0

CAPB

VIN1

CML

VIN2

GAIN

VIN3

SENSE

AVSS

AVDD

BMS

PMS

DMS

RD

GND

BG

WR

A13

A12

A11

A10

NC = NO CONNECT

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

ADMC401

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

10

11

12

13

14

15

16

17

18

1

2

3

4

5

6

7

8

9

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

99

98

97

96

95

94

93

92

91

108

107

106

105

104

103

102

101

100

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

REV. B

ADMC401

Ł14Ł

(Continued from Page 1)

Programmable Digital I/O (PIO) Port

12-Pin Configurable Digital I/O Port

Flexible Interrupt Generation

Four Dedicated PIO Interrupt Vectors

Each I/O Line Configurable as PWM Shutdown

Two 8-Bit Auxiliary PWM Outputs

Programmable Switching Frequency

Independent or Offset Modes

Two-Channel Event Timer (Capture) Unit

Configurable Event Definition

Single-Shot or Free-Running Modes

Peripheral Interrupt Controller

Manages Peripheral Interrupts

16-Bit Watchdog Timer

Internal Power-On Reset System

Programmable 16-Bit Interval Timer with Prescaler

Two Double Buffered Synchronous Serial Ports

Boot Load Protocols via SPORT1:

Synchronous E

2

PROM/SROM Booting

UART Boot Loader with Autobaud

Synchronous Master or Slave Boot Loader

Debugger Interface via SPORT1:

UART Interface with Autobaud

Synchronous Master or Slave Interface

Full Debugger for Program Development

Industrial Temperature Range Ł40 C to +85 C

Operating Voltage 5.0 V

5%

Package: 144-Lead LQFP

GENERAL DESCRIPTION

The ADMC401 is a single-chip DSP-based controller, suitable

for high performance control of ac induction motors (ACIM),

permanent magnet synchronous motors (PMSM), brushless dc

motors (BDCM) and switched reluctance (SR) motors in indus-

trial applications. The ADMC401 integrates a 26 MIPS, fixed-

point DSP core with a complete set of motor control peripherals

that permits fast motor control in a highly integrated environment.

The DSP core of the ADMC401 is the ADSP-2171 which is

completely code compatible with the ADSP-21xx DSP family

(as well as other members of the integrated motor controllers of

the ADMC3xx family) and combines three computational units,

data address generators and a program sequencer. The computa-

tional units comprise an ALU, a multiplier/accumulator (MAC)

and a barrel shifter. The DSP core also adds instructions for bit

manipulation, squaring (x

2

), biased rounding and global inter-

rupt masking. In addition, two flexible double-buffered, bidirec-

tional synchronous serial ports are included in the ADMC401.

The ADMC401 provides 2K

ū 24-bit internal program memory

RAM, 2K

ū 24-bit internal program memory ROM and 1K ū

16-bit internal data memory RAM. The program and data

memory RAM can be boot loaded through the serial port from

either a serial E

2

PROM, through a UART connection (either

from external host microprocessor or from the Motion Control

Debugger) or via a synchronous serial interface from a host

microprocessor. Alternatively, the internal program and data

memory RAM may be booted from an external device across the

address and data buses. The program memory ROM includes a

monitor that adds software debugging features through the serial

port.

Additionally, the ADMC401 device adds significant external

memory and peripheral expansion capabilities by making avail-

able the full address and data bus of the DSP core. This feature

permits expansion of both external program and data memory

and means that the DSP core can address up to 14K

ū 24 bits of

external program memory and up to 13K

ū 16 bits of external

data memory.

The ADMC401 contains a number of special purpose, motor

control peripherals. The first is a high performance, 8-channel,

12-bit ADC system with dual channel simultaneous sampling

ability across 4 pair of inputs. An internal precision voltage refer-

ence is also available as part of the ADC system. In addition, a

three-phase, 16-bit, center-based PWM generation unit can be

used to produce high-accuracy PWM signals with minimal pro-

cessor overhead. The ADMC401 also contains a flexible incre-

mental encoder interface unit for position sensor feedback;

two adjustable-frequency auxiliary PWM outputs, 12 lines of

digital I/O; a 2-channel event capture system; a 16-bit watchdog

timer; two 16-bit interval timers (one of which can be linked to

the encoder interface unit) and an interrupt controller that man-

ages all peripheral interrupts. Finally, the ADMC401 contains

an integrated power-on-reset (POR) circuit that can be used to

generate the required reset signal for the device on power-on.

ADMC401

Ł15Ł

REV. B

BUS

EXCHANGE

DATA

ADDRESS

GENERATOR

#2

DATA

ADDRESS

GENERATOR

#1

14

14

24

16

6

R BUS

16

COMPANDING

CIRCUITRY

DMA BUS

PMA BUS

DMD BUS

PMD BUS

PROGRAM

SEQUENCER

INSTRUCTION

REGISTER

INPUT REGS

OUTPUT REGS

SHIFTER

INPUT REGS

OUTPUT REGS

MAC

INPUT REGS

OUTPUT REGS

ALU

SERIAL

PORT 0

RECEIVE REG

TRANSMIT REG

CONTROL

LOGIC

DM RAM

1K 16

PM ROM

2K 24

PM RAM

2K 24

SERIAL

PORT 1

RECEIVE REG

TRANSMIT REG

5

TIMER

BOOT

ADDRESS

GENERATOR

14

24

2

POWER DOWN

CONTROL

LOGIC

EXTERNAL

DATA BUS

EXTERNAL

ADDRESS BUS

Figure 10. DSP Core Block Diagram

ARCHITECTURE OVERVIEW

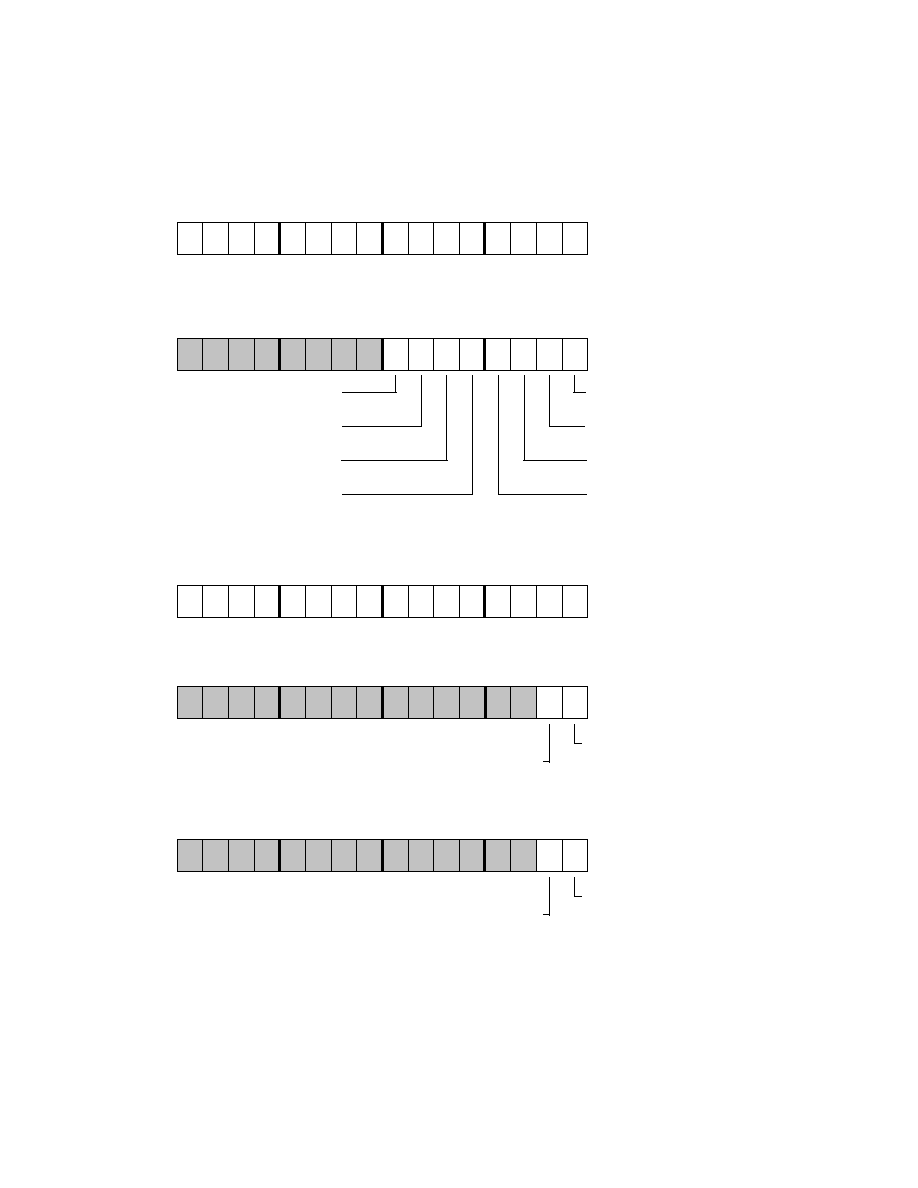

Figure 10 is a functional block diagram of the DSP core of the

ADMC401. The DSP core is based on the fixed-point ADSP-

2171 core that is a member of the fixed-point ADSP-21xx

family of general purpose DSPs from Analog Devices Inc.

The ADSP-2171 flexible architecture and comprehensive in-

struction set allow the processor to perform multiple operations

in parallel.

In one processor cycle (38.5 ns with a 13 MHz crystal) the DSP

core can:

Ę Generate the next program address.

Ę Fetch the next instruction.

Ę Perform one or two data moves.

Ę Update one or two data address pointers.

Ę Perform a computational operation.

This all takes place while the ADMC401 continues to:

Ę Receive and transmit through the serial ports.

Ę Decrement the interval timers.

Ę Generate PWM signals.

Ę Convert the ADC input signals.

Ę Operate the encoder interface unit.

Ę Operate all other peripherals including the auxiliary PWM and

event timer subsystem.

The processor contains three independent computational units:

the arithmetic and logic unit (ALU), the multiplier/accumulator

(MAC) and the shifter. The computational units process 16-bit

data directly and have provisions to support multiprecision

computations. The ALU performs a standard set of arithmetic

and logic operations; division primitives are also supported. The

MAC performs single-cycle multiply, multiply/add, multiply/

subtract operations with 40 bits of accumulation. The shifter

performs logical and arithmetic shifts, normalization, denormal-

ization and derive exponent operations. The shifter can be used

to implement numeric format control efficiently, including

floating-point representations. The internal result (R) bus di-

rectly connects the computational units so that the output of

any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient delivery of operands to these compu-

tational units. The sequencer supports conditional jumps, sub-

routine calls and returns in a single cycle. With internal loop

counters and loop stacks, the ADMC401 executes looping code

with zero overhead; no explicit jump instructions are required to

maintain the loop.

REV. B

ADMC401

Ł16Ł

Two data address generators (DAGs) provide addresses for

simultaneous dual operand fetches from data memory and pro-

gram memory. Each DAG maintains and updates four address

pointers (I registers). Whenever the pointer is used to access

data (indirect addressing), it is post-modified by the value in

one of four modify (M) registers. A length value may be associ-

ated with each pointer (L registers) to implement automatic

modulo addressing for circular buffers. The circular buffering

feature is also used by the serial ports for automatic data trans-

fers to and from on-chip memory. DAG1 generates only data

memory addresses but provides an optional bit-reversal capabil-

ity. DAG2 may generate either program or data memory ad-

dresses, but has no bit-reversal capability.

Efficient data transfer is achieved with the use of five internal

buses:

Ę Program Memory Address (PMA) Bus.

Ę Program Memory Data (PMD) Bus.

Ę Data Memory Address (DMA) Bus.

Ę Data Memory Data (DMD) Bus.

Ę Result (R) Bus.

Program memory can store both instructions and data, permit-

ting the ADMC401 to fetch two operands in a single cycle, one

from internal program memory and one from internal data

memory. The ADMC401 can fetch an operand from on-chip

program memory and the next instruction in the same cycle.

The ADMC401 writes data from its 16-bit registers to the 24-

bit program memory using the PX register to provide the lower

eight bits. When it reads data (not instructions) from 24-bit

program memory to a 16-bit data register, the lower eight bits

are placed in the PX register.

The ADMC401 can respond to a number of distinct DSP core

and peripheral interrupts. The DSP core interrupts include

serial port receive and transmit interrupts, timer interrupts,

software interrupts and external interrupts. In addition, there is

a master

RESET signal. The motor control peripherals also

produce interrupts to the DSP core.

The two serial ports (SPORTs) provide a complete synchronous

serial interface with optional companding in hardware and a

wide variety of framed and unframed data transmit and receive

modes of operation. Each SPORT can generate an internal

programmable serial clock or accept an external serial clock.

Boot loading of both the program and data memory RAM of the

ADMC401 can be through the serial port SPORT1. Alterna-

tively the ADMC401 can be boot loaded from an external byte-

wide memory connected to the external address and data buses.

After reset, seven wait states are automatically generated. This

permits, for example, a 38.5 ns ADMC401 to use an external

250 ns EPROM as boot memory. The internal boot address

generator provides the addresses for booting from an external

byte-wide memory.

A programmable interval counter is also included in the DSP

core and can be used to generate periodic interrupts. A 16-bit

count register (TCOUNT) is decremented every n processor

cycles, where n-1 is a scaling value stored in the 8-bit TSCALE

register. When the value of the counter reaches zero, an inter-

rupt is generated and the count register is reloaded from a 16-

bit period register (TPERIOD).

The ADMC401 instruction set provides flexible data moves and

multifunction (one or two data moves with a computation)

instructions. Each instruction is executed in a single 38.5 ns

processor cycle (for a 13 MHz crystal). The ADMC401 assem-

bly language uses an algebraic syntax for ease of coding and

readability. A comprehensive set of development tools supports

program development.

Serial Ports

The ADMC401 incorporates two complete synchronous serial

ports (SPORT0 and SPORT1) for serial communications and

multiprocessor communication. The following is a brief list of

the capabilities of the ADMC401 SPORTs. Refer to the ADSP-

2100 Family User's Manual, Third Edition for further details.

Ę SPORTs are bidirectional and have a separate, double-

buffered transmit and receive section.

Ę

SPORTs can use an external serial clock or generate their

own serial clock internally.

Ę

SPORTs have independent framing for the receive and trans-

mit sections. Sections run in a frameless mode or with frame

synchronization signals internally or externally generated.

Frame synchronization signals are active high or inverted,

with either of two pulsewidths and timings.

SPORTs support serial data word lengths from 3 bits to 16

bits and provide optional A-law and

Ą-law companding.

Ę

SPORT receive and transmit sections can generate unique

interrupts on completing a data word transfer.

Ę

SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data word. An inter-

rupt is generated after a data buffer transfer.

Ę

SPORT0 has a multichannel interface to selectively receive

and transmit a 24-word or 32-word, time-division multi-

plexed, serial bitstream.

Ę

SPORT1 can be configured to have two external interrupts

(

IRQ0 and IRQ1), and the Flag In and Flag Out signals. The

internally generated serial clock may still be used in this

configuration.

The following are additional capabilities of the ADMC401

SPORTs that are not part of the ADSP-21xx products:

Ę

SPORT1 is the input for single pin program and data

memory boot loading. The RFS1 pin can be configured

internally to the ADMC401 as an SROM/E

2

PROM reset

signal.

Ę

SPORT1 has two data receive pins (DR1A and DR1B). The

DR1A pin is intended only for synchronous data receive

from the external E

2

PROM. The DR1B pin can be used as

the data receive pin for a general purpose SPORT after boot-

ing or as the data receive pin for other boot load modes or as

the UART/debugger interface. The DR1A and DR1B pins

are internally multiplexed onto the one data receive pin of

the SPORT. The particular data receive pin selected is deter-

mined by Bit 4 of the MODECTRL register.

ADMC401

Ł17Ł

REV. B

PIN FUNCTION DESCRIPTION

The ADMC401 is available in an 144-lead TQFP package. Table

I contains the pin descriptions.

Table I. Pin List

Pin

#

Group

of

Input/

Name

Pins Output Function

A13ŁA0

14

O

Address Lines

D23ŁD0

24

I/O

Data Lines

PMS, DMS, BMS 3

O

External Memory Select Lines

RD, WR

2

O

External Memory Read/Write Enable

MMAP

1

I

Memory Map Select

POR

1

O

Internal Power On Reset Output

RESET

1

I

Processor Reset Input

CLKOUT

1

O

Processor Clock Output

CLKIN, XTAL

2

I, O

External Clock or Quartz Crystal

Input

BR

1

I

Bus Request

BG, BGH

2

O

Bus Grant and Bus Hang Control

BMODE

1

I

Boot Mode Select

PWD, PWDACK

2

I, O

Power-Down and Power-Down

Acknowledge

SPORT0

5

I/O

Serial Port 0 Pins (TFS0, RFS0,

DT0, DR0, SCLK0)

SPORT1

6

I/O

Serial Port 1 (TFS1/

IRQ1, RFS1/

IRQ0/SROM, DT1/FO, DR1A/FI,

DR1B/FI, SCLK1)

VIN0ŁVIN7

8

I

Analog Inputs

ASHAN, BSHAN

2

I

Inverting Inputs to Sample and

Hold Amplifiers

GAIN

1

I

Analog Input for Gain Calibration

V

REF

1

I/O

Reference Voltage Input/Output

REFCOM

1

GND

Reference Common

CML

1

O

Common-

Mode

Level (Midsupply)

CAPT, CAPB

2

O

Noise Reduction Pins

SENSE

1

I

Voltage Reference Select

CONVST

1

I

External Convert Start

AH-CL

6

O

PWM Outputs

PWMTRIP

1

I

PWM Shutdown Signal

PWMPOL

1

I

PWM Polarity Control

PWMSYNC

1

O

PWM Synchronization Output

PWMSR

1

I

PWM Switched Reluctance Mode

Control

PIO0ŁPIO11

12

I/O

Digital I/O Port

ETU0, ETU1

2

I

Event Timer Inputs

AUX0ŁAUX1

2

O

Auxiliary PWM Outputs

EIA, EIB, EIZ,

EIS

4

I

Encoder Interface Inputs and

External Registration Inputs

NC

2

No Connect

AVDD

2

SUP

Analog Power Supply

AVSS

2

GND

Analog Ground

VDD

8

SUP

Digital Power Supply

GND

16

GND

Digital Ground

INTERRUPT OVERVIEW

The ADMC401 can respond to different interrupt sources, some

of which are internal DSP core interrupts and others from the

motor control peripherals. The DSP core interrupts include a:

Ę

Power up (or

RESET) interrupt.

Ę

A peripheral (or

IRQ2) interrupt.

Ę

A SPORT0 receive and a SPORT0 transmit interrupt.

Ę

A SPORT1 receive (or

IRQ0) and a SPORT1 transmit (or

IRQ1) interrupt.

Ę

Two software interrupts.

Ę

An interval timer timeout interrupt.

Ę

A power-down interrupt.

In addition, the motor control peripherals add other interrupts

that include:

Ę A PWMSYNC interrupt.

Ę An ADC end of conversion interrupt.

Ę An encoder loop timer timeout interrupt.

Ę Five peripheral input/output (PIO) interrupts.

Ę An event timer interrupt.

Ę An encoder count error interrupt.

Ę A PWM trip interrupt.

The interrupts are internally prioritized and individually maskable

except for the nonmaskable power-down interrupt.

Memory Map

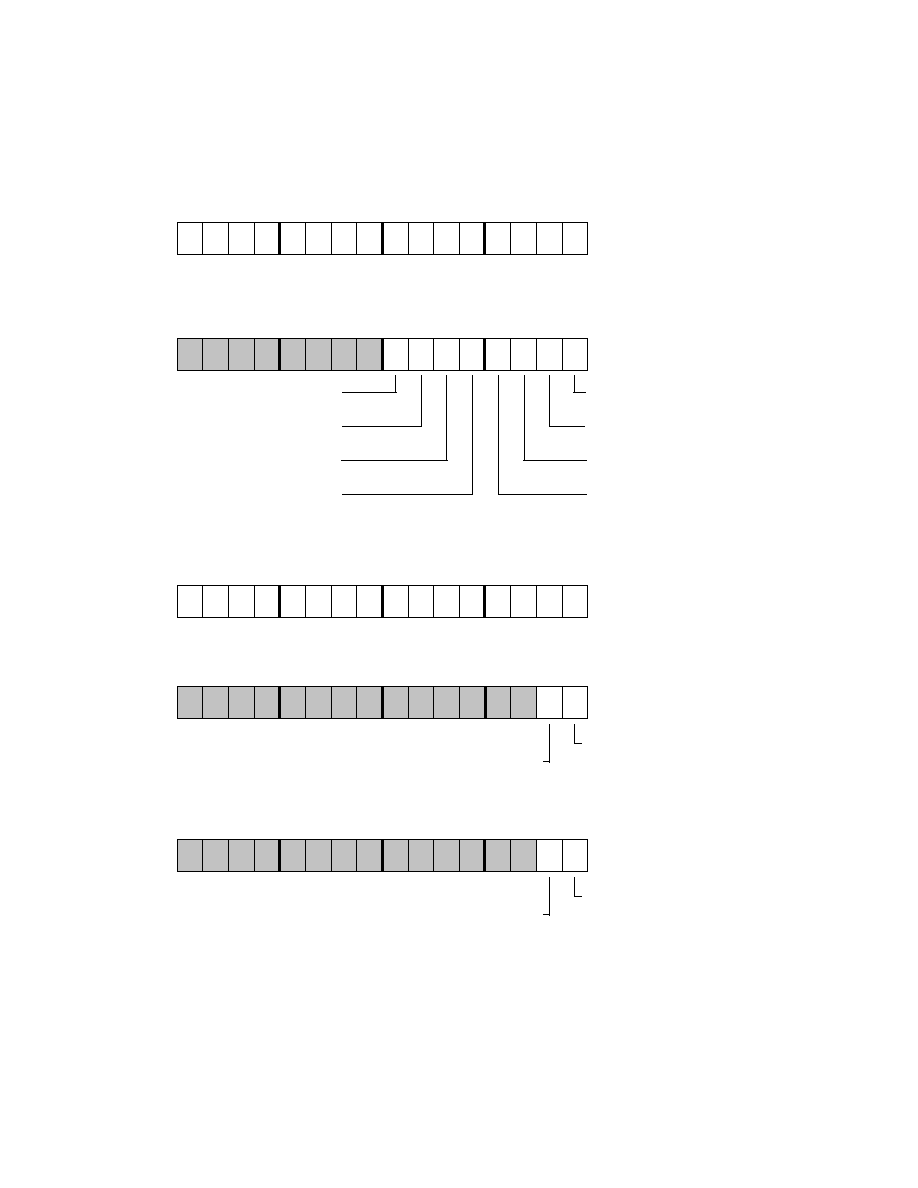

The ADMC401 has two distinct memory types; program memory

and data memory (in addition to external boot memory). In

general, program memory contains user code and coefficients,

while the data memory is used to store variables and data during

program execution. Both program memory RAM and ROM is

provided internally on the ADMC401. The program memory

map of the ADMC401 can be altered depending on the state of

the MMAP and BMODE pins. The various program memory

maps are illustrated in Figure 11 for the permissible settings of

MMAP and BMODE. The state of these pins also impact the

way in which the internal memory of the ADMC401 is booted,

as described later.

There is 2K of internal ROM on the ADMC401. Setting the

ROMENABLE bit on the Data Memory Wait State Control

Register (at address DM (0x3FFE)) enables the ROM. When the

ROMENABLE bit is set to 1, addressing program memory in the

ROM range will access the on-chip ROM. When ROMENABLE

is set to zero, addressing program memory in this range will

access external program memory. The ROMENABLE bit is

initialized to zero after reset unless MMAP and BMODE = 1.

When MMAP = BMODE = 0, the ADMC401 provides 2K

ū 24

bits of internal program memory RAM starting at address

0x0000 that is booted from a byte-wide interface on the address

and data buses. Following boot loading, program execution

starts at address 0x0000. In this mode, the remainder of the

program memory space, a 12K

ū 24-bit block starting at address

0x1000, is assigned to external memory.

When MMAP = BMODE = 1, the program memory map is

identical to the previous case, but ROMENABLE defaults to 1 at

reset, and execution starts from the internal program memory

ROM located at address 0x0800. This permits the internal (and

external if desired) memory to be boot loaded across the various

serial interfaces on SPORT1.

REV. B

ADMC401

Ł18Ł

When MMAP = 1 and BMODE = 0, the internal program

memory RAM is mapped to the top of the program memory space

(starting at address 0x3800) and no boot loading occurs. Program

execution starts from external program memory at address 0x0000.

Only with ROMENABLE = 1 are the internal ROM monitor

and debugger features of the ADMC401 available for program

development. Additionally, certain spaces of the memory map

have predefined functions as illustrated in Figure 12 where it

can be seen that address space 0x0000 to 0x005F is reserved for

the interrupt vector table.

VECTOR TABLE

USER

PROGRAM

SPACE

0x000

ROM

MONITOR

RESERVED

EXTERNAL

MEMORY

0x05F

0x060

0x7FF

0x800

0xFEF

0xFF0

0xFFF

0x1000

Figure 12. Detailed View of Program Memory Map with

MMAP = BMODE = 1

The program memory interface can generate 0 to 7 wait states

for external memory devices. The program memory wait state

field (PWAIT) in the System Control Register controls the number

of inserted wait states and defaults to 7. The structure of the

System Control Register is shown at the end of the data sheet.

The data memory map of the ADMC401 is shown in Figure 13.

The internal data memory RAM of the ADMC401 is arranged

as a single 1K

ū 16-bit block starting at address 0x3800. In

addition, there are two 1K blocks of reserved data memory

space; one block starting at address 0x2000 that is reserved for

the peripheral registers and one starting at address 0x3C00 that

is reserved for internal DSP core registers. Data memory wait

states are controlled by the DWAIT0, DWAIT1, DWAIT2,

DWAIT3 and DWAIT4 fields of the Data Memory Wait State

Register (MEMWAIT) as illustrated in Figure 13. Following

reset, DWAIT0 = DWAIT1 = DWAIT2 = DWAIT 3 =

DWAIT4 = 7. However, in standalone mode with MMAP =

BMODE = 1, the internal monitor code writes 0 to these five

fields. For correct operation DWAIT2 must always be 0. The

configuration of the MEMWAIT register is shown at the end of

the data sheet.

0x0000

8K EXTERNAL

MEMORY

0x23FF

0x2400

0x1FFF

0x2000

PERIPHERAL

REGISTERS

5K EXTERNAL

MEMORY

DSP CORE

REGISTERS/

RESERVED

INTERNAL USER

RAM

0x37FF

0x3800

0x3BFF

0x3C00

0x3FFF

0x3B5F

0x3B60

RESERVED BY

MONITOR

0x0000

0x03FF

0x0400

DWAIT0

0x2FFF

0x3000

0x3FFF

DWAIT1

DWAIT2

NO WAIT

STATES

0x07FF

0x0800

DWAIT3

DWAIT4

0x3400

0x3800

Figure 13. Data Memory Map of the ADMC401

ROM Code

The 2K

ū 24-bit block of internal program memory ROM start-

ing at address 0x800 contains a monitor function that can be

used to download and execute user programs via the serial port.

In addition, the monitor function supports an interactive mode

in which commands are received and processed from a host that

is configured as a UART device. An example of such a host is

the Windows-based Motion Control Debugger that is part of

the software development system for the ADMC401. In the

interactive mode, the host can access both the internal DSP and

peripheral motor control registers of the ADMC401, read and

write to both program and data memory, implement break-

points and perform single-step operation as part of the program

debugging cycle. Again, this debugging feature is only available

when ROMENABLE = 1.

2K INTERNAL RAM

(BOOTED FROM

BYTE-WIDE EPROM)

2K INTERNAL ROM

(ROMENABLE = 1)

OR

2K EXTERNAL

(ROMENABLE = 0)

12K EXTERNAL

MEMORY

0x0000

0x0FFF

0x1000

0x07FF

0x0800

0x3FFF

MMAP = 0

BMODE = 0

2K EXTERNAL

MEMORY

10K EXTERNAL

MEMORY

0x0000

0x0FFF

0x1000

0x07FF

0x0800

0x3FFF

MMAP = 1

BMODE = 0

2K INTERNAL RAM

(BOOTED VIA

SPORT1)

2K INTERNAL ROM

(ROMENABLE

DEFAULTS TO 1

DURING RESET)

0x0000

0x0FFF

0x1000

0x07FF

0x0800

0x3FFF

MMAP = 1

BMODE = 1

0x3800

2K INTERNAL RAM

2K INTERNAL ROM

(ROMENABLE = 1)

OR

2K EXTERNAL

(ROMENABLE = 0)

12K EXTERNAL

MEMORY

Figure 11. Program Memory Map of ADMC401

ADMC401

Ł19Ł

REV. B

SYSTEM INTERFACE

CLOCK SIGNALS

The ADMC401 uses an input clock with a frequency equal to

half the instruction rate; a 13 MHz input clock yields a 38.5 ns

processor cycle (which is equivalent to 26 MHz). Normally

instructions are executed in a single processor cycle. All device

timing is relative to the internal instruction rate, which is indi-

cated by the CLKOUT signal (when enabled). Throughout this

data sheet, the period of the CLKIN signal is denoted by t

CKI

.

The DSP instruction period is t

CK

(the period of the CLKOUT

signal), and t

CK

= 0.5

ū t

CKI

. For 26 MIPS operation, a 13 MHz

CLKIN signal is used, corresponding to t

CKI

= 76.9 ns and t

CK

= 38.5 ns. Additionally, t

CK

is the fundamental time increment

of the motor control peripherals. Therefore, unless otherwise

specified, the motor control peripherals are clocked at a rate

equal to CLKOUT. The ADMC401 can be clocked by either a

crystal or by an external clock source. The CLKIN input cannot

be halted, changed in frequency, or operated below the specified

minimum frequency during normal operation.

If an external clock source is used, it should be a TTL-compatible

signal running at half the instruction rate. The signal is con-

nected to the CLKIN pin of the ADMC401. In this mode, with

an external clock signal, the XTAL pin must be left unconnected.

Because the ADMC401 includes an on-chip oscillator circuit,

an external crystal may be used instead of a clock source. The

crystal should be connected across the CLKIN and XTAL pins.

A parallel-resonant, fundamental frequency, microprocessor-

grade crystal should be used. The frequency value selected for

the crystal should be equal to half the desired instruction rate

for the processor. Figure 15 shows a 13 MHz crystal properly

connected to yield a 26 MHz processor rate.

The CLKOUT output can be enabled and disabled by the

CLKODIS bit of the SPORT0 Autobuffer Control Register,

DM (0x3FF3). However, extreme care must be exercised when

using this bit (and is thus discouraged) since disabling CLKOUT

effectively disables all motor control peripherals, except the

watchdog timer.

RESET AND POWER-ON RESET CIRCUIT

The

RESET pin initiates a complete hardware reset of the

ADMC401 when pulled low. The

RESET signal must be asserted

when the device is powered up to assure proper initialization.

The ADMC401 contains an integrated power-on reset circuit

that provides an output reset signal,

POR, from the ADMC401

on power up and if the power supply voltage falls below the

threshold level. The ADMC401 may be reset from an external

source using the

RESET signal or alternatively the internal

power-on reset circuit may be used by connecting the

POR pin

to the

RESET pin. During power-up the RESET line must be

activated for long enough to allow the DSP core's internal clock

to stabilize. The power-up sequence is defined as the total time

required for the crystal oscillator to stabilize after a valid V

DD

is

applied to the processor and for the internal phase locked loop

(PLL) to lock onto the specific crystal frequency. A minimum of

2000t

CKI

cycles will ensure that the PLL has locked (this does not

include the crystal oscillator start-up time).

The operation of the internal power-on reset circuit is illustrated

in Figure 14. On power-up, the circuit maintains the

POR pin

low until it detects that the V

DD

line has attained the threshold

voltage, V

RST

level. As soon as the threshold voltage is attained,

the power on reset circuit enables a 17-bit counter that is

clocked at the CLKOUT rate. While the counter is counting the

POR pin is held low. When the counter overflows, after a time:

t

ms

RST

=

ū

ū

=

2

38 5

10

2 52

16

9

.

.

Ł

the

POR pin is brought high and if the POR and RESET pins

are connected, the device is brought out of reset.

The internal power-on reset circuit also acts as a power supply

monitor and puts the

POR pin at a LO level if it detects a volt-

age less than V

RST

ŁV

HYST

, where V

HYST

is the hysteresis voltage

built into the POR circuit. The supply voltage must then exceed

V

RST

to initiate another power-on reset sequence.

VDD

POR

t

RST

t

RST

V

RST

V

RST

- V

HYST

Figure 14. Operation of Power-On Reset (POR) Circuit of

ADMC401

The master reset (

RESET = LO) causes a Full System Reset,

which sets all internal stack pointers to the empty stack condi-

tion, masks all interrupts, clears the MSTAT register, restores

the program counter to its initial value and performs a full reset

of all of the motor control peripherals including the watchdog

timer. Following a power-up, it is possible to initiate a Full

System Reset by simply pulling the

RESET low. For these

resets, there is no need to wait for PLL stabilization and the

RESET signal must meet the minimum pulsewidth specifica-

tion, t

RSP

. To generate the external

RESET signal, it is recom-

mended to use either an RC circuit with a Schmitt trigger or a

commercially available reset IC.

Separate from a Full System Reset, a software controlled Periph-

eral Reset (excluding the watchdog timer) is achieved by toggling

the DSP FL2 flag with the following code segment:

PRESET:

SET FL2;

TOGGLE FL2;

TOGGLE FL2;

RTS;

A full DSP and peripheral reset (except the watchdog timer

itself) will occur automatically on a watchdog trip.

EXTERNAL MEMORY INTERFACE

The ADMC401 can address 14K

ū 24 bits of external program

memory and up to 13K

ū 16 bits of external data memory. The

ADMC401 provides the address on a 14-bit address bus

(A13ŁA0). Instructions or data are transferred across the 24-bit

data bus (D23ŁD0) during program memory accesses. During

data memory accesses, data is transferred on the 16 most signifi-

cant bits (D23ŁD8) of the data bus. For a dual off-chip fetch,

the data from program memory is read first, then the data from

data memory. The program memory select pin,

PMS, is acti-

vated during external program memory accesses and can be

used as a chip select signal for the external program memory

devices. Similarly, for external data memory accesses, the

DMS

pin is activated.

REV. B

ADMC401

Ł20Ł

Two control lines indicate the direction of the transfer. Memory

read,

RD, is active low, signaling a read from external memory

and memory write;

WR, is active low, signaling a write to exter-

nal memory. Typically, the

PMS line is connected to the CE

(chip enable) of the external program memory and the

RD line

is connected to the

CE line of the external data memory. The

RD line is connected to the OE (output enable) and the WR

line is connected to the

WE (write enable) of both memories.

On-chip accesses (to internal program memory RAM and ROM)

do not drive any of the external signals. The

PMS, RD and the

WR lines remain high (deasserted) and the address and data

buses are three-stated during these internal accesses. Similarly,

internal accesses to data memory (including internal DM RAM

and peripheral and DSP core memory mapped registers) do not

drive external signals and the

DMS, RD and the WR lines re-

main high (deasserted) and the address and data buses are also

three-stated.

External peripherals can also be connected externally and memory

mapped to the external memory space of the ADMC401. The

16 MSBs of the external data bus are connected internally to the

16 bits of the internal data memory bus. Therefore, the data

lines D23ŁD8 should be used for 16-bit peripherals.

BOOT LOADING

Standalone Mode (MMAP = BMODE = 1)

Boot loading of the ADMC401 may occur in a number of differ-

ent ways and is determined by the state of both the MMAP and

BMODE pins. If both MMAP and BMODE are tied to V

DD

(HI), the ADMC401 is placed in the so-called standalone mode

and execution starts from internal program memory ROM at

address 0x0800 following a power-on or reset. This starts execu-

tion of the internal monitor function that first performs some

initialization functions (including writing 0 to the three data

memory wait state fields) and copies a default interrupt vector

table to addresses 0x0000Ł0x005F of program memory RAM.

The monitor program next clears Bit 4 of the MODECTRL

register to connect the DR1A pin to the internal data receive

port (DR1) of SPORT1. In addition, Bit 5 of the MODECTRL

register is set. This connects the FL1 port of the DSP core to

the RFS1/SROM pin to act as a reset for a serial memory device.

The monitor next attempts to boot load from an external Serial

ROM (SROM) or Serial E

2

PROM on SPORT1 using the three

wire connection of Figure 15. This SROM or E

2

PROM should be

programmed with the protocol of the MAKEPROM utility

provided with the Motion Control Debugger. The monitor

program first toggles the RFS1/

SROM pin of the ADMC401 to

reset the serial memory device with the following code segment:

SROMRESET:

SET FL1;

TOGGLE FL1;

TOGGLE FL1;

RTS;

If a properly programmed SROM or E

2

PROM is connected to

SPORT1, data is clocked synchronously into the ADMC401 at

a rate of 1 Mb/s. Both internal and external program and data

memory RAM can be loaded from the SROM/E

2

PROM, up to

the available capacity of the serial memory device. After the

entire boot load is complete, program execution begins at ad-

dress 0x0060. This is where the first instruction of the user code

should be placed.

V

DD

CLKOUT

MMAP

BMODE

RESET

XTAL

CLKIN

DR1A

SCLK1

RFS1/

SROM

SERIAL ROM

OR

E

2

PROM

ADMC401

13MHz

20pF

20pF

DATA

CLK

RESET

Figure 15. Basic System Configuration in Standalone

Mode

If boot loading from an SROM or E

2

PROM is unsuccessful, the

monitor code reconfigures SPORT1 as a UART (setting both

Bit 4 and Bit 5 of the MODECTRL register) and attempts to

receive commands from an external device on this serial port

using the DR1B pin. The monitor now waits for two bytes of

information. These bytes are received asynchronously so that no

clock is needed. The first byte is the autobaud byte and it is

used to calculate the baud rate at which data is being received.

This is known as the autobaud feature. The ADMC401 will

automatically lock onto the baud rate of the external device if

it is sent a byte of 0x70. The maximum baud rate that the

ADMC401 will lock onto is 300 kb/s for a 26 MHz CLKOUT.

The second byte of information received is the header byte that

uniquely identifies to the monitor which type of interface it is

connected to. There are six different interfaces supported on the

ADMC401. These includes:

Ę

A UART boot loader such as from a Motorola 68HC11

communicating over its Serial Communications Interface

(SCI) port.

Ę

A synchronous slave boot loader (the clock is external).

Ę

A synchronous master boot loader (the ADMC401 provides

the clock).

Ę

A UART debugger interface such as the Motion Control

Debugger from Analog Devices. The monitor then processes

commands received from the debugger over the UART

interface.

Ę

A synchronous master debugger interface.

Ę

A synchronous slave debugger interface.

Detailed information on these software interfaces can be

found in the "UART Boot Loader Protocol" and "UART

Debugger Protocol" appendices of the ADMC401 Developer's

Reference Manual.

Byte-Wide EPROM Boot Mode (MMAP = BMODE = 0)

If both the MMAP and BMODE pins are tied to GND, the

ADMC401 operates in the so-called EPROM Boot mode. In this

mode the entire internal program memory, or any portion of it,

can be loaded from an external source using a boot sequence

over the memory interface. To allow boot loading from inexpen-

sive 8-bit wide EPROM devices, the processor loads data one

byte at a time. The boot sequence can also be initiated after

reset by software.

Boot memory is organized into eight pages, each of which is 8k

bytes long. Every fourth byte of a page is an empty byte except

for the first one, which contains the page length. Each set of

three bytes between successive empty bytes contains one 24-bit

instruction to be loaded into the internal PM RAM of the DSP.

ADMC401

Ł21Ł

REV. B

The page length is read first and then bytes are loaded from the

top of the page downwards. This causes shorter booting times

for shorter pages. The length of the boot page is given as:

page length = (number of 24-bit PM words/8) Ł 1

That is, a page length of 0 causes the boot address generator to

generate byte addresses for eight words that reside in 32 sequen-

tial EPROM locations.

A PROM splitter utility (SPL21), part of the Motion Control

Debugger tool set, calculates the proper page length for your

program and orders the bytes of your program according to the

proper protocol. More detailed information about the use of

this PROM splitter utility can be found in the "Booting from

External EPROM with MMAP = BMODE = 0" chapter of the

ADMC401's Developer's Reference Manual.

Following a reset, if both MMAP and BMODE are LO, the

boot sequence always boot loads page 0. After reset, boot load-

ing can occur under program control from any one of up to

eight different boot pages. The boot page select field (BPAGE)

in the memory mapped System Control Register specifies which

boot page is to be loaded. To boot from a specific boot page,

first set the BPAGE bits to the desired value and set the boot

force bit (BFORCE) of the System Control Register to initiate a

boot sequence.

The ADMC401 can boot its internal program memory from a

single byte-wide CMOS EPROM such as the 27C64 or the

27C512. A low cost commodity-grade EPROM with an indus-

try-standard access time can be used. The number of wait states

for the boot memory access is selected in the BWAIT field of

the System Control Register. This field can be set to any value

from 0 to 7 to set the number of wait states. The default value

for the BWAIT field is 7 so that seven wait states are inserted

into the reset-initiated boot loading sequence.

Timing of the boot memory access is identical to that of external

program memory or external data memory accesses, except that

the active strobe is

BMS rather than PMS or DMS. To address

eight pages of 8K bytes each, 16 address lines are needed. The

least significant 14 bits are output on the 14-bit address bus

(A13 to A0) while the most significant two bits are output on

the 2 MSBs of the data bus (D23 and D22) during boot memory

accesses. The data is read from the middle eight bits of the data

bus (D15 to D8).

The development tools for the ADMC401 support the creation